CadenceAllegroPCB封装建库程序

CADENCE的PCB封装库设计说明

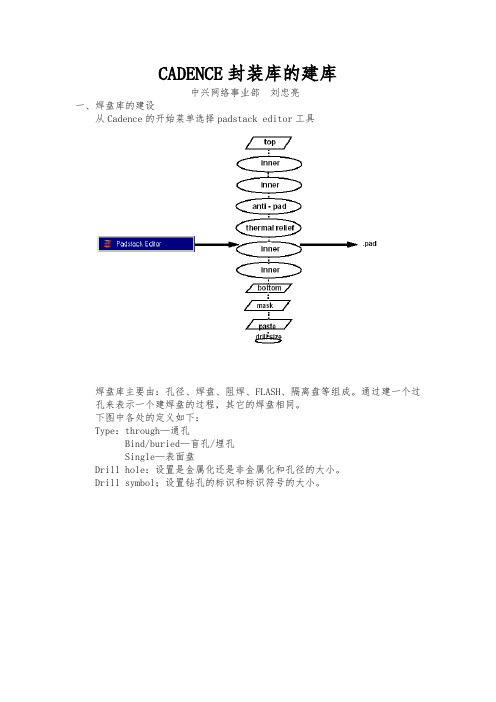

CADENCE封装库的建库中兴网络事业部刘忠亮一、焊盘库的建设从Cadence的开始菜单选择padstack editor工具焊盘库主要由:孔径、焊盘、阻焊、FLASH、隔离盘等组成。

通过建一个过孔来表示一个建焊盘的过程,其它的焊盘相同。

下图中各处的定义如下:Type:through—通孔Bind/buried—盲孔/埋孔Single—表面盘Drill hole:设置是金属化还是非金属化和孔径的大小。

Drill symbol;设置钻孔的标识和标识符号的大小。

上图设定各层的焊盘、热焊盘、隔离焊盘,以及表层的阻焊层、钢网层等。

各层可以用拷贝的方法。

Regular pad—焊盘Thermal relief—FLASH热焊盘/花焊盘(要先建好,在下面介绍怎么建)Anti pad—反焊盘/隔离焊盘Soldermask_top/bottom—阻焊Pastemask_top/bottom—钢网层经以上设置OK后,选择SAVE AS将文件存为 *.pad的文件,这就是所用的焊盘库,库的名称最好要有一定的规则,一看焊盘名称就能理解是什么焊盘。

二、FLASH热焊盘的设计1、打开PCB工具allegro,在drawing type中选择为flash symbol,如下图1。

2、选择菜单add-flash命令加入flash,如下图2所示。

设置花焊盘的内径/外径、花辨的宽度/数量/方向。

3、保存并创建flash通过保存生成.dra文件,以及创建出 .fsm文件,把这两个文件都保存好放入库中。

这里焊盘调用FLASH时只用到FSM文件,但因为以后修改等都要通过DRA 文件重新创建出,所以最好也一并将此文件保留。

三、器件库的创建以DIP14为例:1、从ALLEGRO中新建一封装文件,从TYPE中选择package symbol2、设置单位/精度,坐标原点等。

一般以器件中心或者器件的第一脚为原点,以后放置和移动器件等均以原点为操作点。

Allegro PCB Editor使用流程简介

本文档主要介绍Cadence的PCB设计软件Allegro PCB Editor的基本使用方法,其中封装库的建立不再赘述,参见“Cadence软件库操作管理文档”。

目录一、创建电路板 (2)1、新建电路板文件 (2)2、设置页面尺寸 (2)3、绘制电路板外框outline (3)4、电路板倒角 (4)5、添加装配孔 (5)6、添加布局/布线允许区域(可选) (7)二、网表导入和板层设置 (7)1、网表导入 (7)2、板层设置 (8)三、布局 (9)1、手动布局 (9)2、布局时对元器件的基本操作 (10)3、快速布局 (11)4、按ROOM方式布局 (12)5、布局复用 (15)四、设置约束规则 (17)1、设置走线宽度 (17)2、设置过孔类型 (18)3、间距规则设置 (19)五、布线 (20)1、设置走线格点 (20)2、添加连接线 (20)3、添加过孔 (21)4、优化走线 (21)5、删除走线 (21)六、敷铜 (22)1、设置敷铜参数 (22)2、敷铜 (23)七、PCB后处理 (25)1、检查电路板 (25)2、调整丝印文本 (27)3、导出钻孔文件 (28)4、导出光绘文件 (29)一、创建电路板1、新建电路板文件原理图成功导出网表进行PCB设计之前,首先需要根据实际情况建立电路板文件(.brd),主要是设置PCB板的外框尺寸(软件中称为outline)、安装孔等基本信息。

启动Allegro PCB Editor软件:选择“File-New”,在新建对话框中设置电路板存放路径,名称等信息:点击“OK”2、设置页面尺寸这里的页面尺寸并不是电路板的实际尺寸,而是软件界面的允许范围,根据实际电路板的大小设置合理的页面尺寸。

选择“Setup-Design Parameters”范围设置(Extents)中的Left X和Lower Y分别代表页面最坐下角的坐标,初次启动软件时,默认原点(0,0)为页面的最左下角。

CdenceAllegro元件封装制作流程含实例定稿版

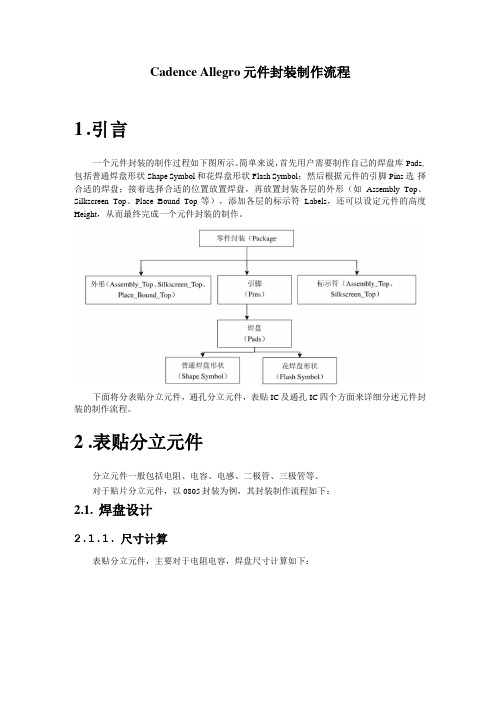

C d e n c e A l l e g r o元件封装制作流程含实例 HUA system office room 【HUA16H-TTMS2A-HUAS8Q8-HUAH1688】Cadence Allegro元件封装制作流程1.引言一个元件封装的制作过程如下图所示。

简单来说,首先用户需要制作自己的焊盘库Pads,包括普通焊盘形状Shape Symbol和花焊盘形状Flash Symbol;然后根据元件的引脚Pins选择合适的焊盘;接着选择合适的位置放置焊盘,再放置封装各层的外形(如Assembly_Top、Silkscreen_Top、Place_Bound_Top等),添加各层的标示符Labels,还可以设定元件的高度Height,从而最终完成一个元件封装的制作。

下面将分表贴分立元件,通孔分立元件,表贴IC及通孔IC四个方面来详细分述元件封装的制作流程。

2.表贴分立元件分立元件一般包括电阻、电容、电感、二极管、三极管等。

对于贴片分立元件,以0805封装为例,其封装制作流程如下:2.1.焊盘设计2.1.1.尺寸计算表贴分立元件,主要对于电阻电容,焊盘尺寸计算如下:其中,K为元件引脚宽度,H为元件引脚高度,W为引脚长度,P为两引脚之间距离(边距离,非中心距离),L为元件长度。

X为焊盘长度,Y为焊盘宽度,R为焊盘间边距离,G为封装总长度。

则封装的各尺寸可按下述规则:1)X=Wmax+2/3*Hmax+8 mil2)Y=L,当L<50 mil;Y=L+ (6~10) mil,当L>=50 mil时3)R=P-8=L-2*Wmax-8 mil;或者G=L+X。

这两条选一个即可。

个人觉得后者更容易理解,相当于元件引脚外边沿处于焊盘中点,这在元件尺寸较小时很适合(尤其是当Wmax标得不准时,第一个原则对封装影响很大),但若元件尺寸较大(比如说钽电容的封装)则会使得焊盘间距过大,不利于机器焊接,这时候就可以选用第一条原则。

简述pcb封装库创建流程

PCB封装库创建流程

PCB封装库创建流程如下:

1. 创建PCB封装库文件:选择“文件”按钮,在下拉菜单中执行“新建”-“封装”命令,即可打开一个空白库文件。

2. 添加焊盘:在“画布属性”面板中设置单位为mm,单击封装工具中的“焊盘”按钮,在画布上单击,放置焊盘。

3. 添加丝印:添加完焊盘后,可添加丝印,包括添加文字、图像等内容。

4. 添加属性:为元件封装添加属性,包括封装名称、尺寸等信息。

5. 保存PCB封装:完成元件封装的绘制后,需要保存PCB封装。

以上步骤完成后,即可创建出PCB封装库。

如需更多信息,建议咨询专业人士。

Cadenceallegro设计一个做封装的模板

Cadenceallegro设计一个做封装的模板

设计封装我们用PCB Editor或Package Designer都行

(1)点击File--new--package symbol,给个名字,例如:tem;

(2)接下来设置参数(单位,格点,区域)和颜色

a、Setup--板参数(DP)-- Display 勾选显示相关选项,设置

0.1格点

-- Design 设置单位:mm和精度:3位小数,

设置Extents:X和Y设置-100;W和H设置200

b、Display--设置颜色(如下图)--PG--Pin number管脚(红色)

Assembly装配顶 (粉色)

silkscreen 丝印层 (白色)(元件外框,1脚标识)

place_bound_top 元件高度 (蓝色)

Paste_top ,soldermask_top;

设置完保存到某个路径,做BGA,QFN等标准器件时,加载就可

以了,每次做封装就方便很多;在用户参数(setup-UP)--Path--config--点next,有个wizard,在此处设置模板的路径。

做直插电解电容,接口,连接器等不规则时,就直接打开模板,save as 另存为指定名称。

cadence allegro pcb layout详细教程

cadence allegro pcb layout详细教程

本文为大家带来cadence allegro pcb layout详细教程。

一、用Design Entry CIS(Capture)设计原理图1、创建工程file--》new--》project ;输入工程名称,指定工程放置路径;

2、设置操作环境OpTIons--》Preferencses:颜色:colors/Print

格子:Grid Display

杂项:Miscellaneous

常取默认值

3、配置设计图纸:设定模板:OpTIons--》Design Template:(应用于新图)

设定当前图纸OpTIons--》SchemaTIc Page Properities

4、创建元件及元件库File--》New Library --》选择要添加到的工程

Design --》New Part.(或者在Library处右击选择New Part)

(1)Homogeneous:复合封装元件中(多个元件图组成时)每个元件图都一样(default 适用于标准逻辑)

(2)Heterogeneous:复合封装元件(多个元件图组成时)中使用不一样的元件图(较适用于大元件)

一个封装下多个元件图,以View ext part(previous part)切换视图元器件封装:

(1)place --》line画线,用来画封装外形;

(2)place--》pin放置管脚;放单个或多个;

不同类型的管脚选择的type不同;

5、绘制原理图(1)放置电器。

Cadence_PCB封装库的制作及使用

第六章Cadence PCB封装库的制作及使用封装库是进行PCB设计时使用的元件图形库,本章主要介绍使用Cadence 软件进行PCB封装库制作的方法及封装库的使用方法。

一、创建焊盘在设计中,每个器件的封装引脚都是由与之相关的焊盘构成的,焊盘描述了器件引脚如何与设计中所涉及的每个物理层发生关系,每个焊盘包含以下信息:●焊盘尺寸大小和焊盘形状;●钻孔尺寸和显示符号。

焊盘还描述了引脚在表层(顶层和底层)的SOLDERMASK、PASTEMASK 和FILMMASK等相关信息。

同时,焊盘还包含有数控钻孔数据,Allegro用此数据产生钻孔符号和钻带文件。

1.焊盘设计器Allegro在创建器件封装前必须先建立焊盘,建立的焊盘放在焊盘库里,在做器件封装时从焊盘库里调用。

Allegro创建的焊盘文件名后缀为.pad。

Allegro 用Pad Designer创建并编辑焊盘。

在Allegro中,一个器件封装的每个引脚必须有一个与之相联系的焊盘名。

在创建器件封装时,将引脚添加到所画的封装中。

在添加每一个引脚时,Allegro 找到库中的焊盘,将焊盘的定义拷贝到封装图中,并显示焊盘的图示。

基于这个原因,必须在创建器件封装前先设计出库中要用到的焊盘。

在创建器件封装符号时,Allegro存储每一个引脚对应的焊盘名而不是焊盘数据,在将器件封装符号加到设计中时,Allegro从焊盘库拷贝焊盘数据,同时从器件封装库拷贝器件封装数据。

Allegro用在全局或本地环境文件定义的焊盘库路径指针(PADPATH)和器件封装库路径指针(PSMPATH)查找焊盘库和器件封装库。

一旦一个焊盘在某个设计中出现一次,Allegro使其他所有相同的焊盘参考于那个焊盘而不是参考库中的焊盘。

有两种方法可以启动焊盘设计器:1、选择【开始】/【程序】/【Cadence SPB 16.6】/【PCB Editor Utilities】/【Pad Designer】命令,即可启动焊盘设计器;2、按照前面章节所述,创建一个库项目,库项目界面如图6_1所示,点击界面中的“Pad Stack Editor”按钮,也可以启动焊盘设计器。

Cadence_Allegro元件封装制作流程含实例

Cadence Allegro元件封装制作流程1.引言一个元件封装的制作过程如下图所示。

简单来说,首先用户需要制作自己的焊盘库Pads, 包括普通焊盘形状Shape Symbol和花焊盘形状Flash Symbol;然后根据元件的引脚Pins选择合适的焊盘;接着选择合适的位置放置焊盘,再放置封装各层的外形(如Assembly_Top、Silkscreen_Top、Place_Bound_Top等),添加各层的标示符Labels,还可以设定元件的高度Height,从而最终完成一个元件封装的制作。

下面将分表贴分立元件,通孔分立元件,表贴IC及通孔IC四个方面来详细分述元件封装的制作流程。

2.表贴分立元件分立元件一般包括电阻、电容、电感、二极管、三极管等。

对于贴片分立元件,以0805封装为例,其封装制作流程如下:2.1.焊盘设计2.1.1.尺寸计算表贴分立元件,主要对于电阻电容,焊盘尺寸计算如下:其中,K 为元件引脚宽度,H 为元件引脚高度,W 为引脚长度,P 为两引脚之间距离(边 距离,非中心距离),L 为元件长度。

X 为焊盘长度,Y 为焊盘宽度,R 为焊盘间边距离,G 为封装总长度。

则封装的各尺寸可按下述规则:1) X=Wmax+2/3*Hmax+8 mil2) Y=L ,当 L<50 mil ; Y=L+ (6~10) mil ,当 L>=50 mil 时3) R=P-8=L-2*Wmax-8 mil ;或者G=L+X 。

这两条选一个即可。

个人觉得后者更容易理解,相当于元件引脚外边沿处于焊盘中点,这在元件尺寸较小时很适合(尤其是当 Wmax 标得不准时,第一个原则对封装影响很大),但若元件尺寸较大(比如说钽电容 的封装)则会使得焊盘间距过大,不利于机器焊接,这时候就可以选用第一条原则。

本文介绍中统一使用第二个。

注:实际选择尺寸时多选用整数值,如果手工焊接,尺寸多或少几个mil 影响均不大, 可视具体情况自由选择;若是机器焊接,最好联系工厂得到其推荐的尺寸。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2.钻孔直径取值=器件管脚直径+8mi。

3.焊盘直径取值=钻孔直径+21mil。(取5倍数)

4.对于图中第二种情况实体左边缘与焊盘中心距离=1.5d+50mil。

建库要点:

1.环境设置。DrawingType选择PackageSymbol。Drawingsize毫米选3位精度,微英寸选2位精度。网格设置为5mil倍数。

ThermalRelief:与Antipad取相同尺寸

阻焊:阻焊尺寸比钻孔尺寸大6mil

过孔

命名规则:VIA钻孔大小,比如VIA10,如果为堵孔,命名为VIA钻孔大小-F。比如VIA12-F。

参数计算:

参照下列表

钻孔(mil)

焊盘

钢网

阻焊

Antipad

ThermalRelief

VIA8

8

18

18

13Байду номын сангаас

7.生成器件RefDes。参考表贴电阻设置方法。

8.生成器件Value。参考表贴电阻设置方法。

9.时间标注。参考表贴电阻设置方法。

10.产生psm库文件。参考表贴电阻设置方法。

11.生成Device文件。详细情况参考“DEVICE文件”。

不规则表贴分立元件

命名规则:按照器件厂家和其PN命名,如UTS10354/UTS-ALX589623。(如PN第一字与公司名最后一字同为字母或同为数字,则需在中间加中划线,否则直连。)

8.生成器件Value。器件Value标注在COMPONENTVALUE/ASSEMBLY_TOP层。

9.时间标注。时间标注表明库的最新刷新时间,以便于版本管理。此项标注于PACKAGEGEOMETRY/DISPLAY_TOP层,格式为。

10.产生psm库文件。DatabaseCheck,在指定目录下保存dra文件,生成psm文件。

封装库主要由PackageSymbol,MechanicalSymbol,FormatSymbol,ShapeSymbol,Flashsymbol五种.他们又可以分为可编辑(*.dra)与不可编辑(PackageSymbol→.psm,MechanicalSymbol→.bsm,FormatSymbol→.osm,ShapeSymbol→.ssm,flashsymbol→*.fsm)

5.设置器件Place_Boundary。参考表贴电阻设置方法。

6.添加禁布区域。表贴二极管不允许在丝印框范围类存在过孔,选菜单Setup->Area->ViaKeepout,按丝印大小勾画出相应禁布区域。如果器件对于部分区域有禁布线要求,则选菜单Setup->Area->RouteKeepout,按要求勾画出相应禁布区域。

7.生成器件RefDes。参考表贴电阻设置方法。

8.生成器件Value。参考表贴电阻设置方法。

9.时间标注。参考表贴电阻设置方法。

10.产生psm库文件。参考表贴电阻设置方法。

11.生成Device文件。详细情况参考“DEVICE文件”。

保险丝

命名规则:一般情况下按照FUSE–A(B、C…)派生方式进行命名,特殊情况下按照器件的PN来进行命名。

4.器件丝印。如果器件焊盘完全处于器件实体内,则按照器件实体件大小采用4/6mil线宽在PACKAGEGEOMETRY/SILKSCREEN_TOP层勾勒出器件丝印框;如果焊盘处于器件实体外,则沿焊盘阻焊外边缘大10mil尺寸在相同层描绘出器件丝印。实情况选择是否使用第一管脚标识。如果器件管脚较多,则需在PACKAGEGEOMETRY/SILKSCRREN_TOP层将器件5n管脚标识出。而对于矩形或圆形器件,需将标志性丝印画出,避免器件摆放错误。

11.生成Device文件。详细情况参考“DEVICE文件”。

二极管

命名规则:通常制命名,前缀为SD。例如SD0603、SD0805……如果器件封装为标准封装,则按标准封装命名,如SOD123、DO-252,非标准器件按器件PN进行命名。

器件封装参数计算:

1.L=O+T+5mil,其中O近似取值范围为0.5H到50mil。H为器件高度。按照计算结果取5倍数为最终焊盘长度值。

5.设置器件Place_Boundary。参考表贴电阻设置方法。

6.添加禁布区域。如果器件封装区域内禁止打孔,选菜单Setup->Area->ViaKeepout,按丝印大小勾画出相应禁布区域。如果器件对于部分区域有禁布线要求,则选菜单Setup->Area->RouteKeepout,按要求勾画出相应禁布区域。

METRIC

1005

1608

2012

3216

3225

3246

5025

6332

建库要点:

建库要点:

1.环境设置。DrawingType选择PackageSymbol。Drawingsize毫米选3位精度,微英寸选2位精度。网格设置为5mil倍数。

2.放置焊盘。按照参数计算结果在库中选择合适的焊盘。放置焊盘时,保证器件中心位于坐标原点,检查PinNumber是否正确。

其中目前和我们联系比较大的是PackageSymbol,MechanicalSymbol,FormatSymbol,Flashsymbol。下表为他们的简单介绍与比较。

内容

需提供参数

备注

Padstack

器件焊盘制作

焊盘形状、尺寸、类型

1

PackageSymbol

BGA、连接起、电阻、电容和变压器等电子设备的物理描述

参数计算:

焊盘:分为表层焊盘和内层焊盘,表层焊盘尺寸参考各器件封装参数计算;内层焊盘比钻孔大尺寸10~20mil

Antipad:各层Antipad至少比焊盘大10mil,具体尺寸大小应该考虑电气安全、传输阻抗、生产可行性等实际情况而定

ThermalRelief:与Antipad取相同尺寸

阻焊:阻焊尺寸比焊盘尺寸大6mil

5.设置器件Place_Boundary。参考表贴电阻设置方法。

6.添加禁布区域。表贴保险丝不允许在丝印框范围类存在过孔,选菜单Setup->Area->ViaKeepout,按丝印大小勾画出相应禁布区域。如果器件对于部分区域有禁布线要求,则选菜单Setup->Area->RouteKeepout,按要求勾画出相应禁布区域。

器件类型、边框管脚尺寸、管脚数目以及一些特殊要求

2

MechanicalSymbol

机械符号,比如加工孔,外框等非电气属性器件,其不包含管脚信息。也可以包括一些线、器件、过孔的keepinorkeepout区域。

孔、外框或者区域的大小

FormatSymbol

生产图纸、标志及其相关制作

FlashSymbol

26

26

VIA8-F

8

18

28

/

26

26

VIA10

10

22

22

15

32

32

VIA10-F

10

22

22

/

32

32

VIA12

12

25

25

17

40

40

VIA12-F

12

25

25

/

40

40

VIA16

16

30

30

21

45

45

VIA16-F

16

30

30

/

45

45

VIA24

24

40

40

29

60

60

备注:

封装库

封装库的组成

5.设置器件Place_Boundary。Place_Boundary描述了封装的投影高度。选菜单Setup->Area->PackageBoundary,按丝印大小勾画区域,选菜单Setup->Area->PackageHeight,点击设定区域,在控制面板的Option选项设置器件高度的最大最小值,空缺时系统自动按缺省值300mil处理。

器件封装参数计算:参照器件手册推荐值。

建库要点:

1.环境设置。参考表贴电阻设置方法。

2.放置焊盘。参考表贴电阻设置方法。

3.勾勒器件实体。参考表贴电阻设置方法。

4.器件丝印。根据器件大小采用4/6mil线宽沿焊盘外10mil处在PACKAGEGEOMETRY/SILKSCREEN_TOP层勾勒出器件丝印框。并在丝印层标注器件电流允许值。

非金属化孔

命名规则:MaDOTb(钻孔直径为a.bmm)/Tooling-Hole,(2004-4-15以前PAD为按照FIaDOTb命名),如果为整数直径,则为Ma即可。

参数计算:

焊盘:设置焊盘比钻孔大1mil

Antipad:各层Antipad至少比焊盘大10mil,具体尺寸大小应该考虑电气安全、生产可行性等实际情况而定

表贴式分立元件

电阻/电容/电感

命名规则:表贴电阻/电容/电感按照英制命名,前缀分别为SR/SC/SL。例如SR0603、SR0805……

器件封装参数计算:

表贴电阻/电容/电感的焊盘大小参照器件手册推荐值。下表列出常见封装公英制对照表:

INCH

0402

0603

0805

1206

1210

1218

2010

2512

封装参数计算:参考器件手册推荐值。

建库要点:

1.环境设置。参考表贴电阻设置方法。

2.放置焊盘。此类封装原点为所有管脚外边缘所构成矩形中心点。依照次中心点计算出各焊盘放置位置。注意检查PinNumber的正确。