数字匹配滤波器的优化设计与FPGA实现

基于FPGA的音频信号数字滤波器设计与实现

基于FPGA的音频信号数字滤波器设计与实现音频信号数字滤波器是一种常见的数字信号处理技术,它可以对音频信号进行滤波处理,提取出用户感兴趣的频率成分,去除不需要的噪声等。

近年来,随着现代科技的发展,基于现场可编程门阵列(FPGA)的音频信号数字滤波器的设计与实现越来越受到人们的关注。

本文将介绍基于FPGA的音频信号数字滤波器的设计原理和实现方法。

FPGA是一种可编程逻辑器件,具有高度的灵活性和可编程性,可以根据用户的需求进行定制化的设计。

在音频信号处理中,FPGA可以被用来实现数字滤波器,通过对音频信号进行采样和滤波处理,改善音频信号的质量。

1. 设计原理基于FPGA的音频信号数字滤波器的设计原理主要包括以下几个方面:1.1 数字滤波器的选择在设计过程中,首先需要选择适合音频信号处理的数字滤波器。

常见的数字滤波器包括有限脉冲响应(FIR)滤波器和无限脉冲响应(IIR)滤波器。

FIR滤波器具有线性相位和稳定性等优点,常用于音频信号处理中。

1.2 滤波器的特性和参数根据音频信号处理的要求,可以确定滤波器的通带、阻带、截止频率等参数。

通过对滤波器的特性进行设置,可以实现对音频信号的不同频段进行滤波处理。

1.3 整体系统设计在确定滤波器的参数后,需要进行整体系统的设计。

这包括对FPGA的硬件资源进行评估,选择适合的FPGA器件以及其他所需外设的选择。

同时,还需要设计滤波器的时钟、采样率等系统参数,并进行时序分析和综合等步骤。

2. 实现方法基于FPGA的音频信号数字滤波器的实现方法主要涉及以下几个方面:2.1 开发环境的选择在进行设计之前,需要选择适合的开发环境。

常见的FPGA开发工具包括Xilinx的Vivado和Altera的Quartus II等。

这些工具提供了实现FPGA的硬件描述语言(如Verilog或VHDL)以及综合、布局布线等功能。

2.2 硬件描述语言的编写根据滤波器的设计原理和参数,可以使用硬件描述语言编写滤波器的逻辑电路。

直扩系统中匹配滤波器的FPGA实现及优化设计

直 扩 系统 中匹配 滤 波器 的 F GA 实 现及 优 化 设 计 P

顾 何 方 , 康 志 伦

(. 1合肥工业大学 计算机与信息学院 , 安徽 合肥 2 0 0 ; . 中国电子科技集 团公 司第 3 309 2 8研究所 , 安徽 合肥

203) 3 0 1

摘

要 : 匹配滤波器也称作数字相关器 , 数字 文章介 绍 了数 字 匹配 滤波器在 F G 上 的实 现方式 , 于卫 星 PA 对

通信等领域 中要 求的匹配长度 较长而导致 的器件 消耗增 大 , 讨论 了资源 优化 的途 径 , 对 比 2种优 化方式 , 并 给出了经改进后 的逻辑复用 的 FR结构 ; I 综合结果表 明, 该结 构能有效地 节省器 件的消耗 。

c rea in ln t n s t l t o o r lt e g h i ael ec mm u ia in f l sa e d s u s d a d a m p o e lilxn I o i n c to i d r ic s e n n i r v d mu t e i g F R e p sr cu ei r p s d tu t r sp o o e .Th i u ain r s l s o h tt i sr cu ei fe tv nr d cn e o r e esm lto e u t h wst a hs tu t r se fciei e u ig r s u c

b sn y u i g FPGA n p e d s e tu y tm s i DS s r a p cr m s se

GU - n . KANG h-u He f g a Z i n l

( . c o l f o u e n fr t n 1 S h o mp t r d I o mai ,Hee Unv ri f c n lg ,Hee 2 0 0 ,C ia 2 No 3 s a c n t u e hn oC a n o fi iest o h oo y y Te fi 3 0 9 hn ; . . 8Re e rh I si t ,C iaE t

基于FPGA的带通数字滤波器设计与实现

毕业设计说明书基于FPGA的带通数字滤波器设计与实现学生姓名专业名称电子信息工程指导教师电子与信息工程系基于FPGA的带通数字滤波器设计与实现FPGA-Based Band-Pass Digital Filter Design andImplementation摘要随着高速DSP技术的广泛应用,实时而又快速可靠地进行数字信号的处理越来越成为用户追求的目标。

本文分析了国内外数字滤波技术的应用现状与发展趋势,介绍了数字滤波器的基本结构,介绍了数字滤波器的理论及常见的实现方法。

FPGA是常用的可编程逻辑器件,它所具有的查找表结构非常的适用于实现实时而又快速可靠的数字滤波器上,加上Verilog语言灵活的描述方式以及与硬件无关的这种特点,使得使基于Verilog语言的FPGA芯片实现数字滤波器成为研究的方向。

本文正是围绕着硬件描述语言在数字硬件系统设计中的应用展开来的。

首先从比较传统的数字硬件系统的设计方法与采用硬件描述语言的数字硬件系统设计方法的特点出发,介绍了EDA技术发展的过程以及VHDL语言的特点。

介绍了分布式算法,基于ALTERA 公司四输入查找表结构的FPGA器件的带通数字滤波器设计技术和结合先进的Quartus II 软件、Matlab软件进行高效设计的方法和途径,给出了设计仿真结果。

该设计能够满足要求,设计效率高,对于FPGA硬件资源高效合理的利用。

关键词:FPGA;Verilog;查找表;分布式算法ABSTRACTWith the extensive application of high-speed DSP technology, the users pursuit the target that it is real time high-speed and reliable to process digital signal. This paper analyzes the situation of application and development of digital filter technology home and abroad, introduced the basic structure of the digital filter, introduce the theory of digital filter and common method of its implementation. FPGA is ones of usual PLD, and its architecture of LUT is be applicable to implement real-time, high-speed and reliable digital filter, in addition, Verilog HDL can be quickly learned and mastered , and has nothing to do with hardware, which make it to be a research problem that using Verilog achieves digital filters based on FPGA.This paper is arranged around the apply of Verilog in digital system design. We analyze the way of digital system design traditional and using Verilog ,and introduced the development of EDA, the characteristic of Verilog. Introduced the distributed algorithm, the design technology of the band-pass digital filter in digital algorithm design and implementation is described based on4-input look-up table in FPGA' s, the way and method of high-speed design using excellent Quartus II software,Matlab software. The design can meet the quest and be high-speed, proper in using FPGA’ hardware.Keywords: FPGA; Verilog; LUT(Look-Up-Table); Distributed Algorithm目录第1章绪论 (1)1.1 数字滤波器研究的背景与意义 (1)1.2 数字滤波器的研究基础 (1)1.2.1 电子设计EDA自动化技术 (1)1.2.2可编程逻辑器件 (2)1.2.3硬件描述语言Verilog及数字系统设计方法 (3)1.3 数字滤波器实现方法的现状分析 (4)1.4 本文的研究内容 (5)第2章数字滤波器原理及设计方法 (7)2.1 数字滤波器的基本原理................................ 错误!未定义书签。

基于FPGA的数字滤波器设计与实现

基于FPGA的数字滤波器设计与实现数字滤波器是一种非常重要的信号处理器件,用于从信号中分离出特定频率下的成分。

它可以应用于音频、无线通讯、图像处理等领域,并且随着数字信号处理技术的发展,数字滤波器的性能和功能也日益提高。

本文将介绍基于FPGA的数字滤波器的设计与实现,以及其在实际应用中的一些注意事项。

一、数字滤波器的工作原理数字滤波器是通过模拟信号转换成数字信号后,在数字域中进行信号处理的器件。

其工作原理与模拟滤波器类似,其主要作用是从信号的频谱中分离出所需要的成分。

数字滤波器通常由数字滤波器器件和数字信号处理器构成。

数字滤波器可以分为时域滤波器和频域滤波器。

时域滤波器是根据信号的时间域特性进行滤波,滤波算法通常采用卷积或差分运算。

频域滤波器是将信号变换到频域后通过频率响应特性进行滤波,其通常采用离散傅里叶变换(DFT)或快速傅里叶变换(FFT)等算法。

二、FPGA实现数字滤波器的方式FPGA是一种基于可编程逻辑单元的可重构芯片,具有灵活性、高速性和可重构性等特点,非常适合用于数字信号处理的应用。

FPGA实现数字滤波器的方式主要有两种:直接实现数字滤波器和通过CPU控制实现数字滤波器。

直接实现数字滤波器是指将数字滤波器的算法逻辑直接实现在FPGA芯片内部,其优点是响应速度快、功耗低、实现简单。

缺点是难以对算法进行改进和优化。

而通过CPU控制实现数字滤波器则是将数字滤波器的算法逻辑实现在CPU中,通过FPGA模块将需要滤波的信号通过DMA方式传输给CPU进行处理。

该方式的优点是灵活性高、可扩展性强,缺点是响应速度慢。

三、数字滤波器设计的基本步骤数字滤波器的设计需要进行三个主要的步骤:滤波器的规格化、系统函数的设计和离散化。

滤波器的规格化是指根据滤波需求,对滤波器进行不同的设计。

主要包括滤波器类型的选择、通带、阻带和过渡带的确定等。

系统函数的设计是指根据滤波器的规格化要求,设计出数字滤波器的系统函数。

基于FPGA的数字滤波器的设计与实现

基于FPGA的数字滤波器的设计与实现数字滤波器是一种非常重要的数字信号处理技术,用于消除输入信号中的噪声,并提高信号品质和可靠性。

FPGA(Field Programmable Gate Array)是一种用于构建数字电路的可编程逻辑器件,因其高度的可定制性、可重构性和高性能而被广泛应用于数字信号处理中。

本文将介绍基于FPGA的数字滤波器的设计和实现,包括滤波器原理、数字滤波器设计方法、FPGA实现技术以及实验结果分析等内容。

一、数字滤波器原理数字滤波器是滤波器的一种,其实现基于数字信号处理技术。

数字滤波器的输入信号是离散时间信号,输出信号也是离散时间信号。

数字滤波器通过在离散时间域上对输入信号进行滤波,实现对输入信号中某些频率成分的滤除或保留。

数字滤波器通常分为FIR(有限脉冲响应)滤波器和IIR(无限脉冲响应)滤波器两类。

FIR滤波器是一种线性相位滤波器,其系统函数是一个有限长度的冲激响应权重系数序列。

FIR滤波器通过对输入信号的每个样本与权重系数的乘积进行累加,输出得到滤波后的信号。

FIR滤波器具有零相位失真、线性相应特性、易于设计、易于实现等优点。

IIR滤波器是一种具有无限脉冲响应的滤波器,其系统函数是一个有理多项式。

与FIR滤波器相比,IIR滤波器具有更高的滤波效率、更低的计算复杂度和更好的逼近性,但也存在稳定性差、相位失真大等问题。

二、数字滤波器设计方法数字滤波器的设计方法主要包括滤波器性能要求的确定、滤波器类型的选择、滤波器设计的数学模型的建立、滤波器参数的计算、滤波器实现等几个方面。

在确定滤波器性能要求方面,需要考虑滤波器的通频带、阻带、通带和阻带带宽、滤波器响应曲线、阶数等方面的参数。

在滤波器类型的选择方面,需要根据滤波器的性能要求、实现难易度、计算复杂度和开销等方面的因素进行综合考虑。

在滤波器设计的数学模型的建立方面,需要根据选定的滤波器类型建立其对应的数学模型。

在滤波器参数的计算方面,需要根据滤波器的数学模型进行参数的计算和优化。

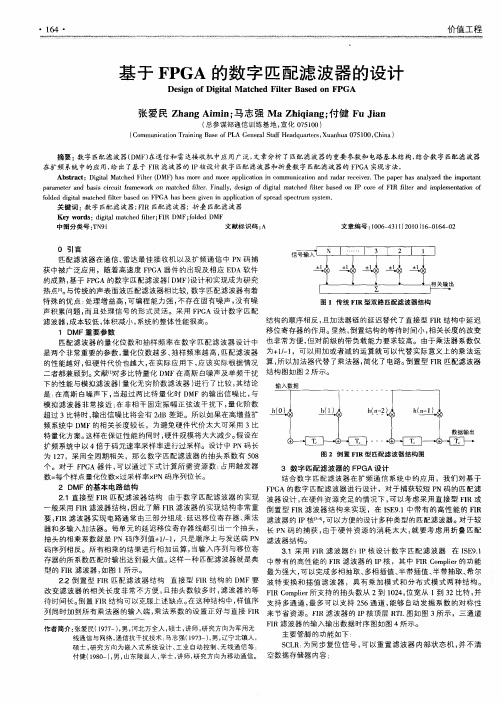

基于FPGA的数字匹配滤波器的设计

摘 要 : 字 匹配滤 波 器( MF在 通信 和 雷达接 收机 中应用 广 泛, 数 D ) 文章 分析 了 匹配 滤 波器 的重要 参数 和 电路基 本 结构 , 结合 数字 匹配滤 波器

在扩 频 系统 中的应 用 , 出 了基 于 F R滤波 器的 I 核 设计 数 字 匹配滤波 器和折 叠数 字 匹配滤 波器 的 F G 实现 方 法。 给 I P PA

文章 编 号 :0 6 4 I( 00)6 06 — 2 10 — 3 12 1 1— 14 0

O 引言

匹 配 滤 波器 在通 信 、 达 最 佳 接 收机 以 及 扩 频 通 信 中 P 雷 N码 捕 获 中 被 广 泛 应 用 , 随着 高 速度 F G P A器 件 的 出现 及相 应 E A软 件 D 的成 熟 , 于 F G 的数 字 匹配 滤 波 器 ( F) 计和 实 现成 为研 究 基 PA DM 设 热 点 l 与传 统 的声 表 面 波 匹配 滤 波 器 相 比较 , l l 。 数字 匹配 滤 波 器 有着 特 殊 的优 点 : 理 增 益 高 , 编 程 能 力 强 , 存 在 固 有 噪 声 , 有 噪 处 可 不 没 图 1 传 统 FR 型 双 路 匹 配滤 波 器 结 构 I 声 积 累 问 题 , 且 处 理 信 号 的形 式 灵 活 。 采 用 F G 设计 数 字 匹 配 而 PA 结 构 的 顺 序相 反 , 加法 器 链 的 延 迟 替 代 了直接 型 FR结 构 中延 迟 且 I 滤 波 器 , 本 较低 , 积减 小 , 统 的 整体 性 能 很 高 。 成 体 系 移 位 寄 存 器 的作 用 。 然 , 置 结 构 的 等 待 时 间小 , 关长 度 的 改 变 显 倒 相 1 MF重 要 参数 D 但 匹配滤波器 的量化位数和抽样 频率在数 字匹配滤波器设计 中 也 非常 方 便 , 对 前 级 的带 负载 能 力 要 求 较 高 。 由于 乘法 器 系数 仅 1 ,可 以用 加 或 者 减 的 运 算 就 可 以代 替 实 际 意 义上 的乘 法运 一 是 两 个 非 常 重 要 的参 数 , 化 位 数 越 多 、 量 抽样 频 率 越 高 , 配 滤 波器 为+ /1 匹 所 简 倒 I 的性 能 越 好 , 硬 件代 价 也 越 大 , 实 际 应 用 下 , 该 实 际 根 据 情 况 算 , 以加 法 器 代 替 了乘 法器 , 化 了 电路 。 置 型 FR 匹配 滤 波器 但 在 应 二者 都 兼 顾 到 。 献川 多 比特 量 化 D 文 对 MF在 高 斯 白噪声 及 单 频 干扰 结 构 图 如 图 2所 示。 下 的性 能 与 模 拟 滤波 器 ( 化 无 穷 阶 数 滤 波 器 ) 行 了 比较 , 结论 量 进 其 是 : 高 斯 白 噪声 下 , 在 当超 过 两 比特 量 化 时 D MF的输 出信 噪 比 , 与 模 拟 滤 波 器 非 常 接 近 非 相 干 固 定 振 幅 正 弦 波 干扰 下 , 化 阶 数 在 量 超过 3比特时 , 输出信 噪比将会有 2 B差距。所以如果在高增益扩 d 频 系统 中 D MF的 相 关 长 度 较 长 ,为避 免 硬 件 代 价 太 大 可 采 用 3比 特量 化 方 案 。 样 在 保 证性 能 的 同时 , 件 规 模将 大 大减 少 。 设 在 这 硬 假 扩频 系统 中以 4信于码元速率采样率进行过采样。设计 中 P N码长 为 17 2 ,采用全周期相关 ,那么数字匹配滤波器的抽头系数有 5 8 0 个。对于 F G P A器 件 , 可以通过下式计算所需资 源数 : 占用触 发器 数: 每个 样 点 量 化 位 数× 采 样 率 x N码 序 列 位 长 。 过 P

基于FPGA的多模式数字匹配滤波器的设计与实现

c e i v i n g e n d o f t h e s a me d i r e c t s e q u e n c e s p r e a d s p e c t r u m c o mmu n i c a t i o n s y s t e m f o r d e s p r e a d i n g o f s p r e a d s p e c t u m s r i g n ls a wi t h mu l t i p l e s p r e a d—s p e c t r u m r a t i o s i mp r o v e s t h e p e r f o ma r n c e o f c o mmu n i c a t i o n s y s t e m. On hi t s b a s i s ,t h e e f f e c t i v e n e s s i s v e if r i e d b y

获 得 更 高 的 系统 性 能 。 首 先 介 绍 了数 字 匹 配 滤多模 式 DMF的 设 计 原 理 , 在 同一 个 直 接 序 列 扩 频 通 信 系 统 的 接 收 端 集 成 多种 模 式 , 实现 对 多种 扩 频 比 扩 频 信 号 的 解 扩 , 提 高通信 系统的性 能 。在 此基础 上 , 通

数字匹配滤波器的优化设计与FPGA实现

一

7一 0

《 国外 电子元器件》06 20 年第 5期 20 年 5月 06

●主 题 论 文

数 字 匹配 滤 波 器 的优化 设计 与 F GA 实现 P

( 光 , 田 斌 王 ,吴 勉 易克初 田红心 , , )

(. 安 电子科 技 大 学 综 合 业 务 网 国 家重 点 实验 室 , 西 西安 7 0 7 ; 1 西 陕 10 1 2深圳 通 创 通 信 有 限公 司 , 东 深 圳 5 8 0 ) . 广 10 1

接

匹 配滤 波器 是 扩 频通 信 中的关 键 部件 , 的性 它

能直 接影 响到通 信 的质量 。本 文从 数字 匹配滤 波器

的理论 及 结构 出发 , 讨论 了 它 在数 字通 信 直 扩 系统 中的应用 ,并 对其 基于 F G 的具体 实现 进行 了优 PA

化。

2 数 字 匹配 滤 波 捕 获 技 术

Ab t a tT e m— e u n e Ss n h o o s c p u n n d r c e u n e s r a p cr m y t m y U — sr c : h s q e c ’ y c r n u a t r g i ie ts q e c p e d s e tu s se b S i i g d gtl mac i g f tr i d s r e , i e l a in sr c u e i a a y e n t o t z t n i l — n ii th n l e c b d a i e s i t r a i t tu t r s n lz d a d i p i a i mp e s z o s mi o me tt n i ic s e n d ti T e r s l s o h tt e o t z t n d gtl mac i g f tr c n d — n a i s d s u s d i ea l o . e u t h ws t a h p i ai ii t h n l a e h mi o a i e c e s h e o r e o c p t n g e t n n r a e wo k n f ce c . r a e t er s u c c u a i r al a d i c e s r i g e f i n y o y i

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

●主题论文1引言在通信系统中,匹配滤波器的应用十分广泛,尤其在扩频通信如在CDMA系统中,用于伪随机序列(通常是m序列)的同步捕获。

匹配滤波器是扩频通信中的关键部件,它的性能直接影响到通信的质量。

本文从数字匹配滤波器的理论及结构出发,讨论了它在数字通信直扩系统中的应用,并对其基于FPGA的具体实现进行了优化。

2数字匹配滤波捕获技术在直接序列扩频解扩系统中,数字匹配滤波器的捕获是以接收端扩频码序列作为数字FIR滤波器的抽头系数,对接收到的信号进行相关滤波,滤波输出结果进入门限判决器进行门限判决,如果超过设定门限,表明此刻本地序列码的相位与接收扩频序列码的相位达到同步。

如果并未超过设定门限,则表明此刻本地序列码的相位与接收到的扩频序列码的相位不同步,需要再次重复相关运算,直到同步为止,如图1所示。

数字匹配滤波器由移位寄存器、乘法器和累加器组成,这只是FIR滤波器的结构形式,只不过伪数字匹配滤波器的优化设计与FPGA实现(王光1,田斌1,吴勉2,易克初1,田红心1)(1.西安电子科技大学综合业务网国家重点实验室,陕西西安710071;2.深圳通创通信有限公司,广东深圳518001)摘要:介绍在直接序列扩频通信中应用数字匹配滤波器实现m序列同步,分析其具体结构,详细讨论了其基于FPGA(现场可编程门阵列)的性能优化。

结果表明,数字匹配滤波器用FPGA实现时,能够大大减少资源占用,并提高工作效率。

关键词:FPGA;数字匹配滤波器;直接序列扩频中图分类号:TN713文献标识码:A文章编号:1006-6977(2006)05-0070-04Digitalmatchingfilter’soptimizationdesigningandFPGAimplementationWANGGuang1,TIANBin1,WUMian2,YIKe-chu1,TIANHong-xin1(1.NationalKeyLaboratoryofIntegratedServicesNetworks,XidianUniversity,Xi’an710071,China;2.ShenzhenNewComTelecommunicationsCo.,Ltd,Shenzhen518001,China)Abstract:Them-sequence’ssynchronouscapturingindirectsequencespreadspectrumsystembyus-ingdigitalmatchingfilterisdescribed,itsrealizationstructureisanalyzedanditsoptimizationimple-mentationisdiscussedindetail.Theresultshowsthattheoptimizationdigitalmatchingfiltercande-creasetheresourceoccupationgreatlyandincreaseworkingefficiency.Keywords:FPGA;digitalmatchingfilter;directsequencespreadspectrum图1数字匹配滤波器的结构图码寄存器中的系数为-1或+1,实际并不是真正意义上的乘法。

伪码寄存器中的数据可以由一种伪随机序列发生器产生。

数字匹配滤波器的表达式为:其中,x(n)为输入信号;h(-i)为滤波系数,由接收端扩频码决定,取值-1或+1,m序列码元为1,取值为+1,m序列码元为0,取值为-1。

匹配滤波器的长度N等于扩频比,也就是对于每一信息符号的扩频码元数,即Tb/Tc。

当输入信号{x(n)}与本地扩频码{h(-i)}匹配时,时输出Z达到最大,超出预先设定的门限,表示捕获成功。

很显然,数字匹配滤波器中的关键部件是乘法器和累加器,而移位寄存器可以由信号的相互移位来实现,例如要实现8bit串行数据的移位,假设输入数据序列为din,移位寄存器中的信号为d0,d1,d2,d3,d4,d5,d6,d7,用VHDL语言中的进程语句实现程序为[1]:process(clk)beginif(clk’eventandclk=‘1’)thend7<=d6;d6<=d5;d5<=d4;d4<=d3;d3<=d2;d2<=d1;d1<=d0;d0<=din;endif;endprocess;每来一个时钟信号,信号同时改变1次,这就实现了和移位寄存器相同的功能。

这样的进程实现并不需要太多的逻辑单元。

所以影响资源占用和工作效率的主要是乘法器和累加器。

下面讨论就乘法器和累加器分别加以讨论,研究其对资源和效率的影响。

3乘法器由于此处采用的是0,1的二进制系统,所以将逻辑0映射为实际电平-1,逻辑1映射为实际电平+1,也就是伪码寄存器中的系数。

移位寄存器抽头输出为有符号二进制补码,采用乘法器实现相乘运算时,如果伪码较长,则需要耗费太多的逻辑单元且运行速度过慢。

已经知道,一个数乘以1不改变原值,而乘以-1则改变符号,因为移位寄存器抽头系数只能是1和-1,可以考虑用二进制的补码运算来代替相乘1和-1运算,这就避免了相乘运算对资源的大量耗费,并能提高运算速度。

可以看到,伪码寄存器中的系数为+1或-1,如对移位抽头输出进行乘1运算,相当于不改变原补码值,而对移位抽头输出进行乘-1运算,则相当于对原补码数值改变符号,并对低位二进制码元求其补码值。

下面证明上述结论[2]。

假设二进制补码数为x=xn-1xn-2xn-3…x2x1x0(2)最高位xn-1为符号位,其取值为0或1,0代表正数,1代表负数。

不失一般性,设xn-2,xn-3,x1,x0均为1,x2到xn-4均设为0,则二进制补码数x的后n-1位代表的真值为2n-2+2n-3+21+20当最高位xn-1=0时,若移位抽头输出系数为1,则x代表的正数乘1后仍然是xn-2+2n-3+21+20,正数的补码表示还是x。

若移位抽头输出系数为-1,x代表的正数和-1相乘后变为负数,取x的后n-1位的补码值,可以表示为2n-4+2n-3+…+23+20,改变x最高位的符号位为1,取2n-4+2n-3+…+23+20的二进制表示作为x的后(n-1)位,即为x与-1相乘的补码表示;当最高位xn-1=1时,若移位抽头输出系数为1,则x代表的负数乘1后的真值仍然是x的后n-1位的补码值2n-4+2n-3+…+23+20,负数的补码表示还是x。

若移位抽头输出系数为-1,x代表的负数和-1相乘后变为正数,取x的后n-1位的补码值,可以表示为2n-4+2n-3+…+23+20,改变x最高位的符号位为0,取2n-4+2n-3+…+23+20的二进制表示作为x的后(n-1)位,即为x与-1相乘的补码表示。

结论成立,二进制求补运算代替乘法器的处理框图为如图2所示。

综上所述,在数字匹配滤波器中,因为滤波系数即移位抽头系数取值只能为1或-1,所以将有符号图2补码器的结构数的二进制补码的乘法运算变为求补码运算是完全可行的,这就避免了乘法运算对于资源的大量需求,运算速度也可大大提高。

在补码运算中,对每个移位抽头输出同时并行运算,并在后两个时钟得到并行求补码运算输出数据。

传统设计乘法器时,输入n1,n2位的2路有符号补码,结果输出为n1+n2位二进制补码数据。

随着移位寄存器输入有符号二进制补码矢量数据,时钟改变一次,移位寄存器每个抽头输出均和相应的抽头系数做一次相乘运算。

求补码运算代替乘法器时,不同于传统的乘法器设计,寄存器中每一数据只需求其补码即可,省略了相乘运算。

从根本上说,用求补代替相乘运算只是功能相同,但可以大大减少资源浪费并提高运算速度,所以有很大的应用优势。

4累加器数字匹配滤波器的移位寄存器每一级抽头进行1次乘法运算,结果输出到累加器进行累加,当运算到最后一级时,输出累加结果,送入门限判决器进行判决。

当对2个二进制补码相加时,若2个加数都为Bbit,考虑到数据可能溢出,则加法器的输出只需要(B+1)bit;而当3个bit二进制补码相加时,输出则需要(B+2)bit。

通过观察可以发现:2N个Bbit二进制补码的值可以用(B+N)bit二进制表示。

4.1传统的累加器设计考虑到传统累加器数据可能溢出,故将数据位展宽,比如在本仿真中,63个4位有符号补码求和,最后结果最多为4+6位,其中4为每一加数的位数,因为26<64,故扩展位为6位。

所以计算,如果数据位不足10位,正数在数据前加0,负数在数据前加1,这样每一数据都是10位(包括符号位),不用考虑溢出问题,完全用62个10位加法器可以实现。

4.2较优的累加器设计随着移位级数的增加,加法器的位数当然也要相应增加,第1级加法器用(B+1)位,第2、3级用(B+2)位,第4级到第7级用(B+3)位,后面依次类推。

这样设计,每一级并没有用考虑溢出结果的最多位的加法器,而是递推增加,可以减少资源浪费。

4.3优化的累加器设计将匹配滤波器的乘法器输出数据进行分组,并执行加法运算,第一级的加法器用(B+1)位,第二级用位,第三级用(B+3)位,后面依次类推。

每一级的加法器数量是前面的大约一半,依几何级数递减,这样的设计在低位相加时用了较多的加法器并以几何级数递减,也就避免了高位相加的资源浪费。

以63位m序列为例,设有符号补码数为B位:将前62位输入分为2组,每一组输入和另一组中相应输入作相加运算,总共用到31个(B+1)位加法器;余1位输入和31个(B+1)位加法器输出再次分组,用到16个(B+2)位加法器;16个(B+2)位加法器输出再次分组,用到8个(B+3)位加法器;16个(B+2)位加法器输出再次分组,用到8个(B+3)位加法器;8个(B+2)位加法器输出再次分组,用到4个(B+4)位加法器;4个(B+4)位加法器输出再次分组,用到2个(B+5)位加法器;2个(B+5)位加法器输出再次分组,用到1个(B+6)位加法器。

63位累加器占用加法器的比较如表1所示。

较优累加器的运算形式是串行,而优化累加器的运算形式是并行。

可以很明显看出,优化的累加器比较优的累加器更能减少资源占用,运行效率也可大大提高。

4.4Quatus模块化设计法Quatus仿真软件的MegaWizardPlug-InManag-er中提供了parallel_add模块,用户可以自由设计输入数据位宽,累加数据个数,定义累加输入数据类型,模块最终自动生成适当位宽的数据输出(考虑了所有的数据溢出)。

与上面的累加器设计比较,这样的设计很方便,可读性强,程序简练。

实际中逻辑单元占用也不是很多,只比上面多出10%左右。

所以,如果不是特别关注资源占用问题,这样的设计也不失为一种好方法。