一位全减器

EDA技术与Verilog_HDL(潘松)第四章课后习题答案

图4-27

1位全减器

习

题

x为被减数, y为减数, sub_in为 低位的借 位, diff r为差,su b_out为向 高位的借 位。

x 0 0 0 y 0 0 1 sub_in diffr sub_out 0 1 0 0 1 1 0 1 1

//一个二进制半减器设计进行了阐述

module h_suber(x,y,diff,s_out); input x,y; output diff, s_out; assign diff=x^y; assign s_out=(~x)&y; endmodule

reg [2:0]A ;

wire[7:0]Y ; reg G1 ,G2 ,G3;

decoder3_8 DUT ( G1 ,Y ,G2 ,A ,G3 );

initialቤተ መጻሕፍቲ ባይዱbegin $monitor($time,"A=%d,G1=%b,G2=%b, G3=%b,Y= %d\n",A, G1, G2, G3, Y); end

习

题

4-3 阻塞赋值和非阻塞赋值有何区别? 答:Verilog中,用普通等号“=”作为阻塞式赋值语句的赋值符号,如y=b。 Verilog中,用普通等号“<=”作为非阻塞式赋值语句的赋值符号,如y<=b。 阻塞式赋值的特点是,一旦执行完当前的赋值语句,赋值目标变量y即刻 获得来自等号右侧表达式的计算值。如果在一个块语句中含有多条阻塞式赋值 语句,则当执行到其中某条赋值语句时,其他语句将禁止执行,即如同被阻塞 了一样。 非阻塞式赋值的特点是必须在块语句执行结束时才整体完成赋值操作。非 阻塞的含义可以理解为在执行当前语句时,对于块中的其他语句的执行情况一 律不加限制,不加阻塞。这也可以理解为,在begin_end块中的所有赋值语句都 可以并行运行。

全加器与全减器设计

学校代码:_________学号:__________Hefei University数电设计报告NUMBER OF ELECTRICAL DESIGNREPORT设计题目:全加器与全减器设计学位类别:工学学士年级专业(班级):电子信息工程1班作者姓名:汤家映(1405011019)、宋道远(1405011020)、朱亚东(1405011022)导师姓名:谭敏完成时间: 2015-5-17目录一、设计任务 (2)1.用组合逻辑电路设计1位二进制全加器与全减器 (2)2.用双8选1数据选择器74LS151设计1位二进制全加器与全减器 (2)3.用广义译码器VHDL语言设计1位二进制全加器与全减器 (2)二、设计过程 (2)1.用组合逻辑电路设计1位二进制全加器与全减器 (2)(1)进行逻辑抽象,建立真值表 (2)(2)画出卡诺图 (2)(3)画出逻辑电路 (3)2.用双8选1数据选择器74LS151设计1位二进制全加器与全减器 (3)(1)逻辑问题进行抽象,列出真值表 (3)(2)列出函数表达关系 (4)(3)用数据选择器74LS151画出逻辑电路图 (4)3.用广义译码器VHDL语言设计1位二进制全加器与全减器 (5)三、总结 (6)一、设计任务1、用组合逻辑电路设计1位二进制全加器与全减器;2、用双8选1数据选择器74LS151设计1位二进制全加器与全减器;3、用广义译码器VHDL语言设计1位二进制全加器与全减器。

二、设计过程1、用组合逻辑电路设计1位二进制全加器与全减器(1)进行逻辑抽象,建立真值表全加器与全减器真值表输入输出A B C全加器(m=0)全减器(m=1)S D S D0 0 0 0 0 0 00 0 1 1 0 1 10 1 0 1 0 1 10 1 1 0 1 0 11 0 0 1 0 1 01 0 0 1 0 1 01 0 1 0 1 0 01 1 1 1 1 1 1(说明:当m=1时为全加器A.B分别表示被减数和减数C表示低位向高位的借位数,S表示本位和值,D表示向高位的借位;当m=0时为全加器A.B分别表示两个加数C表示低位向高位的进位数,S表示本位和值,D表示向高位的进位)(2)画出卡诺图S 的卡诺图 D 的卡诺图 BC\mA 00 01 11 10 00 0 1 1 0 01 1 0 0 1 11 0 1 1 0 10 10 0 1 全加器:m=0时,C B A S ⊕⊕=,BC AC AB BC AC ABD ∙∙=++=全减器:m=1时,C B A S ⊕⊕=,BC C A B A BC C A B A D ∙∙=++=(3)画出逻辑电路根据最简逻辑表达式画出逻辑电路图VCCAINPUT VCCBINPUT VCCCINPUT VCCmINPUT NAND2inst7NAND2inst8NAND2inst9XORinstXORinst11NAND3inst12SOUTPUT DOUTPUTXORinst132、用双8选1数据选择器74LS151设计1位二进制全加器与全减器; (1)逻辑问题进行抽象,列出真值表BC\mA 00 01 11 10 00 0 0 0 0 01 0 1 0 1 11 1 1 1 1 1011全加器与全减器真值表m A B C S D0 0 0 0 0 0000110001010001101010010010101011001011111100000100111101011101101110010110100111000111111 4(说明:当m=1时为全加器A.B分别表示被减数和减数C表示低位向高位的借位数,S表示本位和值,D表示向高位的借位当m=0时为全加器A.B分别表示两个加数C表示低位向高位的进位数,S表示本位和值,D表示向高位的进位)(2)列出函数表达关系根据上面真值表,列出逻辑函数表达式(标准与或式)S mAmBCmAm++=++++m+ACBCmABBABCBCBCACAmmABCD+++AmBCm+mAm=m+++mCBmAmABCBCBAABCCCABCBA(3)用数据选择器74LS151画出逻辑电路图根据逻辑函数的标准与或式画出逻辑电路图VCC C INPUT VCCBINPUT VCCAINPUT VCCmINPUT sOUTPUT DOUTPUT MULTIP LE XE RGNC B A D5D0D1D4D3D2D6D7Y WN74151instMULTIP LE XE RGNC B A D5D0D1D4D3D2D6D7Y WN74151inst1VCCNOTinst6GND3、用广义译码器VHDL 语言设计1位二进制全加器与全减器 根据全加器与全减器的真值表编写VHDL 程序,程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY JJ ISPORT(M,A,B,C:IN STD_LOGIC; S,D: OUT STD_LOGIC); END ENTITY JJ;ARCHITECTURE one OF JJ ISSIGNAL MABC:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINMABC<=M&A&B&C; PROCESS(MABC) BEGINCASE MABC ISWHEN"0000"=>S<='0';D<='0'; WHEN"0001"=>S<='1';D<='0'; WHEN"0010"=>S<='1';D<='0'; WHEN"0011"=>S<='0';D<='1'; WHEN"0100"=>S<='1';D<='0'; WHEN"0101"=>S<='0';D<='1'; WHEN"0110"=>S<='0';D<='1'; WHEN"0111"=>S<='1';D<='1';WHEN"1000"=>S<='0';D<='0';WHEN"1001"=>S<='1';D<='1';WHEN"1010"=>S<='1';D<='1';WHEN"1011"=>S<='0';D<='1';WHEN"1100"=>S<='1';D<='0';WHEN"1101"=>S<='0';D<='0';WHEN"1110"=>S<='0';D<='0';WHEN"1111"=>S<='1';D<='1';WHEN OTHERS=>NULL;END CASE;END PROCESS;END ARCHITECTURE one;三、总结本次关于全加器与全减器的设计是由本组三人共同合作配合完成,知道了合作完成任务的重要性。

EDA技术与Verilog_HDL(潘松)第四章课后习题答案

习

题

4-3 阻塞赋值和非阻塞赋值有何区别? 答:Verilog中,用普通等号“=”作为阻塞式赋值语句的赋值符号,如y=b。 Verilog中,用普通等号“<=”作为非阻塞式赋值语句的赋值符号,如y<=b。 阻塞式赋值的特点是,一旦执行完当前的赋值语句,赋值目标变量y即刻 获得来自等号右侧表达式的计算值。如果在一个块语句中含有多条阻塞式赋值 语句,则当执行到其中某条赋值语句时,其他语句将禁止执行,即如同被阻塞 了一样。 非阻塞式赋值的特点是必须在块语句执行结束时才整体完成赋值操作。非 阻塞的含义可以理解为在执行当前语句时,对于块中的其他语句的执行情况一 律不加限制,不加阻塞。这也可以理解为,在begin_end块中的所有赋值语句都 可以并行运行。

4-4 举例说明,为什么使用条件叙述不完整的条件句能导致产生时序模块的综合结果? 答:● 当CLK发生了电平变化,但是从1变到0。这时无论D是否变化,都将启动

过程去执行if语句;但此时CLK=0,无法执行if语句,从而无法执行赋值语句 Q<=D,于是Q只能保持原值不变(这就意味着需要在设计模块中引入存储元件)。 ● 当CLK没有发生任何变化,且CLK一直为0,而敏感信号D发生了变化。这 时也能启动过程,但由于CLK=0,无法执行if语句,从而也就无法执行赋值语句 Q<=D,导致Q只能保持原值(这也意味着需要在设计模块中引入存储元件)。 在以上两种情况中,由于if语句不满足条件,于是将跳过赋值表达式Q<=D, 不执行此赋值表达式而结束if语句和过程.对于这种语言现象,Velilog综合器解 释为,对于不满足条件,跳过赋值语句Q<=D不予执行,即意味着保持Q的原值 不变(保持前一次满足if条件时Q被更新的值)。对于数字电路来说,当输入改变后 试图保持一个值不变,就意味着使用具有存储功能的元件,就是必须引进时序元 件来保存Q中的原值,直到满足if语句的判断条件后才能更新Q中的值,于是便产 生了时序元件。 module LATCH1 (CLK, D, Q); output Q; input CLK, D; reg Q; always @(D or CLK) if(CLK)Q<=D; //当CLK=1时D被锁入Q endmodule

vhdl 四输入表决器 二位二进制乘法器 一位二进制全减器等源代码及仿真波形

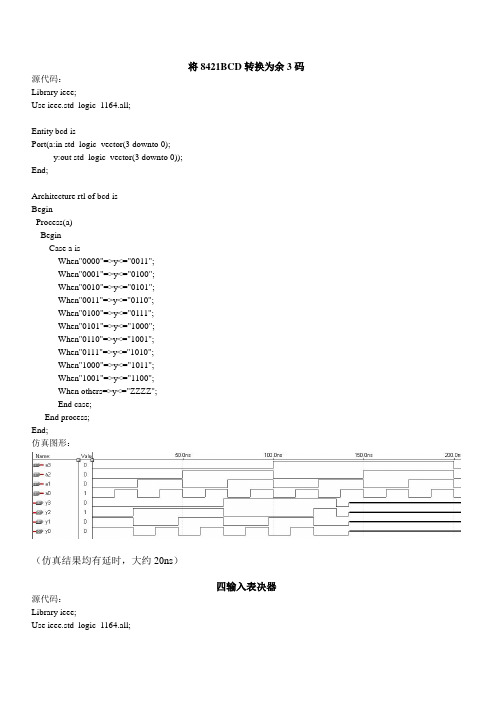

将8421BCD转换为余3码源代码:Library ieee;Use ieee.std_logic_1164.all;Entity bcd isPort(a:in std_logic_vector(3 downto 0);y:out std_logic_vector(3 downto 0));End;Architecture rtl of bcd isBeginProcess(a)BeginCase a isWhen"0000"=>y<="0011";When"0001"=>y<="0100";When"0010"=>y<="0101";When"0011"=>y<="0110";When"0100"=>y<="0111";When"0101"=>y<="1000";When"0110"=>y<="1001";When"0111"=>y<="1010";When"1000"=>y<="1011";When"1001"=>y<="1100";When others=>y<="ZZZZ";End case;End process;End;仿真图形:(仿真结果均有延时,大约20ns)四输入表决器源代码:Library ieee;Use ieee.std_logic_1164.all;Entity bjq isPort(i:in std_logic_vector(3 downto 0);f:out std_logic);End;Architecture nm2 of bjq isBeginProcess(i)Begincase i isWhen"0000"=>f<='0';When"0001"=>f<='0';When"0010"=>f<='0';When"0011"=>f<='0';When"0100"=>f<='0';When"0101"=>f<='0';When"0110"=>f<='0';When"0111"=>f<='1';When"1000"=>f<='0';When"1001"=>f<='0';When"1010"=>f<='0';When"1011"=>f<='1';When"1100"=>f<='0';When"1101"=>f<='1';When"1110"=>f<='1';When"1111"=>f<='1';When others=>f<='Z';End case;End process;End;仿真图形:2位二进制相乘电路源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity multi isport(A,B:in std_logic_vector(1 downto 0);F:out std_logic_vector(3 downto 0));end;architecture bhv of multi isbeginprocess(A,B)beginif(A="01" and B="01" )thenF<="0001";elsif(A="01" and B="10")thenF<="0010";elsif(A="01" and B="11")thenF<="0011";elsif(A="10" and B="01")thenF<="0010";elsif(A="10" and B="10")thenF<="0100";elsif(A="10" and B="11")thenF<="0110";elsif(A="11" and B="01")thenF<="0011";elsif(A="11" and B="10")thenF<="0110";elsif(A="11" and B="11")thenF<="1001";elseF<="0000";end if;end process;end;仿真图形:一位二进制全减器源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity subtracter isport(A,B,Ci:in std_logic;F,Co:out std_logic);end;architecture bhv of subtracter isbeginprocess(A,B,Ci)beginif(A='0' and B='0' and Ci='0')thenF<='0';Co<='0';elsif(A='0' and B='0' and Ci='1')thenF<='1';Co<='1';elsif(A='0' and B='1' and Ci='0')thenF<='1';Co<='1';elsif(A='0' and B='1' and Ci='1')thenF<='0';Co<='1';elsif(A='1' and B='0' and Ci='0')thenF<='1';Co<='0';elsif(A='1' and B='0' and Ci='1')thenF<='0';Co<='0';elsif(A='1' and B='1' and Ci='0')thenF<='0';Co<='0';elseF<='1';Co<='1';end if;end process;end;仿真图形:开关控制电路源代码:Library ieee;Use ieee.std_logic_1164.all;Entity switch_control isPort(a,b,c:in std_logic;y:out std_logic);End;Architecture nm5 of switch_control isBeginProcess(a,b,c);V ariable comb:std_logic_vector(2 downto 0);BeginComb:=a&b&c;Case comb isWhen"000"=>y<='0';When"001"=>y<='1';When"011"=>y<='0';When"010"=>y<='1';When"110"=>y<='0';When"111"=>y<='1';When"101"=>y<='0';When"100"=>y<='1';When others=>y<='X';End case;End process;End;仿真图形:。

一位二进制全加减器的设计

一位二进制全加减器的设计在咱们的生活中,数字无处不在,没错,不管是买东西还是算账,数字就是我们的好伙伴。

说到数字,大家一定听说过二进制。

二进制就像是数字的二重奏,只有0和1这两个小家伙,真是简单又有趣。

不过,今天我们不聊二进制的故事,而是聊聊它的一个超级英雄,二进制全加减器。

这家伙可是个了不起的角色,能够让我们轻松进行加法和减法,简直就像是厨房里的万能调料,随时随地为你解闷。

想象一下,你正在和朋友玩游戏,突然间需要计算得分,这时候二进制全加减器就像那救星般闪亮登场。

咱们先来说说加法吧。

二进制的加法其实跟咱们平常的加法差不多,不过就是多了点小规则。

比如说,0加0当然是0,0加1或者1加0就是1,1加1则会产生进位,变成0再加1,这个时候就像是变魔术一样,瞬间升华了。

把这简单的加法放在一起,嘿,整个过程简直就像是舞蹈,轻松而优雅。

再来看看减法。

哦,减法在二进制里也是大有可为。

想象一下,你手里有一块大蛋糕,想给朋友分,但是蛋糕不够,怎么办?这时候就需要用到借位的技巧。

二进制减法就像是抢夺蛋糕的小朋友,借位就是从旁边的小朋友那里借来一口,然后再继续分蛋糕。

这样看似复杂,但实际上只要理解规则,嘿,就能轻松搞定。

那好,咱们再深入一点,聊聊这个全加减器是怎么工作的。

它就像一个聪明的管家,负责所有的数字进出。

内部的结构就像一座精密的机器,采用逻辑门电路,真是科技的结晶。

这个小家伙有两部分,一部分是加法器,另一部分是减法器,它们就像两位默契的舞者,在舞台上完美配合。

每当有输入数字的时候,它们立刻就开始工作,快速而高效,仿佛时间都为它们停驻。

听到这里,大家可能会想,二进制全加减器有什么用呢?别急,咱们就来聊聊它的应用。

无论是计算机还是电子设备,都离不开这位全加减器。

想想看,咱们每天都在用手机,玩游戏,浏览网页,这些背后可都是二进制全加减器在默默奉献。

它就像一位无名英雄,虽然不显山露水,却是整个系统运作的基石。

说到这里,可能有人会觉得,哎呀,二进制这玩意儿真复杂。

全减器原理

全减器原理全减器是数字电路中常见的逻辑门电路,它用于实现两个二进制数的减法运算。

在数字电路中,全减器通常由几个半加器和一个附加的输入引脚组成,用来处理借位。

在本文中,我们将详细介绍全减器的原理和工作方式。

首先,我们来看一下全减器的基本结构。

全减器通常由三个输入引脚和两个输出引脚组成,分别是被减数A、减数B、借位输入Borrow In、差值输出Difference和借位输出Borrow Out。

全减器的原理是通过对被减数和减数进行异或运算来得到差值,同时通过对被减数、减数和借位输入进行与非运算来得到借位输出。

这样,我们就可以实现两个二进制数的减法运算。

接下来,我们来详细介绍全减器的工作原理。

首先,被减数A和减数B的每一位都分别与对应的减数B和借位输入进行异或运算,得到差值和借位输出。

然后,将这些差值和借位输出通过半加器进行处理,得到最终的差值和借位输出。

通过这样的过程,我们就可以实现两个二进制数的减法运算。

在实际应用中,全减器常常被用于数字电路中,例如在计算机的算术逻辑单元(ALU)中。

在ALU中,全减器用来处理减法运算,从而实现计算机的加减法功能。

此外,全减器还可以被用于其他数字系统中,例如在数字信号处理器(DSP)和通信系统中。

总的来说,全减器是数字电路中非常重要的逻辑门电路,它可以实现两个二进制数的减法运算。

通过对被减数和减数进行异或和与非运算,全减器可以得到差值和借位输出,从而实现减法运算。

在实际应用中,全减器被广泛应用于数字电路和计算机系统中,发挥着重要的作用。

以上就是关于全减器原理的详细介绍,希望能够对大家有所帮助。

如果对全减器原理还有疑问或者需要进一步了解,欢迎继续阅读相关资料或者咨询专业人士。

全减器用法

全减器用法全减器啊,这可是个挺有趣的小玩意儿。

你要是没接触过,就听我好好唠唠。

全减器呢,就像一个小小的数字魔法师。

它主要处理三个输入,被减数、减数还有低位来的借位信号。

这就好比三个人在进行一场特殊的拔河比赛,被减数是一边的大力士,减数是对面来挑战的,而低位来的借位信号呢,就像是旁边一个有点小捣乱但又很关键的小精灵。

咱先说这个被减数。

它就像一个拥有宝藏的主人,宝藏的数量就是它代表的数字。

减数呢,就是那个想要从被减数这里拿走宝藏的小贼。

如果没有那个低位的借位小精灵,那这个减法就像是一场普通的抢夺战,直接看被减数的宝藏够不够减数拿的就行。

比如说被减数是5,减数是3,那很简单,被减数能轻松应对,差就是2,也没有借位的情况。

可一旦那个借位小精灵出现,就像比赛突然加了个特殊规则。

比如说被减数还是5,减数是3,但是有低位来的借位信号。

这时候就相当于被减数要先拿出一份宝藏给这个小精灵,那被减数就只剩下4了,再和减数3比,差就变成1了。

这就是全减器中被减数在不同情况下的作用。

再说说减数。

减数可有点像个贪心的家伙。

它总是想着从被减数那里得到尽可能多的东西。

它的大小直接决定了和被减数之间的差距。

要是减数特别大,大到比被减数加上借位情况调整后的数还大,那就会产生借位,这个借位就像一个连锁反应,会传递到更高位去。

就像一个多米诺骨牌,一块倒了,可能会影响到后面一连串的情况。

还有那个低位来的借位信号。

这个小精灵虽然小,但是作用可大着呢。

它能改变整个减法的局面。

有时候它一出现,本来能轻松获胜的被减数就变得有点吃力了。

它就像一阵突然刮起的逆风,让原本顺利的事情变得有点波折。

全减器的输出呢,有两个,一个是差,一个是向高位的借位。

这个差就像是这场拔河比赛或者宝藏抢夺战后的结果。

而向高位的借位就像是一个信号旗,如果这个比赛或者抢夺很激烈,被减数应付不过来,这个信号旗就升起来,告诉高位的计算,这里有点情况,你们要注意啦。

我曾经自己摆弄过全减器的电路模型。

实验三 4位减法器的设计

实验三 4位减法器的设计

一、实验目的

1.利用实验二的1位全减器sub1设计一个4位全减器,掌握原理图输入法的层次化设计。

2.对设计电路仿真和硬件验证,进一步了解减法器的功能

二、实验步骤

首先,在quartu sⅡ集成环境下执行“File>Create / Update>Creat Symbol Files for Current File”命令,创建1位全减器sub1的元件符号,然后新建一个工程项目,在新的原理图文件中,调入4个sub1元件,仿照4位加法器的原理将4个元件相应端口连接起来,构成4位减法器的电路。

三、实验连线(略)

四、实验结果(自制表格,在表格中填写实验结果)

五、实验原理图及仿真图

(给出截图,包含原理图和仿真波形图记录,并描述硬件仿真的实验现象。

)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一 1位二进制全减器设计

一、实验目的

1.熟悉Quartes II集成开发软件的使用;

2.初步熟悉PH-1V型实验装置的使用;

3 . 学习用原理图输入法和文本输入法进行简单的数字电路设计,掌握系统仿真,学会分析硬件测试结果。

二、实验内容与要求

1.采用原理图输入法和文本输入法分别实现,分层设计,底层由半减器(也用原理图输入法)和逻辑门组成;

2.建立波形文件,并进行系统仿真,用软件验证设计结果;

3. 在仿真正确的情况下,对1位二进制半加/减器分别下载到实验箱中做硬件测试

三、实验原理及设计思路

根据一位二进制全减器的工作原理,可得其真值表为(如下:cin表示低位向本位借位。

cout 表示本位向高位借位)

由EDA教程中全加器的顶层设计描述及半加器调用可类比到全减器的设计,可由先对半减器进行描述,然后进行两次调用。

半减器的工作时的逻辑表达式为:so=a XOR b ;co=(NOT a)AND b 四、实验程序(程序来源:EDA技术实验教程)

LIBRARY IEEE ; ——或门逻辑描述

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY or2a IS

PORT (a, b :IN STD_LOGIC;

c : OUT STD_LOGIC );

END ENTITY or2a;

ARCHITECTURE one OF or2a IS

BEGIN

c <= a OR b ;

END ARCHITECTURE one;

LIBRARY IEEE; ——半减器描述

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_suber IS

PORT (a, b : IN STD_LOGIC;

co, so : OUT STD_LOGIC);

END ENTITY h_suber;

ARCHITECTURE fh1 OF h_suber is

BEGIN

so <= a xor b ;

co <= (not a )AND b ;

END ARCHITECTURE fh1;

LIBRARY IEEE; ——1位二进制全减器顶层设计描述

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY f_suber IS

PORT (ain,bin,cin : IN STD_LOGIC;

cout,sum : OUT STD_LOGIC );

END ENTITY f_suber;

ARCHITECTURE fd1 OF f_suber IS

COMPONENT h_suber ——调用半减器声明语句

PORT ( a,b : IN STD_LOGIC;

co,so : OUT STD_LOGIC);

END COMPONENT ;

COMPONENT or2a ——调用或门声明语句

PORT (a,b : IN STD_LOGIC;

c : OUT STD_LOGIC);

END COMPONENT;

SIGNAL d,e,f : STD_LOGIC; ——定义3个信号作为内部的连接线

BEGIN

u1 : h_suber PORT MAP(a=>ain,b=>bin,

co=>d,so=>e); ——例化语句

u2 : h_suber PORT MAP(a=>e, b=>cin,

co=>f,so=>sum);

u3 : or2a PORT MAP(a=>d, b=>f,c=>cout);

END ARCHITECTURE fd1 ;

五、实验步骤:

1.打开Quartes II软件,建立工程文件,注意工程名要与实体名一致:

2、打开QuartusII,选择菜单File->New->VHDL.File,建立vhdl文件,将以上程序输入并进行编译;

3、建立波形文件,并进行系统仿真,注意设置仿真结束时间以及添加结点;

4、输入信号波形Tools->Options->Waveform Editor,进行功能仿真Tools->Simulator Tools,在Simulator Mode选择Functional,仿真表生成后点击Start开始仿真,完成后点击Report结果如下图所示;

5、引脚锁定,及设置流程

对各管脚进行分配,将ain分配给53,bin分配给54,cin分配给55。

sum分配给208,Cout分配给206。

选择菜单Assignment->Assignment Editor->Pin 窗口,选择菜单View->Show All Knowm Pin Names 进行引脚设置:

7、用下载线将计算机并口和实验箱上的JTAG口连接起来,接通电源;选择tool->programmer 菜单,打开programmer窗口,在Mode中选择JTAG,选择好硬件设置,然后进行下载:

8、原理图输入法只需在第2步中建立Block Diagrame/Schematic File,然后输入上述原理图,选择菜单File->create symbol file for current file项,将其变成元件符号存盘,在做全减器原理图时进行调用:

半减器原理图:

全减器原理图:

六、硬件测试结果

在硬件试验箱上,按照真值表的值给出高、低电平,最后在LED8、LED7观察其亮灭情况,符合高电平亮,低电平灭的规律,表明实验成功。

通过实验结果与真值表相符,实验成功。

七、实验心得

实验前,一定要做好实验预习,写好实验报告,事前写好设计项目的VHDL设计文件.

熟悉实验箱的用法,对实验设计过程的各个步骤要做到心中有数,遇到不理解的地方,一定要向同学或老师问清楚,明确各个具体的操作步骤和详细的过程.熟悉EDA设计的完整流程.仔细思考

可能出现和已经出现的问题,独立解决.比如下载出现异常,如何处理.实验的时候出现这种情况,经过检查发现是接口有问题,更换后,能成功的下载和进行硬件测试,得到正确的结果.在此过程,做好引脚设置也是关键.。