二位全减器VHDL设计

实验四 实验名称:组合逻辑电路设计(二)—三态门、数选器、逻辑运算器

实验名称:组合逻辑电路设计(二)—三态门、数选器、逻辑运算器二、实验目的1)掌握三态门、数选器、逻辑运算器三种组合逻辑电路的设计方法,及其VHDL 描述方法。

2)掌握利用CPLD器件开发组合逻辑电路的方法。

三、实验器材PC,EDA软件四、实验原理1)示例7.5(见P195-196)示例7.6(见P197-198)示例7.7(见P198-199)2)注意事项:(1)有时程序代码虽然简单,但是占用器件资源却多;相反,有事程序代码虽然复杂,但是占用器件资源却少。

因此,不能简单地用程序代码简单还是复杂来判断程序代码的优劣,而是要对程序代码进行综合评价,才能得出比较科学的结论。

(2)Std_logic数据类型,除“0”、“1”外,还有其他值,用others穷尽所有可能的组合值。

(3)结构体“with_selece”是并行选择信号赋值语句。

与case语句相似,不允许条件重叠和涵盖不全。

要用“when others”代表其他值,以穷尽所有可能值。

(4)编程要根据要求及真值表,要考虑输入所有可能出现的情况,尽量简洁。

(5)建立功能仿真波形时,要穷尽输入信号的所有逻辑组合。

(6)下载后测试电路功能时,要验证真值表里的所有逻辑组合情况。

五、实验内容及结果(1)设计一个多数表决电路,要求:①当输入A、B、C、D有三个或三个以上为1时输出F为1;输入为其他状态时输出为0。

②写出实验内容的真值表及逻辑表达式。

③编写出实现该电路的VHDL程序。

④用MAX+plusⅡ进行仿真。

⑤将编写好的程序下载到CPLD芯片里,观察结果。

逻辑表达式:真值表:表格 1 多数表决器真值表输入输出A B C D F0 0 0 0 00 0 0 1 00 0 1 0 00 0 1 1 00 1 0 0 00 1 0 1 00 1 1 0 00 1 1 1 11 0 0 0 01 0 0 1 01 0 1 0 01 0 1 1 11 1 0 0 01 1 0 1 11 1 1 0 11 1 1 1 1 VHDL语言描述:仿真图形:(2)设计二个二位二进制数相乘电路,要求:①写出实验内容的真值表。

《EDA课程设计2位十进制四则运算电路》

《电子设计自动化》课程设计题目:2位十进制四则运算器电路院(系)信息科学与工程学院专业通信工程届别2011级班级1班学号1115102040姓名韦桂任课老师彭盛亮摘要本次课程设计主要内容是采用VHDL语言实现2位十进制数四则运算编程,用Quartus II 软件实现功能仿真,并完成硬件测试。

本次试验目的是:输入任意两个两十进制位数(0~99),选择计算模式(加减乘除),输出它们的计算结果,利用四个数码 LED 分别显示输入的两个两位数,利用四个发光二极管显示计算模式(每次只有一个二极管发光),利用另外四个数码管显示计算结果;实现方法是:将整个系统分为输入模块,计算模块和输出模块三个部分组成。

输入模块由3个脉冲键,2个复位键和2个使能端组成;计算模块分别为加法器,减法器,乘法器,除法器;输出模块通过8个数码管和4个发光二极管分别显示运算数值,运算结果和运算模式。

经过多次修改,波形仿真和硬件测试均成功。

设置两个计数器的复位键,以便于输入比较大的数之后,想进行比较小的数字的运算可以按复位键,以减少按键5或键6的次数,设置模块时,为使电路看起来更加简洁,应减少使用电路模块,如:都除以10取余时,把除数端口都连接在同一个常数端。

目录第一部分系统设计 (4)1.1设计要求: (4)1.2系统设计方案: (4)1.2.1设计总思路: (4)1.2.2实验的主要方法: (4)1.2.3电路设计: (4)1.2.4实验电路图: (4)(1)总电路 (5)(2)输入模块: (5)(3)计算模块 (5)(4)输出模块: (6)1.2.5:总体方法的论证与比较: (7)第二部分软件设计 (7)2.1软件设计平台 (7)2.2程序流程图 (7)2.3实验相关程序 (7)2.3.1clkA与clkB中需要用的100进制计数器cnt100: (7)2.3.2.四进制计数器cnt4程序: (8)2.3.3.nu15_add中需用的加法程序: (9)2.3.4.nu15_sub中需要用的减法程序: (9)2.3.5.nu15_mod程序: (10)2.4 总电路波形仿真 (11)2.5 管脚分配 (11)(1)Input: (11)(2)Output: (11)第三部分系统测试 (12)3.1 软件测试结构综合结果 (12)3.2仪器设备名称、型号 (12)3.3功能测试方法、步骤: (12)第四部分结论及收获 (13)4.1结论 (13)4.2致谢 (13)4.3 参考文献 (13)第一部分系统设计1.1设计要求:输入两个2位十进制数(0~99),输出它们的四则运算(加减乘除)结果;发光二极管显示运算模式;可调用LPM_MULT及LPM_DIVIDE模块。

二位BCD码加法器的VHDL源程序如下

二位BCD码加法器的VHDL源程序如下:ibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity bcdadd is ---------------------实体部分port(key:in std_logic;---------------定义key输入口a0,a1,b0,b1:in integer range 0 to 9; -----定义两个加数的输入口a0l,a1l,b0l,b1l,s0l,s1l,s2l:out std_logic_vector(6 downto 0);----定义七个输出数码管s:out std_logic);----定义Key指示灯输出口end;architecture one of bcdadd is ----------结构体部分signal one:integer range 0 to 18; ----定义两个数的个位相加之后的信号signal ten:integer range 0 to 19; -----定义两个数的十位相加之后的信号signal co1,co2:integer range 0 to 1; ----定义个位和十位的进位信号signal s0,s1:integer range 0 to 15;beginp1:process(one,ten,a0,b0,a1,b1,co1)----第一个进程,进行加运算beginone<=a0+b0; --------------------个位相加之和if one>9 then--------------------和大于9,进位为1co1<=1;s0<=one-10; -----------------------个位的值else -----------------------和小于9,进位为0co1<=0;s0<=one; -------------------------个位的值end if;ten<=a1+b1+co1;----------------------十位相加值和,加数包括个位来的进位if ten>9 then -------------------和大于9,进位为1co2<=1;s1<=ten-10;-------------------十位的值else ----------------------------------和小于9,进位为0co2<=0;s1<=ten;-----------------------十位的值end if;end process p1;p2:process(a0,a1,b0,b1) ----------第二个进程,两个加数的输出数码管显示译码begincase a0 is ----------------------被加数的个位显示译码when 0=>a0l<="1000000";when 1=>a0l<="1111001";when 2=>a0l<="0100100";when 3=>a0l<="0110000";when 4=>a0l<="0011001";when 5=>a0l<="0010010";when 6=>a0l<="0000010";when 7=>a0l<="1111000";when 8=>a0l<="0000000";when 9=>a0l<="0010000";when others=>a0l<="ZZZZZZZ";end case;case a1 is ------------------------------被加数的十位显示译码when 0=>a1l<="1000000";when 1=>a1l<="1111001";when 2=>a1l<="0100100";when 3=>a1l<="0110000";when 4=>a1l<="0011001";when 5=>a1l<="0010010";when 6=>a1l<="0000010";when 7=>a1l<="1111000";when 8=>a1l<="0000000";when 9=>a1l<="0010000";when others=>a1l<="ZZZZZZZ";end case;case b0 is-----------------------------加数的个位显示译码when 0=>b0l<="1000000";when 1=>b0l<="1111001";when 2=>b0l<="0100100";when 3=>b0l<="0110000";when 4=>b0l<="0011001";when 5=>b0l<="0010010";when 6=>b0l<="0000010";when 7=>b0l<="1111000";when 8=>b0l<="0000000";when 9=>b0l<="0010000";when others=>b0l<="ZZZZZZZ";end case;case b1 is ----------------------------加数的十位显示译码when 0=>b1l<="1000000";when 1=>b1l<="1111001";when 2=>b1l<="0100100";when 3=>b1l<="0110000";when 4=>b1l<="0011001";when 5=>b1l<="0010010";when 6=>b1l<="0000010";when 7=>b1l<="1111000";when 8=>b1l<="0000000";when 9=>b1l<="0010000";when others=>b1l<="ZZZZZZZ";en d case;end process p2;p3:process(key,s0,s1,co2,a0,a1,b0,b1) --------第三个进程,和的显示译码以及输入大于9是的出来beginif key='0' or a0>9 or b0>9 or a1>9 or b1>9 then --当key等于0或者两个输入中的任何一个位大于9,和的数码显示均为“Z”状态s0l<="ZZZZZZZ";s1l<="ZZZZZZZ";s2l<="ZZZZZZZ";elsecase s0 is-------------------------------和的个位显示译码when 0=>s0l<="1000000";when 1=>s0l<="1111001";when 2=>s0l<="0100100";when 3=>s0l<="0110000";when 4=>s0l<="0011001";when 5=>s0l<="0010010";when 6=>s0l<="0000010";when 7=>s0l<="1111000";when 8=>s0l<="0000000";when 9=>s0l<="0010000";when others=>s0l<="ZZZZZZZ";end case;case s1 is--------------------------------和的十位显示译码when 0=>s1l<="1000000";when 1=>s1l<="1111001";when 2=>s1l<="0100100";when 3=>s1l<="0110000";when 4=>s1l<="0011001";when 5=>s1l<="0010010";when 6=>s1l<="0000010";when 7=>s1l<="1111000";when 8=>s1l<="0000000";when 9=>s1l<="0010000";when others=>s1l<="ZZZZZZZ";end case;case co2 is --------------------------和的百位显示译码when 0=>s2l<="1000000";when 1=>s2l<="1111001";end case;end if;end process p3;p4:process(key) -------------第四个进程,设置key的指示灯begini f key='1' thens<='1' ;else s<='0';end if;end process p4;end;。

vhdl 四输入表决器 二位二进制乘法器 一位二进制全减器等源代码及仿真波形

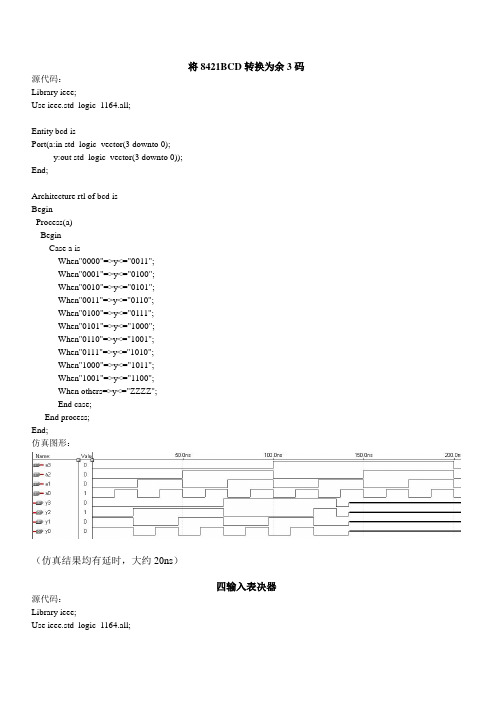

将8421BCD转换为余3码源代码:Library ieee;Use ieee.std_logic_1164.all;Entity bcd isPort(a:in std_logic_vector(3 downto 0);y:out std_logic_vector(3 downto 0));End;Architecture rtl of bcd isBeginProcess(a)BeginCase a isWhen"0000"=>y<="0011";When"0001"=>y<="0100";When"0010"=>y<="0101";When"0011"=>y<="0110";When"0100"=>y<="0111";When"0101"=>y<="1000";When"0110"=>y<="1001";When"0111"=>y<="1010";When"1000"=>y<="1011";When"1001"=>y<="1100";When others=>y<="ZZZZ";End case;End process;End;仿真图形:(仿真结果均有延时,大约20ns)四输入表决器源代码:Library ieee;Use ieee.std_logic_1164.all;Entity bjq isPort(i:in std_logic_vector(3 downto 0);f:out std_logic);End;Architecture nm2 of bjq isBeginProcess(i)Begincase i isWhen"0000"=>f<='0';When"0001"=>f<='0';When"0010"=>f<='0';When"0011"=>f<='0';When"0100"=>f<='0';When"0101"=>f<='0';When"0110"=>f<='0';When"0111"=>f<='1';When"1000"=>f<='0';When"1001"=>f<='0';When"1010"=>f<='0';When"1011"=>f<='1';When"1100"=>f<='0';When"1101"=>f<='1';When"1110"=>f<='1';When"1111"=>f<='1';When others=>f<='Z';End case;End process;End;仿真图形:2位二进制相乘电路源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity multi isport(A,B:in std_logic_vector(1 downto 0);F:out std_logic_vector(3 downto 0));end;architecture bhv of multi isbeginprocess(A,B)beginif(A="01" and B="01" )thenF<="0001";elsif(A="01" and B="10")thenF<="0010";elsif(A="01" and B="11")thenF<="0011";elsif(A="10" and B="01")thenF<="0010";elsif(A="10" and B="10")thenF<="0100";elsif(A="10" and B="11")thenF<="0110";elsif(A="11" and B="01")thenF<="0011";elsif(A="11" and B="10")thenF<="0110";elsif(A="11" and B="11")thenF<="1001";elseF<="0000";end if;end process;end;仿真图形:一位二进制全减器源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity subtracter isport(A,B,Ci:in std_logic;F,Co:out std_logic);end;architecture bhv of subtracter isbeginprocess(A,B,Ci)beginif(A='0' and B='0' and Ci='0')thenF<='0';Co<='0';elsif(A='0' and B='0' and Ci='1')thenF<='1';Co<='1';elsif(A='0' and B='1' and Ci='0')thenF<='1';Co<='1';elsif(A='0' and B='1' and Ci='1')thenF<='0';Co<='1';elsif(A='1' and B='0' and Ci='0')thenF<='1';Co<='0';elsif(A='1' and B='0' and Ci='1')thenF<='0';Co<='0';elsif(A='1' and B='1' and Ci='0')thenF<='0';Co<='0';elseF<='1';Co<='1';end if;end process;end;仿真图形:开关控制电路源代码:Library ieee;Use ieee.std_logic_1164.all;Entity switch_control isPort(a,b,c:in std_logic;y:out std_logic);End;Architecture nm5 of switch_control isBeginProcess(a,b,c);V ariable comb:std_logic_vector(2 downto 0);BeginComb:=a&b&c;Case comb isWhen"000"=>y<='0';When"001"=>y<='1';When"011"=>y<='0';When"010"=>y<='1';When"110"=>y<='0';When"111"=>y<='1';When"101"=>y<='0';When"100"=>y<='1';When others=>y<='X';End case;End process;End;仿真图形:。

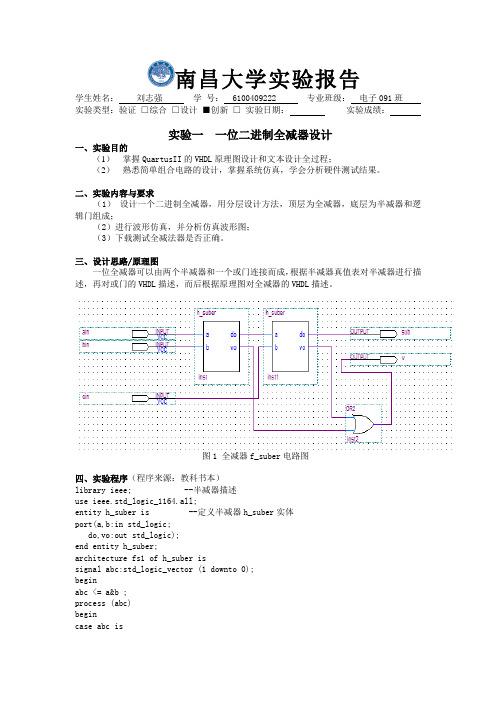

实验一:一位二进制全减器设计

南昌大学实验报告学生姓名:刘志强学号: 6100409222 专业班级:电子091班实验类型:验证□综合□设计■创新□实验日期:实验成绩:实验一一位二进制全减器设计一、实验目的(1)掌握QuartusII的VHDL原理图设计和文本设计全过程;(2)熟悉简单组合电路的设计,掌握系统仿真,学会分析硬件测试结果。

二、实验内容与要求(1)设计一个二进制全减器,用分层设计方法,顶层为全减器,底层为半减器和逻辑门组成;(2)进行波形仿真,并分析仿真波形图;(3)下载测试全减法器是否正确。

三、设计思路/原理图一位全减器可以由两个半减器和一个或门连接而成,根据半减器真值表对半减器进行描述,再对或门的VHDL描述,而后根据原理图对全减器的VHDL描述。

图1 全减器f_suber电路图四、实验程序(程序来源:教科书本)library ieee; --半减器描述use ieee.std_logic_1164.all;entity h_suber is --定义半减器h_suber实体port(a,b:in std_logic;do,vo:out std_logic);end entity h_suber;architecture fs1 of h_suber issignal abc:std_logic_vector (1 downto 0);beginabc <= a&b ;process (abc)begincase abc iswhen "00" => do<='0';vo<='0';when "01" => do<='1';vo<='1';when "10" => do<='1';vo<='0';when "11" => do<='0';vo<='0';when others => null;end case;end process;end architecture fs1;library ieee; --一位二进制全减器顶层设计描述use ieee.std_logic_1164.all;entity f_suber is --定义全减器f_suber实体port (ain,bin,cin:in std_logic;v,sub:out std_logic);end entity f_suber;architecture fs of f_suber iscomponent h_suber ---调用半减器声明语句port (a,b:in std_logic;do,vo:out std_logic);end component;component or2a --调用或逻辑门声明语句port (m,n:in std_logic;h:out std_logic);end component;signal e,f,g:std_logic; ---定义3个信号作为内部的连接线beginu1:h_suber port map(a=>ain,b=>bin,do=>e,vo=>f); ---例化语句u2:h_suber port map(a=>e,b=>cin,do=>sub,vo=>g);u3:or2a port map(m=>g,n=>f,h=>v);end architecture fs;五、实验步骤1. 利用Quartus II 7.2建立工程在file中打开【】→【】→在【】中选择存放的目录→【】f_suber要与顶层文件中entity f_suber相同→点击next→点击next→选择芯片→next完成;再在file下面点【】→【】→点击ok→编写程序→编译并保存在f_suber文件中(改动程序后,再保存,再编译)→管脚【】→【】→而后对芯片设置,即打开device→点【】→点【】与【】→选如【】与【】→选芯片→确定ok ;重新编译→点下载,后选【】硬件有“JTAG【】”和“ASP【】手动添加以扩展名为.pof的文件【】”两个接口其一(要看硬件接口),选中【】”→添加【】中的驱动程序→【】→点【】开始下载。

用VHDL结构描述设计一全减器

下面再将或门的VHDL程序描述如下:

ENTITY orgate IS PORT(A1,B1:IN BIT; O1:OUT BIT); END orgate;

ARCHITECTURE orgate_arc OF orgate IS BEGIN O1<= A1 OR B1; END orgate_arc;

下面将两个半减器,一个或门的端口,通过定义一 些中间信号将其连接起来形成VHDL的结构描述。

在下面举的全减器例子里可以看到定义了中间信号

temp_T,temp_c1和temp_c2

ENTITY fullsub IS PORT(I1,I2,C_IN:IN BIT; FT,C_OUT:OUT BIT); END fullsub; ARCHITECTURE fullsub_arc OF fullsub IS SIGNAL temp_T,temp_c1,temp_c2:BIT; COMPONENT halfsub U0 temp_T U1 PORT(A,B:IN BIT; FT I1 T,C:OUT BIT); I2 halfsub halfsub END COMPONENT; temp_c2 C_IN COMPONENT orgate PORT(A1,B1:IN BIT; temp_c1 U2 C_OUT O1:OUT BIT); END COMPONENT;

首先用VHDL的行为描述设计半减器:

ENTITY halfsub IS PORT(A,B:IN BIT; T,C:OUT BIT); END halfsub; ARCHITECTURE halfsub_arc OF halfsub IS BEGIN PROCESS(A,B) BEGIN T<= A XOR B AFTER 10 ns; C <= (NOT A) AND B AFTER 10 ns; END PROCESS; END halfsub_arc;

加法器、减法器的设计 VHDL

实验报告课程名称电子设计自动化实验(基于FPGA)实验项目加法器、减法器的设计实验仪器计算机+ Quartus Ⅱ9.1系别信息与通信工程学院专业通信工程班级/学号学生姓名实验日期2012、5成绩_______________________ 指导教师_______________________加法器、减法器的设计完成一个8位二进制带符号数的加减电路设计。

设计要求如下:通过拨码开关输入两组8位二进制数,最高位为符号位,0表示正数,1表示负数,其余位表示二进制数值。

用一按键对加、减方式进行控制,0表示加,1表示减。

输出用四位LED数码管显示BCD码。

其中LED显示器最高位为符号位。

VHDL代码LIBRARY IEEE;USE IEEE.std_logic_1164.all;USE IEEE.std_logic_arith.all;USE IEEE.std_logic_unsigned.all;ENTITY add ISPORT(a:in std_logic_vector(7 downto 0);b:in std_logic_vector(7 downto 0);ctrl:in std_logic;bcd:out std_logic_vector(15 downto 0));END ENTITY;ARCHITECTURE func OF add ISSIGNAL x:std_logic_vector(9 downto 0);SIGNAL y:std_logic_vector(9 downto 0);SIGNAL z:std_logic_vector(9 downto 0);SIGNAL c:std_logic_vector(8 downto 0);SIGNAL dec:integer;BEGINyunsuan:BLOCK --运算模块BEGINPROCESS(a)BEGINIF (a(7) = '0') THEN --判断正负x <= '0'&'0'&a;ELSEx(9 downto 8) <= '1'&'1';x(7 downto 0) <= NOT('0'&a(6 downto 0)) + 1;END IF;END PROCESS;PROCESS(a,ctrl)BEGINIF(ctrl = '0') THEN --控制键为0,则做加法IF(b(7) = '0') THENy <= '0'&'0'&b;ELSEy <= '1'&'1'&(NOT('0'&b(6 downto 0))+1);END IF;ELSEIF(b(7) = '1') THENy <= '0'&'0'&'0'&b(6 downto 0);ELSEy <= '1'&'1'&(NOT('0'&b(6 downto 0))+1);END IF;END IF;END PROCESS;PROCESS(a,b)BEGINIF(a(6 downto 0) = 0) THENz <= y;ELSE IF(b(6 downto 0) = 0) THENz <= x;ELSEz <= x + y;END IF;END IF;END PROCESS;PROCESS(z)BEGINIF(z(9) = '1') THEN --判断结果的正负c(7 downto 0) <= NOT z(7 downto 0) + 1;c(8) <= '1';ELSEc(8 downto 0) <= '0'&z(7 downto 0);END IF;END PROCESS;END BLOCK;bcdout:BLOCKBEGINdec <= CONV_INTEGER(c); --二进制转十进制PROCESS(c)BEGINCASE c(8) IS --判断最高位正负WHEN '0' => bcd(15 downto 12) <= "0000";WHEN '1' => bcd(15 downto 12) <= "0001";WHEN OTHERS => bcd(15 downto 12) <= NULL;END CASE;CASE dec/100 IS --判断百位数字WHEN 0 => bcd(11 downto 8) <= "0000";WHEN 1 => bcd(11 downto 8) <= "0001";WHEN OTHERS => bcd(11 downto 8) <= NULL;END CASE;CASE (dec REM 100)/10 ISWHEN 0 => bcd(7 downto 4) <= "0000";WHEN 1 => bcd(7 downto 4) <= "0001";WHEN 2 => bcd(7 downto 4) <= "0010";WHEN 3 => bcd(7 downto 4) <= "0011";WHEN 4 => bcd(7 downto 4) <= "0100";WHEN 5 => bcd(7 downto 4) <= "0101";WHEN 6 => bcd(7 downto 4) <= "0110";WHEN 7 => bcd(7 downto 4) <= "0111";WHEN 8 => bcd(7 downto 4) <= "1000";WHEN 9 => bcd(7 downto 4) <= "1001";WHEN OTHERS => bcd(7 downto 4) <= NULL;END CASE;CASE dec REM 10 ISWHEN 0 => bcd(3 downto 0) <= "0000";WHEN 1 => bcd(3 downto 0) <= "0001";WHEN 2 => bcd(3 downto 0) <= "0010";WHEN 3 => bcd(3 downto 0) <= "0011";WHEN 4 => bcd(3 downto 0) <= "0100";WHEN 5 => bcd(3 downto 0) <= "0101";WHEN 6 => bcd(3 downto 0) <= "0110";WHEN 7 => bcd(3 downto 0) <= "0111";WHEN 8 => bcd(3 downto 0) <= "1000";WHEN 9 => bcd(3 downto 0) <= "1001";WHEN OTHERS => bcd(3 downto 0) <= NULL;END CASE;END PROCESS;END BLOCK;END ARCHITECTURE;未下载验证、调试,如发现错误,见谅!——Higashi Q83831295。

VHDL加法器和减法器的原理

VHDL加法器和减法器的原理加法器3.2.1 加法器的原理在将两个多位二进制数相加时,除了最低位以外,每一位都应该考虑来自低位的进位,即将两个对应位的加数和来自低位的进位3个数相加。

这种运算称为全加,所用的电路称为全加器。

多位加法器的构成有两种方式:并行进位和串行进位。

并行进位加法器设有进位产生逻辑,预算速度较快;串行进位方式是将全加器级联构成多位加法器。

并行进位加法器通常比串行级联加法器占用更多的资源。

随着为数的增加,相同位数的并行加法器与串行加法器的资源占用差距也越来越大,因此,在工程中使用加法器时,要在速度和容量之间寻找平衡点。

本次设计采用的是并行加法器方式。

3.2.2 加法器要求实现的功能实现两个二进制数字的相加运算。

当到达时钟上升沿时,将两数输入,运算,输出结果。

3.2.3 加法器的VHDL语言实现(以下以12位数加16位数生成16位数的加法器为例)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_arith.ALL;ENTITY add121616 isPORT(clk : in STD_LOGIC;Din1 :in signed (11 downto 0);Din2 :in signed (15 downto 0);Dout:out signed (15 downto 0));END add121616;ARCHITECTURE a of add121616 isSIGNAL s1: signed(15 downto 0);BEGINs1<=(Din1(11)&Din1(11)&Din1(11)&Din1(11)&Din1);PROCESS(Din1,Din2,clk)BEGINif clk'event and clk='1' thenDout<=s1+Din2;end if;end process;end a;3.2.4 加法器的模块图3.2.5 加法器的波形仿真完全符合设计要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

u2 : h_suber PORT MAP(a=>e, b=>cin, co=>f,so=>sum); u3 : or2a PORT MAP(a=>d, b=>f,c=>cout); END ARCHITECTURE fd1 ; ///////////////////////////////////////////////////////////////////////////////// LIBRARY IEEE; ——二位全减器 USE IEEE.STD_LOGIC_1164.ALL; ENTITY f_2_suber IS PORT ( A,B: IN STD_LOGIC_VECTOR(1 DOWNTO 0); C0:IN STD_LOGIC; S: OUT STD_LOGIC_ VECTOR(1 DOWNTO 0); C:OUT STD_LOGIC ); END ENTITY f_2_suber; ARCHITECTURE one OF f_2_suber IS COMPONENT f_suber ——调用一位全减器声明语句 PORT (ain,bin,cin : IN STD_LOGIC; cout,sum : OUT STD_LOGIC ); END COMPONENT ; SIGNAL S1,C1,S2: STD_LOGIC; BEGIN U1: f_suber PORT MAP ( ain=>A(0),bin=>B(0),cin=>C0,cout=>C1,sum=>S1 ); U2: f_suber PORT MAP ( ain=>A(1),bin=>B(1),cin=>C1,cout=>C,sum=>S2 ); S<=S2&S1; END ARCHITECTURE one ;

1 1 1 1

0 0 1 1 表4

0 1 0 1

1 0 0 1

0 0 0 1

二位全减器:

四、实验程序(程序来源:EDA 技术实验教程)

LIBRARY IEEE ; ——或门逻辑描述 USE IEEE.STD_LOGIC_1164.ALL; ENTITY or2a IS PORT (a, b :IN STD_LOGIC; c : OUT STD_LOGIC ); END ENTITY or2a; ARCHITECTURE one OF or2a IS //可以试试不用或门定义试试 BEGIN c <= a OR b ; END ARCHITECTURE one; ////////////////////////////////////////////////////////////////// LIBRARY IEEE; ——半减器描述 USE IEEE.STD_LOGIC_1164.ALL; ENTITY h_suber IS PORT (a, b : IN STD_LOGIC; co, so : OUT STD_LOGIC); END ENTITY h_suber; ARCHITECTURE fh1 OF h_suber is BEGIN so <= a xor b ; co <= (not a )AND b ; END ARCHITECTURE fh1; //////////////////////////////////////////////////////////////////// LIBRARY IEEE; ——1 位二进制全减器顶层设计描述 USE IEEE.STD_LOGIC_1164.ALL; ENTITY f_suber IS PORT (ain,bin,cin : IN STD_LOGIC; cout,sum : OUT STD_LOGIC ); END ENTITY f_suber; ARCHITECTURE fd1 OF f_suber IS COMPONENT h_suber ——调用半减器声明语句 PORT ( a,b : IN STD_LOGIC; co,so : OUT STD_LOGIC); END COMPONENT ; COMPONENT or2a ——调用或门声明语句 PORT (a,b : IN STD_LOGIC; c : OUT STD_LOGIC); END COMPONENT; SIGNAL d,e,f : STD_LOGIC; ——定义 3 个信号作为内部的连接线 BEGIN u1 : h_suber PORT MAP(a=>ain,b=>bin, co=>d,so=>e); ——例化语句

1. 半减器原理

两个二进制数相减叫做半减,实现半减操作的电路称为半减器,表 2 为 半减器的真值表。A 为被减数,B 为减数,S 表示半减差,C 表示向高位 借位。 A B S C 0 0 0 0 0 1 1 1 1 0 1 0 1 1 0 0 从二进制数减法的角度看,真值表中只考虑了两个减数本身,没有考虑 低位来的借位,这就是半减器的由来。 S= A xor B C=(NOT A) and B

由 EDA 教程中全加器的顶层设计描述及半加器调用可类比Байду номын сангаас全减器的设计,可由先对半减 器进行描述,然后进行两次调用。半减器的工作时的逻辑表达式为:so=a XOR b ; co=(NOT a)AND b

1. 全减器原理 全减器能减数、被减数和低位来的借位信号相减,并根据求减结果给出该位 的借位信号。表 4 为全减器的真值表。Ai 表示被减数Bi 表示减数Ci −1 表示相 邻低位来的借位数,Si 表示本为和差,Ci 表示向相邻高位的借位数。 Ai Bi Ci −1 Si Ci 0 0 0 0 0 0 0 1 1 1 0 1 0 1 1 0 1 1 0 1

全减器真值表

根据一位二进制全减器的工作原理, 可得其真值表为 (如下: cin 表示低位向本位借位。 cout 表示本位向高位借位) ain 0 0 0 0 1 1 1 1 bin 0 0 1 1 0 0 1 1 cin 0 1 0 1 0 1 0 1 cout 0 1 1 1 0 0 0 1 sum 0 1 1 0 1 0 0 1