一位全减器的设计

一位全减器

实验一 1位二进制全减器设计一、实验目的1.熟悉Quartes II集成开发软件的使用;2.初步熟悉PH-1V型实验装置的使用;3 . 学习用原理图输入法和文本输入法进行简单的数字电路设计,掌握系统仿真,学会分析硬件测试结果。

二、实验内容与要求1.采用原理图输入法和文本输入法分别实现,分层设计,底层由半减器(也用原理图输入法)和逻辑门组成;2.建立波形文件,并进行系统仿真,用软件验证设计结果;3. 在仿真正确的情况下,对1位二进制半加/减器分别下载到实验箱中做硬件测试三、实验原理及设计思路根据一位二进制全减器的工作原理,可得其真值表为(如下:cin表示低位向本位借位。

cout 表示本位向高位借位)由EDA教程中全加器的顶层设计描述及半加器调用可类比到全减器的设计,可由先对半减器进行描述,然后进行两次调用。

半减器的工作时的逻辑表达式为:so=a XOR b ;co=(NOT a)AND b 四、实验程序(程序来源:EDA技术实验教程)LIBRARY IEEE ; ——或门逻辑描述USE IEEE.STD_LOGIC_1164.ALL;ENTITY or2a ISPORT (a, b :IN STD_LOGIC;c : OUT STD_LOGIC );END ENTITY or2a;ARCHITECTURE one OF or2a ISBEGINc <= a OR b ;END ARCHITECTURE one;LIBRARY IEEE; ——半减器描述USE IEEE.STD_LOGIC_1164.ALL;ENTITY h_suber ISPORT (a, b : IN STD_LOGIC;co, so : OUT STD_LOGIC);END ENTITY h_suber;ARCHITECTURE fh1 OF h_suber isBEGINso <= a xor b ;co <= (not a )AND b ;END ARCHITECTURE fh1;LIBRARY IEEE; ——1位二进制全减器顶层设计描述USE IEEE.STD_LOGIC_1164.ALL;ENTITY f_suber ISPORT (ain,bin,cin : IN STD_LOGIC;cout,sum : OUT STD_LOGIC );END ENTITY f_suber;ARCHITECTURE fd1 OF f_suber ISCOMPONENT h_suber ——调用半减器声明语句PORT ( a,b : IN STD_LOGIC;co,so : OUT STD_LOGIC);END COMPONENT ;COMPONENT or2a ——调用或门声明语句PORT (a,b : IN STD_LOGIC;c : OUT STD_LOGIC);END COMPONENT;SIGNAL d,e,f : STD_LOGIC; ——定义3个信号作为内部的连接线BEGINu1 : h_suber PORT MAP(a=>ain,b=>bin,co=>d,so=>e); ——例化语句u2 : h_suber PORT MAP(a=>e, b=>cin,co=>f,so=>sum);u3 : or2a PORT MAP(a=>d, b=>f,c=>cout);END ARCHITECTURE fd1 ;五、实验步骤:1.打开Quartes II软件,建立工程文件,注意工程名要与实体名一致:2、打开QuartusII,选择菜单File->New->VHDL.File,建立vhdl文件,将以上程序输入并进行编译;3、建立波形文件,并进行系统仿真,注意设置仿真结束时间以及添加结点;4、输入信号波形Tools->Options->Waveform Editor,进行功能仿真Tools->Simulator Tools,在Simulator Mode选择Functional,仿真表生成后点击Start开始仿真,完成后点击Report结果如下图所示;5、引脚锁定,及设置流程对各管脚进行分配,将ain分配给53,bin分配给54,cin分配给55。

全加器和全减器的设计实验报告

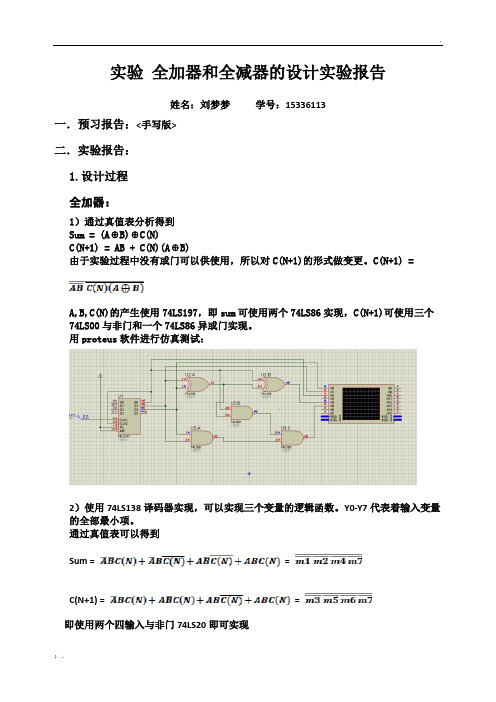

实验全加器和全减器的设计实验报告姓名:刘梦梦学号:15336113一.预习报告:<手写版>二.实验报告:1.设计过程全加器:1)通过真值表分析得到Sum = (A⊕B)⊕C(N)C(N+1) = AB + C(N)(A⊕B)由于实验过程中没有或门可以供使用,所以对C(N+1)的形式做变更。

C(N+1) =A,B,C(N)的产生使用74LS197,即sum可使用两个74LS86实现,C(N+1)可使用三个74LS00与非门和一个74LS86异或门实现。

用proteus软件进行仿真测试:2)使用74LS138译码器实现,可以实现三个变量的逻辑函数。

Y0-Y7代表着输入变量的全部最小项。

通过真值表可以得到Sum = =C(N+1) = =即使用两个四输入与非门74LS20即可实现用proteus软件进行电路仿真测试:全减器:1)通过真值表分析得到Sum = (A⊕B)⊕C(N)C(N+1) = BC(N) + (B⊕C(N))由于实验过程中没有或门可以供使用,所以对C(N+1)的形式做变更。

C(N+1) =A,B,C(N)的产生使用74LS197,即sum可使用两个74LS86实现,C(N+1)可使用三个74LS00与非门和一个74LS86异或门实现,其中的实现可以将A接入一个与非门,达到取反。

用proteus软件进行仿真测试:2)使用74LS138译码器实现,可以实现三个变量的逻辑函数。

Y0-Y7代表着输入变量的全部最小项。

通过真值表可以得到Sum = =C(N+1) ==即使用两个四输入与非门74LS20即可实现用proteus软件进行电路仿真测试:2.实验过程全加器:1)利用门电路实现。

使用74ls197构成十六进制计数器产生8421码作为A,B,C(N)的信号输入,将CP0接连续脉冲10kHz,Q0和CP1,连接,Q2,Q1,Q0分别作为A,B,C(N),将A,B接入74ls86,其输出和C(N)再一起接入74ls86,输出即为sum。

用3线8线译码器74LS138和门电路设计1位二进制全减器

1、用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号(74LS138的逻辑框图如图1.1所示)。

CO---向高位的借位; Y---两位数之差;C I ---来自低位的借位;

故:

Y=m 1+m 2+m 4+m 7;CO=m 3+m 5+m 6+m 7; 其逻辑图如下:

Y

2、试用8选1数据选择器74LS152和必要的门电路设计一个路灯控制电路,要求在四个不同的地方都能独立地开灯和关灯,画出逻辑电路图(74LS152的逻辑框图如图2.1所示)。

i i i m D A A A D A A A D Y ∑

==++⋅⋅=7001270120 图2.1 74LS152的逻辑框图

D3

D2D1

D0

Y A0A1

A2

D7

D6D5D4

74L S 152

m m m

m

其中A3,A2,A1,A0分别代表四个不同的地方;Y代表灯;1代表亮,或是开关闭合;0代表灯灭;

Y=A3(m1+m2+m4+m0)

对照着所给的逻辑表达式可得:

D0=D1=D2=D4=A3

D3=D5=D6=D7=0; A2=A2;A1=A1;A0=A0;

故逻辑图如下所示:

A3

Y

1。

用VHDL结构描述设计一全减器

下面再将或门的VHDL程序描述如下:

ENTITY orgate IS PORT(A1,B1:IN BIT; O1:OUT BIT); END orgate;

ARCHITECTURE orgate_arc OF orgate IS BEGIN O1<= A1 OR B1; END orgate_arc;

I1 I2

U0 halfsub

temp_T

ห้องสมุดไป่ตู้

U1

FT

C_OUT

BEGIN U0:halfsub PORT MAP(I1,I2,temp_T,temp_c1); U1:halfsub PORT MAP(temp_T,C_IN,FT,temp_c2); U2:orgate PORT MAP(temp_c1,temp_c2,C_OUT); END fullsub_arc; 图中虚线框各元件之间 halfsub 的连线命名。temp_T将第一 temp_c2 个半减器的差位输出连到第 C_IN 二个半减器的输入端。信号 temp_c1 temp_c1将第一个半减器的借 U2 位输出连至“或”门的一个输入 端,信号temp_c2将第二个半 减器的借位输出连至“或”门的 另一个输入端。 用三个元件调用语句定义这三个连接关系。

用VHDL结构描述设计一全减器,全减器可由两个 半减器和一个或门组成。

I1 I2 C_IN

U0 temp_T U1 FT halfsub halfsub temp_c2 temp_c1 U2 C_OUT

首先用VHDL的行为描述设计半减器:

ENTITY halfsub IS PORT(A,B:IN BIT; T,C:OUT BIT); END halfsub; ARCHITECTURE halfsub_arc OF halfsub IS BEGIN PROCESS(A,B) BEGIN T<= A XOR B AFTER 10 ns; C <= (NOT A) AND B AFTER 10 ns; END PROCESS; END halfsub_arc;

一位全减器课程设计

一位全减器课程设计一、课程目标知识目标:1. 学生能理解全减器的基本原理,掌握全减器的电路组成和功能。

2. 学生能运用所学知识,分析全减器的逻辑功能,解释全减器在实际电路中的应用。

3. 学生了解全减器与其他逻辑门的关系,能正确区分全减器与半减器的区别。

技能目标:1. 学生能运用所学知识,设计简单的全减器电路,并进行模拟验证。

2. 学生能通过实际操作,分析全减器电路的故障现象,并提出解决方案。

3. 学生具备一定的电路图识别能力,能读懂并绘制全减器电路图。

情感态度价值观目标:1. 培养学生对电子电路的兴趣,激发他们探索电子世界的热情。

2. 培养学生的团队协作精神,使他们学会在小组合作中共同解决问题。

3. 培养学生具备良好的学习习惯,树立严谨的科学态度,提高他们的自主学习能力。

课程性质:本课程为电子技术基础课程,以理论教学与实践操作相结合的方式进行。

学生特点:学生具备一定的电子技术基础知识,对全减器有一定了解,但对实际应用和电路设计尚不熟练。

教学要求:结合学生特点,注重理论与实践相结合,注重培养学生的动手操作能力和创新能力。

在教学过程中,关注学生的个体差异,因材施教,使学生在掌握全减器知识的基础上,提高综合运用能力。

通过具体的学习成果,对学生的学习效果进行评估,确保课程目标的达成。

二、教学内容1. 全减器的基本原理:包括全减器的定义、作用及其在数字电路中的应用。

- 教材章节:第三章第三节《全减器与加法器》- 内容:全减器的工作原理、逻辑表达式、真值表。

2. 全减器的电路组成:分析全减器电路的各个部分,探讨其功能及相互关系。

- 教材章节:第三章第四节《全减器电路的设计》- 内容:全减器电路的组成部分,如输入端、输出端、借位端等。

3. 全减器与其他逻辑门的关系:介绍全减器与半减器、与非门等逻辑门的联系与区别。

- 教材章节:第三章第五节《各类逻辑门的特性与应用》- 内容:全减器与其他逻辑门的功能对比,应用场景。

用74LS138和门电路设计1位二进制全减器

1、用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号(74LS138的逻辑框图如图所示)。

CO---向高位的借位; Y---两位数之差;C I ---来自低位的借位; 真值表如下:其中A 2=A 0;A 1=A 1;A 0=C I

故:

Y=m 1+m 2+m 4+m 7;CO=m 3+m 5+m 6+m 7; 其逻辑图如下:

Y

1

2、试用8选1数据选择器74LS152和必要的门电路设计一个路灯控制电路,要求在四个不同的地方都能独立地开灯和关灯,画出逻辑电路图(74LS152的逻辑框图如图所示)。

i

i i m D A A A D A A A D Y ∑==++⋅⋅=7

01270120Λ图 74LS152的逻辑框图

D3D2D1D0Y

A0A1A2D7

D6D5D474L S 152

m

m

m

m

其中A3,A2,A1,A0分别代表四个不同的地方;Y代表灯;1代表亮,或是开关闭合;0代表灯灭;Y=A3(m1+m2+m4+m0)

对照着所给的逻辑表达式可得:

D0=D1=D2=D4=A3

D3=D5=D6=D7=0; A2=A2;A1=A1;A0=A0;

故逻辑图如下所示:

A3

Y

1。

全加器全减器设计实验报告

全加器全减器设计实验报告1. 引言全加器和全减器是数字电路中常用的基本电路模块之一。

全加器用于将两个二进制数相加,全减器用于将两个二进制数相减。

在本实验中,我们将设计并实现一个4位的全加器和一个4位的全减器电路。

2. 原理2.1 全加器全加器是由两个半加器和一个或门组成的电路。

一个半加器用于计算两个输入位的和,另一个半加器用于计算进位值。

将两个半加器的结果和进位值通过或门进行运算,即可得到全加器的输出。

如下图所示为全加器的逻辑电路图:其中,A和B为输入信号,用于表示待相加的两个二进制数的对应位;S为输出信号,表示两个输入数的对应位相加的结果;C为进位信号,表示相加时产生的进位。

2.2 全减器全减器是由两个半减器和一个与非门组成的电路。

与全加器类似,一个半减器用于计算两个输入位的差,另一个半减器用于计算借位值。

将两个半减器的结果和借位值通过与非门进行运算,即可得到全减器的输出。

如下图所示为全减器的逻辑电路图:其中,A和B为输入信号,用于表示待相减的两个二进制数的对应位;D为输出信号,表示两个输入数的对应位相减的结果;B为借位信号,表示相减时需要借出的位。

3. 设计和实现3.1 全加器设计根据2.1中的原理,我们可以使用两个半加器和一个或门来实现一个4位的全加器电路。

根据全加器的逻辑电路图,我们可以将四个输入位(A0, A1, A2, A3)依次与另外四个输入位(B0, B1, B2, B3)连接到两个半加器中,然后将两个半加器的和(S0, S1, S2, S3)通过或门进行运算。

此外,计算进位值需要使用到四个位的与门(And)。

具体电路图如下:3.2 全减器设计根据2.2中的原理,我们可以使用两个半减器和一个与非门来实现一个4位的全减器电路。

根据全减器的逻辑电路图,我们可以将四个输入位(A0, A1, A2, A3)依次与另外四个输入位取反连接到两个半减器中,然后将两个半减器的差(D0, D1, D2, D3)通过与非门进行运算。

全减器实验报告

全减器实验报告

实验目的:

通过对全减器的实验操作,了解全减器的定义、功能、结构等基本知识,掌握全减器的使用方法以及相关原理,并能够进行全减器的电路设计与搭建。

实验原理:

全减器是一种数字电路,根据二进制数学原理,全减器用于将两个二进制数相减,得到差以及借位信息。

全减器的主要功能是实现两个二进制数的减法运算,但是由于差为负数时,无法实现借位,所以需要在电路中进行特殊的设计,以实现差为负数时的运算。

实验器材:

数字电路实验箱、数字万用表、全减器电路芯片、电路设计图等。

实验步骤:

1.根据实验设计图,将全减器电路芯片与其他器材连接,保证电路的正常工作。

2.将二进制数 A 和 B 分别输入到全减器中,通过电路实现 A -

B 的减法运算。

3.通过数字万用表验证电路的输入和输出是否正确,避免操作错误导致实验结果不准确。

4.在完成一次计算后,将全减器清零,准备进行下一次计算操作。

实验结果:

在实验过程中,根据实验设计图正确搭建了全减器电路,通过输入二进制数 A 和 B,实现了减法运算,并在数字万用表上验证了电路的输入和输出正确。

在清零全减器后,可以进行下一次减法计算操作。

实验结论:

通过本次实验,深入理解了全减器的概念和工作原理,掌握了全减器电路的设计和搭建方法,增强了数字电路实验的操作技能和实验能力。

总结:

数字电路作为电子工程学科的基础知识,对于电子工程师以及相关专业的学生非常重要。

本次实验不仅让我深入了解了全减器的概念和工作原理,也让我从实践中学会了电路搭建和调试的方法,同时也感受到了实验的乐趣和挑战。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA技术实用教程

课题报告

课题名称:一位全减器的设计

院系:

专业:电子信息工程

组员:

设计流程:

一、一位半减器的设计

一位半减器程序如下; 其中x,y 是输入,diff 是输出差,s_out 是借位输出, sub_in 为借位输入。

library ieee;

use ieee.std_logic_1164.all; entity h_suber is

port (x,y : in std_logic; diff,s_out : out std_logic ); end h_suber;

architecture hdlarch of h_suber is begin process(x,y) begin

diff <= x xor y;s_out <= (not x) and y; end process; end hdlarch;

半减器逻辑表达式:

半减器真值表:

输入输出

x y diff s_sout

0000

0111

1010

1100半减器波形图如下:

半减器封装图:

二、一位全减器的设计

一位全减器设计结构图:sub_in为借位输入,clk是输入延迟信号用来消除仿真图中出现的毛刺现象

一位全减器逻辑表达式:

一位全减器真值表:

一位全减器波形图:

一位全减器封装图:。