半导体器件原理-第二章

第二章-半导体分立器件

例:

后缀,以进 一步标明半 导体器件的 特性或对器 件进行进一 步的分类。

3. 二极管 半导体二极管是由一个PN结、引出线和管壳三 部分构成的。 符号:

P N

+

-

① 按照工艺结构分类

◆点接触型二极管

结构:由管心、引线和玻璃管壳组成。管心是一根 金属触须(半径约为0.1mm的钨丝或金丝)压接在 半导体晶体上,利用电形成工艺来获得PN结。

S

(f)增强型PMOS管

结电容(pF)

反向偏压(v)

④ 二极管极性的识别及测量

◆二极管极性的识别

根据标志识别:一般印有红色点一 端为正极,印有白色点一端为负极。 根据结构识别:对于玻 璃封装的点接触式二极 管,可透过玻璃外壳观 察其内部结构来区分极 性,金属丝一端为正极, 半导体晶片一端为负极。

_

+

根据正反向电阻识别: 万用表拨到R×100Ω或R×1kΩ档,测量二 极管的直流电阻。 正向电阻﹤反向电阻 用万用表测小功率二极管的直流电阻时,不 能使用R×1Ω和R×10kΩ档,因为R×1Ω档电流 很大,容易烧坏二极管,R×10kΩ档的电压较高, 容易使二极管的PN结击穿。

七、半导体分立器件 1. 分类

① 半导体二极管 普通二极管:整流二极管、检波二极管、稳压二极管 、恒流二极管、开关二极管等; 特殊二极管:肖特基势垒管(SBD)、隧道二极管( TD)、位置显示管(PIN)、变容二极管、雪崩二极 管等。

② 晶体三极管 锗管:高频小功率管、低频大功率管; 硅管:高频小功率管、超高频小功率管、高速开关管、 低噪声管、微波低噪声管; 专用器件:单结晶体管和可编程晶体管。

2S502的改进型

JEIA登记号

NPN高频晶体管

半导体物理学第二章

5 杂质的补偿作用

• 同时掺入P型和n型两种杂质,它们会相互抵消。 • 若ND>NA,则为n型半导体,n= ND-NA ; • 反之为P型,p= NA-ND。 • 其净杂质浓度称之为“有效杂质浓度”。 • 值得注意的是,当两种杂质的含量均较高且浓度基本相同

时,材料容易被误认为是“高纯半导体”,实际上,过多 的杂质含量会使半导体的性能变差,不能用于制造器件。

空位缺陷的最近邻有四个原子,每个原子有一个不成对 的电子,为不饱和的共价键,有接受电子的倾向,表现 出受主的作用。反之,间隙缺陷有四个可以失去的价电 子,表现为施主。

热缺陷产生的原因

• 系统的热平衡取决于自由能 F= U-TS。而S=klnW,设 熵是由组态变化引起。在N个原子的晶体中,有n个空位, 则排列方式为W=(N+n)!/N!n!种。

• 结论:掺磷(5价),施主,电子导电,n型半导体。

半导体的掺杂

施主:掺入在半导体中的杂质原子,能够向半导体中提供导电的电子, 并成为带正电的离子。如Si中的P 和As

ED

As

N型半导体

施主能级

EC ED

EV

3 受主杂质 受主能级

• 在硅中掺入3价的硼B,硼原子有3个价电子,与周围四个 硅原子形成共价鍵,缺少一个电子,必须从周围获得一 个电子,成为负电中心B-。

主要讨论杂质和缺陷:

杂质的影响:105个硅原子中有一个杂质硼原子,室温电 导率增加103个数量级。 缺陷的影响:硅平面器件要求位错密度控制在103cm2以下。 原因1.破坏了周期性势场; 2.在禁带中引入了杂质能级。

与理想情况的偏离的影响

• 极微量的杂质和缺陷,会对半导体材料 的物理性质和化学性质产生决定性的影 响,同时也严重影响半导体器件的质量。 – 1个B原子/ 1 0 5 个Si原子 在室温下电导率提高1 0 3 倍 – Si单晶位错密度要求低于 103cm2

复旦大学半导体器件第二章平衡载流子

重点内容

• 费米分布函数和玻尔兹曼分布函数及其适用的条件; • 施主、受主能级上电子和空穴的分布几率; • 在计算有效质量时要考虑各向异性,在计算有效状态

密度时要考虑到导带最低点的个数(硅有六个);

• 载流子浓度和中性施主、受主浓度的公式; • 均匀掺杂半导体满足电中性条件,电中性条件的公式;

• n0 p0 ni2 成立的条件;

• 虚线是本征载流子浓度,只在 本征激发区才显示出和电子浓 度可比拟的量。

• 饱和电离区是晶体管和集成电 路正常工作的温度范围。

三个区域的计算公式

• 弱电离区

1/2

n0NgcN DD expE2ckBTED

• 饱和电离区

n0 ND

• 本征激发区

n0p0ni NcNV1/2exp2E kB gT

• 电子-空穴浓度积始终满足

• 费米分布函数:在热平衡情况下,考虑到一个量子态最多只能被

一个电子占有,能量为E的单量子态被电子占有的几率为:

fe

E

exp

1

E EF kBT

1

kB是 玻 尔 兹 曼 常 数

• 一个状态要么被一个电子占有要么没有电子占有,该状态空着的

几率是:

1feEfh(E)expEkF1BTE1

费米分布函数和玻尔兹曼分布函数

• 处于费米能级相同位置的能量状态 上,电子占有的几率是1/2,费米能级

表示电子的平均填充水平。

EEF:fe

fh

1 2

• 玻尔兹曼分布函数(一个量子态可 以同时被多个电子占有)

feAexpEkT

EEF kT时费米分布近似于玻尔兹曼分布

fe(E)1exp1EkTEF

expkETF expkET

第二章半导体三极管与分立元件放大电路

IC IB

IE(1)IB

三、三极管的电流放大作用

(1)三极管的电流放大作用就是基极电流IB的微小变化控 制了集电极电流IC较大的变化。

(2)三极管放大电流时,被放大的IC是由电源VCC提供 的,并不是三极管自身生成的,放大的实质是小信号对大信 号的控制作用。

(3)三极管是一种电流控制器件。

UB

Rb 2V CC Rb1 Rb2

若电路满足I1≥(5~10)IB,UB≥(5~10)UBE由上式可知, UB由Rb1、Rb2分压而定,与温度变化基本无关。

如果温度升高使IC增大,则IE增大,发射极电位UE=IERe升 高,结果使UBE=UB-UE减小,IB相应减小,从而限制了IC的增 大,使IC基本保持不变。上述稳定工作点的过程可表示为

这个值时,放大性能下降或损坏管子。

(2)反向击穿电压(Reverse breakdown voltage) U(BR)CBO : 发射极开路时,集电极-基极之间允许施加的最高 反向电压,超过此值,集电结发生反向击穿。 U(BR)EBO : 集电极开路时,发射极-基极之间允许施加的最高反 向电压。 U(BR)CEO:基极开路时,集电极与发射极之间所能承受的最高反 向电压。为可靠工作,使用时VCC取U(BR)CEO的1/2或2/3。在输出特 性曲线中,iB=0的曲线开始急剧上翘所对应的电压即为U(BR)CEO , 其值比U(BR)CBO小。T↑,U(BR)↓。

图(b)的电路,由于C1的隔断直流作用,VCC不能通过Rb 使管子的发射结正偏即发射结零偏,因此三极管不工作在放大 区,无放大作用。

2.2.4 共射基本电路的静态工作点

一般,三极管的UBE可视为已知量,硅管│UBE│取0.7V, 锗管│UBE│取0.2V,VCC>>UBE。

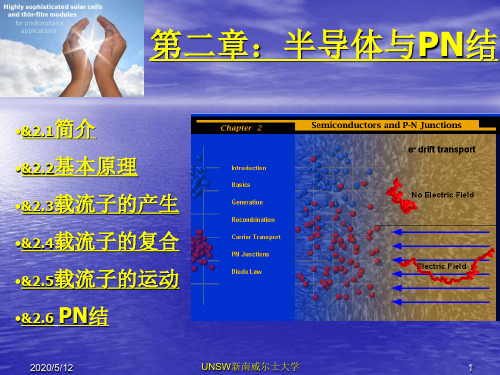

第二章-半导体与PN结

&2.3.2载流子的产生

--吸收系数

吸收系数决定着一个给定波长的光子在被吸收之前能在材料走多 远的距离。如果某种材料的吸收系数很低,那么光将很少被吸收, 并且如果材料的厚度足够薄,它就相当于透明的。吸收系数的大小 决定于材料和被吸收的光的波长。在半导体的吸收系数曲线图中出 现了一个很清晰的边缘,这是因为能量低于禁带宽度的光没有足够 的能量把电子从价带转移到导带。因此,光线也就没被吸收了。下 图显示几种半导体材料的吸收系数: 四种不同半导体才在温 度为300K时的吸收系数α, 实验在真空环境下进行。

2014-8-24

UNSW新南威尔士大学

13

&2.2.5基本原理

--平衡载流子浓度

在没有外加偏压的情况下,导带和价带中的载流子浓度就叫本征载 流子浓度。对于多子来说,其平衡载流子浓度等于本征载流子浓度 加上掺杂入半导体的自由载流子的浓度。在多数情况下,掺杂后半 导体的自由载流子浓度要比本征载流子浓度高出几个数量级,因此 多子的浓度几乎等于掺杂载流子的浓度。 在平衡状态下,多子和少子的浓度为常数,由质量作用定律可 得其数学表达式。 n0p0=n2i 式中ni表示本征载流子浓度,n0和p0分别为电子和空穴的平衡载 流子浓度。使用上面的质量作用定律,可得多子和少子的浓度:

右图是一个硅锭,由 一个大的单晶硅组成, 这样一个硅锭可以被切 割成薄片然后被制成不 同半导体器件,包括太 阳能电池和电脑芯片。

2014-8-24 UNSW新南威尔士大学 2

&2.2.1基本原理

--半导体的结构

半导体是由许多单原子组成的,它们以有规律的周期性的结构键 合在一起,然后排列成型,借此,每个原子都被8个电子包围着。 一个单原子由原子核和电子构成,原子核则包括了质子(带正电荷 的粒子)和中子(电中性的粒子),而电子则围绕在原子核周围。 电子和质子拥有相同的数量,因此一个原子的整体是显电中性的。 基于原子内的电子数目(元素周期表中的每个元素都是不同的), 每个电子都占据着特定的能级。下图展示了一种半导体的结构.

半导体器件物理学习指导:第二章 PN结

型区扩散。由电子和空穴扩散留下的未被补偿的施主和

受主离子建立了一个电场。这一电场是沿着抵消载流子扩 散趋势的方向

在热平衡时,载流子的漂移运动正好和载流子的扩散运动

相平衡,电子和空穴的扩散与漂移在N型和P型各边分别留

下未被补偿的施主离子和受主离子N d和

N

a

。结果建立了

两个电荷层即空间电荷区。

i

反偏产生电流在 P N 结反向偏压的情况下,空间电荷区 中 np ni2 。于是会载流子的产生,相应的电流即为空间电 荷区产生电流。

隧道电流:当P侧和N侧均为重掺杂的情况时,有些载流子可 能穿透(代替越过)势垒而产生电流,这种电流叫做隧道电流

产生隧道电流的条件: (1)费米能级位于导带或价带的内部; (2)空间电荷层的宽度很窄,因而有高的隧道穿透几率; (3)在相同的能量水平上在一侧的能带中有电子而在另

雪崩击穿:在N区(P区)的一个杂散空穴(电子)进入空 间电荷层,在它掠向P区(N区)的过程中,它从电场获得 动能。空穴(电子)带着高能和晶格碰撞,并从晶格中电 离出一个电子以产生一个电子空穴对。在第一次碰撞之后, 原始的和产生的载流子将继续它们的行程,并且可能发生 更多的碰撞,产生更多的载流子。结果,载流子的增加是 一个倍增过程,称为雪崩倍增或碰撞电离,由此造成的PN 结击穿叫做雪崩击穿。

Ae-wn Lp K2 = - 2sh wn - xn

Lp

(4)

Aewn Lp K1 = 2sh wn - xn

Lp

(5)

将(4)(5)代入(1):

sh wn - x

pn

-

pn0

=

pn0 (eV

VT

- 1) sh

Lp wn - xn

第二章半导体基本器件(精)

第二章半导体基本器件内容提要【了解】半导体的相关知识【熟悉】二极管(即PN结)的单向导电性及主要参数【了解】三极管的电流放大原理【熟悉】三极管输出特性曲线的三个工作区及条件和特点、主要参数【了解】MOS管的工作原理、相应的三个工作区以及与三极管的性能区别一.复习提要二.典型例题三.本章小结复习提要:*了解半导体基础相关知识:半导体(导电性能介于┉)、本征半导体(纯净,晶体)、共价键(共用电子对);热激发:自由电子-空穴对、载流子、复合、浓度(微量,温度影响) ;掺杂半导体:N型(五价磷)、P型半导体(三价硼)、多子、少子;PN结:扩散、离子、空间电荷区、内电场EIN、阻挡层、漂移、动态平衡。

(p38~p41)本征半导体掺杂半导体PN结一.PN结(二极管)的单向导电性:p41单向导电性1.PN结内部扩散和漂移的动态平衡(空间电荷区的调节作用);2.外加电压(外电场)打破原有的平衡(加正向偏压,削弱了内电场的作用,有利于扩散,形成较大的正向电流,导通;加反向偏压,增强了内电场的作用,有利于漂移,形成微弱的反向电流,截止);3.熟悉PN结的伏安特性(i~u):硅和锗的导通电压U ON分别为0.5V和0.1V、正向电压降U D分别为0.6~0.8V和0.1~0.3V,击穿电压U(RB)、二极管符号、主要参数(p43)及应用(数字:开关;模拟:整流、限幅;稳压管:正常工作在反向击穿状态,为了使稳压管不会因过流而损坏,应当在电路中加限流电阻(见图2.1.9)。

伏安特性稳压管电路*了解三极管电流放大原理:(1)发射结正偏,其正向电流主要是由发射区的多子向基区扩散所形成的电流I E(因为发射区重掺杂而基区掺杂浓度很低,故基区的多子向发射区扩散可以忽略);(2) 注入到基区的多子在基区的复合和继续扩散;(3) 复合所形成基极复合电流I BN(≈I B)很小,大部分扩散被集电结反向偏置电场吸引到集电区,形成较大的集电极收集电流I CN(≈I C)(因为基区薄、掺杂浓度低,集电结反偏)。

半导体物理 第二章 PN结 图文

国家级精品课程——半导体器件物理与实验

第二章 PN结

引言

4-4 外延工艺:

外延是一种薄膜生长工艺,外延生长是在单晶衬底上沿晶体 原来晶向向外延伸生长一层薄膜单晶层。

外延工艺可以在一种单晶材料上生长另一种单晶材料薄膜。

外延工艺可以方便地形成不同导电类型,不同杂质浓度,杂 质分布陡峭的外延层。

外延技术:汽相外延(PVD,CVD)、液相外延(LPE)、分 子束外延(MBE)、热壁外延(HWE)、原子层外延技术。

硅平面工艺的主体

国家级精品课程——半导体器件物理与实验

第二章 PN结

引言

4-1 氧化工艺:

1957年,人们发现硅表面的二氧化硅层具有阻止杂质向硅内 扩散的作用。这一发现直接导致了氧化工艺的出现。 二氧化硅薄膜的作用: (1)对杂质扩散的掩蔽作用; (2)作为MOS器件的绝缘栅材料; (3)器件表面钝化作用; (4)集成电路中的隔离介质和绝缘介质; (5)集成电路中电容器元件的绝缘介质。 硅表面二氧化硅薄膜的生长方法: 热氧化和化学气相沉积方法。

N(x) (a)

Na

Nd xj

(b) -a(x - xj)

引言

扩 SiO2 散 结 N-Si

杂质扩散

P

N-Si

N-Si

由扩散法形成的P-N结,杂质浓度从P区到N区是

逐渐变化的,通常称之为缓变结,如图所示。设 P-N结位置在x=xj处,则结中的杂质分布可表示为: x

Na Nd (x xj), Na Nd (x xj)

Al

液体

Al

P

N-Si

N-Si

N-Si

把一小粒铝放在一块N型单晶硅片上, 加热到一定温度,形成铝硅的熔融体, 然后降低温度,熔融体开始凝固,在N 型硅片上形成含有高浓度铝的P型硅薄 层,它和N型硅衬底的交界面即为P-N 结(称之为铝硅合金结)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

光刻工艺:

光刻工艺是为实现选择掺杂、形成金属电极和布线,表 面钝化等工艺而使用的一种工艺技术。

光刻工艺的基本原理是把一种称为光刻胶的高分子有机 化合物(由光敏化合物、树脂和有机溶剂组成)涂敷在 半导体晶片表面上。受特定波长光线的照射后,光刻胶 的化学结构发生变化。

如果光刻胶受光照(曝光)的区域在显影时能够除去, 称之为正性胶;反之如果光刻胶受光照的区域在显影时 被保留,未曝光的胶被除去称之为负性胶.

半导体器件原理

Principles of Semiconductor Devices

CCZU

第一章:pn结二极管

刘宪云 xyliu@

从物理到器件

引言

能带理论 统计物理

pn结二极管

肖特基二极管

双 极 晶 体 管

JFET、 MESFET、 MOSFET、

HEMT

欧姆接触

半导体器件基础 半导体器件接触的物理机制:-平衡时的能带图

硅表面二氧化硅薄膜的生长方法:热氧化和化学气相 沉积方法。

扩散工艺:由于热运动,任何物质都有一种从浓度高处向 浓度低处运动,使其趋于均匀的趋势,这种现象称为扩散。

常用扩散工艺:液态源扩散、片状源扩散、固-固扩散、双 温区锑扩散。

液态源扩散工艺:使保护气体(如氮气)通过含有扩散杂 质的液态源,从而携带杂质蒸汽进入高温扩散炉中。在高 温下杂质蒸汽分解,在硅片四周形成饱和蒸汽压,杂质原 子通过硅片表面向内部扩散。

用于集成电路制造

工艺中。PN 结面

积可大可小,用于

高频整流和开关电

路中。

13

半导体器件的特性与工作过程均与pn结有密切联系; 稳压电路和开关电路利用pn结基本特性来工作。 通过对pn结器件的分析

建立在讨论其他半导体器件时经常用到的基本术语和 概念; 分析pn结的基本技巧也适用于研究其它半导体器件;

SiO2

N Si N+

(f)腐蚀SiO2后 的晶片

•采用硅平面工艺制备结的主要工艺过程

SiO2

N Si N+

(g)完成光刻后去胶 的晶片

P Si N+

SiO2 N Si

(i)蒸发/溅射金属

金属

P Si N+

SiO2

N Si

(h)通过扩散(或离子注入) 形成 P-N结

金属

P Si

金属

N+

SiO2

N Si

(j) P-N 结制作完成

pn结二极管

电路符号

PN结+引- -线+ ++管壳=封装形成+晶(体P)二极管 -(N)

P

- - ++ - - ++

N

- - ++

D

类型:

面接触型

点接触型

平面型

PN结面积大,用于 工频大电流整流电路。

PN结面积小, 结电容小,用于 检波和变频等高 频电路。

理解和掌握pn结原理是学习半导体器件原理的关键。

14

本章学习要点:

1.pn结基本器件工艺; 2.掌握平衡状态下pn结的特性:内建电势、内建

电场及空间电荷区宽度等; 3.掌握pn结二极管的I-V特性; 4.了解pn结击穿。

第一章:pn结二极管

1.1 pn结的基本结构 1.2 pn结静态特性:平衡pn结 1.3 反偏 1.4 pn结电流 1.5 pn结的小信号模型 1.6 产生—复合电流 1.7 结击穿 1.8 隧道二极管

同质结与异质结 同型结与异型结

1、金属--半导体界面 第一个被研究的半导体器件。可作为 整流接触--肖特基势垒,或用作欧姆接 触。也可以得到其他许多器件,如 MESFET.

2、pn结

具有整流特性,广泛用于电子电路的 整流、开关及其他工作中。若再加一 p 型半导体,两个p-n 结构成 p-n-p双极 晶体管。

➢ 1950年美国人奥尔(R.Ohl)和肖克莱(Shockley) 发明的离子注入工艺。

➢ 1956年美国人富勒(C.S.Fuller)发明的扩散工艺。

➢ 1960年卢尔(H.H.Loor)和克里斯坦森 (Christenson)发明的外延工艺。

➢ 1970年斯皮勒(E.Spiller)和卡斯特兰尼 (E.Castellani)发明的光刻工艺。正是光刻工艺的 出现才使硅器件制造技术进入平面工艺技术时代, 才有大规模集成电路和微电子学飞速发展的今天。

离子注入技术: 将杂质元素的原子离化变成带电的杂质离子,在强电

场下加速,获得较高的能量(1万-100万eV)后直接轰击 到半导体基片(靶片)中,再经过退火使杂质激活,在半 导体片中形成一定的杂质分布。 离子注入技术的特点: ① 低温; ② 可精确控制浓度和结深; ③ 可选出一种元素注入,避免混入其它杂质; ④ 可在较大面积上形成薄而均匀的掺杂层; ⑤ 控制离子束的扫描区域,可实现选择注入,不需掩膜技术; ⑥ 设备昂贵。

3、异质结界面

具有两种半导体各自的pn结都不 能达到的优良光电特性

适于制作高速开关器件、太阳能 电池及半导体激光器等。

4、金属-绝缘体-半导体结构

若用氧化物代替绝缘体,可视为 M-O-S界面。 ULSL中最重要的MOSFET器件的 基本结构。

70年代以来,制备结的主要技术是硅平面工艺。硅平面 工艺包括以下主要的工艺技术:

采用硅平面工艺制备PN结的主要工艺过程

光刻胶

N Si

N+

(a)抛光处理后的 n型硅晶片

紫外光

N+

(b)采用干法或湿 法氧化工艺的晶片

氧化层制作

SiO2

N Si N+

(c)光刻胶层匀 胶及坚膜

掩模板

光刻胶 SiO2

N Si N+

(Si

N+

(e)曝光后去掉扩 散窗口胶膜的晶片

外延工艺:

外延是一种薄膜生长工艺,外延生长是在单晶衬底上 沿晶体原来晶向向外延伸生长一层薄膜单晶层。

外延工艺可以在一种单晶材料上生长另一种单晶材料 薄膜。

外延工艺可以方便地可以方便地形成不同导电类型, 不同杂质浓度,杂质分布陡峭的外延层。

外延技术:汽相外延、液相外延、分子束外延 (MBE)、热壁外延(HWE)、原子层外延技术。

上述工艺和真空镀膜技术,氧化技术加上测试,封装工 艺等构成了硅平面工艺的主体。

氧化工艺:

1957年人们发现硅表面的二氧化硅层具有阻止杂质向硅内扩 散的作用。这一发现直接导致了硅平面工艺技术的出现。

在集成电路中二氧化硅薄膜的作用主要有以下五条:

(1)对杂质扩散的掩蔽作用; (2)作为MOS器件的绝缘栅材料; (3)器件表面钝化作用; (4)集成电路中的隔离介质和绝缘介质; (5)集成电路中电容器元件的绝缘介质。