一种基于USB的高速数据采集系统硬件设计

基于USB总线的数据采集系统软件设计

1 基 于 US 的数 据 采 集 系统 B

基 于 US B总线 的数 据采 集 系统一 般 由主机 、 B US 控 制器 、 AD转换 及存 储 模块 构 成 , 基本 结 构 如 图 1 所

US B控 制器 ( y esE — B F ( Y7 6 0 3 ) ; C p s Z US X2 C C 8 1 ) 等

软 件 部 分 主 要 包 括 US B控 制 器 固件 程 序 、 B设 备 US 驱 动程 序 、 户 应用 程序 等 。 用

2 数 据 采 集 软件 系 统 设计

汪 红 童 小念

( 中南民族 大学 计算机 科 学学 院 武汉

407) 3 0 4

【 摘 要】在 现代 工 业控制 和科 学研 究过 程 中, 常需要 对数据 信 号进 行采 集 并加 以分 析 , 经 随着 总 线技 术 的发展 , US 以其 特有 的高速 、 B 方便 、 灵活 等优 势迅 速成 为 主要 的信 号传 输 总线 。在 对基 于 US 总线 的数 据采 集 系统 的 B 总体 结构进 行 综述 的基 础上 , 系统 的固件 程序 、 于 WD 的 US 对 基 M B驱 动程 序及 用 户 态应 用程 序 等软 件部 分设 计进行 了较 详 细的讨论 , 为上述 软件 部分 设计 对基 于 US 总线 系统设 计 非常关键 。 认 B

用。 ‘

换 之后 成为 数字 信 号 , 暂时保 存 在存储 器 中 , 被 然后 在 US B控制 器 的作 用下 , 过 总线 传输 到 主机 进 行后 期 通

基于USB2.0接口的高速数据采集系统设计

Absr t Thi pa r ntod e t s t tac : s pe i r uc s he ofwar a ha d a e e nd r w r de i of hi s e d t a qu ston y t m b s d sgn a gh pe d a a c i ii s s e a e on

驱 动 程序 设 计 和 应 用程 序 设 计 3部 分 组 成 。事 实证 明 , 基 于 2 0接 口 的 高速 数 据 采 集 系统 完全 满 足 设 计 和 使 用要 求 。 该 .

关键 词 : B 2 0 数 据 采 集 ; Y7 8 1 ; 件 设 计 US . ; C C6 0 3 软 中图分类号 : 347 TP 3 . 文 献标 识 码 : B 文 章 编 号 : 0 4—3 3 2 0 ) 4 6 0 10 7 X( 0 7 2 —0 9— 4

w a e de i n, rv r p o a sin a d a plc ton pr gr m e i .I s pr ve ha he s t m an a s ut l ufl t sg r s g d ie r gr m de g n p ia i o a d sgn ti o d t tt ys e c b ol e y f il hede in a s e nd u e r que t s.

基于TI5502的USB高速低功耗数据采集系统设计

王 洪武 赵 继敏 ( 上海交通大学电气工程 系, 上海 2 0 3 ) 0 0 0

摘 要

介 绍 一 种 基 于 T5 0 D P和 C 7 6 0 3 的 U B . 多通 道 高速 低 功 耗 实 时数 据 采 集 系 统 ,可 以 直接 由 笔 记 本 I5 2 S Y C 8 1A S 20

L01 e 1 I ’11 CO 1 .

一 ’

一

<

… 一 1

c

4

一

多种 触 发方 式 的数 据采 集 功 能 。 系统 具有 4个 并 行 测 量 通道 、 1

路 转 速 信号 , 且可 以根 据需 要 进 行级 联 实 现 8路 甚 至 是 1 并 6路 的通 道 。 个 测量 通 道 具 有 1 54 的采 样 频率 的 2 bt A D 单 0 .K 4 i的 / 转换 器 A S 2 1 提 供 5 k z带 宽 、 8 V C 的失 调 漂 移 以 及 D 17, 0H 1  ̄ / 1 9 B的 信 噪 比( NR 。 0d S )

1 硬 件 设计

P C

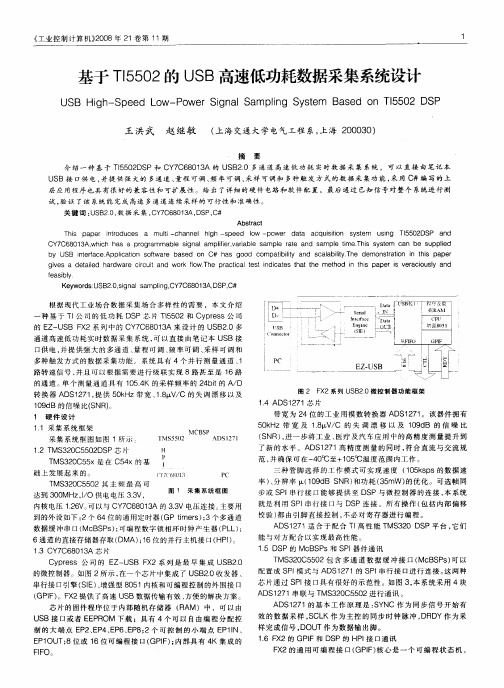

图 2 F 2系 列 US 20徽1芯 片

带宽为 2 4位 的工 业 用 模 数 转 换 器 AD 1 7 。该 器 件 拥 有 S2t M BP c S T 50 MS 52

H f7603 、 ( 81 Y P C

11 采集 系 统 框 架 ・ 采 集 系统 框 图 如 图 1所示 :

12 TM¥3 0 5 2 P芯 片 . 2 C5 0 DS

5 k z带 宽 及 18 V C 的 失 调 漂 移 以 及 1 9 B 的 信 噪 比 0H . ̄ / 0d

( N , 一 步将 工 业 、 S R) 进 医疗 及汽 车 应 用 中 的 高 精度 测 量 提 升 到 了新 的 水 平 。A S1 7 D 2 1高精 度测 量 的 同时 , 合直 流 与 交 流 规 符

一种基于USB2.0接口的高速数据采集系统的设计

Sa e lO 模 式 的时 序 。 Iv FF 其 中 , lv FF 模 式 接 口工作 时序 如 下 : Sa e IO IL : 写事 件 发 生 时 , 状 态 1 D E当 进 ;

真 , U B设 备 具 有 安装 方 便 、 插 即 用 、 带 宽 、 传 输 速 度 、 而 S 即 高 高

易 于 扩 展 等优 点 ,得 到 了更 加 广 泛 的 应用 。本 文应 用 F G 和 P A C 7 81 Y C6 0 3芯 片 设 计 一 种 基 于 U B . S 20接 口的 数 据 高 速 采 集 传输 系统 , 可广 泛 应 用 。

1 基 于 F GA 和 C 7 6 0 3芯 片 的 U B . P Y C 81 S 20接 口数 据 采 集 传 输 系统

F G n Y C 8 1 h s a e n te U B 2 n r c s o b , e w r rg ri Y C 8 1 h ( S . i P A a d C 7 6 0 3 c i ,b s d o h S . i ef e .N t lt ok e adn C 7 6 0 3 c i U B 2 n p 0 t a a yh g p 0 — tr c )i p r r d i Sa ei d ,n h IO i CY C6 0 i c nrl d b P ef e s ef me n l fo mo ea d te FF n a o v f 7 8 1 s o t l y F GA (xen lman c nrlr o c r 3 oe e tra i o t l )t a— oe

状态 1使 FF A [:1 向 I IO, : IO DR 10指 N FF 进状态 2;

状 态 2: FF 满 , 如 IO 在本 状 态 等 待 , 则 进 状 态 3 否 ;

基于USB2.0的高速高精度数据采集系统模拟电路设计

c i r c u i t , i n - d e p t h s t u d y o f t h e k e y t e c h n o l o g i e s o f d a t a a c q u i s i t i o n p r e c i s i o n , ADC c i r c u i t i s g i v e n a n d k e e p c o n v e r s i o n a c c u r a c y i n

杜 改 丽

( 河 南 职 工 医学 院 河 南 郑 州 4 5 1 1 9 1 ) 摘 要 :为 了满足 数 据 采 集 系统 对 输 入 信 号 的 高 速 高精 度 采 集 . 本 文重 点 介 绍 了模 拟 前 端 放 大 器件 选 型 以及 模 拟 前 端 信 号 调 理 电路 的设 计 , 深 入 的研 究 了影 响 数 据 采 集 精度 的 关键 技 术 . 给 出 了 AD C 电路 设 计 中提 高 和保 持 转 换精 度 的

DU Ga i — l i

( He n a n Me d i c a l f f e , 0 r S t a fa n d Wo r k s , Z h e n g z h o u 4 5 1 1 9 1 , C h i n a )

Ab s t r a c t : I n o r d e r t o s a t i s f y t h e d a t a a c q u i s i t i o n s y s t e m f o r h i g h s p e e d a n d h i g h p r e c i s i o n o f t h e i n p u t s i g n a l a c q u i s i t i o n ,t h i s p a p e r ma i n l y i n t r o d u c e s t h e a n a l o g f r o n t - e n d a mp l i f i c a t i o n d e v i c e s e l e c t i o n a n d t h e d e s i g n o f a n a l o g r f o n t - e n d s i g n a l d i s p o s a l

基于USB2.0的高速实时数据采集系统设计

US Unv ra eilB s 是 由 Co a , B( ies lS r u ) a mp q HP, — Mi

( B 接 口器件 , US ) 他完全 符合 US . B 2 0规 范 , 了具 有一 除

摘 要 : 实现 数 据 高 速 采 集 并 将 大批 量 数 据 快 速 传 输 到 P 为 C机 做 后 续 处 理 , 计 了一 种 基 于 US . 设 B2 0的 高速 实时 数 据 采 集 系统 。 介 绍 了整 个 系统 的硬 件 设 计 , 细 阐述 了 US 详 B接 口芯 片 IP 5 1的 固件 、 动 厦 应 用 程 序 开 发 。 本 系 统 设 计 已 S ]8 驱

De i n o h g p e a —tm e Da a Ac u s to y t m s d o B . sg ft e Hi h S e d Re l i t q iii n S se Ba e n US 2 0

W AN ig S Ta , AN Ha i n G P n , U o F G ou

维普资讯

《 现代 电 子技术) 0 7 第 1期 总 第 2 0期 20 年 4

测试 ・ 测量 ・自动 化 司

基于 U B20 S . 的高速实时数据采集系统设计

王 平 , 涛 , 苏 方浩俊

基于USB2.0的高速多路数据采集系统设计

控制转换 , 将各通道采样数据存人其 内部缓存。 旦转换完成 , 据转换 电路向 U B微处理器 数 S 发读采样结果信号 , S U B微处理器依次取走批量

一

数据 , 传输给 主机 , 采样数据传输 给主机时 , 在 U B微处理器持续读取采样 的结果 , S 保证了连续 高速采集数据的实时性 。

3 1 硬 件设计 .

据结果 跳转 到其 它任 意 一个 状 态 或 延迟 1~26 5 个 IC K时钟 周 期 。 当然 也 可 以根 据 输 入端 的 FL

U B控制 器 Cpes 司 F 2系列 单 片机 S yrs 公 X C 7 603与 外设有 两 种接 口方式 : 编程接 口 Y C81 可

维普资讯

第 2期 20 0 7年 6月

电

光

系

统

No 2 .

E e to i n l cr — p ia y tms l cr nc a d E e t o t lS se o c

Jn .2 0 u e 07

基于 U B . S 2 0的高速 多路 数 据 采 集 系 统 设 计

把其 中两 个 信 号 相 与 、 或 或 者相 异 或 , 相 根

实用的软硬件平 台。主机采用台式计算机, S UB 控 制器采 用 C 7 60 3 数据转 换 电路 以美信 公 Y C81 , 司的 M X 1 A 15高速 多通 道 同步 A D采 样芯 片 为 / 例, 详细说 明该 方案实 现 的过程 。

至需要整个数据采集系统能够方便携带。 目前, 能够 完成数 据采 集 的计算机 接 口包 括 : A总线 、C 总线 、34总线 、 S 、 I S PI 19 U B 红外 、 蓝 牙等。U B接 口具有较 高 的传输 速率、 S 方便连 接, 最高传输速度可达 4 0M p, 8 b s实现了真正意 义上的“ 即插 即用” 同时 U B接 口最多可 以连 , S 接 17 2 个外设 , U B接 口技术应用于数据的高 将 S 速实时采集具备一定 的优势。

基于FPGA和USB的高速数据实时采集系统的设计和实现

0 引言现代工业自动化的发展日新月异,各个领域对数据采集的质量和速度要求都在不断提高。

传统的数据采集设备多采用固定数据接口如USB、串口、网口、SPI 等,本系统中由于项目特殊需求,需要对高速IO 数据进行实时采集传输,所以不能采用传统的仅以DSP 或ARM 作为控制核心的系统设计[1]。

由于FPGA 具有时钟频率高、内部延时小、开发周期短、运算速度快、编程配置灵活、集成度高、功耗低、内部资源丰富等优点,所以本系统中加入了FPGA 芯片控制。

所以,本文设计了一种 FPGA+STM32+USB3300+上位机架构的高速IO 实时数据采集系统,当前硬件配置最高支持IO 的传输速率为30Mb/s,理论上该系统的速度仅受限于SPI实时分析处理。

1 系统原理及组成1.1 系统框架本系统总体架构如图1所示,主要包含FPGA 硬件缓冲及转换协议模块、STM32数据采集及传输模块、USB3300数据上传模块,上位机实时接收及存储模块。

1.2 系统工作原理系统上电后,用户打开上位机采集界面,启动采集,STM32收到命令以后,开始通过SPI 读取FPGA 数据;收到的数据满一包之后,STM32传输数据到USB3300芯片,该芯片通过USB 驱动上传数据给上位机,上位机监测到数据即读取芯片控制电路,STM32F407核心控制电路和USB3300传输通信电路。

FPGA 控制电路比较简单,因为其编程配置灵活,其大部分IO 口可以根据需要配置,在本系统中该芯片主要作用是IO 数据缓UARTetc. Therefore, the system is compatible with multi interface protocol, fast transmission speed, simple structure, real-time and high reliability. After many tests, it is proved that the system can be applied to high-speed data transmission and acquisition, and can meet the requirements of real-time data transmission.Keywords: FPGA ;STM32;USSB3300;USB ;multi interface protocol ;high-speed ;real-time2.2 STM32和USB3300原理图本系统中STM32及USB3300的电路设计都是采用的数据手册推荐设计,如下图3所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

理, 在设计数据采集 系统时往往应该 根据 不同场合 不同要求

要用运算放大器对信号进行调理,以满足 AD转换器的输 /

入 电平要求, 以充分利用 AD转换器 的满量程分辨 率。AD / / 转换器 是采集通道的核心, 也是影 响数据采集系统频率和精 度的主要因素。采样过程是将被测的连续信号离散化, 从连 续信号 中抽取采样 时刻的信号值 , 由多 路开 关、 采样 / 持 保 器完成。如 果被测信号变化缓慢, 也可以不用采样 / 保持器 。 多路开关将各路 信号轮流切换到输入端, 对各路信号分时采

进行放 大, 即放大器的放 大倍数可 以实 时控 制改变 。程控放

大器能够实现这个要求, 它的放大倍数 随时可以由一组数码

控制 。 这样 , 在多路开关改 变其通道序号时, 程控放大器也 由

相应的一组数码控 制改变放大倍数, 即为每个模 拟通道提供

最合适的放 大倍 数, 它的使用大大拓宽了数据 采集系统的适

地 址和中断资源的限制, 可扩展性 比较差 等。3使用 US 20 () B.

采样 / 保持器 、 大器 、 / 换器 及计 算机等组成 。数据采 放 AD转

集要经过采样和量化两个必要步骤 。

图一假设数据采集 系统 对多路模拟量进行采 集, 一般在

不要 求高速采集 的场合, 可使用公共 AD 转换器, / 用模 拟多 路开关轮流切换各路模拟量与 A D转换器之间的通道, / 使得 在一个特定 的时间内,只允许一路模 拟信号 输入 到 A D, / 从 而实现分时转换的 目的 。在模 拟信号进入 A D转 换器 前, / 需

数据 采集哪 。

1 数 据 采 集 系统

率较高 , 在输 出部分必须 附带高速 缓存, 才能实 现实 时高 速

的数据采集 。 常用的数据采集 有以下三种方法 :1 用串 / 口来进 () 使 并

1 典型数据采集系统 . 1

典型数据采集 系统 的原理如 图一所示 ,它由多路开关 、

行 。 RS 3 , 传输速率低, 如 22其 达不到系统所要求的高数据传 输速率, 也无法实现数据 的同步传输与采集 , 因此, I的速 串Z I 率远远达不到实 时要求; 并 口, 对于 虽然它的传输 速率很高 , 但布线比较复杂。() 2采用通用的高速数据采集卡 。 这些采集 卡虽然在 数据存取速度上可满足 系统要 求, 但存在 比如安装 复杂、 价格 昂贵 、 兼容 性不好 , 而且还 要受 计算 机插槽数 量 、

s n i h曲 sedd t aq it nss m. h ae kn y rs smi nu trSE - S X ei f Y C 8 1 ste i s s i p e a c usi yt T epp ra igcpes e c d co’ Z U B F 2sr so 7 6 0 3a g t h a io e t o e C h

d c r 司的 E - BF 2系列的 C C 8 1 片作为核心 芯片,主要叙述 了整个高速数据采 集 系统 的硬 件设计 ,同时将 ut 公 o ZUS X Y7 6 0 3芯 U 8连接技术 引入到测试测量 中, 制 了一套接近 实用 的便携式高速数据采集系统。通过 US 20接 口, S 研 B. 实现 了数据的实时高 d D t c u s t o y t m B s d o S e ino ad ae f r H g- pe a aA q i iin S s e a e nU B

花春飞 宁蕴绯

Hu h n e Ni gYu f i aC u fi n n e

图三 高速数据采集 系统 原理 图

22系统硬件 构成 .

( C 7 603 1 Y C 8 1 芯片 ) C 7 603 Y C 8 1 集成了以下特性: S 2 收发器 、l( UB. 0 S 串行 E

接 口引擎)和增强型 8 5 微处理器 ; 0 l 01 8 5 程序从 内部 R AM 开 始 运 行 ; 个 可 编 程 BL 4 U K/I E RU T/ NT R P IOC ・ O US端点; S H R NO 8位 1 6位外部数据 接 口;通用可编

AD / ,转换一 路信号要 受到器件特 性 、工艺水 平的限制, 因 此, 高速 AD在实 际情况下分时转换基本不可能 。由于数据 /

一 基于 c 种 ∽田的 高 速 数据 采 集 系 统 硬 件 设计

经综合考虑 ,在此选择采用 U B .接 口来完 成对数据 S2 0

的传输与采集 , 实现 了低成本, 高可 靠性, 多点 、 实时高速 的

高。U B接 口实现 了计算 机与多个外 围设备 的简单高速 互 S 联, 既省去计算机外 部过多 电缆 , 又避免 了像 P I 口那 样 C接

的插入式 接口板带来的操 作危险性 。因此, US 将 B技术应用 于数据采集非常适合【] l。 - z

保持器 、放大器 、I AD转换器及计算机 等组成。但对于高速

应面。

() 3 采样 / 保持器 在 实际系统 中用到 AD转换 时,如果模拟信号变换较 /

快, 那么 , 了保证转换 精度 , 要在 AD转换之 前加上采 为 就 / 样, 保持电路, 使得在 AD转 换期间输入的模拟信号保持不 / 变。 采样 / 持器一般 由输入缓冲放 大器 、 保 输出缓冲放大器、 保持电容和控制开关组成t 4 ] 。

Ab t c : l e mp o et ese d o aaa q iio np t e e s r eisa tn i fd t c ust , ewi rd — sr tn od rt i r v h p e fd t c us in i mci , n u t tna et o aaa ii o t t e a I o t o eh n y q i h n e

样。 / AD转换器将采样信号量化, 将转换成 的数字信号输人

到计算机中 。放 大器 、 滤波器 可根据被 测信号 的大小及干扰 的强弱选 用。有 的系统不采用公用放大器, 而根据信号特点

单独配置。

() 1多路转换模 拟开 关

模 拟开 关是数据采集系统 中主要部件之一, 它的作用是

切换各路输入信号 。为 了满足不同需要, 现己开 发出各种集

cr i, ad aeds f eh曲 ・ eddt a usi e eci d i e a t ,nrd cs et n l yo oec p h rw r ei o i s e a c it ns m id sr e ,nt ni i o ue c oo f h n g h t p a q io  ̄t s b h me me t h h t e g U

.

( 河南 城建学 院, 河南 平顶 山 4 7 4 ) 6 04

( nn i ri f bnC nt co ,H nnPn dn sa 6 0 4 Hea v syo Ura o su t n e a ig igh n 4 74 ) Un e t r i

摘

要 : 了提 高实际数据采 集的速度 , 为 保证数据采 集的实 时性 , 设计 了此高速数据采 集系统。本 文以 C pes e cn y rs mio . S

K y rs D t c usi ; 曲 一 e ; ; Y C 8 1 ; IO ewod : a A q it Hi s e U a io n pd C 7 6 0 3 FF

0 引言

通用串行接 口总 线。U B接 口是一种 重要的计算 机外设 接 S

口, 它支持热插拔和 即插 即用 , 使用非常方便 , 而且传 输速率

采用不同的结构 。 1 . 2高速数据 采集系统

前面是针对一般 AD 尤其是低速 AD 的概述 , 于高 /, / 对

速 A D 转换一路信号要受 到器件特性 、 /, 工艺水平 的限制 。 因 此, 高速 A D在 实际情况下分时转换基本不 可能 。相反 , / 由

于数据率较高 , 在输 出部分必须 附带高速缓存 , 图二 是高速 数据采集系统框 图。

在数据 采集 时, 自传感器 的模 拟信号一般都是 比较弱 来 的低电平信 号。 程控放大器的作用是将微弱输人 信号进行放

大。 以便充分利用 A D转换器的满量程分辨率 。一般 通用数 /

据采集 系统 均支持多路模拟通道, 而各通道 的模 拟信号 电压 可能有较大差异。 因此最好是对 各通道采用不 同的放 大倍数

程 接 口( I)3 V电源 系统 ; GPF; . 3 矢量 US B中断; 独立 的数据 缓冲 区供 S T P和 DA A包 控制传输 ;集 成 1C控 制器 , EU T 2

量选用表面封装器件 ,这样可 以减小元器件 之间的距离 , 减 小寄生电感 、 寄生电容, 同时减小电路板的尺寸 。 要将功能相 近 、 互间联系紧密 的元器 件放在一起 , 各连 接线长度 尽 相 使

速 采 集 , 证 了采 集 的效 率 。 保

关键词 : 数据采集 ; 高速 ; B; Y C60 3 FF US C 7 8 1 ;IO 中图分类号 :P 7 +2 T 24 . 文献标识码 : B 文章编 号:6 1 7 2(0 080 2 .3 1 7- 9 . 1).1 70 4 2

cn et ni tetsa dme u m  ̄, vl da ls rci l ot l h曲- eddt cus i s m. h 曲 U B . on ci t n a r e d e印e coe op t c r be i s e aaa it ns t T 瓜l o nh e s e e t a ap a p q io y e S 20 i e aete ytm a i e tentn n i a usi , de sr te il fc n y f e ol t . n r c, s c e s is t eydt a it a u s hg i i c o t cl ci tf h s e h v h a a t a c io n n e h q n Ie e h e o n