一种简单实用的A/D转换接口电路

A D转换电路

• 所谓采样就是将随时间连续变 化的模拟信号大小(振幅), 按一定的时间间隔采集样值, 形成在时间上不连续的脉冲序 列,这一操作叫做采样。图7-2 是采样过程示意图。

• 从图中可以看出,在tA时刻, 模拟信号在图中的A点的幅度是 5,采样的作用就是在tA时刻测 出信号幅度为5。同样的道理, 在tB时刻得到的采样值是模拟 量的7。每一个采样点,都可以 得到一个与该时刻信号振幅对 应的样本,这一对应的信号幅 度值叫做采样值,通过采样, 经将在时间上连续变化的模拟 信号变成了一列的样本值。

3,量化和编码

• 量化就是通过四舍五入的方法将采样后的模拟信号转换 为数字信号的过程。如前所述,对模拟信号采样后的信 号是一种阶梯信号,它虽然在时间轴上已经离散,但这 种阶梯信号幅值仍然是连续的,若对这种信号用二进制 数码精确表示,需要无穷多位的二进制编码,所以要采 用四舍五入的方法将每一个采样值归并到某一个临近的 整数,这样就可以用一定字长的二进制码来表示,这种 取有限个数值近似地表示某一连续变化信号的过程称为 量化。

,2,转换时间

• 转换时间是指A/D转换器从转换控制信号 到来开始,到输出端得到稳定的数字信号 所经过的时间。A/D转换器的转换时间与 转换电路的类型有关,不同类型的转换器 转换速度相差甚远。逐次比较型A/D转换 器转换时间在10μs~50μs以内,双积分 A/D转换器的转换时间大都在几十毫秒至 几百毫秒之间。

与

时钟、数据保持良好的相应关系。

引

导

• AD9883内含有PLL时钟锁相环电路,具有可编成增益、 偏置和钳位控制功能;PLL锁相环能够根据输入的 HSYNC同步信号和COAST信号产生ADC取样时钟和像 素时钟信号,时钟频率范围为12MHz~11MHz。在 HYNC行同步信号未出现时,COAST信号可维持时钟的 输出。PLL时钟产生电路框图如图7-7所示。

TLC5510中文资料

8位高速A/D转换器TLC5510中文资料2009-07-20 15:34TLC5510是美国德州仪器(TI)公司生产的8位半闪速结构模数转换器,它采用CMOS工艺制造,可提供最小20Msps的采样率。

可广泛用于数字TV。

医学图像。

视频会议。

高速数据转换以及QAM解调器等方面。

文中介绍了TLC5510的性能指标。

引脚功能。

内部结构和操作时序,给出了TLC5510的应用线路设计和参考电压的配置方法。

关键词:高速AD转换;数据采集;TLC55101概述TLC5510是美国TI公司生产的新型模数转换器件(ADC),它是一种采用CMOS工艺制造的8位高阻抗并行A/D芯片,能提供的最小采样率为20MSPS。

由于TLC5510采用了半闪速结构及CMOS工艺,因而大大减少了器件中比较器的数量,而且在高速转换的同时能够保持较低的功耗。

在推荐工作条件下,TLC5510的功耗仅为130mW。

由于TLC5510不仅具有高速的A/D转换功能,而且还带有内部采样保持电路,从而大大简化了外围电路的设计;同时,由于其内部带有了标准分压电阻,因而可以从+5V的电源获得2V满刻度的基准电压。

TLC5510可应用于数字TV。

医学图像。

视频会议。

高速数据转换以及QAM解调器等方面。

2内部结构。

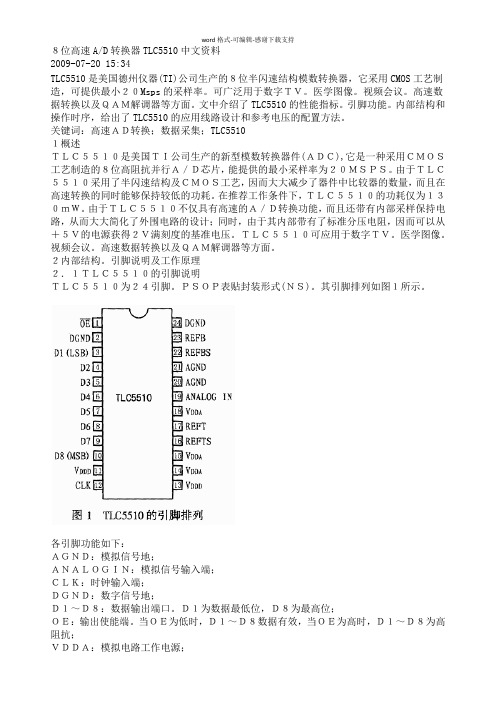

引脚说明及工作原理2.1TLC5510的引脚说明TLC5510为24引脚。

PSOP表贴封装形式(NS)。

其引脚排列如图1所示。

各引脚功能如下:AGND:模拟信号地;ANALOGIN:模拟信号输入端;CLK:时钟输入端;DGND:数字信号地;D1~D8:数据输出端口。

D1为数据最低位,D8为最高位;OE:输出使能端。

当OE为低时,D1~D8数据有效,当OE为高时,D1~D8为高阻抗;VDDA:模拟电路工作电源;VDDD:数字电路工作电源;REFTS:内部参考电压引出端之一,当使用内部电压分压器产生额定的2V基准电压时,此端短路至REFT端;REFT:参考电压引出端之二;REFB:参考电压引出端之三;REFBS:内部参考电压引出端之四,当使用内部电压基准器产生额定的2V基准电压时,此端短路至REFB端。

DA和 AD转换电路的讲解

李家虎编

20

片选

写入 1 模拟 地

数字 输入 参考电 压

电 源 输入锁 存允许

转移 控制

写入 2

数字输 入 电流输出 2

反馈 电阻 数字 地

2013-8-11

引脚图及说明

2007-5-20 李家虎编

电流输出 1

21

1)引脚说明 ILE:输入锁存选通(高电平有效),与CS组 合选通WR 。 WR :写信号1(低电平有效),用来将输入数 据送到锁存器,当WR 为高电平时,输入到锁 存器的数据被锁定。 CS:片选信号(低电平有效),同ILE组合选 通WR 。 WR :写信号2(低电平有效),与XFER组合 可以使输入到锁存器的8位数据传到D/A寄存器 中。 XFER:传送控制信号(低电平有效),它将选 通WR 。

模拟量输 出uA

图2

2013-8-11 2007-5-20 李家虎编 5

图中D是n位并行输入的数字量,uA 是输出模拟量,UREF是实现转换所 必须的参考电压。

u A KU REF

D

i 0

n 1

i

2

i

这个表达式反映了数字量与输出模 拟量的线性关系。

2013-8-11

2007-5-20

2013-8-11 2007-5-20 李家虎编 15

(6)馈送误差 馈送误差是指杂散信号通过D/A器件内部电 路耦合到输出端而造成的误差。 (7)线性误差 D/A转换的理想特征是线性的,但实际上存 在误差,模拟输出偏离理想输出的最大值 称为线性误差。 2)动态参数 (1)建立时间 输入数字从全“0”到全“1”时,建立时间 最长,因此将该时间称为建立时间。

D/A、A/D转换电路的讲解

使用一个IO口实现AD转换输入.

使用一个使用一个I/O口实现A/D转换输入文件编码:文件编码:HA0128S简介功能说明在某些特定的场合,主要是在数字电子应用方面,需要一个模拟信号输入来做一些基本的模拟量的测量或者是提供可控的方式使用外部电位器。

当然,像这样的需求,由一个内置A/D转换的MCU 就能极好地实现,但是也可以使用一些经济的外部器件,由一个标准的数字I/O口来实现一个简单的模数转换功能。

此篇应用将以HOLTEK 系列MCU 为对象,介绍如何使用标准的施密特输入口或CMOS IO 口做为基本的A/D转换口使用,为对A/D转换精度要求不高的应用提供一种超低成本的A/D转换实用方案。

这种模数转换的原理就是通过对某一电容充电达到某个固定的电压值,然后以恒定电流进行放电,我们可以通过测量放电时间来获得当前输入信号的强弱。

通过设置I/O口为输出高电平可以迅速对电容进行充电,在输出口与电容之间建议串接一个100欧姆的小电阻来限流,防止大电流损坏。

电容充电的表达公式如下:Vc = Vo (1-e-t/RC此处Vc 是电容电压,V o 是IO 口输出电压(与MCU 实际工作电压有关),将输出口置高开始对电容充电后仅需仅短时间的延时,充电电压即可达到V o 的98%,此案中需要的时间大约为39μs 。

完成充电过程后即可将控制口设置为输入状态,因为其输入状态为高阻态,此时电容就只能通过三极管的发射极对地以恒定的电流放电,电流大小与发射极上串拉的电阻有关。

改变放电电流的大小即会改变放电斜率。

1电流大小与电容电量之间的关系式如下:I = CdVdt此处C 是元件的电容,单位是法拉。

dV/dt是电容上电压变化率,单位是伏特/每秒。

I 是流过电容的电流,单位为安培。

如下图所示,如果流经电容的电流是恒定的,那么充电时电容电压上升的速率也是恒定的,实际上也就是说对电容的充放电斜坡的斜率是由电容参数值和充放电电流值决定的,电压的变化率dVdt 等于 IC 。

适用于光纤传感微弱信号检测的A/D转换芯片接口电路设计

( nt ue Lg t v e nl y B in atn i ri B in 0 0 4 C ia Is tt i i  ̄ e c oo e igJ oogUnz sy, e i 10 4 , hn ) k T h g j i  ̄ t jg

Ab t a t S r n t i e p i e s rd t c in i o sd r d b c u e o t x el n i e rt s r c : te g h f ro t s n o e e t s c n i e e e a s fi e c l tl a i b c o s e n y,h g e i a c o ih r s tn et s ee to g e i i t re e c n t e h r c e it s I r e o u i z a i u c a in ,a d f r h re h n lc r ma n t n e f r n e a d o h r c a a t rsi . n o d r t t ie i v r so c s s n u t e n a — c c l n o o cn h e st iy o h e e t n o w— o r in l e d l t n i o t n .Th / c n e trc i sf r i g t e s n ii t ft e d t c i f o p we g a d mo u a i i v o l s o s mp r a t eA D o v re h p o a we k s n l e e t n i h i e p i e sn n r g a a i a t c i t e f r t s n i g a d p o r mm a l lg cd v c t ra ecr u t e i n a e i to g d o n b o c b e o i e ie i e f c ic i d sg r r — n n d c d h d a t g s a d d s d a t g s o a i u p i n r n ls d a d s m ma i d a d a p r f t e p o u e ,t e a v n a e n ia v n a e f v r so t s a e a ay e n u o o re n a to h r —

A-D转换器

1.5 A/D转换器接口方法

2.A/D

A/D转换器接口,一般要完成以下

1) 进行通道选择。对有多个模拟量输入通道的系统,要分别选用 各模拟量输入端,以引入模拟量。对单通道模拟量输入,则不需通道寻 址。通常,模拟量通道的编号是以代码的形式从数据线上发出的,当然,

2)发转换启动信号。因为A/D转换器的转换何时开始,是由外部来 控制的,所以A/D接口的首要任务是向A/D转换器发“转换启动”控制 信号,使ADC

CLK:时钟脉冲输入端。要求时钟频率不高于640KHz。 REF(+)、REF(-):基准电压。 VCC :电源,单一+5V。 GND:地。

ADC0809的工作过程是:首先输入3位地址,并使ALE=1,将地址存入地 址锁存器中。此地址经译码选通8路模拟输入之一到比较器。START上升沿将 逐次逼近寄存器复位。下降沿启动 A/D转换,之后EOC输出信号变低,指示 转换正在进行。直到A/D转换完成,EOC变为高电平,指示A/D转换结束,结 果数据已存入锁存器,这个信号可用作中断申请。当OE输入高电平时,输出 三态门打开,转换结果的数字量输出到数据总线上。

1.2 A/D转换器的工作原理

A/D转换的方法很多,下面介绍常用的A/D转换原理。 1.计数式 这种A/D转换原理最简单直观,它由D/A转换器、计数器 和比较器组成,如图12.13所示。工作时,计数器由零开始计数, 将其计数值送往D/A转换器进行转换,将生成的模拟信号与输 入模拟信号在比较器内进行比较,若前者小于后者,则计数值加 1,重复D/A转换及比较过程。因为计数值是递增的,所以D/ A输出的模拟信号是一个逐步增加的量,当这个信号值与输出模 拟量比较相等时(在允许的误差范围内),比较器输出一个停止计 数信号给计数器,计数器立即停止计数。此时D/A转换器输出 的模拟量就为模拟输入值,计数器的值就是转换成的相应的数字 量值。 这种A/D转换器结构简单、原理清楚,但它的转换速度与精 度之间存在着严重矛盾。即若要转换速度高,则转换器输出与输 入的误差就大,反之亦然。所以在实际中很少使用它。

A-D转换器原理

A/D转换器原理

A/D 转换器原理

A/D 转换器是用来通过一定的电路将模拟量转变为数字量。

模拟量可以是电压、电流等电信号,也可以是压力、温度、湿度、位移、声音等非电信号。

但在A/D 转换前,输入到A/D 转换器的输入信号必须经各种

传感器把各种物理量转换成电压信号。

A/D 转换后,输出的数字信号可以有8 位、10 位、12 位和16 位等。

A/D 转换器的工作原理主要介绍以下三种方法:逐次逼近法双积分法电压频率转换法

(1). 逐次逼近法逐次逼近式A/D 是比较常见的一种A/D 转换电路,转换的时间为微秒级。

采用逐次逼近法的A/D 转换器是由一个比较器、D/A 转换器、缓冲寄存器及控制逻辑电路组成,如图4.21 所示。

基本原理是从高位到低位逐位试探比较,好像用天平称物体,从重到轻逐级增减砝码进行试探。

逐次逼近法

图4.21 逐次逼近式A/D 转换器原理框图逐次逼近法转换过程是:初始化时将逐次逼近寄存器各位清零;转换开始时,先将逐次逼近寄存器最高位置1,送入D/A 转换器,经D/A 转换后生成的模拟量送入比较器,称为Vo,与送入比较器的待转换的模拟量Vi 进行比较,若Vo 转换器,输出的Vo 再与Vi 比较,若Vo(2)双积分法采用双积分法的A/D 转换器由电子开关、积分器、比较器和控制逻辑等部件组成。

如图4.22 所示。

基本原理是将输入电压变换成与其平均值成正比的时间间隔,再把此时间间隔转换成数字量,属于间接转换。

双积分法。

A-D转换原理与接口

;再次启动A/D转换

RETI

;中断返回

END

C语言参考程序:

#include <reg51.h>//包含特殊功能寄存器库

#include <absacc.h>

//包含定义绝对地址访问库

#define uchar unsigned char //定义uchar为无符号字符数据

类型

#define IN0 XBYTE[0x0000] //定义IN0为通道0的地址

单片机原理与应用

A/D转换原理与接口

1.1 A/D转换器常用芯片简介 A/D转换器是将模拟信号转换为数字信号的器件,种类繁多,性能各

异。与单片机的接口形式也不尽相同,但大致分为并行接口和串行接口两 种。

1、ADC0809

ADC0809具有8路模拟量输入,可在程序控制下对任意通道进行A/D转 换,输出8位二进制数字量。与单片机之间是并行通信。其内部逻辑结构和 引脚如图8-2所示。

CLK=1; //第二个脉冲,第2、3个脉冲下降之前,DI必须分别输入两位数

据用于选择//通道,这里选通道CH0

CLK=0; //第二个脉冲下降沿

DIO=0; //DI置0,选择通道0

CLK=1; //第三个脉冲

CLK=0; //第三个脉冲下降沿

DIO=1; //第三个脉冲下降沿之后,输入端DIO失去作用,应置1

换电路(ADC0832)转换成数字量,并按顺序依次存于片内RAM的

30H~39H单元中。采样完10次后停止。

汇编语言数据采集串行A/D转换参考程序:

ORG 0000H

;

AJMP MAIN

ORG 0100H

MAIN:MOV R7,#0AH

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字码 有两种输 出方式 : 串行输 出与分 时并行输 出…。

1 1 串行输出时序 分 析 .

当 s B 、 zB 、 8 串行输 出时 序如 图 1 示。从 图 1 示 的时序 可 码 。类 似地, D 为 高 电平 时, lB 、 4B 输 出万 位 所 所

D 以看到 , 一个 完整 的测 量 周期包 括 3 阶段 : 个 自动稳零 BC 码 。 据此 , 果 单 片 机 要 接 收 I I 15分 时 输 出 的 如 C 3 7 即A Z阶段 ; 信号积分即 s 阶段 ; I 参考 电压积分即 R 阶 I

电路 的驱 动程序 。与常 见的接 口电路比较 . 具有 结构 简单 、 占用单 片机 资源 少、 执行 速度快 的特点。

关键词 : 片机 单

A D转换器 /

接 口电路

中圈分 类号 : P 3 T 35

Smpea dP at a nefc f / o vr r i l n rci l t a e D C n et c I r oA e

的时钟周期数 , 减去 10 1 数后剩余 的数。 00 个

2 硬 件接 口电 路

根据图 1所示 时序设计 的硬件接 口 电路 如 图 2所 示 。IL 15仪通过两根 IO线 与 AT 9 5 C 73 / 8C 2相接 , 仅

C 至少 要 占用 9条 io线。从读 出时间上 分析, / 段。自动 稳 零 A 阶 段 结 束 后, C 7 3 Z I L 1 5的 2 引 脚 B D码, 1 从 D 到 的 高 电平输 出要 占 用 1 0 l 0 0个 时 钟周 期, BS U Y开 始跳 变 为高 电平。在 整个 信 号 积 分 s I阶段, C 73 D 00 B Y一直维持 高 电平, US 直到参考电压积分 R 阶段 积分 I L 1 5一 个 完 整 的 A/ 转 换 需 4 0 2个 时 钟 周 I l 当选 择 时钟 频 率为 1 0 H 时 , 取 A D转换结 J 2k z 读 / 回零后再经过 1 时钟周 期为 止, U Y重 新恢 复为 低 期l , 个 BS

Yu Zho g Li i n de nM n

Da t fAuo E g , l 1 l t fLg tId , l [ 1 6 3 p .0 t n Da 1 o ih n . Dai 1 1 0 4  ̄[ I s a A sr c : eh r wa'itr c fAT8 ei igec i cmp trwihA/ C n etrI 7 3 n h rvn b ta tTh ad / ne a eo e l 9 8r  ̄s l hp o u e t D o v re CL 1 5a dt ed iig e n

时所经 历 的 时 钟 周 期, 所 记 录 的 时 钟 周 期 数 减 去 将 10 1 0 0 后就 是 A D转换的 数字码 。 / 1 2 分时 并行 输 出时 序分析 . 在分 时 并 行 输 出 时 序 里 , A D 转 换 后 的 数 字 经 / 码, 通过 D 、 2D 、 4D 、 lB 、 、 8 。I 、 ,D 、 sB 、 2 B 管脚 分 时 ) 9个 输 出。当 D 为高 电平 时, lB 、 、 8 出个 位 B D l B 、2岛 B 输 C

s f a e l t t di sp p r ti s l tu t r ,l t c u y n e o i ot r esa e t a e I i ei sr c u e i l i o c p ig r s u ̄ w a n h i s mp n te n e e u ig c mp r t  ̄n e ir n . x c t o a ewi n h vm n M o e o ig ec i o 4 p t r n a t n fs l h p 3 a u e ,a d fs n 3 i

维普资讯

3 8

仪 表技 术 与 传 感 器

20 正 02

一

种 简单 实 用 的 A D转换 接 口电路 /

于忠得 林 敏 163 104 大连轻 L 业学院 自动化 系 大连 市

【 摘要】 提出了一种 A 8 T 9系列单片机与 4 / 位 A D转换器 IL 1 5的接口电路, 12 / C 73 给出了该

果 的时 间为 J :

10 / 2 0 0 8 3 , 0 0 1 0 0  ̄ . ms

对于 一个 实时 系 统 来讲 , 个 读 取 时 间是 足 够 长 这

的。

根据 以上 的分析 , 据图 1所 示 的 串行 输 出 时序 根

应是最 佳的接 口电路 。 就是 在 B Y信号为高 电平时, US 用计 数器记录 下所经过 设 计的接 口电路 ,

电平 。如果将 B Y信号 与时钟 输入信号 进行逻辑 与, US 那么, B S 在 U Y信 号 为 高 电平时 所记 录 下 的 时钟 周期 数, 将包括两 部分 的信 息 : 信号 积分 阶段 所 占用 的固定 的 100个时钟周期, 00 与模拟输 入信号 线性对 应的时钟

周期数, 再加上 1 。由此可见 , A D转换 后 的数字码 , 经 /

பைடு நூலகம்

Ke rs Sn l C p C mp tr A D C n e e ; tr c yWo d :ige h o ue ; / o vr r I el e i t n a

l I L 15输 出 时 序 分 析 C 73

I I 1 5是 4/ C. 3 7 ‘2位双 向积分 式 A/ D转 换器 , 格 价 便宜 , 性能优 良, 国内智能仪表设 计 中经 常采 用 的一 是 种 A D转 换 器。 模 拟 信 号 经 I L 1 5 / 转 换 后 的 / c 73A D