仿真波形图

matlab-simlink仿真波形画图技巧

相信很多同学,特别是硕士和博士同学在写期刊论文或学位论文时需要使用matlab/simulink仿真,而且需要将波形导出来写入论文。

本文将介绍一种导出波形的方法,不一定是最快捷的,但是一定能够达到清晰的效果。

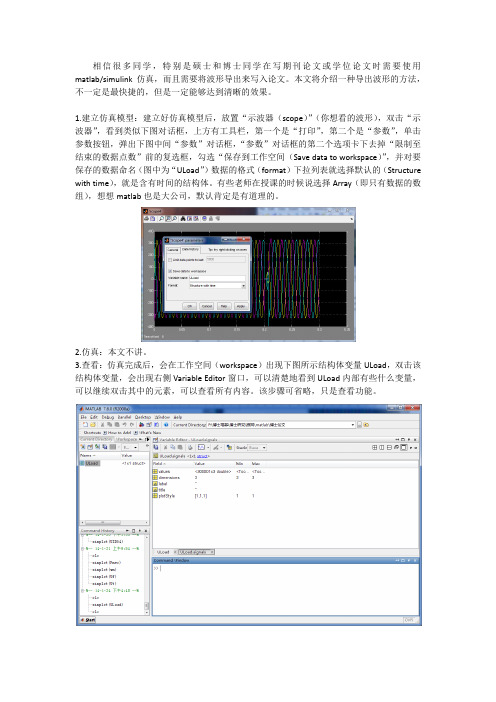

1.建立仿真模型:建立好仿真模型后,放置“示波器(scope)”(你想看的波形),双击“示波器”,看到类似下图对话框,上方有工具栏,第一个是“打印”,第二个是“参数”,单击参数按钮,弹出下图中间“参数”对话框,“参数”对话框的第二个选项卡下去掉“限制至结束的数据点数”前的复选框,勾选“保存到工作空间(Save data to workspace)”,并对要保存的数据命名(图中为“ULoad”)数据的格式(format)下拉列表就选择默认的(Structure with time),就是含有时间的结构体。

有些老师在授课的时候说选择Array(即只有数据的数组),想想matlab也是大公司,默认肯定是有道理的。

2.仿真:本文不讲。

3.查看:仿真完成后,会在工作空间(workspace)出现下图所示结构体变量ULoad,双击该结构体变量,会出现右侧Variable Editor窗口,可以清楚地看到ULoad内部有些什么变量,可以继续双击其中的元素,可以查看所有内容。

该步骤可省略,只是查看功能。

4.画图:这是关键的一步,请用simplot函数,而不是plot函数,而simplot函数对应的变量形式就是“Structure with time”,也就是说matlab公司希望用户直接用这个函数。

例如:simplot(ULoad);出现下图所示与示波器一模一样的图形。

单击工具栏“属性”按钮,如图中红色圆圈中所示。

5.属性编辑:这一步也很重要,单击属性按钮后,如下图所示属性面板好像啥也没有,不捉急,你想修改什么就单击什么,比如背景肯定不希望是黑色的吧,单击背景,或者坐标轴(因为背景和坐标是属于坐标轴的),如下图所示左下方红色框内改变背景填充色和网各色,也可以去掉网格,左上方为添加标题,中间为xy坐标范围和标签,后面都有个Ticks按钮,还有more properties按钮,点开看看呗。

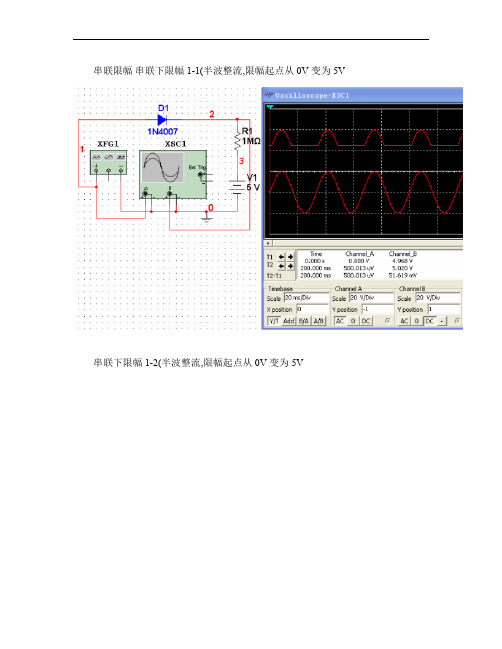

限幅电路仿真及波形.

串联限幅串联下限幅 1-1(半波整流,限幅起点从 0V 变为 5V

串联下限幅 1-2(半波整流,限幅起点从 0V 变为 5V

串联下限幅 2-1(半波整流,限幅起点从 0V 变为 -5V

串联下限幅 2-2(半波整流,限幅起点从 0V 变为 -5V

串联上限幅 1-1(半波整流,限幅起点从 0V 变为 5V

串联上限幅 1-2(半波整流,限幅起点从 0V 变为 5V

串联上限幅 2-1(半波整流,限幅起点从 0V 变为 -5V

串联上限幅 2-2(半波整流,限幅起点从 0V 变为 -5V

并联限幅并联上限幅 1-1(半波整流,限幅起点从 0V 变为 -5V

并联上限幅

1-2

并联上限幅 2-1 并联上限幅 2-2 并联下限幅 1-1 并联下限幅 1-2 并联下限幅 2-1 并联下限幅 2-2。

Bright Spark 电子教学仿真软件及其应用

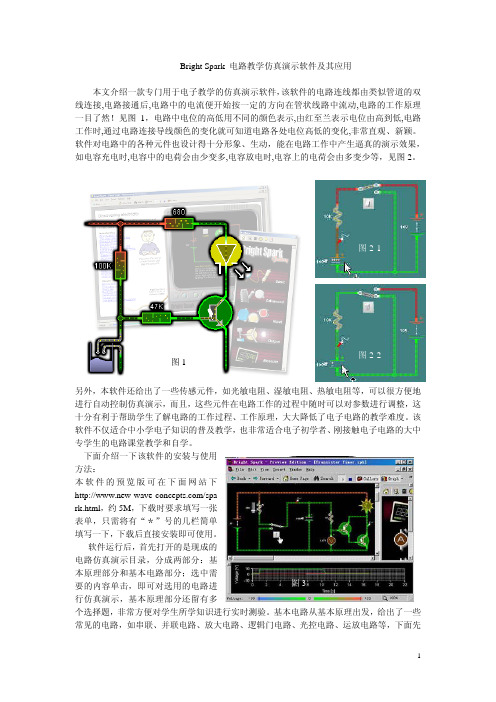

Bright Spark 电路教学仿真演示软件及其应用本文介绍一款专门用于电子教学的仿真演示软件,该软件的电路连线都由类似管道的双线连接,电路接通后,电路中的电流便开始按一定的方向在管状线路中流动,电路的工作原理一目了然!见图1,电路中电位的高低用不同的颜色表示,由红至兰表示电位由高到低,电路工作时,通过电路连接导线颜色的变化就可知道电路各处电位高低的变化,非常直观、新颖。

软件对电路中的各种元件也设计得十分形象、生动,能在电路工作中产生逼真的演示效果,如电容充电时,电容中的电荷会由少变多,电容放电时,电容上的电荷会由多变少等,见图2。

另外,本软件还给出了一些传感元件,如光敏电阻、湿敏电阻、热敏电阻等,可以很方便地进行自动控制仿真演示,而且,这些元件在电路工作的过程中随时可以对参数进行调整,这十分有利于帮助学生了解电路的工作过程、工作原理,大大降低了电子电路的教学难度。

该软件不仅适合中小学电子知识的普及教学,也非常适合电子初学者、刚接触电子电路的大中专学生的电路课堂教学和自学。

下面介绍一下该软件的安装与使用方法:本软件的预览版可在下面网站下/spark.html ,约5M ,下载时要求填写一张表单,只需将有“*”号的几栏简单填写一下,下载后直接安装即可使用。

软件运行后,首先打开的是现成的电路仿真演示目录,分成两部分:基本原理部分和基本电路部分;选中需要的内容单击,即可对选用的电路进行仿真演示,基本原理部分还留有多个选择题,非常方便对学生所学知识进行实时测验。

基本电路从基本原理出发,给出了一些常见的电路,如串联、并联电路、放大电路、逻辑门电路、光控电路、运放电路等,下面先仿真演示电路 仿真波形图 仿真元件库 图1 3介绍对电路的仿真演示操作方法:单击要选择的电路,这里选晶体管延时电路(transistor timer),打开后如图3,其已处于仿真运行状态,如果打开后的界面没有元件库和波图形,分别按下Ctrl+F1键和Ctrl+F2键即可。

实验五1位全加器的文本输入(波形仿真应用)

实验五 1位全加器的文本输入(波形仿真用)1.实验目的通过此实验让学生逐步了解、熟悉和掌握FPGA开发软件Quartus II的使用方法及VHDL 的编程方法。

学习电路的仿真方法。

2.实验内容本实验的内容是建立一个1位全加器。

在实验箱上的按键KEY1~KEY3分别为A、B 和Cin,并通过LED1~LED3指示相应的状态。

输出Sum和Cout通过LED7和LED8指示。

3.实验原理1位全加器的真值表如下所示。

表1位全加器逻辑功能真值表4.实验步骤(1) 启动Quartus II,建立一个空白工程,然后命名为full_add.qpf。

(2) 新建full_add.vhd源程序文件,编写代码。

然后进行综合编译。

若在编译过程中发现错误,则找出并更正错误,直到编译成功为止。

也可采用原理图文件的输入方式,建立半加器,然后在组成1位全加器。

原理图如下所示半加器设计1位全加器设计(3) 波形仿真步骤如下:① 在Quartus II 主界面中选择File → New 命名,打开新建文件对话框,从中选择V ector Waveform File ,如下图所示。

单击OK 建立一个空的波形编辑窗口。

选择File →Saveas 改名为full_add.vwf。

此时会看到窗口内出现如下图所示。

图 新建文件对话框 图 新建波形文件界面② 在上图所示的Name 选项卡内双击鼠标左键,弹出如图 所示的对话框。

在该对话框中单击Node Finder 按钮,弹出如图 所示的对话框。

图 添加节点对话框③ 按照下图所示进行选择和设置,先按下“list ”按钮,再按下“>>”按钮添加所有节点,最后按下“ok ”按钮。

图添加节点④波形编辑器默认的仿真结束时间为1us,根据仿真需要可以设置仿真文件的结束时间。

选择Edit→ End Time命令可以更改。

这里采用默认值不需更改。

图添加完节点的波形图⑤编辑输入节点的波形。

编辑时将使用到波形编辑工具栏中的各种工具。

DDS实验报告

电子线路课程设计 --直接数字频率合成器(DDS)2014 年 11 月摘要本实验通过使用 QuartusⅡ软件,并结合数字逻辑电路的知识设计,使用DDS 的方法设计一个任意频率的正弦信号发生器,要求具有频率控制、相位控制、以及使能开关等功能。

在此基础上,本实验还设计了扩展功能,包括测频、切换波形,动态显示。

在控制电路的作用下能实现保持、清零功能,另外还能同时显示输出频率、相位控制字、频率控制字。

在利用 QuartusⅡ进行相应的设计、仿真、调试后下载到SmartSOPC实验实现 D/A转换,验证实验的准确性,并用示波器观察输出波形。

关键词:SmartSOPC实验箱 QUARTUSⅡ数字频率合成仿真AbstractThis experiment is based on QuartusⅡ,with the help of knowledge relating to the digital logic circuits and system design,to design a sine signal generator which generates any frequency by the method of DDS. This generator is provided with the functions of frequency control,phase control and switch control. Based on the basic design,I also design extra functions,including frequency measurement,changes of wave forms and dynamic display.The control circuit can be maintained time clearing and time keeping functions,and also shows the output frequency,phase control characters,frequency control word. All the designing and simulating work are based on QuartusⅡ. After all the work finished on computer, I downloaded the final circuit to SmartSOPC experiment system to realize the transformation of D/A ,and then test the accuracy of the design by means of oscilloscope observing the wave forms.Key words: SmartSOPC QUARTUSⅡ DDS Simulation目录摘要 (1)目录 (2)一、设计要求 (3)二、方案论证 (3)三、直接数字频率合成器总电路图 (4)四、各子模块设计原理及分析说明 (5)4.1、脉冲发生电路 (5)4.2、频率相位预置与调节电路 (9)4.3、累加器电路 (10)4.4、相位控制电路 (11)4.5、波形存储器ROM电路 (12)4.6、测频电路 (14)4.7、不同波形选择电路 (15)4.8、动态译码显示电路 (16)五、程序下载、仿真与调试 (17)六、实验结果 (18)七、实验总结与感想 (23)八、参考文献 (23)一、设计要求1、利用QuartusII软件和SmartSOPC实验箱实现直接数字频率合成器(DDS)的设计;2、DDS中的波形存储器模块用Altera公司的Cyclone系列FPGA芯片中的RAM 实现,RAM结构配置成212×10类型;3、具体参数要求:频率控制字K取4位;基准频率fc=1MHz,由实验板上的系统时钟分频得到;4、系统具有使能功能;5、利用实验箱上的D/A转换器件将ROM输出的数字信号转换为模拟信号,能够通过示波器观察到正弦波形;6、通过开关(实验箱上的Ki)输入DDS的频率和相位控制字,并能用示波器观察加以验证;7、可适当添加其他功能二、方案论证直接数字频率合成器(Direct Digital Frequency Synthesizer)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。

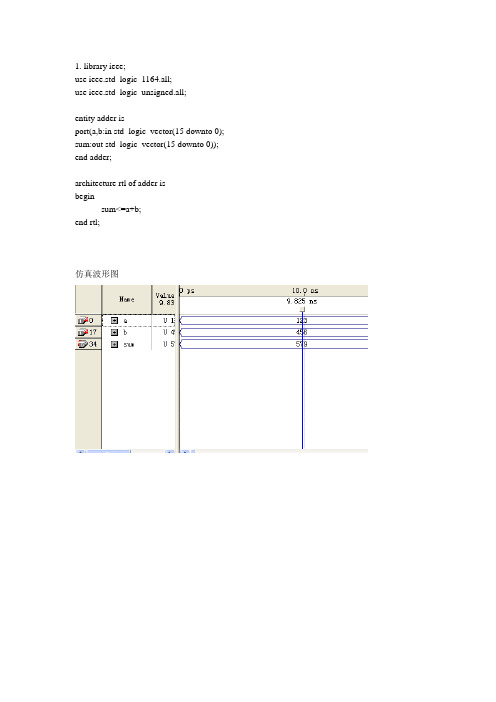

8位加法器程序源代码及仿真波形

use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder isport(a,b:in std_logic_vector(15 downto 0); sum:out std_logic_vector(15 downto 0)); end adder;architecture rtl of adder isbeginsum<=a+b;end rtl;仿真波形图use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity mux4 isport(a,b:in std_logic_vector(3 downto 0);sel:in std_logic;y:out std_logic_vector(3 downto 0)); end mux4;architecture rtl of mux4 isbeginprocess(sel,a,b)beginif(sel='0') then y<=a;else y<=b;end if;end process;end rtl;仿真波形图use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity seven isport(input:in std_logic_vector(2 downto 0);a,b,c,d,e,f,g:out std_logic);end seven;architecture rtl of seven isbeginprocess(input)begincase input iswhen "000" => a<='1';b<='1';c<='1';d<='1';e<='1';f<='1';g<='0';when "001" => a<='0';b<='1';c<='1';d<='0';e<='0';f<='0';g<='0';when "010" => a<='1';b<='1';c<='0';d<='1';e<='1';f<='0';g<='1';when "011" => a<='1';b<='1';c<='1';d<='1';e<='0';f<='0';g<='1';when "100" => a<='1';b<='0';c<='0';d<='1';e<='1';f<='1';g<='1';when "101" => a<='1';b<='0';c<='0';d<='1';e<='1';f<='1';g<='1';when "110" => a<='1';b<='0';c<='0';d<='1';e<='1';f<='1';g<='1';when "111" => a<='1';b<='0';c<='0';d<='1';e<='1';f<='1';g<='1'; end case;end process;end rtl;仿真波形图use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity shifter isport(input:in std_logic_vector(7 downto 0);cnt:in std_logic_vector(1 downto 0);result:out std_logic_vector(15 downto 0)); end shifter;architecture rtl of shifter isbeginprocess(cnt,input)begincase cnt iswhen "00" => for i in 15 downto 0 loopif i>=8 then result(i)<='0';else result(i)<=input(i);end if;end loop;when "01" => for i in 15 downto 0 loopif i>=12 or i<=3 then result(i)<='0';else result(i)<=input(i-4);end if;end loop;when "10" => for i in 15 downto 0 loopif i>=8 then result(i)<=input(i-8);else result(i)<='0';end if;end loop;when "11" => for i in 15 downto 0 loopif i>=8 then result(i)<='0';else result(i)<=input(i);end if;end loop;end case;end process;end rtl;仿真波形图use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity rega isport(in_reg:in std_logic_vector(15 downto 0);clk:in std_logic; clr:in std_logic; clken:in std_logic;out_reg:out std_logic_vector(15 downto 0));end rega;architecture rtl of rega isbeginprocess(clk,clr,clken)beginif(clk'event and clk='1' ) thenif (clr='1' and clken='0') then out_reg<=in_reg;else out_reg<="0000000000000000";end if;end if;end process;end rtl;仿真波形图use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter isport(clk:in std_logic;clr:in std_logic;sum:out std_logic_vector(1 downto 0));end counter;architecture rtl of counter isbeginprocess(clk,clr)variable m:std_logic_vector(1 downto 0); beginif(clr='0') then m:="00";elsif(clk'event and clk='1') thenm:=m+1;end if;sum<=m;end process;end rtl;仿真波形图6. (1)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity control isport(clk,rst,start:in std_logic;count:in std_logic_vector(1 downto 0);in_sel,shift:out std_logic_vector(1 downto 0); state_out:out std_logic_vector(2 downto 0);done,clken,regclr:out std_logic );end entity control;architecture rtl of control istype states is(idle,lsb,err,mid,msb);signal current_state,next_state:states;beginreg:process(rst,clk ) isbeginif rst='1' thencurrent_state<=idle;elsif(clk='1' and clk'event) thencurrent_state<=next_state;end if;end process reg;com:process(current_state,count,start) isvariable m,n:std_logic;variable r:std_logic_vector(1 downto 0);begincase current_state iswhen idle=>state_out<="000";if start='1' thennext_state<=lsb;m:='0';clken<='1';n:='0';else next_state<=idle;m:='0';clken<='1';n:='1';end if;when lsb=>state_out<="001";if (start='0' and count="00") thennext_state<=mid;r:="00";shift<="00"; m:='0';clken<='0';n:='1';else next_state<=err;m:='0';clken<='1';n:='1';end if;when mid=>state_out<="010";if (start='0' and count="01") thennext_state<=mid;r:="01";shift<="01"; m:='0';clken<='0';n:='1';elsif (start='0' and count="10") thennext_state<=msb;r:="10";shift<="01"; m:='0';clken<='0';n:='1';else next_state<=err ;m:='0';clken<='1';n:='1';end if;when msb=>state_out<="011";if (start='0' and count="11") thennext_state<=idle;r:="11";shift<="10"; m:='1';clken<='0';n:='1';else next_state<=err ;m:='0';clken<='1';n:='1';end if;when err=>state_out<="100";if start='1' thennext_state<= lsb ;m:='0';clken<='1';n:='0';else next_state<= err ;m:='0';clken<='1';n:='1';end if;end case;done<=m;regclr<=n;in_sel<=r;end process com;end rtl;6.(1)仿真波形图6.(2) LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY lpm;USE lpm.all;ENTITY mult4x4 ISPORT(dataa : IN STD_LOGIC_VECTOR (3 DOWNTO 0);datab : IN STD_LOGIC_VECTOR (3 DOWNTO 0);result : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );END mult4x4;ARCHITECTURE SYN OF mult4x4 ISSIGNAL sub_wire0 : STD_LOGIC_VECTOR (7 DOWNTO 0);COMPONENT lpm_multGENERIC (lpm_hint : STRING;lpm_representation : STRING;lpm_type : STRING;lpm_widtha : NA TURAL;lpm_widthb : NA TURAL;lpm_widthp : NA TURAL);PORT (dataa : IN STD_LOGIC_VECTOR (3 DOWNTO 0);datab : IN STD_LOGIC_VECTOR (3 DOWNTO 0);result : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );END COMPONENT;BEGINresult <= sub_wire0(7 DOWNTO 0);lpm_mult_component : lpm_multGENERIC MAP (lpm_hint => "MAXIMIZE_SPEED=5",lpm_representation => "UNSIGNED",lpm_type => "LPM_MULT",lpm_widtha => 4,lpm_widthb => 4,lpm_widthp => 8)PORT MAP (dataa => dataa,datab => datab,result => sub_wire0 );END SYN;6.(2)仿真波形图6.(3)仿真波形图。

Matlab电力电子仿真教程ppt课件

第5章 电力电子电路仿真分析

(a)

(b)

图5-7 晶闸管模块的电路符号和静态伏安特性 (a) 电路符号;(b) 静态伏安特性

第5章 电力电子电路仿真分析 SimPowerSystems库提供的晶闸管模块一共有两种:一 种是详细的模块(Detailed Thyristor),需要设置的参数较多; 另一种是简化的模块(Thyristor),参数设置较简单。晶闸管 模块的图标如图5-8。

解:(1) 按图5-5搭建仿真电路模型,选用的各模块的名 称及提取路径见表5-1。

第5章 电力电子电路仿真分析 图5-5 例5.1的仿真电路图

第5章 电力电子电路仿真分析

表5-1 例5.1仿真电路模块的名称及提取路径

模块名 功率二极管模块 D1、D2、D3、D4 交流电压源 Vs 串联 RLC 支路 R 电压表模块 VR 电流表模块 IR 信号分离模块 Demux 示波器 Scope

7所示为晶闸管模块的电路符号和静态伏安特性。当晶闸管 承受正向电压(Vak>0)且门极有正的触发脉冲(g>0)时,晶闸 管导通。触发脉冲必须足够宽,才能使阳极电流Iak大于设定 的晶闸管擎住电流I1,否则晶闸管仍要转向关断。导通的晶 闸管在阳极电流下降到0(Iak=0)或者承受反向电压时关断, 同样晶闸管承受反向电压的时间应大于设置的关断时间,否 则,尽管门极信号为0,晶闸管也可能导通。这是因为关断 时间是表示晶闸管内载流子复合的时间,是晶闸管阳极电流 降到0到晶闸管能重新施加正向电压而不会误导通的时间。

(9) “测量输出端”(Show measurement port)复选框:选 中该复选框,出现测量输出端口m,可以观测晶闸管的电流 和电压值。

【例5.2】如图5-10所示,构建单相桥式可控整流电路, 观测整流效果。晶闸管模块采用默认参数。

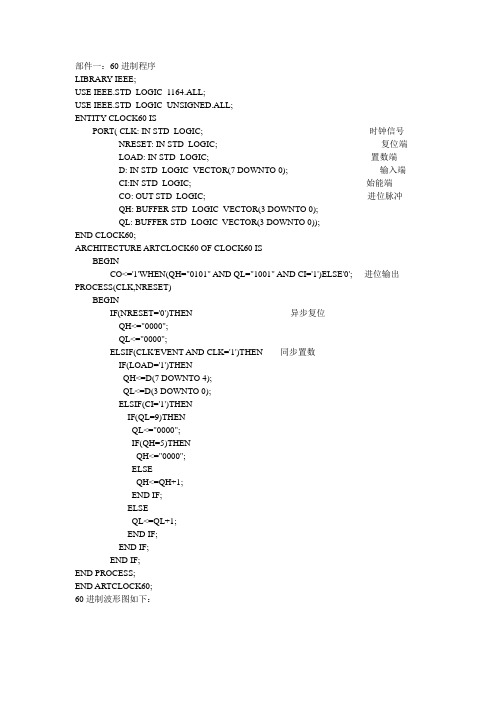

eda数字钟程序及波形仿真图

部件一:60进制程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CLOCK60 ISPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END CLOCK60;ARCHITECTURE ARTCLOCK60 OF CLOCK60 ISBEGINCO<='1'WHEN(QH="0101" AND QL="1001" AND CI='1')ELSE'0';----进位输出PROCESS(CLK,NRESET)BEGINIF(NRESET='0')THEN -----异步复位QH<="0000";QL<="0000";ELSIF(CLK'EVENT AND CLK='1')THEN------同步置数IF(LOAD='1')THENQH<=D(7 DOWNTO 4);QL<=D(3 DOWNTO 0);ELSIF(CI='1')THENIF(QL=9)THENQL<="0000";IF(QH=5)THENQH<="0000";ELSEQH<=QH+1;END IF;ELSEQL<=QL+1;END IF;END IF;END IF;END PROCESS;END ARTCLOCK60;60进制波形图如下:部件二:24进制程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CLOCK24 ISPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END CLOCK24;ARCHITECTURE ARTCLOCK24 OF CLOCK24 ISBEGINCO<='1'WHEN(QH="0101" AND QL="1001" AND CI='1')ELSE'0';----进位输出PROCESS(CLK,NRESET)BEGINIF(NRESET='0')THEN -----异步复位QH<="0000";QL<="0000";ELSIF(CLK'EVENT AND CLK='1')THEN------同步置数IF(LOAD='1')THENQH<=D(7 DOWNTO 4);QL<=D(3 DOWNTO 0);ELSIF(CI='1')THENIF(QL=9 or (QH=2 AND QL=3))THENQL<="0000";IF(QH=2)THENQH<="0000";ELSEQH<=QH+1;END IF;ELSEQL<=QL+1;END IF;END IF;END IF;END PROCESS;END ARTCLOCK24;24进制的波形图如下:数字钟的全部程序如下:LIBRARY IEEE; ---秒信号USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CLOCK60s ISPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END CLOCK60s;ARCHITECTURE ARTCLOCK60s OF CLOCK60s ISBEGINCO<='1'WHEN(QH="0101" AND QL="1001" AND CI='1')ELSE'0'; --进位输出PROCESS(CLK,NRESET)BEGINIF(NRESET='0')THEN ---异步复位QH<="0000";QL<="0000";ELSIF(CLK'EVENT AND CLK='1')THEN --同步置数IF(LOAD='1')THENQH<=D(7 DOWNTO 4);QL<=D(3 DOWNTO 0);ELSIF(CI='1')THENIF(QL=9)THENQL<="0000";IF(QH=5)THENQH<="0000";ELSEQH<=QH+1;END IF;ELSEQL<=QL+1;END IF;END IF;END IF;END PROCESS;END ARTCLOCK60s;LIBRARY IEEE; ---分信号USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CLOCK60m ISPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END CLOCK60m;ARCHITECTURE ARTCLOCK60m OF CLOCK60m ISBEGINCO<='1'WHEN(QH="0101" AND QL="1001" AND CI='1')ELSE'0'; --进位输出PROCESS(CLK,NRESET)BEGINIF(NRESET='0')THEN --异步复位QH<="0000";QL<="0000";ELSIF(CLK'EVENT AND CLK='1')THEN ---同步置数IF(LOAD='1')THENQH<=D(7 DOWNTO 4);QL<=D(3 DOWNTO 0);ELSIF(CI='1')THENIF(QL=9)THENQL<="0000";IF(QH=5)THENQH<="0000";ELSEEND IF;ELSEQL<=QL+1;END IF;END IF;END IF;END PROCESS;END ARTCLOCK60m;LIBRARY IEEE; ---时信号USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CLOCK24 ISPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; --进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END CLOCK24;ARCHITECTURE ARTCLOCK24 OF CLOCK24 ISBEGINCO<='1'WHEN(QH="0101" AND QL="1001" AND CI='1')ELSE'0'; ---进位输出PROCESS(CLK,NRESET)BEGINIF(NRESET='0')THEN ---异步复位QH<="0000";QL<="0000";ELSIF(CLK'EVENT AND CLK='1')THEN ---同步置数IF(LOAD='1')THENQH<=D(7 DOWNTO 4);QL<=D(3 DOWNTO 0);ELSIF(CI='1')THENIF(QL=9 or (QH=2 AND QL=3))THENQL<="0000";IF(QH=2)THENQH<="0000";ELSEQH<=QH+1;END IF;ELSEEND IF;END IF;END IF;END PROCESS;END ARTCLOCK24;LIBRARY IEEE; ---时信号USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY hour ISPORT( CLK: IN STD_LOGIC; ---时钟信号NRESETS: IN STD_LOGIC; ---复位端LOADS: IN STD_LOGIC; ---置数端NRESETM: IN STD_LOGIC; ---复位端LOADM: IN STD_LOGIC; ---置数端NRESETH: IN STD_LOGIC; ---复位端LOADH: IN STD_LOGIC; ---置数端DS: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端DM: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端DH: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH1: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL1: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QH2: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL2: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QH3: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL3: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END hour;ARCHITECTURE ART OF hour ISCOMPONENT CLOCK60SPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT CLOCK60MPORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; ---始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;COMPONENT CLOCK24PORT( CLK: IN STD_LOGIC; ---时钟信号NRESET: IN STD_LOGIC; ---复位端LOAD: IN STD_LOGIC; ---置数端D: IN STD_LOGIC_VECTOR(7 DOWNTO 0); ---输入端CI:IN STD_LOGIC; --始能端CO: OUT STD_LOGIC; ---进位脉冲QH: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT;SIGNAL Z1,Z2:STD_LOGIC;BEGINU1: CLOCK60S PORT MAP(CLK,NRESETS,LOADS,DS,CI,Z1,QH1,QL1);U2: CLOCK60M PORT MAP(CLK,NRESETM,LOADM,DM,Z1,Z2,QH2,QL2);U3: CLOCK24 PORT MAP(CLK,NRESETH,LOADH,DH,Z2,CO,QH3,QL3);END ARCHITECTURE ART;电子钟全部引脚显示波形:00:00:59波形显示如下:00:59:59波形图如下,进位后为01:00:00 23:59:59波形图如下:调时间波形如下:用置位端进行调时,调到02:51:15波形如下:经验证,以上设计完全符合题目要求!。