DSP_课程复习资料整理

DSP复习要点

DSP复习要点第一章:1.DSP 技术应用非常广泛,例如:移动通信系统、VOIP 、HFC 、软件无线电、数码相机、DB DIGITAL AC-3、汽车多媒体系统、噪声消除算法、机顶盒(SET-TOP-BOX )、飞机驾驶模拟器、全球定位系统(GPS )、雷达/声纳、巡航导弹、F-117发射激光制导灵巧炸弹、图像识别、图像鉴别、医院用的B 超、CT 、核磁共振、卫星遥感遥测;天气预报,地震预报,地震探矿;风动试验;数字化士兵,数字化战争;高清晰度电视、虚拟仪器2. 主要DSP 芯片厂商有:AD 公司、AT&T 公司(现在的Lucent 公司)、 Motorola 公司、TI 公司(美国德州仪器公司)、NEC 公司。

3. 3. DSP 芯片,也称数字信号处理器,是一种具有特殊结构的微处理器。

DSP 芯片的内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,广泛采用流水线操作,提供特殊的DSP 指令,可以用来快速的实现各种数字信号处理算法。

4.冯·诺伊曼(Von Neuman )结构该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

5. 哈佛(Harvard )结构该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

6. DSP 芯片的特点:7. 根据芯片工作的数据格式,按其精度或动态范围,可将通用DSP 划分为定点DSP 和浮点DSP 两类。

7. 一般来说,选择DSP 芯片时应考虑的重要因素:运算速度、价格、功耗第二章4. 改进型的哈佛结构是采用双存储空间和数条总线,即一条程序总线和多条数据总线,允许在程序空间和数据空间之间相互传送数据。

DSP复习资料

DSP复习资料1、DSP 芯⽚的结构?答:DSP 是改进的哈佛结构 (80C51是哈佛结构)。

冯.诺依曼结构与哈佛结构的区别是地址空间和数据空间分开与否。

冯诺依曼结构数据空间和地址空间不分开,哈佛结构数据空间和地址空间是分开的。

哈佛结构的特点:使⽤两个独⽴的存储器模块,分别存储指令和数据,每个存储模块都不允许指令和数据并存;使⽤独⽴的两条总线,分别作为CPU 与每个存储器之间的专⽤通信路径,⽽这两条总线之间毫⽆关联。

改进的哈佛结构,其结构特点为:使⽤两个独⽴的存储器模块,分别存储指令和数据,每个存储模块都不允许指令和数据并存,以便实现并⾏处理;具有⼀条独⽴的地址总线和⼀条独⽴的数据总线,利⽤公⽤地址总线访问两个存储模块(程序存储模块和数据存储模块),公⽤数据总线则被⽤来完成程序存储模块或数据存储模块与CPU 之间的数据传输,改进的哈佛结构在哈佛结构的基础上⼜加以改进,即使得程序代码和数据存储空间之间也可以进⾏数据的传送。

TMS320LF2407A 采⽤改进的哈佛结构,芯⽚内部具有六条16位总线,即程序地址总线(PAB )、数据读地址总线(DRAB )、数据写地址总线(DWAB )、程序读总线(PRDB )、数据读总线(DRDB )、数据写总线(DWEB ),其程序存储器总线和数据存储器总线相互独⽴,⽀持并⾏的程序和操作数寻址,因此CPU 的读/写可在同⼀周期内进⾏,这种⾼速运算能⼒使⾃适应控制、卡尔曼滤波、神经⽹络、遗传算法等复杂控制算法得以实现。

结构⽰意图如下:2、什么是流⽔线技术?DSP 是不是具有流⽔线技术(pipeline) ?答:流⽔线技术是将各指令的各个步骤重叠起来执⾏,⽽不是⼀条指令执⾏完成之后,才开始执⾏下⼀条指令。

计算机在执⾏⼀条指令时,总要经过取指、译码、取数、执⾏运算等步骤,需要若⼲个指令周期才能完成。

流⽔线技术是将各指令的各个步骤重叠起来执⾏,⽽不是⼀条指令执⾏完成之后,才开始执⾏下⼀条指令。

DSP复习提纲精华版

1、请列出几种常用的嵌入式操作系统,并简单说明其特点?2、常用的嵌入式处理器包括?3、DSP按照数据格式可以分为定点和浮点处理器两种4、DSP同单片机不同在于其哈弗结构,请说明其特点?5、DSP与MCU硬件结构比较,有何异同?6、请列出几个常用的DSP制造商?7、CPU组成包括什么?8、DSP的程序执行机构是什么?9、DSP的每次取指操作都是取8条32位指令,称为一个取指包10、指令执行时,每条指令占用一个功能单元11、什么是DSP的数据通路,C6000的数据通路包括什么?12、下列寄存器哪个不能用作条件寄存器A1、A2、A3、B0、B1、B213、C6000DSP中有8个功能单元,分别是什么?14、什么是流水线,其操作原理是什么?15、DSP的流水线都按照所有指令均按取指(fetch)、译码(decode)和执行三级进行。

16、取指级有4个节拍,译码级有2个节拍,执行级对不同类型的指令有不同数目的节拍17、流水线操作以CPU周期为单位,1个执行包在流水线1个节拍的时间就是1个CPU周期。

18、①在DP节拍,1个取指包的8条指令根据并行性被分成几个执行包,执行包由1~8条并行指令组成。

②在DP节拍期间,1个执行包的指令被分别分配到相应的功能单元③同时,源寄存器、目的寄存器和有关数据通路被译码以便在功能单元完成指令执行19、C6000片内为哈佛结构,即存储器分为程序存储空间和数据存储空间。

20、延迟间隙21、取指包:CPU运行时总是一次取8条32位指令,组成一个取指包执行包:所有并行执行的指令组成一个执行包。

22、C6000全部采用间接寻址23、所有寄存器都可以作为线性寻址的地址指针。

而A4~A7,B4~B7这8个寄存器还可以作为循环寻址的地址指针24、DSP试验箱通过仿真器连接电脑,其接口是JTAG口。

25、CCS有两种工作模式,软件仿真模式;硬件在线编程模式26、为什么要使用RTOS27、DSP/BIOS提供了4种不同的线程:硬件中断(HWI)、软件中断(SWI) 、任务(TSK) 、IDLE线程。

dsp重点知识点总结

dsp重点知识点总结1. 数字信号处理基础数字信号处理的基础知识包括采样定理、离散时间信号、离散时间系统、Z变换等内容。

采样定理指出,为了保证原始信号的完整性,需要将其进行采样,并且采样频率不能小于其最高频率的两倍。

离散时间信号是指在离散时间点上取得的信号,可以用离散序列表示。

离散时间系统是指输入、输出和状态都是离散时间信号的系统。

Z变换将时域的离散信号转换为Z域的函数,它是离散时间信号处理的数学基础。

2. 时域分析时域分析是对信号在时域上的特性进行分析和描述。

时域分析中常用的方法包括时域图形表示、自相关函数、互相关函数、卷积等。

时域图形表示是通过时域波形来表示信号的特性,包括幅度、相位、频率等。

自相关函数是用来描述信号在时间上的相关性,互相关函数是用来描述不同信号之间的相关性。

卷积是一种将两个信号进行联合的运算方法。

3. 频域分析频域分析是对信号在频域上的特性进行分析和描述。

频域分析中常用的方法包括频谱分析、傅里叶变换、滤波器设计等。

频谱分析是通过信号的频谱来描述信号在频域上的特性,可以得到信号的频率成分和相位信息。

傅里叶变换是将时域信号转换为频域信号的一种数学变换方法,可以将信号的频率成分和相位信息进行分析。

滤波器设计是对信号进行滤波处理,可以剔除不需要的频率成分或增强需要的频率成分。

4. 数字滤波器数字滤波器是数字信号处理中的重要组成部分,通过对信号进行滤波处理,可以实现对信号的增强、降噪、分离等效果。

数字滤波器包括有限冲激响应(FIR)滤波器和无限冲激响应(IIR)滤波器两种类型。

有限冲激响应(FIR)滤波器是一种只有有限个系数的滤波器,它可以实现线性相位和稳定性处理。

无限冲激响应(IIR)滤波器是一种有无限个系数的滤波器,它可以实现非线性相位和较高的滤波效果。

5. 离散傅里叶变换(DFT)和快速傅里叶变换(FFT)离散傅里叶变换(DFT)是将时域离散信号转换为频域离散信号的一种数学变换方法,其计算复杂度为O(N^2)。

DSP复习要点详解

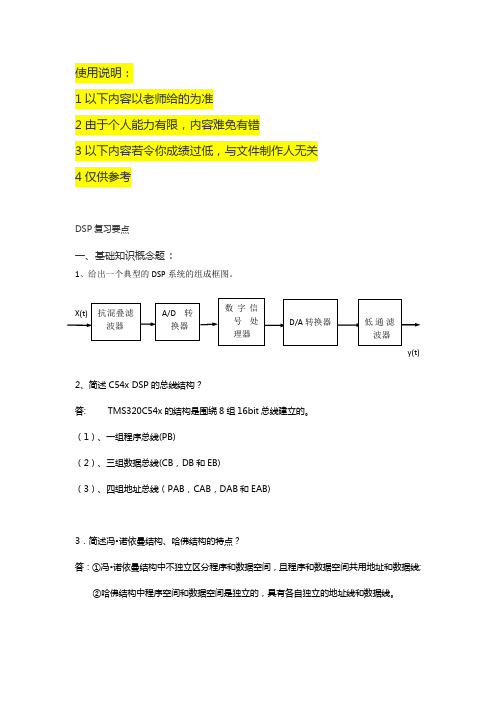

使用说明:1以下内容以老师给的为准2由于个人能力有限,内容难免有错3以下内容若令你成绩过低,与文件制作人无关4仅供参考DSP复习要点一、基础知识概念题:1、给出一个典型的DSP系统的组成框图。

y(t) 2、简述C54x DSP的总线结构?答: TMS320C54x的结构是围绕8组16bit总线建立的。

(1)、一组程序总线(PB)(2)、三组数据总线(CB,DB和EB)(3)、四组地址总线(PAB,CAB,DAB和EAB)3.简述冯•诺依曼结构、哈佛结构的特点?答:①冯•诺依曼结构中不独立区分程序和数据空间,且程序和数据空间共用地址和数据线;②哈佛结构中程序空间和数据空间是独立的,具有各自独立的地址线和数据线。

4、C54x DSP的CPU包括哪些单元?答:'C54X 芯片的CPU包括:(1)、40bit的算术逻辑单元(2)、累加器A和B(3)、桶形移位寄存器(4)、乘法器/加法器单元(5)、比较选择和存储单元(6)、指数编码器(7)、CPU状态和控制寄存器(8)、寻址单元。

6、C54x的三个独立存储器空间分别是什么?答:(1)、64K字的程序存储空间(2)、64K字的数据空间(3)、64K字的I/O空间,7、简述TMS320C54xDSP的流水线分为几个操作阶段答:分为6个阶段1、预取指2、取指3、译码4、寻址5、读数6、执行8、简述C54x有哪些数据寻址方式?答:1、立即寻址2、绝对寻址3、累加器寻址4、直接寻址5、间接寻址6、存储器映像寄存器寻址7、堆栈寻址10、68页表3.1.1缩略语要记住。

缩略语含义Smem 单数据存储器操作数Xmem 双数据存储器操作数,从DB数据总线上读取Ymem 双数据存储器操作数,从CB数据总线上读取dmad 数据存储器地址pmad 程序存储器地址PA I/O口地址src 源累加器dst 目的累加器1k 16位长立即数11、定时器的初始化STM #0010H,TCR;关闭定时器,TSS=1定时器不工作STM #4999,PRD;定时周期寄存器为4999,当TIM减至0时重新装载STM #0669,TCR;重新设置定时的工作参数,TRB=1允许装载,TSS=0定时器开始工作。

dsp复习资料

一,Dsp 的硬件结构:⑴1组程序总线(PB),3组数据总线(CB,DB,EB),4组地址总线(PAB,CAB,DAB,EAB).⑵40位算术逻辑单元alu{C16=0工作在双精度算术运算方式,C16=1工作在双16位方式}ALU 溢出后状态寄存器ST0的OVM=1时,用32位最大正数007FFFFFFFH 或最大负数FF80000000H 加载累加器,溢出后溢出标志位OVA 或OVB=1直到复位!⑶1个40位桶行移位寄存器,⑷2个独立40位ACCA 和ACCB{ACCA 和ACCB 差别在于A 的31~16位可以用途乘法器的一个输入}.⑸17X17并行乘法器与40位的专用加法器相连,用于MAC 运算.⑹比较/选择/存储单元(CSSU)用于加法比较运算,⑺指数单元EXP(40位),⑻有16bit 状态寄存器ST0,ST1和工作方式状态寄存器PMST.二,存储结构:①哈佛结构(ROM 和RAM 分开),②三个独立64kb,ROM,RAM,I/O 空间,程序空间通过PMST 的MP/MC\和OVLY 控制,MP 控制使用内部存储器,MP=0,4000H-EFFFH 程序存储空间定义为外部存储器,FF00H-FEFFH 为内部,FF00H-FFFFH 为内部ROM 存储器,工作方式为微型计算机,MP=1,4000H-FFFFH 全部定义为外部存储器,工作方式为处理器模式.当OVLY=0时,0000H~3FFFH 全部定义为外部程序存储空间,程序空间不使用内部RAM,此时内部RAM 只作为数据存储器使用,OVLY=10000H~007FH 保留,程序无法使用,0080H~3FFFH 定义为内部DARAM,即内部RAM 被映射到程序存储空间和数据存储空间.③片上外设:2个通用I/O,XF(外部标志输出信号.控制外设工作)和BIO(控制分支转移信号,监测外部状态).BIO=0时执行转移指令.④定时器:4位预分频器和16位减法计数器组成,定时设定寄存器TIM(16bit)→0024H,复位/定时TIM 装入PRD(定时寄存器→0025H,存放定时常数)寄存器的值,然后减1计数,TIM 减到0后产生TINT 中断,TCR(定时控制寄存器→0026H)用来控制定时器的控制位和状态位,包括定时分频TDDR,预标定时计数器PSC,控制位TRB 和TSS 等.周期=时钟T*(TDDR+1)*(PRD+1).⑤时钟发生器:内部振荡器和锁相环PLL{⑴硬件配置PLL,通过[CLKMD1,CLKMD2,CLKMD3R 的状态,]⑵软件设置[通过16位的CLKMD →58H 控制]},⑥主机接口HPI:{控制寄存器HPIC,地址寄存器HPIA,数据锁存器HPID,HPI 内存},三,外设接口:软件等待状态寄存器SWWSR →0028H,复位时SWWSR →7FFFH,四,中断:1,可屏蔽中断{INT0-3,串行口中断,定时器中断TINT0-1,DMA 中断(DMAC4,DMAC5).HPINT(HPI 中断)}.2,非可屏蔽中断{外部中断投复位和‾NMI ‾(可用软件中断)}中断标志寄存器IFR 和中断屏蔽寄存器IMR{中断向量地址的计算[中断向量地址是由PMST 寄存器中的IPTR(中断向量指针,9bits)和左移2位后的中断向量序号(中断向量序号为0~31,左移两位后变成7位)所组成]例如INT0的中断序号为16(10H)左移两位后成40H 若IPTR=0001H,则中断地址为00C0H,复位时IPTR 全为1,所以硬件复位后程序总是从0FF80H 执行}.五,指令系统:1,寻址方式{i.立即寻址.[用于初始化(LD#80H,A)].ii.绝对寻址[①数据存储器(dmad)寻址(mvkd exam1,*ar5)②程序存储器(pmad)寻址(mvpd table,*ar2)③端口(pa)寻址(PORTR FIFO,*AR5)④*(1K)寻址(LD *(PN),A))].iii.累加器寻址{是用累加器中的数值作为地址来读写程序存储器,READA Smem,WRITASmen}.iv.直接寻址{ADD @x,A}.v.间接寻址[(寻址范围0~64kb)利用辅助寄存器内容作为地址访问存储器(C54x 有8个16bits 辅助寄存器AR0-AR7)]vi.存储器映像寄存器(MMR))寻址{LDM,MVDM,MVMD,MVMM,POPM,PSHM,STLM,STM}vii.堆栈寻址{PSHD,PSHM,POPD,POPD}.常用缩写{Smem:16位的单寻址操作数,Xmem:16位双寻址操作数,Ymem:16位双寻址操作数,PA:16位立即数,src:源累加器,dst:目的累加器,lk:16位长立即数},六,软件开发过程:.text 文本段,.data 数据段,.bss 保留空间,通常对未初始化变量保存,.sect 建立包含代码和数据的自定义段,.usect 为未初始化变量保留存储空间的自定义段,.word 用来设置一个或多个16位带符号整型常数,.int 设置无符号整型常数.title 后面是双引号的程序名,.end 结束汇编命令,汇编程序举例:㈠堆栈的使用:100单元的堆栈,size .set 100 \stack .usect “stk ”,size\STM #stack+size SP.㈡加减乘,①Z=X+Y-W,SUM:LD @x,A\ADD @y,A\SUB @w,A\STL A,@z.②y=mx+b,ld @m,t\mpy @x,A\add @b,A\stlA,@y.③y=x1*a1+x2*a2,ld @x1,t\mpy @a1,B\ld @a2,t\mpy @x2,b\stlB,@y\sth B,@y+1④y= a i 4i =1x i stm #a,ar1\stm #x,ar2\stm #2,ar3/ld *ar1+,t\mpy *ar2+,A\loopl:ld *ar1+,tMpy *ar2+,b/max A/banz loop,*ar3-㈢数组初始化x[5]=[1,2,3,4,5].data\tbl:.word 1,2,3,4,5\.sect “.vector ”\B START\.bss x,5\.text\START:stm #x,ar5\rpt #4\MVPD TBL,*AR5.㈣设计对称FIR 滤波器(N=8).title “firs5”\.mmregs\.def start\.bss y,1\x_old .usect “data1”,4\x_new .uscet “data2”,A\size .set 4\PA0 .set 0\PA1 .set 1\.data/COEF .word 1*32768/10,2*32768/10\.text/start:ld #y,dp\ssbxfrct\stm #x_new,ar2\stm #x_old+(size-1),ar3\stm #size,bk\stm #-1,ar0\POPTR PA1,#x_new\FIR5: ADD *AR2+0%,*AR3+0%,A\RPTZ B,#(size-1)\FIRS *AR2+0%,*AR3+0%,COEF\STH B,@y\MAR *+AR2(2)%\MAR *AR3+%\MVDD *AR2,*AR3+0%\BD FIR5\POPRTR PA1,*AR2\.end 用线性缓冲法和直接寻址法实现FIR 滤波器:N=5,Y(n)=a0x(n)+a1x(n-1)+a2x(n-2)+a3x(n-3)+a4x(n-4)程序:.title “fir1.asm ”\.mmrges\.def start\.bss y,1\XN .usect “XN ”,1\XNM1 .usect “XNM1”,1\XNM2 .usect “xnm2”,1\xnm3 .Usect “xnm3”,1\xnm4 .usect “xnm4”,1\a0 .usect “a0”,1\a1 .usect “a1”,1\a2 .usect “a2”,1\a3 .usect “a3”,1\a4 .usect “a4”,1\pa0 .set 0\pa1 .set 1\.data\table: .word1*32768/10\.word -3*32768/10\.word 5*32768/10\.word -3*32768/10\.word 1*32768/10\.text\start: ssbxfrct\stm #a0,ar1\rpt #4\mvpd table,ar1+\ld #xn,dp\portr pa1,@xn\fir1:ld @xnm4,t\Mpy @a4,a\ltd @xnm3\mac @a3,a\ltd @xnm2\mac @a2,a\ltd @xnm1,a\mac @a1,a\ltd @xn,a\mac @a0,a\ltha,@y\portw @y,pa0\bd fir1\portrpa1,@xn\.end 循环缓冲区和双操作数寻址方法实现:.title “firs ”\.mmregs\.def start\.bss new_data.1\.bss y,1\xn .usect “xn ”,5\a0 .usect “a0”,5\.data\tsble:.word 1*32768/10\.word 2*32768/10\.word 3*32768/10\.word 4*32768/10\.word 5*32768/10\.text\start:ssbxfrct\stm @a0,ar1\rpt #4\mvpd table,*ar1+\stm #xn+4,ar3\stm #a0+4,ar4\stm 5,bk\stm #-1,ar0\ld ##new_data\fir4:rptz a,#4\mac *ar3+0%,*ar4+0%,a\stha,@y\bd fir4\ldnew_data,bstl b,*ar3+0%\.end。

DSP复习资料

DSP最新考纲1、CPU总线结构基本概念。

2、直接寻址模式的基本寻址方法。

3、存储器映像寄存器包括的主要内容及地址。

4、CCS生成可执行文件的过程及载入可执行文件的方法。

5、片上ROM固化的内容及地址。

6、DSP系统的结构框图。

7、软件等待状态发生器的设置。

8、C语言中I/O端口的访问方法及插入汇编命令的方法。

9、自举的概念。

10、中断向量表地址的计算方法。

11、多路缓冲串口的发送和接收过程。

12、上电复位电路及手动复位电路设计方法。

13、定时器定时时间计算方法:定时周期 = CLKOUT×(TDDR+1)×(PRD+1)14、中断编程过程及方法。

15、布置的作业。

复习:1-01.数字信号处理:答:数字信号处理是利用计算机或专用处理设备,以数字的形式对信号进行分析、采集、合成、变换、滤波、估算、压缩、识别等加工处理,以便提取有用的信息并进行有效的传输与应用。

1-02.DSP系统的构成:1-03.数字信号处理器的特点:答:数字信号处理器(DSP)是一种特别适合于进行数字信号处理运算的微处理器,主要用于实时快速实现各种数字信号处理的算法。

哈弗结构;多总线结构;流水线结构;多处理单元;特殊的dsp指令;指令周期短;运算精度高;硬件配置高。

1-04.定点DSP:数据采用定点格式工作的DSP芯片。

浮点DSP:数据采用浮点格式工作的DSP芯片。

1-05.54x的特点:答:(1) 改进哈佛结构;(2) 8条总线(1条程序总线,3条数据总线,4条地址总线);(3) 高度专业指令系统;(4) 内核供电电压低。

优点:(1)功耗低;(2)高度并行性。

1-06.1. 总线结构:8条16位总线(1条程序,3条数据,4条地址)(1)PB:传送程序存储器的指令代码和操作数;(2)CB、DB:传送来自数据存储器的操作数;(3)EB传送写入数据存储器操作数;(4)PAB、CAB、DAB、EAB:传送地址信息。

DSP复习资料

第一章:DSP的实现方法:1.用专用的DSP芯片实现2.用通用的可编程DSP芯片实现3.用通用的单片机(如MCS-51、96系列等)实现4.在通用计算机系统中加上专用的加速处理机实现5.在通用的计算机(如PC)上用软件(如C语言)实现DSP系统工作过程1,对输入信号进行带限滤波和抽样;②进行A/D变换,将信号变换成数字比特流;③根据系统要求,DSP芯片对输入信号按照特定算法进行处理;④D/A转换,将处理后的数字样值转换为模拟信号;⑤平滑滤波,得到连续的模拟信号波形。

DSP系统特点:①接口方便②编程方便③稳定性好④精度高⑤可重复性好⑥集成方便DSP系统的设计1.定义系统性能指标2.采用高级语言进行性能模拟3.设计实时DSP应用系统4.借助开发工具进行软硬件调试5.系统集成与独立系统运行DSP芯片的分类按数据格式分——根据DSP芯片工作的数据格式来分类定点DSP芯片:价格较便宜、功耗较低,但运算精度稍低。

浮点DSP芯片:运算精度高,用C语言编程调试方便,但价格稍贵,功耗较大。

DSP系统的运算量1.按样点处理:即DSP算法对每一个输入样点循环一次。

2.按帧处理:针对DSP算法不是每个输入样点循环一次,而是每隔一定的时间间隔(即帧)循环一次。

第二章DSP芯片的基本结构大致分为CPU算术逻辑单元(ALU)、累加器(ACC)、乘累加单元(MAC)移位寄存器、寻址单元等存储器包括片内ROM、Flash、SARAM、DARAM等集成外设和专用硬件电路包括片内串行接口、主机接口、定时器、时钟发生器、锁相环及各种控制电路。

总线用于传送指令和数据;在CPU与存储器、集成外设和专用硬件电路等部分之间。

寻址方式1.程序寻址程序计数器PC:由程序地址产生单元产生。

例如,TMS320C54x 系列DSP芯片的PAGEN。

①包含需要取指的下一条指令所在的程序存储器地址,一般在存储器地址中按顺序产生;②当执行到子函数调用、中断时,将用相应的子函数入口地址或中断ISR入口地址来加载PC;③当执行到跳转语句时,会使用相应的跳转地址来加载PC。