PCB经典层叠

PCB叠层设计层的排布原则和常用层叠结构

PCB叠层设计层的排布原则和常用层叠结构叠层设计层的排布原则和常用层叠结构在设计多层PCB板之前,设计者需要首先按照电路的规模、电路板的尺寸和电磁兼容()的要求来确定所采纳的电路板结构,也就是打算采纳4层,6层,还是更多层数的电路板。

确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信号。

这就是多层PCB层叠结构的挑选问题。

层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。

本文介绍多层PCB板层叠结构的相关内容。

对于电源、地的层数以及信号层数确定后,它们之间的相对排布位置是每一个PCB工程师都不能回避的话题;层的排布普通原则:1、确定多层PCB板的层叠结构需要考虑较多的因素。

从布线方面来说,层数越多越利于布线,但是制板成本和难度也会随之增强。

对于生产厂家来说,层叠结构对称与否是PCB板创造时需要关注的焦点,所以层数的挑选需要考虑各方面的需求,以达到最佳的平衡。

对于有阅历的设计人员来说,在完成元器件的预布局后,会对PCB的布线瓶颈处举行重点分析。

结合其他工具分析电路板的布线密度;再综合有特别布线要求的信号线如差分线、敏感信号线等的数量和种类来确定信号层的层数;然后按照电源的种类、隔离和抗干扰的要求来确定内电层的数目。

这样,囫囵电路板的板层数目就基本确定了。

2、元件面下面(其次层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;敏感信号层应当与一个内电层相邻(内部电源/地层),利用内电层的大铜膜来为信号层提供屏蔽。

电路中的高速信号传输层应当是信号中间层,并且夹在两个内电层之间。

这样两个内电层的铜膜可以为高速信号传输提供电磁屏蔽,同时也能有效地将高速信号的辐射限制在两个内电层之间,不对外造成干扰。

3、全部信号层尽可能与地平面相邻;4、尽量避开两信号层挺直相邻;相邻的信号层之间简单引入串扰,从而导致电路功能失效。

在两信号层之间加入地平面可以有效地避开串扰。

关于PCB叠层理解

关于PCB叠层的理解设计者可能会设计奇数层印制电路板(PCB)。

如果布线不需要额外的层,为什么还要用它呢?难道减少层不会让电路板更薄吗?如果电路板少一层,难道成本不是更低么?但是,在一些情况下,增加一层反而会降低费用。

电路板有两种不同的结构:核芯结构和敷箔结构。

在核芯结构中,电路板中的所有导电层敷在核芯材料上;而在敷箔结构中,只有电路板内部导电层才敷在核芯材料上,外导电层用敷箔介质板。

所有的导电层通过介质利用多层层压工艺粘合在一起。

核材料就是工厂中的双面敷箔板。

因为每个核有两个面,全面利用时,PCB的导电层数为偶数。

为什么不在一边用敷箔而其余用核结构呢?其主要原因是:PCB的成本及PCB的弯曲度。

偶数层电路板的成本优势因为少一层介质和敷箔,奇数PCB板原材料的成本略低于偶数层PCB。

但是奇数层PCB的加工成本明显高于偶数层PCB。

内层的加工成本相同;但敷箔/核结构明显的增加外层的处理成本。

奇数层PCB需要在核结构工艺的基础上增加非标准的层叠核层粘合工艺。

与核结构相比,在核结构外添加敷箔的工厂生产效率将下降。

在层压粘合以前,外面的核需要附加的工艺处理,这增加了外层被划伤和蚀刻错误的风险。

平衡结构避免弯曲不用奇数层设计PCB的最好的理由是:奇数层电路板容易弯曲。

当PCB在多层电路粘合工艺后冷却时,核结构和敷箔结构冷却时不同的层压张力会引起PCB弯曲。

随着电路板厚度的增加,具有两个不同结构的复合PCB弯曲的风险就越大。

消除电路板弯曲的关键是采用平衡的层叠。

尽管一定程度弯曲的PCB达到规范要求,但后续处理效率将降低,导致成本增加。

因为装配时需要特别的设备和工艺,元器件放置准确度降低,故将损害质量。

使用偶数层PCB当设计中出现奇数层PCB时,用以下几种方法可以达到平衡层叠、降低PCB制作成本、避免PCB弯曲。

以下几种方法按优选级排列。

1.一层信号层并利用。

如果设计PCB的电源层为偶数而信号层为奇数可采用这种方法。

常用pcb叠层

2.0 +0.2/-0.2(mm)

单线-线宽、阻抗、参考层控制信息

线宽 的计量单位为mil,阻抗的计量单位为ohm

单线

层标识 设计线宽 设计阻抗 调整线宽 调整阻抗

1/10

6

50+/-10%

5.5

50.931

3/4/7/8

6

50+/-10%

6

49.939

参考层 2/9

1 Core

1 PP

0.333_Plating PP

0.333+Plating 客户设计板厚: 厂家理论板厚:

PCB厂家设计调整(oz/mil)

介质厚度

层叠图示

3.6 5.21 3.94 5.21 5.59 16.14 5.59 5.21 3.94 5.21 3.6

0.333+Plating pp(3313)

2&5 6&9

差分线-线宽/线距、阻抗、参考层控制信息

线宽、线距 的计量单位为mil,阻抗的计量单位为ohm

差分线

层标识 设计宽/距 设计阻抗 调整线宽/线距 调整阻抗

1/10

6/8

100+/-10%

4.7/9.3

100.722

NOTE): ar2510121z

参考层 2/9

2021/4/3

z/mil)

假层 DK值 使用

) .2(mm)

3.9 3.65 4.2 3.65 3.65 3.65 3.65 4.2 3.65 3.9

层叠阻抗信息确认表单

Material :

TU768

Date:

层叠控制信息

层标识 Top P2 S3 S4 P5

PCB层叠设计的关键要点汇总

层叠设计的关键要点汇总1、层叠设计的最后一个层次接上一篇文章说的层叠设计的最后一个层次,其实这是一个开放性题目,非要让大家按照我固定的封闭思路答题,是不公平的。

所以我在上周的点评才说是“任性”一次。

不过也还是有朋友的回答和我想的一样,先握个手。

第3层次,不仅同时提供阻抗需求表以及层叠设计表,同时还要详细指定每一层的材料型号。

比如铜箔是采用RTF铜箔还是VLP铜箔,1-2层之间是使用2张1080,RC 含量为XX。

2-3层之间是Core芯板,是XX型号,等等。

如下图所示:有人会问:为什么要详细到这个程度?我又不是板厂的ME工程师!这个层次不是所有的项目都需要达到的,一般是推荐10G Bps+的系统,采用了低损耗板材或者超低损耗板材的时候,由于材料对信号的影响变得更加显著,需要关注到铜箔的粗糙度以及玻璃纤维布的编制效应等。

2、层叠设计的关键要点所以,层叠设计的第一个关键要点其实已经揭示答案了:要了解板材的基本知识。

其实就算是上文提到的阻抗控制设计的第2层次,虽然不用制定铜箔及玻纤布型号,但是也需要了解材料的基本知识,知道Core芯板一般都有哪些厚度,知道什么是3313、2116……以及不同型号玻纤布的DK、DF参数等。

这不,高速先生微信群有人提问了:生益S1000的材料,算阻抗的时候,DK应该取什么值呢?所以大家注意了,高速先生是有微信群的,平常可以沟通交流技术问题,欢迎大家后台联系管理员加入哈。

下面来看一下TU872 SLK的详细Datasheet,在1G Hz的时候,不同型号的芯片,DK可以从3.48到4.0。

这么大的差异,对我们阻抗计算以及仿真都会带来影响,不能忽视。

那层叠设计还有其他哪些关键要点呢?信号回流与参考平面布线层数规划,这个是确定一个板子设计多少层的前提因素,我们的高速小姐刘为霞会在后续文章详细解释电源、地层数的规划层间串扰以及双带线的设计跨分割的影响,如何考虑信号跨分割下图是本系列层叠设计文章的大致计划,用脑图的方式来规划高速先生的文章,是不是很高大上的感觉?。

PCB叠层

PCB叠层1层叠的定义及添加对高速多层板来说,默认的两层设计无法满足布线信号质量及走线密度要求,这个时候需要对PCB层叠进行添加,以满足设计的要求。

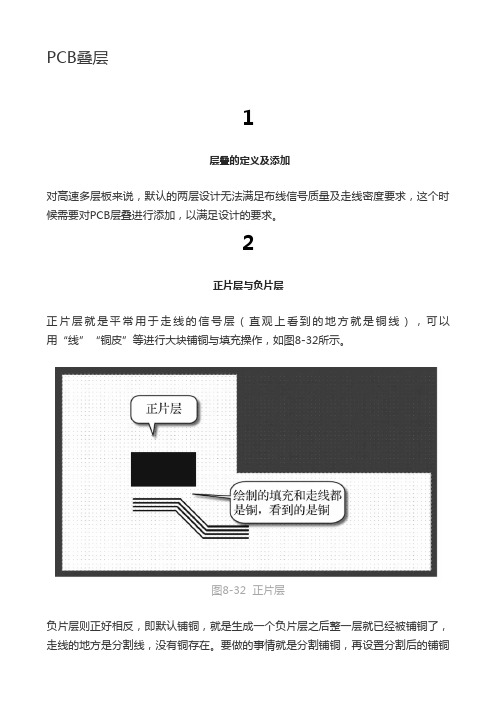

2正片层与负片层正片层就是平常用于走线的信号层(直观上看到的地方就是铜线),可以用“线”“铜皮”等进行大块铺铜与填充操作,如图8-32所示。

图8-32 正片层负片层则正好相反,即默认铺铜,就是生成一个负片层之后整一层就已经被铺铜了,走线的地方是分割线,没有铜存在。

要做的事情就是分割铺铜,再设置分割后的铺铜的网络即可,如图8-33所示。

图8-33 负片层3内电层的分割实现在Protel版本中,内电压是用“分裂”来分割的,而现在用的版本Altium Designer 19直接用“线条”、快捷键“PL”来分割。

分割线不宜太细,可以选择15mil及以上。

分割铺铜时,只要用“线条”画一个封闭的多边形框,再双击框内铺铜设置网络即可,如图8-34所示。

图8-34 双击给予网络正、负片都可以用于内电层,正片通过走线和铺铜也可以实现。

负片的好处在于默认大块铺铜填充,再进行添加过孔、改变铺铜大小等操作都不需要重新铺铜,这样省去了重新铺铜计算的时间。

中间层用电源层和GND层(也称地层、地线层、接地层)时,层面上大多是大块铺铜,这样用负片的优势就很明显。

4PCB层叠的认识随着高速电路的不断涌现,PCB的复杂度也越来越高,为了避免电气因素的干扰,信号层和电源层必须分离,所以就牵涉到多层PCB的设计。

在设计多层PCB之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层、6层,还是更多层数的电路板。

这就是设计多层板的一个简单概念。

确定层数之后,再确定内电层的放置位置及如何在这些层上分布不同的信号。

这就是多层PCB层叠结构的选择问题。

层叠结构是影响PCB的EMC性能的一个重要因素,一个好的层叠设计方案将会大大减小电磁干扰(EMI)及串扰的影响。

PCB叠层设计层的排布原则和常用层叠结构

PCB叠层设计层的排布原则和常用层叠结构

一、PCB叠层设计层的排布原则

1、符合设计要求

PCB的叠层设计层要符合系统的结构要求,如信号传输、控制线路、

电源线路等。

这些要求具体取决于系统的功能和特点,要根据系统的需求

做出具体的叠层设计。

2、选择合适的铜厚度

叠层的设计要根据系统的参数,如电源电压和负载,确定线路的电阻

和电容,并估算线路的截面积。

根据截面积和PCB板材的铜厚度,确定叠

层设计中适当的铜厚度。

3、信号传输需求

叠层的设计需要考虑信号传输的需求,包括信号传输的速度、范围和

灵敏度。

线路的长度、铜厚度和布线方式,均会影响信号的传输特性。

因此,在叠层设计中要充分考虑信号传输的需求,进行合理的设计。

4、传输功耗过大

在进行叠层设计时,要注意线路的连接方式,避免节点功耗过大,以

免引起线路内部温度升高,影响系统的稳定性和可靠性。

5、保证叠层间的绝缘性

在PCB的叠层设计中,要注意保证叠层间的绝缘性,避免接触和短路。

这不仅有利于线路的正常工作,也有助于降低功耗,提高系统性能。

1、4层PCB

4层 PCB(4 Layer PCB)是一种常见的PCB叠层结构。

pcb叠层结构知识

pcb叠层结构知识(汇总)2011-11-16 13:58:14标签:休闲多层板职场随着高速电路的不断涌现,PCB板的复杂度也越来越高,为了避免电气因素的干扰,信号层和电源层必须分离,所以就牵涉到多层PCB 的设计。

在多层板的设计中,对于叠层的安排显得尤为重要。

一个好的叠层设计方案将会大大减小EMI及串扰的影响,在下面的讨论中,我们将具体分析叠层设计如何影响高速电路的电气性能。

一.多层板和铺铜层(Plane)多层板在设计中和普通的PCB板相比,除了添加了必要的信号走线层之外,最重要的是安排了独立的电源和地层(铺铜层)。

在高速数字电路系统中,使用电源和地层来代替以前的电源和地总线的优点主要在于:1.为数字信号的变换提供一个稳定的参考电压。

2.均匀地将电源同时加在每个逻辑器件上3.有效地抑制信号之间的串扰原因在于,使用大面积铺铜作为电源和地层大大减小了电源和地的电阻,使得电源层上的电压很均匀平稳,而且可以保证每根信号线都有很近的地平面相对应,这同时减小了信号线的特征阻抗,对有效地较少串扰也非常有利。

所以,对于某些高端的高速电路设计,已经明确规定一定要使用6层(或以上的)的叠层方案,如Intel对PC133内存模块PCB板的要求。

这主要就是考虑到多层板在电气特性,以及对电磁辐射的抑制,甚至在抵抗物理机械损伤的能力上都明显优于低层数的PCB板。

如果从成本的因素考虑,也并不是层数越多价格越贵,因为PCB板的成本除了和层数有关外,还和单位面积走线的密度有关,在降低了层数后,走线的空间必然减小,从而增大了走线的密度,甚至不得不通过减小线宽,缩短间距来达到设计要求,往往这些造成的成本增加反而有可能会超过减少叠层而降低的成本,再加上电气性能的变差,这种做法经常会适得其反。

所以对于设计者来说,一定要做到全方面的考虑。

二.高频下地平面层对信号的影响如果我们将PCB的微带布线作为一个传输线模型来看,那么地平面层也可以看成是传输线的一部分,这里可以用“回路”的概念来代替“地”的概念,地铺铜层其实是信号线的回流通路。

AM2-780G 主板pcb层叠结构与阻抗控制

AM2-780G 主板pcb 层叠结构与阻抗控制一、参考层叠 1. 层叠图示阻焊绿油0.3~0.7mil 厚度Top 层厚度为2.0mil 铜(电镀之后) 1x3313 Pre-Preg 压合厚度 3.7mil 内层厚度 1.4mil 铜中间调节约48mil ,确保整板厚度为1.6mm 内层厚度 1.4mil 铜1x3313 Pre-Preg 压合厚度 3.7milBottom 层厚度为2.0mil 铜(电镀之后) 阻焊绿油0.3~0.7mil 厚度2. Pcb 板材要求Pcb 板材: Fr-4, Er= 4.0 @ 1.0GHz 3313PP 4mil 压合控制厚度为 3.7mil 整板厚度:63mil ±5mil ( = 1.6mm )二、控制阻抗线在pcb 上的位置图示1.CLKIN – CPU ( Clock IC to CPU ) 时钟差分对阻抗要求W/S1/S2 = 5mil/6mil/20mil阻抗控制要求预控制阻抗的线位置图示2.HT—CLK ( Clock IC to NB ) 时钟差分对阻抗要求W/S1/S2 = 5mil/7mil/20mil阻抗控制要求预控制阻抗的线位置图示3.HT—CAD、CTL (NB to CPU) 差分对阻抗要求W/S1/S2 = 4.5mil/5mil/16mil阻抗控制要求预控制阻抗的线位置图示W/S1/S2 = 5mil/5mil/16mil 阻抗控制要求预控制阻抗的线位置图示W/S1/S2 = 5mil/5mil/16mil 阻抗控制要求预控制阻抗的线位置图示6.DDR3—Addr、CMD、CTL (CPU to DIMM) 单端阻抗要求W = 9.5mil阻抗控制要求预控制阻抗的线位置图示7.DDR3—Data (CPU to DIMM) 单端阻抗要求W = 9.5mil阻抗控制要求预控制阻抗的线位置图示8.PCIEx16—GFX (NB to PCIEx16) 差分对阻抗要求W/S1/S2 = 5mil/5mil/16mil阻抗控制要求预控制阻抗的线位置图示9.PCIEx16 – REFCLK ( Clock IC to LAN, PCIEx16, SB and NB) 差分对阻抗要求W/S1/S2 = 5mil/5mil/16mil阻抗控制要求预控制阻抗的线位置图示10.HIS/HSO ( NB to LAN) 差分对阻抗要求W/S1/S2 = 5mil/5mil/16mil阻抗控制要求预控制阻抗的线位置图示N – MDI 差分对阻抗要求W/S1/S2 = 5mil/6mil/20mil阻抗控制要求预控制阻抗的线位置图示W/S1/S2 = 5mil/5mil/16mil 阻抗控制要求预控制阻抗的线位置图示W/S1/S2 = 5mil/5mil/16mil 阻抗控制要求预控制阻抗的线位置图示14.DMI ( SB to NB )差分对阻抗要求W/S1/S2 = 5mil/6mil/20mil阻抗控制要求预控制阻抗的线位置图示15.PCICLK (Clock to NB,SN,PCI,and IO)单线时钟阻抗要求W = 5mil阻抗控制要求预控制阻抗的线位置图示16.AUDIO 时钟、数据线阻抗要求W = 5mil阻抗控制要求预控制阻抗的线位置图示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCB 经典层叠

图5.24 到5.26 举例说明了分别为4 层、6 层和10 层的三个板子的经典叠层布局。

在下面描述的这些双层设计中,使用通常的环氧的环氧树脂多层制造方法,超过了10 层、设计者通常结合使用另外的地平面隔离布线层。

这些叠层适用于高速计算机产品,嵌入在屏蔽很好的板卡机架里,如果系统必须通过FCC,VDE,TENPEST 或其他的电磁辐射标准,并且没有屏蔽很好的板卡机架,那幺这些简单的叠层对达到你的目的的还是不充分的。

在每个图中,提到的水平由线的垂直布线是指该层的走线方向。

通常每层上的走线由放时彼此平行,并且与同它相邻一层的布线垂直。

在同一层上,很少有线走对角线,或者拐一个90 度的弯。

这一原则会增加布线的效率。

在图5.24 到图5.26 中,电源和地层以粗实线标识。

走线层按比例表示走线宽度和走线高度。