数字电子技术基础论文

电子类论文范文

电子类论文范文电子类专业是应用性极强的专业,根据电子信息产业的行业特点,培养学生应具有两个方面的职业能力:一是具有电子产品和设备生产第一线的操作和制作能力;二是具有电子产品和设备的设计能力。

下面是店铺为大家整理的电子类论文,供大家参考。

电子类论文范文一:数字电子技术思维导图教学研究摘要:“数字电子技术”是电子、通信类专业本科生的一门重要的专业基础课。

文章针对传统教学中存在的问题,结合自身教学体会,提出了将思维导图引入到“数字电子技术”课程教学中的新方法,并结合教学案例进行了探讨。

经实践表明,思维导图提高了学生的学习兴趣,有利于学生构建知识网络,提高了学习效率。

关键词:数字电子技术;思维导图;教学案例专业基础课程,在整个课程体系中占有重要地位,为后续如单片机原理与应用、微机原理、传感器与检测技术等课程的学习提供理论基础。

该课程具有自身的系统性和实践性,知识点繁多,学生在学习过程中由于对知识点的掌握较为片面,缺乏系统性,容易造成“断章取义”、“不求甚解”的现象。

因而,有必要在教学过程中融入新思想、新方法,帮助学生构建知识体系,提高学习效率。

1教学现状分析当前,各高校均开设有“数字电子技术”课程,大部分仍然属于传统的教学方法,结合笔者在教学过程的一些体会,认为存在如下几个共性问题:(1)教材知识脉络不够清晰。

应用型本科院校选用的教材大都是围绕数字逻辑基础、基本逻辑门、组合逻辑电路、时序逻辑电路、脉冲波形产生与变换几大部分,各自独立成为章节,逐层递进、由浅入深、依次学习。

这样的编排虽然较为全面,但各章节知识点之间的联系不够紧密,学生反映在学习过程中存在“前面学了后面忘”的现象。

(2)课程信息量大,笔记跟不上。

信息化时代,大学课程的教学大多采用多媒体教学形式,即教师边讲解边使用ppt课件播放教学内容,这与传统的板书教学相比具有其优越性,但也不可避免的存在一些缺陷,比如重点内容一闪而过,学生记笔记跟不上,课后对照课件进行复习,又加重了学习任务。

数电论文

组合电路中的竞争冒险【摘要】在组合电路中,当输入信号改变状态时,输入端可能出现过渡干扰脉冲的现象,如果负载是对脉冲信号十分敏感的电路,那可能会影响整个电路的功能。

那么,了解这种现象产生的原因、判断方法以及消除这种现象就具有重要的意义。

【关键词】竞争冒险,冒险现象的识别,消除方法。

【主题】数字电路中有时候会出现竞争冒险,冒险功耗是由电路达到稳态之前的跳变引起的功耗,了解它的产生原因并学会竞争冒险的判断方法避免和消除这种现象是降低电路功耗的一个重要手段。

对电路的正常工作和低功耗设计都具有至关重要的意义。

【内容】一、产生竞争冒险现象的原因由于延迟时间的存在,当一个输入信号经过多条路径传送后又重新会合到某个门上,由于不同路径上门的级数不同,或者门电路延迟时间的差异,导致到达会合点的时间有先有后,从而产生瞬间的错误输出。

这一现象称为竞争冒险。

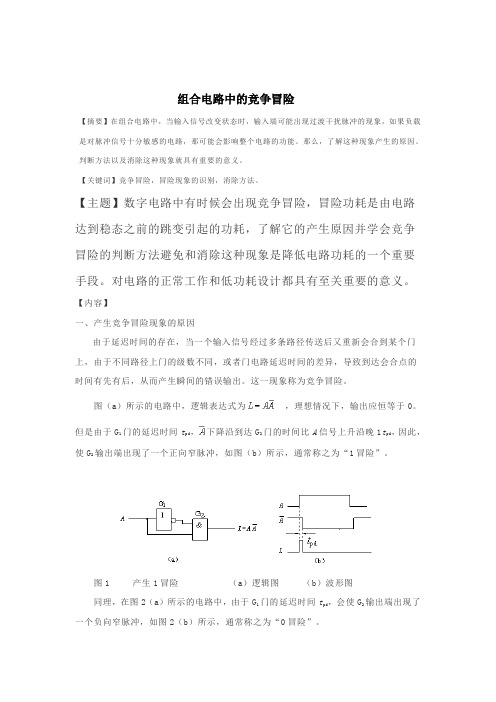

图(a)所示的电路中,逻辑表达式为,理想情况下,输出应恒等于0。

但是由于G1门的延迟时间t pd,下降沿到达G2门的时间比A信号上升沿晚1t pd,因此,使G2输出端出现了一个正向窄脉冲,如图(b)所示,通常称之为“1冒险”。

图1 产生1冒险(a)逻辑图(b)波形图同理,在图2(a)所示的电路中,由于G1门的延迟时间t pd,会使G2输出端出现了一个负向窄脉冲,如图2(b)所示,通常称之为“0冒险”。

图2 产生0冒险(a)逻辑图(b)波形图“0冒险”和“1冒险”统称冒险,是一种干扰脉冲,有可能引起后级电路的错误动作。

产生冒险的原因是由于一个门(如G2)的两个互补的输入信号分别经过两条路径传输,由于延迟时间不同,而到达的时间不同。

这种现象称为竞争。

1、竞争现象任何一个门电路都具有一定的传输延迟时间t,即当输入信号发生突变时,输出信号不可能跟着突变,而要滞后一段时间变化。

由于各个门的传输时间差异,或者输入信号通过的路径(即门的级数)不同造成的传输时间差异,会使一个或几个输入信号经不同的路径到达同一点的时间有差异。

数字电子技术(5篇)

数字电子技术(5篇)数字电子技术(5篇)数字电子技术范文第1篇(一)USB总线微波功率计中数字电子技术的应用USB总线微波功率计主要包括USB通信接口、微信号接收检测电路等内容组成,该仪器充分借助数字电子技术开发相应软件系统,从而使得该虚拟仪器有效实现微波功率采集、测量和传输功能。

USB总线微波功率计中探测器采集到目标微波功率信号后,该设备中微信号检测电路芯片就会对目标信号进行去噪、累加、求差值等等处理,并调整修改信号数据固定程度,最终通过USB通信接口将处理完毕信息传送到上位机,该上位机程序系统就会对该数据进行分析处理。

鉴于该总线微波功率计充分应用了数字电子技术中强大信号处理传输技术,使得该功率计不仅小巧易携带,操作简洁,PC机适用匹配性强,还具备高精度的测量效果,因此饱受专业人员宠爱。

(二)雷达接收机上数字电子技术的应用雷达是军民两用的,具备高要求和高标准的高精度电子设备,而日趋成熟完善的数字电子技术也在精密的雷达生产制造过程中起到其中的作用。

作为雷达,其主要就是搜寻捕获目标信号,因此其必需具备剧烈的抗干扰性,也就是说雷达信号接收设备就必需具备灵敏性强、频段高性能,而数字接收机就基于这一点顺当胜利取代了现代雷达中模拟接收器的地位。

雷达接受机中数字接收机高指标的数字变频滤波技术和I/Q解调技术充分使得雷达接收器的有用性和精确性得到提高,也充分呈现出数字电子技术应用的优越性。

有此可以看出数字电子技术突出的抗干扰、无噪声、易交换储存及处理、能够将设备集成化、微型化的特性在网络信息时代,也会在计算机信号和计算机数字联网方面得到充分应用,从促使网络通信管理实现智能化和自动化,这都需要数字电子技术和网络信息技术的综合支持和进展。

二、数字电子技术将来进展方向和趋势当前网络信息技术加快了全球信息化时代的到来,社会市场进展需求直接推动了电子技术行业的进展进程,而其中数字电子技术更是成为信息时代技术行业市场的生力军,不断促使经济行业产业的更新升级,还使得数字电子技术和信息技术向着更高层次平台前进,可以说数字电子技术是随着市场需求而不断进展进步的,电子技术数字化和信息化已经成为电子技术领域进展主流,也是当前相关行业的普遍共识。

数字电子技术论文15篇(网络中数字电子技术的应用)

数字电子技术论文15篇网络中数字电子技术的应用数字电子技术论文摘要:数字电子技术是科技发展与社会进步的必然产物,近年来,数字电子技术有了很大的发展,并且在人们生活工作的各个方面都得到了广泛的应用,尤其在网络中的应用有着更为重要的作用,它不仅实现了信息的高速流通,而且推动了网络技术的进步和发展。

相信在未来科技的发展中,还将赋予电子技术更多的应用与创新。

关键词数字电子技术电子论文电子数字电子技术论文:网络中数字电子技术的应用【摘要】当今社会,我们处在一个信息技术不断更新换代的时代,信息技术已经成为人们现实生活中不可或缺的一部分。

本文在论述数字电子技术在网络中的基本特征的前提下,指出了数字电子技术在网络中的作用,分析了网络的优势特点,明确了数字电子技术在网络中的应用,为今后数字电子技术在网络中的应用和研究奠定了坚实的基础,促进了网络信息技术的进步和发展。

【关键词】数字电子技术;网络;应用分析网络是电子技术重要的工作环境和信息平台,在网络技术环境下,电子技术可以通过自身优势将人们的生产生活联系起来,进而推动网络技术应用的进一步普及和发展。

一、数字电子技术在网络中的基本特征1.网络搜索与查找具有时间性搜索与查找是网络出现伊始人们赋予其的主要作用和功能,对于时间概念的要求相对较低,网络的时间性可以利用其它途径展现出来,一是利用网络的对应性特征,网络内容具有对应性是网络的基本特征,发挥网络内容对应性优势满足人们对于网络的基本要求;二是网络具有开放性特点,网络世界包罗万象,不仅可以查找自身的有关信息,也可以利用网络的交互性优势,查找所有与之相关的信息内容,使得查找内容更加整体性特征明确,为人们快捷有效的查找信息提供了便利。

2.网络信息的多种呈现形式网络信息世界宽广犹如大海,信息的种类和内容也是多种多样的,文字、视频、音频等都可以是网路信息世界的重要组成部分。

人们在利用网络查找信息资源时,可以根据自己的实际需求,自主的搜索所需要的各类资源。

数字电子技术基础2篇

数字电子技术基础2篇数字电子技术基础是现代电子技术中的重要基础知识之一。

数字电子技术基础主要包括数字电路基础和数字系统基础两个部分。

本篇文章将首先简要介绍数字电路基础的知识,然后详细讲解数字系统基础的相关内容。

第一篇:数字电路基础数字电路基础是研究数字电子技术的基本理论和方法。

数字电路是由逻辑门和触发器等基本电子器件组成的电路,它能够实现电信号的逻辑运算和存储功能。

数字电路的设计与应用广泛应用于计算机、通信、控制等领域。

在数字电路基础的学习中,我们首先需要了解数字电路的基本概念和特点。

数字电路中的电信号只有两个状态,即高电平和低电平。

这种特点使得数字电路具有高抗干扰性和稳定性,能够进行精确的逻辑运算。

数字电路中的基本逻辑门有与门、或门、非门等,这些逻辑门可以实现与、或、非等基本逻辑运算。

此外,数字电路中还包括多路选择器、译码器、编码器等组合逻辑电路和触发器、计数器等时序逻辑电路。

学习数字电路基础的过程中,我们需要掌握数字电路的分析与设计方法。

数字电路的分析包括对数字电路进行真值表和逻辑方程的推导,以及利用卡诺图进行逻辑化简。

而数字电路的设计则包括将逻辑运算表达式转化为逻辑电路图的过程,以及根据设计要求选择适合的电子器件进行布线的过程。

掌握了数字电路基础的知识后,我们就能够进行数字电路的实际应用。

数字电路应用广泛,其中一个重要的应用领域就是计算机。

计算机中的运算器、控制器、存储器等部分都是由数字电路构成的。

此外,数字电路还广泛应用于通信、控制、仪器仪表等领域。

通过了解和应用数字电路,我们可以更好地理解和掌握现代电子技术。

第二篇:数字系统基础数字系统基础是研究数字系统的基本理论和方法。

数字系统是用数字电子技术构成的具有特定功能的系统,由多个数字电路组成。

数字系统可以进行逻辑运算、数据处理、信息存储和传输等功能。

数字系统的设计与应用在现代电子领域中具有广泛的应用。

在数字系统基础的学习中,我们首先需要了解数字系统的组成和结构。

数字电子技术基础

数字电子技术基础第一篇:数字电子技术基础数字电子技术是现代电子技术的重要组成部分,它利用数字信号进行信息传输和处理,广泛应用于计算机、通信、工业控制、医疗设备等领域。

本篇文章将介绍数字电子技术基础中的数字信号、逻辑门、组合逻辑电路和时序逻辑电路四个方面。

一、数字信号数字信号是一种离散的信号,包括两个离散的取值,一般用0和1表示。

数字信号可以通过模拟-数字转换器(ADC)将模拟信号转换为数字信号,也可以通过数字-模拟转换器(DAC)将数字信号转换为模拟信号。

数字信号的优点是抗干扰能力强、可靠性高、易于处理和传输等。

在数字电子技术中,数字信号是信息处理和传输的基础。

二、逻辑门逻辑门是数字电路的基本组成部分,它是由电子器件构成的逻辑电路,用于进行逻辑运算。

逻辑门有与门、或门、非门、与非门、或非门、异或门等多种类型,它们的逻辑运算结果只有0和1两种。

逻辑门的输出信号可作为输入信号进入其他逻辑门,以实现更复杂的逻辑运算。

逻辑门广泛应用于数字电路的设计和实现中。

三、组合逻辑电路组合逻辑电路是由逻辑门组成的电路,其输出只与当前输入有关,不受历史输入的影响。

组合逻辑电路通常用于实现逻辑运算和算术运算,如加法器、减法器、多路选择器等。

组合逻辑电路的设计和实现需要对逻辑门的逻辑运算规律进行深入理解和熟练掌握。

四、时序逻辑电路时序逻辑电路是由组合逻辑电路和触发器组成,其输出不仅与当前输入有关,还与历史输入有关。

时序逻辑电路常用于定时器、计数器、状态机等应用场合,其设计和实现需要对触发器的工作原理和时序逻辑电路的时序分析有深入的认识。

综上所述,数字电子技术基础包括数字信号、逻辑门、组合逻辑电路和时序逻辑电路四个方面。

掌握数字电子技术基础是进行数字电路设计和实现的基础,对于提升电子技术水平和应用能力具有重要的意义。

第二篇:数字电子技术基础中的应用数字电子技术在现代社会中应用广泛,涉及计算机、通信、工业控制、医疗设备等多个领域。

数字电子技术论文

《数字电子技术》是电子、电气和信息类专业的专业基础核心课程,是后续专业课程学习的基础。

下面是为大家精心推荐的,希望能够对您有所帮助。

篇一浅谈《数字电子技术》课程改革摘要:本文阐述了《数字电子技术》课程改革的理念和思路,罗列了项目驱动的模块教学内容,以及每个模块的教学方法和手段,并在课程资源,课程考核方面作了改革。

关键词:理念和思路;项目驱动;教学方法和手段《数字电子技术》是电子、电气和信息类专业的专业基础核心课程,是后续专业课程学习的基础。

在整个课程体系中处于重要地位。

该课程具有较强的理论性、应用性和实践性。

特别是在职业院校中,课程的应用性、实践性更应凸显,本文针对课程自身的特点和规律,结合我校该课程的教改推行,就以下几方面浅谈如下: 1改变教学理念和思路传统的数字电子技术教学方法,一直沿用以理论教学为主的模式。

教师按照传统的“一支粉笔、一块黑板”模式讲授,最多再在数码箱上验证书本上的理论知识。

针对教材内容和实际应用联系不够,职业岗位技能没有得到真正提高等问题,我们提出的思路是: 1自编适合高职院校特点的教材,把课程所需的知识点融进实际任务中,以任务引领教学。

2在教学过程中,采用理论和实践相结合的原则,把教、学、做、验、仿融为一体。

3提高学生学习兴趣,由被动学习转变为主动学习。

4改变考核方式,注重过程考核,课程成绩的评定由学生的作品、平时的表现、知识点考核、职业技能等多方面组成。

2优化教学内容本课程主要以数字逻辑基础模块、逻辑门电路模块、组合逻辑电路模块、时序逻辑电路模块、综合模块为基本内容展开学习,这些模块涵盖了数电的主要内容,并自行设计贴近实际又主要涵盖课程内容的工作任务,以工作任务为职业知识的载体,尽可能将相关知识点分解在各个任务中,强调了工作任务和知识点的联系,工作任务和实际应用的联系,工作任务和职业技能的联系。

具体内容安排如右上表:3改进教学方法和手段在教学方法和手段上,我们根据具体内容的特点,由课堂教学为主的;由制作实物任务驱动的;由在数码箱上验证任务知识点的;由通过EWB软件仿真综合任务的,真正把教、学、做、验、仿融到了整个教学中。

数字电子技术实训论文(倒计时)

数字电子技术(论文)说明书题目:系别:机电工程系专业:机电一体化学生姓名:学号:指导教师:职称:高级工程师题目类型:理论研究软件开发2010 年7 月9 日摘要本次实训,要求做的是一个6位的“时”,“分”,“秒”的数字显示的倒计时装置。

但是由于时间,以及一些其他的原因,原本要做成的6位数码显示的倒计时装置,只做了2位,但是,在仿真系统中,我们也做成了3位的倒计时器,并附有图在论文中。

本系统主要由555多谐振荡器、计数器、译码器、数码管,采用74LS系列(双列直插式)中小规模集成芯片组成,文中会介绍各种芯片及电路的原理。

本次实训最后做成的电路板实现99秒2位倒计时,还带有1个复位键,当复位键按下时,倒计时器回到99秒重新倒计时。

关键词:芯片;74LS192;74LS48;555定时器;数码管;译码;计数;AbstractThis practice is a requirement, the six "time", and "points", "second" digital display the countdown device. But because of the time, and some other reasons, which made the countdown six digital display device, made only two, but, in the simulation system, we also make a counter-down and the attached figure in the thesis. This system mainlyconsists of 555 more harmonic oscillator, counter, decoder, digital tube, using 74LS series (double row inline) medium scale integration chip will introduce various component, the principle and the circuit chip. The practice of last two seconds realization circuit 99, still contain a countdown to reset when reset button press, counter-down back to 99 seconds to countdown.Key words:chip;74LS192;74LS48 ;555 timer equipment ;digital tube;decode;count;目录引言 (4)1 电路原理设计 (5)1.1 设计思路(小四号黑体) (5)1.2 设计原理图(小四号黑体) (5)2 各个电路设计分析 (6)2.1 多谐振荡电路 (6)2.2 设计原理图 (7)2.3 译码电路 (9)2.4数码管结构及原理 (11)3 仿真电路 (12)4 电路总设计图 (13)4.1 计时部分 (13)4.2 译码部分及数码管显示部分 (14)4.3 短路总图 (14)4.4 PCB电路板 (15)5成品及调试 (15)5.1 成品 (15)5.2 调试 (16)6结论 (16)7实训心得体会 (16)谢辞 (17)参考文献 (18)附录 (19)引言随着社会科学技术的迅速发展,人们对时间的把握要求越来越高,也有很多地方用到了倒计时的电路。

数字电子技术基础(杨颂华)

数字电子技术基础随着科技的飞速发展,数字电子技术已经成为我们日常生活和工作中不可或缺的一部分。

它不仅影响着我们的生活方式,还推动着社会的进步。

本教材将带领大家走进数字电子技术的世界,探索其原理和应用。

数字电子技术是研究数字信号的产生、传输、处理和存储等方面的技术。

它涉及到电子学、计算机科学、通信技术等多个领域。

通过学习数字电子技术,我们可以了解电子设备的内部结构和工作原理,掌握数字电路的设计方法,以及数字信号的处理技术。

在数字电子技术中,数字信号是关键的概念。

与模拟信号相比,数字信号具有更高的稳定性和抗干扰能力。

数字信号通过0和1的编码方式,将信息转换为一串二进制序列,从而实现信息的传递和存储。

数字信号的处理和分析,是数字电子技术的核心内容。

数字电子技术的基础是数字电路。

数字电路是由各种逻辑门电路组成的,它们可以实现对数字信号的逻辑运算和数据处理。

通过组合不同的逻辑门电路,可以设计出各种复杂的数字电路系统,如计算机、通信设备等。

除了数字电路,数字信号的处理技术也是数字电子技术的重要组成部分。

数字信号处理技术涉及到信号的采样、量化、滤波、编码和解码等过程。

通过对数字信号进行处理,可以提高信号的传输质量和抗干扰能力,实现更高效的信息传输和存储。

数字电子技术是现代科技的基础,它为我们的生活和工作带来了巨大的便利。

通过学习数字电子技术,我们可以更好地理解电子设备的工作原理,掌握数字电路的设计方法,以及数字信号的处理技术。

这将为我们未来的学习和工作打下坚实的基础。

数字电子技术基础数字电子技术是现代科技的重要基石,它涉及到电子学、计算机科学、通信技术等多个领域。

在日常生活中,我们使用的计算机、手机、家用电器等,都离不开数字电子技术的支持。

本教材将带领大家深入探索数字电子技术的奥秘,理解其原理和应用。

数字电子技术的基础是数字电路。

数字电路是由各种逻辑门电路组成的,它们可以实现对数字信号的逻辑运算和数据处理。

逻辑门电路是数字电路的基本单元,它们可以执行基本的逻辑运算,如与、或、非等。

数电课程论文

H a r b i n I n s t i t u t e o f T e c h n o l o g y课程设计说明书(论文)课程名称:数字电子技术基础设计题目:声控开关的设计与制作院系:电气学院自动化测试与控制系班级:0901103班设计者:郐士超学号:1090110305指导教师:设计时间:哈尔滨工业大学哈尔滨工业大学课程设计任务书声控开关的设计与制作一、概述声控开关在实际中的应用相当广泛,是一些声控灯基本组成部分,其原理适用于很多声控器械,它涉及到时序逻辑电路如何设计、分析和工作等方面。

通过此电路更深刻的了解时序逻辑部件的工作原理,从而掌握如何根据需要设计满足要求的各种电路图,解决生活中的实际问题,将所学知识应用于实践中。

设计任务技术指标:一、任务设计一个声控开关,控制对象为发光二极管。

二、基本要求1、接收到一定强度的声音后,声控开关点亮发光二极管(电流5~10mA),延时时间在1~15s之间可调。

2、延时时间用数字显示(采用共阳极数码管),时间单位可调,显示范围为1~15s。

二、方案说明此方案采用74ls90计数器,74ls47译码器,晶体管放大电路,555构成的整形电路,555构成的单稳态触发器和多谐振荡器,还有74ls00等门电路。

驻极体话筒接收到一定强度的声音信号后,声音信号转换为电压信号,幅度很小,经放大、整形后,触发单稳态延时电路,产生一个宽度可调的脉冲信号,驱动发光二极管显示。

同时,这个脉冲信号作为选通信号,使计数器计数,并用数码管显示延时。

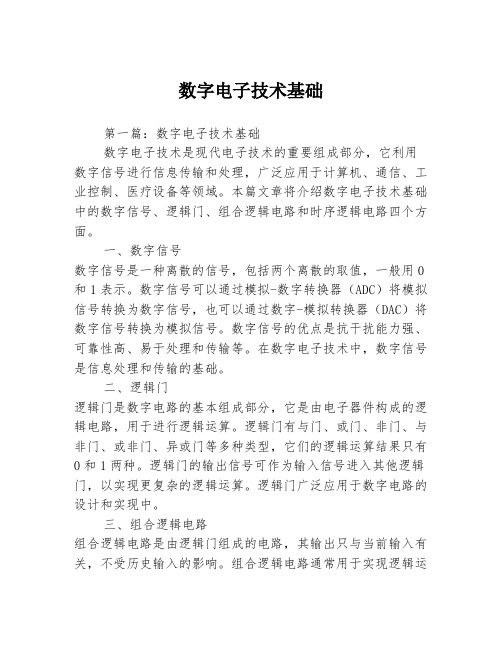

原理框图如图1所示。

图1 声控开关原理框图从以上方案中可知,方案设有信号发生电路,放大整形电路,单稳延时,实基电路,计数器以及译码显示。

各部分功能明确且之间的联系容易理解,所以采用这种方案。

2单稳延时电路用555定时器构成的单稳态触发器起单稳延时作用,高电平触发,其中tw=1.1RC。

时间是0—10s可调,C取100uF,可计算出R为0—100千欧的电位器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

//本模块由50M时钟分频产生占空比50%的1Hz时钟 module clk_1Hz(clk_50M,clk_1,reset); input clk_50M,reset; output clk_ 1; reg clk_1; reg clk_2; reg[25:0] count; always@(posedge clk_50M) begin i f (count ==24_999_999) begin clk_2 = 1'b1; count end else begin clk_2 = 1' b0; count = count+1; end end always@(posedge clk_2 or negedge reset) //由空 比非50%的2Hz时钟分频产生占空比50%的1Hz时钟 begin if (!reset) = 0; //count计 数终点 = f_in/f_out-1 = 50*10^6/2-1 //产生占空比非50%的2Hz时钟 哈尔滨工业大学课程设计说明书(论文) clk_1 = 1'b0; else clk_1 =  ̄ clk _1; end endmodule 方法二 //本模块由50M时钟分频直接产生占空比50%的1Hz时钟 module clk50M_to_clk1(clk_50M,clk_1,reset_n); input clk_50M,reset_n; output clk_1; reg [26:0]count; reg clk_1; always @(posedge clk_50M or nege dge reset_n) begin if(!reset_n) begin count<=0; clk_1<=0; end else if(coun t ==24_999_999) begin f_in/(2*f_out)-1 = 50*10^6/2-1=24999999 clk_1<= ̄clk_ 1; count<=0; end else count<=count+27'b1; // 占 空 比 50% 方 波 count 计 数 终 点 = //1Hz时钟 end endmodule 模块二 被测信号的分频获取 //本模块用于产生被测频率的方波,先分频产生2 00Hz频率方波,再由输入参数freq_div 决定对200Hz进行2 ̄15分频比的分频,从而产 生最后的被测方波 module user_clk(clk_50M,clk_test,freq_div,reset_n); input clk_50M; in put input [3:0] freq_div; reset_n; //被测方波 //输入分频参数 output clk_test; reg clk_test; reg clk_200Hz; reg [25:0] count; reg [ 3:0] cnt; wire [3:0] div; always@(posedge clk_50M) 哈尔滨工业大学课程设计说明书(论文) begin if (count =='d24_9999) //产 生占空比非50%的200Hz时钟 begin clk_200Hz <= 1'b1; count end else begin clk _200Hz <= 1'b0; count <= count+26'b1; end end /*always@(posedge clk_100Hz) begin clk_test<=  ̄ clk_test; end*/ assign div=(freq_div==4'b0) ? 1'b0 : / /已知分频比N,求cnt计数终点。由于产生方波,cnt //由N>>1来计算N/2,同时在N= 0 //对200Hz进行2 ̄15分频比的分频, <= 0; 计数终点=N/2-1 (freq_div==4'b1) ? 1'b0 : ((freq_div>>1)-1); 和1的情况,使cnt计数终点为零即2分频 always @(posedge clk_200Hz or negedge reset_n) begin 从而产生最后的被测方波 if(!reset_n) cnt<=0; else if(cnt==div) cnt<=0; clk_test<= ̄clk_test; e nd else cnt<=cnt+1'b1; end endmodule begin 模块三 频率计中计数与锁存部分的实现 //clk_1作为时基信号开启计数,clk_ test作为计数时钟 module counter(clk_test,clk_1,reset_n,q0,q1,cnt_enb); input clk_test, clk_1,reset_n; output [3:0] q0,q1; output cnt_enb; reg cnt_enb; reg [7:0] count; reg [7:0] out; 哈尔滨工业大学课程设计说明书(论文) always @(posedge clk_1 or negedg e reset_n) if(!reset_n) cnt_enb<=0; begin else cnt_enb<= ̄cnt_enb; //使能开启1S end always @(posedge clk_test or negedge reset_n) if(!reset_n ) count<=8'b0; else if((cnt_enb==1'b1)&&(cou nt[3:0]==4'b1001)) begin count[3:0]<=0; count[7:4]<=count[7:4]+1'b1; end e lse if(cnt_enb==1'b1) count[3:0]<=count[3:0]+1'b1; else //计数使能无效后,

哈尔滨工业大学课程设计说明书(论文) 图 3 时序图 其中,A-被测信号;B-时基信号,秒脉冲;E-计数器计数脉冲信号 ;C-锁存器送数信 号;D-计数器清零信号。 当时基信号出现上升沿时,计数器开始 计数,计到时基信号下 降沿出现,计数器停止计数,此时锁存器送数信号出现上升沿 有效,给数码管送数,等 送数结束后,计数器出现一个上升沿对计数器清零。当下一 个时钟周期到来时,是一样 的过程。 频率计的输入输出关系如下表一所示: 表一 输入输出信号 输入 : clk1Hz uclk 输出: led0 led1 p_cnt_en p_rst_cnt p_loa d 频率值最低位 频率值次低位 计数允许(1 s) 复位计数器 锁存到寄存器中 基准时 钟输入 待测信号输入 哈尔滨工业大学课程设计说明书(论文) 图 4 FPGA 内部均衡逻辑图 方案优化与确定 在满足基础要求后,我们进行设计了的创新。首先,我们在逻 辑中采 用时序逻辑电路的编程方法,即在时基信号为"1"时闸门开启,自动开始计数, 下降沿来 时锁存数据并输出。为了增加频率计的实际应用功能,我们增设了手动分频 功能,即给 出一个 200HZ 的基础频率,通过拨动开关输入想要分频的倍数并显示在 LED 数码管上, 频率计即可自行计算出分频后的频率值。具体的实现方案将在下文 的程序中给出。 方案实现及程序 模块一 1Hz时基信号的分频 时基信号的分频 方法一

本文由yirgui贡献 doc文档可能在WAP端浏览体验不佳。建议您优先选择TXT,或下载源文件到本机 查看。 哈尔滨工业大学课程设计说明书(论文) 数字式频率计 设计任务 在 FPGA 实验板上,利用 FPGA 编程设计一个数字式频率计。 设计要 求与目的 1.利用实验板上的 50M 时钟分频作为被测输入信号;分频成 1Hz 作为时基信 号;(要 求在示波器上显示被测信号和时基信号) 2.数码管显示的频率范围为 00 ̄9 9Hz。 3.测量精度为±1Hz。 设计原理分析 1.频率是指单位时间(1s)内信号振动的次数。当被测信号在一定的时间段 Ts 内 的周期个 数为 N 时,则被测信号的频率: fx = N Ts 2.从测量的角度看,即单位时间测 得的被测信号的脉冲数。被测信号送入通 道 ,经放大整形后,使每个周期形成一个脉冲,用计数器计算脉冲的个数,即为频率。 如下图 1 所示: N Ts 图1 方案设计 由上述原理可以知道,要实现频率计,从硬件方面看,需要时基电路 、单稳 态触发器、放大整形电路、闸门电路、计数器、锁存器和译码显示器等。其硬件 结构图 如下图 2 所示: 译码显示 器 单稳态触发 器 C 单稳态触发 器 B 时基电 路 C 清零 锁存 锁存器 计数器 E 闸门电路 A 放大整形电 路 D 图 2 硬件结构图 而从数字电路时序的角度去分析,其时序图如下图 3 所示:

page 2

再来一个clk_test的上升沿清计数器 count<=0; //此算法使计数结果为BCD码 begin

end always @(posedge clk_1 or negedge reset_n) if(!reset_n) out<=8'b0 ; else if(cnt_enb==1'b1) //时基信号上升沿时若计数使能有效则锁存计数值,因为 这个沿nt; end assign q0=out[3:0]; assign q1=out[7:4]; endmodule 模块四 频率值的数码管显示 module decode47(a,b,c,d,e,f,g,D3,D2,D1,D0); output a,b,c,d,e,f,g; inp ut D3,D2,D1,D0; reg a,b,c,d,e,f,g; always @(D3 or D2 or D1 or D0) begin ca se({D3,D2,D1,D0}) //用case 语句进行译码 4'd0: {a,b,c,d,e,f,g}= ̄7'b1111110; 4'd1: {a,b,c,d,e,f,g}= ̄7'b0110000; 4'd2: {a,b,c,d,e,f,g}= ̄7'b1101101; 4'd 3: {a,b,c,d,e,f,g}= ̄7'b1111001; 4'd4: {a,b,c,d,e,f,g}= ̄7'b0110011; //输入4 位BCD 码 //输出驱动7个笔划段 哈尔滨工业大学课程设计说明书(论文) 4'd5: {a,b,c,d,e,f,g}= ̄7'b101101 1; 4'd6: {a,b,c,d,e,f,g}= ̄7'b1011111; 4'd7: {a,b,c,d,e,f,g}= ̄7'b1110000; 4 'd8: {a,b,c,d,e,f,g}= ̄7'b1111111; 4'd9: {a,b,c,d,e,f,g}= ̄7'b1111011; defau lt: {a,b,c,d,e,f,g}= ̄7'b1111110; endcase end endmodule 模块五 分频系数的数码管显示 //本模块用于显示分频系数,分频系数由开关输 入 module div_display(freq_div,display_div); input output reg [3:0] freq _div; //分频系数 //转成BCD码的分频系数 [7:0] display_div; [7:0] display_div; always @(freq_div) begin if(freq_div==4'b0 || freq_div==4'b1) display_div[7:0]=8'b10; else if (freq_div>=4'b1010) begin ///二进制_to_BCD码算法:因为最大的分频比是15,所 以最高只能到1,当分频比大于4'b1010时,低位减4'b1010,高位加1 display_div[3:0]=freq_div-4'b1010; display_div[7:4]=4'b1; end else be gin display_div[3:0]=freq_div; display_div[7:4]=4'b0; end end endmodule 模块六 频率计的例化及功能实现 //本频率计可以测量对200Hz方波进行2 ̄15分 频后的方波信号的频率, 分频比由拨码开关 设置,并可以通过数码管显示测量频率 和分频比。当是偶数分配比时测量误差在正负1之 间,为奇数时误差较大。 module frequency_counter(clk_50M,HEX0,HEX1,HEX6,HEX7,reset_n,clk_test ,clk_1,freq_div,cnt_enb ,reset); input clk_50M,reset_n; input [3:0] freq_d iv; output clk_test,clk_1,cnt_enb,reset; output[6:0] HEX0,HEX1,HEX6,HEX7; wire [7:0] display_div; wire [7:0] out; assign reset=reset_n; 哈尔滨工业大学课程设计说明书(论文) //实例化各模块 clk50M_to_clk1 u1 (.clk_50M(clk_50M),.clk_1(clk_1),.reset_n(reset_n)); //直接 //间接 得到占空比50%的1Hz时钟 //clk_1Hz u1 (.clk_50M(clk_50M),.clk_1(clk_1),.reset(reset_n)); 得到占空比50%的1Hz时钟 user_clk (.clk_50M(clk_50M),.clk_test(clk_test),.freq_div(freq_div),. reset_n(reset_n)); u2 // 产 生对200Hz进行2 ̄15分频的占空比50%的方波 counter //频率计核心原理部分 c1 (.clk_test(clk_test),.clk_1(clk_1),.reset_n(reset_n),.q0(out[3:0]),.q 1(out[7:4]),.cnt _enb(cnt_enb)); decode47 .D3(out[3]),.D2(out[2]),.D1(out[1]),.D0(out[0])); //显示频率