基于FPGA的键盘扫描电路 EDA课程设计

基于FPGA的键盘扫描程序的设计

摘要在现代电子工业的控制电路中,键盘扫描和显示电路对系统的调试和设置有着重要的作用。

随着EDA技术的发展,基于FPGA的扫描键盘因其结构简单,能有效防止机械键盘按键抖动带来的数据错误等优点在许多电子设备中都得到了广泛的应用。

本文主要是设计一个基于FPGA的键盘扫描程序,该设计在EDA工具Quarutus II9.0上开发完成,以Creat-SOPC2000实验箱上的4*4矩阵键盘为硬件实体,设计键盘扫描程序,将程序划分为时序产生模块、键盘扫描模块、弹跳消除模块、键值译码模块四个模块,时序产生模块为键盘扫描和弹跳消除模块产生时钟信号,键盘扫描模块采用行扫描法对4*4矩阵键盘进行扫描,键值译码模块将所按键值译码为共阳极8位7段数码管的显示码,几个模块组合起来实现键盘扫描的设计要求。

最后对程序进行仿真分析和硬件验证。

仿真结果表明,该系统具有集成度高、稳定性好、设计灵活和设计效率高等优点。

关键词: FPGA,Quartus II,VHDL,键盘扫描ABSTRACTIn the modern electronics industry controlling-circuit, the keyboard scanning and display circuit plays an important role in debugging and setting the system. With the development of EDA technology, FPGA-based scanning keyboard have been widely used in many electronic devices because of its simple structure, and it also can effectively prevent mechanical keyboard jitter caused by data errors.This article primarily designed an FPGA-based keyboard scan procedures, this design is developed on the EDA tools—— Quarutus II9.0 and designed the keyboard scan program, using the Creat-SOPC2000 experimental box 4 * 4 matrix keyboard as the hardware entity .the program is divided into four modules as the timing generation module, a keyboard scanning module, bounce cancellation module and the decoding module. The timing generation module generates the clock signal for the keyboard scanning and bounce elimination module, the keyboard scanning module using the line scanning method to sweep the 4* 4 matrix keyboard, key decoder module decodes the key value for the common anode eight 7-segment display code. Several modules assembles together to meet the keyboard scanning design requirements. Finally, conducting simulation analysis by the program and verifying the hardware.Simulation results show that the system has many advantages such as high integration, good stability, high efficiency, flexible design and high design efficiency.Keywords: FPGA,Quartus II,VHDL,keyboard scanning目录摘要 (I)ABSTRACT .......................................................................................................... I I 第1章绪论 (1)1.1 课题的研究背景 (1)1.2 课题的研究意义 (2)1.3 本文的主要工作 (2)第2章FPGA开发工具简介 (3)2.1 FPGA概述 (3)2.2 VHDL语言以及Quartus II应用 (3)2.3 本章小结 (4)第3章基于FPGA的键盘扫描程序的设计 (3)3.1 键盘扫描程序的总体电路设计 (5)3.1.1 矩阵式键盘扫描的工作原理 (6)3.1.2 数码管的显示原理 (7)3.2 键盘扫描电路各主要功能模块的设计 (8)3.2.1 时序产生模块 (8)3.2.2 键盘扫描模块 (9)3.2.3 弹跳消除模块 (11)3.2.4 键盘译码电路 (13)3.2.5 键盘扫描程序的顶层文件设计 (15)3.3本章小结 (16)第4章键盘扫描程序的波形仿真及硬件验证 (17)4.1 系统仿真 (17)4.1.1 消抖电路仿真 (17)4.1.2 键盘时钟信号仿真 (18)4.1.3 键盘扫描信号仿真 (18)4.1.4 键盘译码电路仿真 (19)4.1.5 键盘扫描总体电路仿真 (21)4.2引脚的锁定 (22)4.3硬件验证 (23)4.4本章小结 (25)结论 (26)参考文献 (27)附录 (28)致谢 (32)第1章绪论1.1 课题的研究背景在现代计算机与电子系统中,一般都采用通用式的标准键盘将所需的数据和指令等信息通过键盘输入到计算机和电子系统,以此来实现人机之间的接口交互。

EDA实验指导 基于FPGA的动态扫描电路设计new

FPGA实验指导及记录实验三基于FPGA的数码管动态扫描电路设计1.实验目的:(1)掌握FPGA工作的基本原理、FPGA硬件平台的使用;(2)熟悉7段数码管显示译码电路的设计。

(3)掌握数码管动态扫描显示原理及动态扫描电路的设计。

2.实验任务:利用FPGA硬件平台上的6位数码管动态显示计数器输出数据。

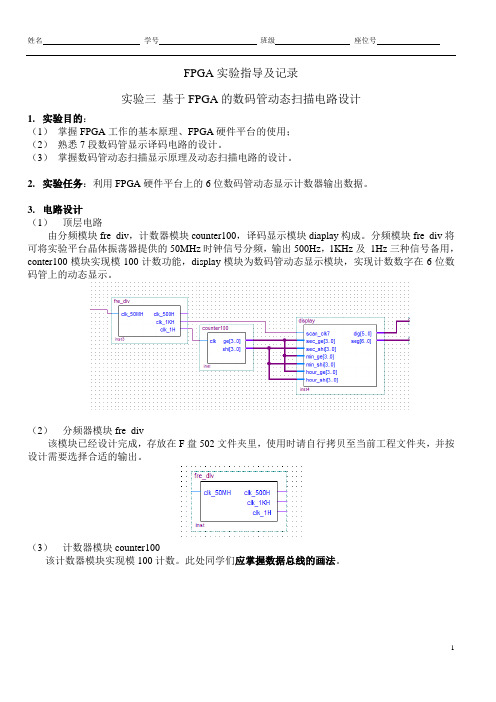

3.电路设计(1)顶层电路由分频模块fre_div,计数器模块counter100,译码显示模块diaplay构成。

分频模块fre_div将可将实验平台晶体振荡器提供的50MHz时钟信号分频,输出500Hz,1KHz及1Hz三种信号备用,conter100模块实现模100计数功能,display模块为数码管动态显示模块,实现计数数字在6位数码管上的动态显示。

(2)分频器模块fre_div该模块已经设计完成,存放在F盘502文件夹里,使用时请自行拷贝至当前工程文件夹,并按设计需要选择合适的输出。

(3)计数器模块counter100该计数器模块实现模100计数。

此处同学们应掌握数据总线的画法。

(4)译码显示模块display该模块由counter6模块,dig_select模块,seg_select模块以及decoder模块构成,请同学们自行完成该模块总体设计,当display模块的输入信号scanclk频率为1KHz时,数码管扫描周期为36ms,每次扫描每位数码管显示时长6ms。

各子模块设计思路如下。

a)counter6模块该模块需使用74390设计一个模6的计数器。

请在空白处做预设计,画出电路图。

b)dig_select模块该模块用于选择6位数码管中的某一位显示相应字形。

74138为3-8译码器,功能表见附录。

c)decoder模块可将4位8421BCD码译为七段码,驱动数码管以十进制数形式显示数字。

7448为共阴极数码管译码器,功能表见附录。

d)seg_select模块该模块功能是从6组4bit信号中选择一组作输出。

矩阵键盘键信号检测电路设计EDA课程设计说明书

课程设计说明书题目EDA技术及应用系(部)专业(班级)姓名学号指导教师起止日期EDA技术课程设计任务书系(部):专业:指导教师:目录引言 (5)一、绪论 (5)1.1 FPGA概况 (5)1.2 此课题的研究意义 (6)二、矩阵键盘接口电路的原理及总体设计 (6)2.1 矩阵键盘接口电路的原理 (6)2.2 总体设计 (8)三、各模块的设计及仿真 (8)3.1 键盘扫描电路 (8)3.2 键盘译码电路和按键标志位产生电路 (11)3.3 时钟产生模块 (16)3.4 键盘接口电路顶层电路实现 (18)四、硬件测试 (19)五、实验设备 (19)六、总结 (20)参考文献 (20)矩阵键盘键信号检测电路设计引言人类文明已进入到高度发达的信息化社会。

信息化社会的发展离不开电子信息产品开发技术、产品品质的提高和进步。

电子信息产品随着科学技术的进步,其电子器件和设计方法更新换代的速度日新月异。

实现这种进步的主要原因就是电子设计技术和电子制造技术的发展,其核心就是电子设计自动化(EDA,Electronic Design Automation)技术,EDA技术的发展和推广应用又极大地推动了电子信息产业的发展。

为保证电子系统设计的速度和质量,适应“第一时间推出产品”的设计要求,EDA技术正逐渐成为不可缺少的一项先进技术和重要工具。

目前,在国内电子技术教学和产业界的技术推广中已形成“EDA热”,完全可以说,掌握EDA技术是电子信息类专业学生、工程技术人员所必备的基本能力和技能。

此设计主要利用VHDL硬件描述语言在EDA平台Quartus II上设计一个4×4阵列键盘扫描电路,将行扫描信号输入阵列键盘,读取列信号的值,输出按键编码,从而判断出按键按下的位置。

并且进行模拟仿真,下载到EDA实验箱进行硬件验证。

一、绪论1.1 FPGA概况早期的可编程逻辑器件只有可编程只读存储器(PROM)、紫外线可擦除只读存储器(EPROM)和电可擦除只读存储器(E2PROM)三种。

矩阵键盘EDA技术课程设计

《电子设计EDA》课程设计专业:电子信息科学与技术班级:2010级电信本(1)班姓名: ***学号: *********指导老师: ***完成时间: 2012.11—2012.12教师评分:目录一、绪论 (1)1.1 FPGA概况 (1)1.2 本课题的研究意义 (2)二、课程设计的任务和目的 (3)三、矩阵键盘接口电路的原理与总体设计 (3)3.1 矩阵键盘接口电路的原理 (3)3.2 总体设计 (5)四、各模块的设计及仿真 (6)4.1 键盘扫描电路 (6)4.2 键盘译码电路和按键标志位产生电路 (8)4.3 时钟产生模块 (10)4.4 键盘接口电路顶层电路实现 (12)五、参考文献 (13)六、心得体会 (13)七、附录 (14)7.1 源程序代码 (14)2题目:矩阵键盘控制接口设计一、绪论1.1 FPGA概况早期的可编程逻辑器件只有可编程只读存储器(PROM)、紫外线可擦除只读存储器(EPROM)和电可擦除只读存储器(E2PROM)三种。

由于结构的限制,它们只能完成简单的数字逻辑功能。

其后出现了一类结构上稍复杂的可编程芯片,即可编程逻辑器件(PLD),它能够完成各种数字逻辑功能。

典型的PLD由一个“与”门和一个“或”门阵列组成,而任意一个组合逻辑都可以用“与—或”表达式来描述,所以PLD能以乘积和的形式完成大量的组合逻辑功能。

这一阶段的产品主要有PAL(可编程阵列逻辑)和GAL(通用阵列逻辑)。

PAL由一个可编程的“与”平面和一个固定的“或”平面构成,或门的输出可以通过触发器有选择地被置为寄存状态。

PAL器件是现场可编程的,它的实现工艺有反熔丝技术、EPROM技术和E2PROM技术。

还有一类结构更为灵活的逻辑器件是可编程逻辑阵列(PLA),它也由一个“与”平面和一个“或”平面构成,但是这两个平面的连接关系是可编程的。

PLA 器件既有现场可编程的,也有掩膜可编程的。

在PAL的基础上又发展了一种通用阵列逻辑(GAL、Generic ArrayLogic),如GAL16V8、GAL22V10等。

eda技术fpga课程设计

eda技术fpga课程设计一、教学目标本课程旨在通过FPGA设计原理与实践,让学生掌握FPGA的基本知识和应用技能,培养EDA技术应用型人才。

知识目标:使学生了解FPGA的硬件结构和基本工作原理,掌握FPGA的配置和编程方法,理解并应用常见的EDA工具。

技能目标:培养学生使用EDA工具进行FPGA设计的能力,包括逻辑设计、综合、布局布线等,以及能够进行简单的FPGA系统开发。

情感态度价值观目标:培养学生对EDA技术和FPGA应用的兴趣,激发学生的创新意识和实践能力,培养学生团队协作和解决问题的能力。

二、教学内容本课程的教学内容主要包括FPGA基本原理、EDA工具使用、FPGA设计与应用等。

第一部分:FPGA基本原理,包括FPGA的硬件结构、工作原理和配置方法。

第二部分:EDA工具使用,包括FPGA逻辑设计、综合、布局布线等基本操作。

第三部分:FPGA设计与应用,包括数字信号处理、数字逻辑设计、嵌入式系统设计等。

三、教学方法为了提高学生的学习兴趣和主动性,本课程将采用讲授法、案例分析法、实验法等多种教学方法。

讲授法:用于向学生传授FPGA基本原理和EDA工具使用方法。

案例分析法:通过分析实际案例,让学生了解FPGA在实际应用中的重要作用。

实验法:让学生亲自动手进行FPGA设计,培养其实际操作能力。

四、教学资源为了支持教学内容和教学方法的实施,我们将准备以下教学资源:教材:选用经典的FPGA教材,为学生提供系统性的理论知识。

参考书:提供相关的FPGA设计和应用方面的参考书籍,丰富学生的知识面。

多媒体资料:制作PPT、视频等教学资料,提高学生的学习兴趣。

实验设备:准备FPGA开发板和相关的实验设备,让学生能够进行实际操作。

五、教学评估本课程的评估方式包括平时表现、作业、考试等,以全面客观地评价学生的学习成果。

平时表现:通过观察学生在课堂上的参与程度、提问回答等情况,评估其学习态度和理解能力。

作业:布置相关的FPGA设计和应用作业,评估学生对课程内容的理解和应用能力。

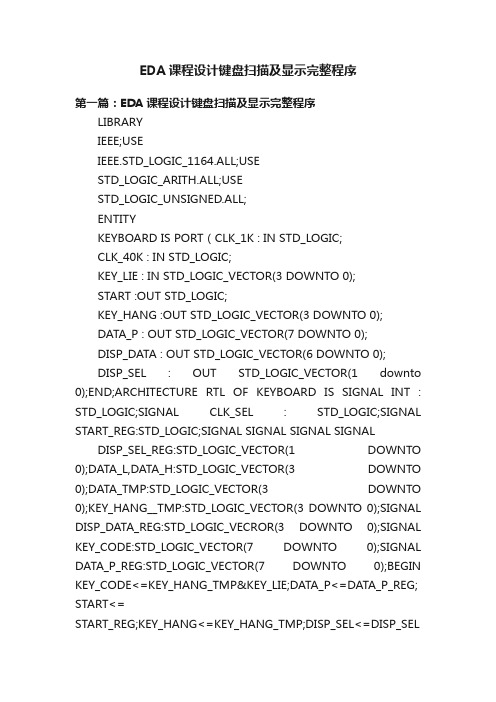

EDA课程设计键盘扫描及显示完整程序

EDA课程设计键盘扫描及显示完整程序第一篇:EDA课程设计键盘扫描及显示完整程序LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USESTD_LOGIC_ARITH.ALL;USESTD_LOGIC_UNSIGNED.ALL;ENTITYKEYBOARD IS PORT(CLK_1K : IN STD_LOGIC;CLK_40K : IN STD_LOGIC;KEY_LIE : IN STD_LOGIC_VECTOR(3 DOWNTO 0);START :OUT STD_LOGIC;KEY_HANG :OUT STD_LOGIC_VECTOR(3 DOWNTO 0);DATA_P : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);DISP_DATA : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);DISP_SEL : OUT STD_LOGIC_VECTOR(1 downto 0);END;ARCHITECTURE RTL OF KEYBOARD IS SIGNAL INT : STD_LOGIC;SIGNAL CLK_SEL : STD_LOGIC;SIGNAL START_REG:STD_LOGIC;SIGNAL SIGNAL SIGNAL SIGNAL DISP_SEL_REG:STD_LOGIC_VECTOR(1 DOWNTO 0);DATA_L,DATA_H:STD_LOGIC_VECTOR(3 DOWNTO 0);DATA_TMP:STD_LOGIC_VECTOR(3 DOWNTO 0);KEY_HANG__TMP:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL DISP_DATA_REG:STD_LOGIC_VECROR(3 DOWNTO 0);SIGNAL KEY_CODE:STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL DATA_P_REG:STD_LOGIC_VECTOR(7 DOWNTO 0);BEGIN KEY_CODE<=KEY_HANG_TMP&KEY_LIE;DATA_P<=DATA_P_REG; START<=START_REG;KEY_HANG<=KEY_HANG_TMP;DISP_SEL<=DISP_SEL_REG;CLK_SEL<=CLK_1K AND(NOT INT);PROCESS(CLK_SEL,CLK_40,INT)VARIABLE STATE : INTEGER RANG 0 TO 3;BEGIN IF RISING_EDGE(CLK_40K)THEN INT<= NOT(KEY_LIE(3)AND KEY_LIE(2)AND KEY_LIE(1)AND KEY_LIE(0));END IF;IF RISING_EDGE(CLK_SEL)THEN CASE STATE IS WHEN 0=>KEY_HANG_TMP<=“1110”;STATE :=1;WHEN 1 =>KEY_HANG_TMP<=“1101”;STATE :=2;WHEN 3 =>KEY_HANG_TMP<=“1011”;STATE :=3;WHEN 4=>KEY_HANG_TMP<=“0111”;STATE :=0;END CASE;END IF;END PROCESS;PROCESS(CLK_40K , INT)VARIABLE STATE :INTEGER RANGE 0 TO 3;VARIABLE COUNTER : INTEGER RANGE 0 TO 31;BEGIN IF INT='0' THENSTATE:=0;COUNTER:=0;ELSIF RISING_EDGE(CLK_40K)THEN CASE STATE ISWHEN 0 => DATA_TMP <= DATA_L;STATE:=1;WHEN 1 =>CASE KEY_CODE ISWHEN “01110111” =>DATA_L <=“0001”;DATA_H <=DATA_TMP; STATE:=2;WHEN “01111011” => DATA_L <=“0010”; DATA_H <=DATA_TMP; STATE:=2;WHEN “01111101” => DATA_L <=“0011”; DATA_H <=DATA_TMP; STATE:=2;WHEN “01111110” => DATA_L <=“0100”; DATA_H <=DATA_TMP; STATE:=2;WHEN “10110111” => DATA_L <=“0101”; DATA_H <=DATA_TMP; STATE:=2;WHEN “10111011” => DATA_L <=“0110”; DATA_H <=DATA_TMP; STATE:=2;WHEN “10111101” => DATA_L <=“0111”; DATA_H <=DATA_TMP; STATE:=2;WHEN “10111110” => DATA_L <=“1000”; DATA_H <=DATA_TMP; STATE:=2;WHEN “11010111” => DATA_L <=“1001”;DATA_H <=DATA_TMP; STATE:=2;WHEN “11011011” => DATA_L <=“0000”;DATA_H <=DATA_TMP; STATE:=2;WHEN “11011101” =>IF DATA_H =“1001” THEN IF DATA_L=“1001” THEN DATA_H<=“1001”;DATA_L<=“1001”;ELSE DATA_L<=DATA_L + 1; END IF;ELSIF DATA_L=“1001” THEN DATA_L<=“0000”;DATA_H<=DATA_H+1; ELSEDATA_L<=DATA_L+1;DATA_H<=DATA_H;END IF;STATE:=2;WHEN “11011110” =>IF DATA_H=“1001” THEN DATA_H<=“1001”;ELSE DATA_L<=DATA_L;DATA_H<= DATA_H+1;END IF; STATE:=2;WHEN “11100111” =>IF DATA_L=“0000” AND DATA_H=“0000” THEN DATA_L<=“0000”;DATA_H<=“0000”;ELSIF DATA_L=“0000” THEN DATA_L<=“1001”;DATA_H<= DATA_H-1;ELSEDATA_L <=DATA_L-1;DATA_H<=DATA_H;END IF;STATE:=2;WHEN “11101011”=>IF DATA_H=“0000” THENDATA_H<=“0000”;ELSEDATA_L<=DATA_L;DATA_<=DATA_H-1;END IF;STATE:2;WHEN “11101110” =>DATA_L<=DATA_L;DATA_H<=DATA_H;DATA_P_REG<=DATA_H&DATA_L;START_REG<='1';STATE:=2;WHEN“11101101” =>DATA_L<=“0000”;DATA_H<=“0000”;STATE:=2;WHEN OTHERS =>STATE:=2;END CASE;WHEN 2 =>IF COUNTER=31 THENCOUNTER:=0;STATE:=3;ELSECOUNTER:=COUNTER+1;STSTE:=2;END IF;WHEN 3 =>START_REG<='0';STATE:=3;END CASE;END IF;END PROCESS;PROCESS(CLK_1K,DATA_L,DATA_H)VARIABLE STATE: INTEGER RANGE 0 TO 1;BEGINIF RISING_EDGE(CLK_1K)THENCASE STATE ISWHEN 0 =>DISP_SEL_REG<=“10”;DISP_DATA_REG<=DATA_L;STATE:=1;WHEN 1 =>DISP_SEL_REG<=“01”;DISP_DATA_REG<=DATA_H;STATA:=0;END CASE;END IF;END PROCESS;PROCESS(CLK_1K,DISP_DATA_REG)BEGIN IF RISING_EDGE(CLK_1K)THENCASE DISP_DATA_REG ISWHEN “0000”=>DISP_DATA<=“1111110” WHEN “0001”=>DISP_DATA<=“0110000” WHEN “0010”=>DISP_DATA<=“1101101” WHEN “0011”=>DISP_DATA<=“1111001” WHEN “0100”=>DISP_DATA<=“0110011” WHEN “0101”=>DISP_DATA<=“1011011” WHEN “0110”=>DISP_DATA<=“1011111” WHEN “0111”=>DISP_DATA<=“1110000” WHEN “1000”=>DISP_DATA<=“1111111” WHEN “1001”=>DISP_DATA<=“1111011” WHEN OTHERS =>DISP_DATA<=“0000000” END CASE;END IF;END PROCESS;END;第二篇:EDA课程设计考试序号:28自动打铃系统设计说明书学生姓名:周文江学号:14112502521专业班级:1102报告提交日期:2013.11.26湖南理工学院物电学院目录一、题目及要求简介...............3 1.设计题目.....................3 2.总体要求简介 (3)二、设计方案说明 (3)三、系统采用器件以及模块说明.........3 1.系统框图............4 2.选择的FPGA芯片及配置.........4 3.系统端口和模块说明 (5)四、各部分仿真结果 (5)五、调试及总结 (6)六、参考文献 (7)七、附录 (7)一、题目及要求简介1、设计题目设计一个多功能自动打铃系统2、总体要求简介① 基本计时和显示功能(24小时制显示),包括:1.24小时制显示2.动态扫描显示;3.显示格式:88-88-88 ② 能设置当前时间(含时、分)③ 能实现基本打铃功能,规定:06:00起床铃,打铃5s二、设计方案说明本次设计主要采用Verilog HDL硬件描述性语言、分模块法设计的自动打铃系统。

基于FPGA的键盘扫描模块的设计与实现

●主题论文1概述1.1通用键盘和专用键盘[1]在现代个人计算机系统中,一般都采用通用的标准键盘(如:标准101/102键盘或Microsoft自然PS/2键盘)来实现人与计算机之间的接口交互,所需要的各种数据和指令等信息都通过键盘来输入计算机。

但是,在各种嵌入式系统(如手机、微波炉、电风扇等)中,所需要的键盘按键个数非常有限,通常为几个到十几个不等(而标准键盘通常为一百多个按键),并且每个按键所代表的功能含义也各不相同。

所以,针对每一种嵌入式系统都应对键盘(包括键盘扫描模块和相关控制信号等)进行专门设计,结合工程实际情况充分利用该系统已有的各种资源,使所设计的键盘恰如其分地融合到嵌入式系统中,成为其不可分割的一部分。

1.2编码键盘和扫描键盘[2]在数字电路中,可以利用编码器实现按键键值的直接编码。

将每个按键的输出信号对应连接到编码器的每个输入端,通过编码逻辑就可以在编码器的输出端得到对应每个按键的码值,早期称这种键盘为编码键盘。

但是,当按键较多时数码逻辑的成本较高,直接编码的方法也不够灵活,一旦编码逻辑固定就难以更改。

在通用键盘上或当按键数量较多时,普遍采用扫描方式产生键值。

将按键连接成矩阵,每个按键位于某行、某列的交点上,如图1所示,先通过扫描方式确定按下键的行和列位,即位置码或扫描码。

再查表将位置码转换为按键码值或者直接使用扫描码,有些参考书称此为“非编码键盘”。

但这种名称容易让人误解为没有对应的键值,因此又称为扫描式键基于FPGA的键盘扫描模块的设计与实现王志辉1,林水生2(电子科技大学通信与信息工程学院,四川成都610054)摘要:在电子产品中,键盘是最基本的输入设备,然而在应用中都采用通用的键盘扫描器件是不现实的,需要单独设计成专用的小键盘。

现代EDA(电子设计自动化)技术提供了一种很好的途径,利用VHDL硬件描述语言和FPGA器件可以很方便地构建键盘扫描模块。

经过实际操作检验,该模块可以很好地对每一次按键动作进行扫描和响应,实现预先设计的功能。

EDA课程设计键盘扫描电路设计

EDA课程设计键盘扫描电路设计电子课程设计—键盘扫描电路设计学院:班级:姓名:学号:指导老师:12月目录1.设计任务与要求 (1)2.功能模块 (2)3.选择器件 (3)4.功能模块 (5)5.设计总体电路图 (8)6.心得体会 (10)一、设计任务与要求1、键盘按钮数为4,系统时钟10MHz;2、能识别出所按按钮;3、按钮被按下后,视为此按钮输入一次,若按钮长时间不松,(时限1S)后每隔0.5S视为再次输入,直至按钮松开;4、要求能对按钮按下时指令的抖动能正确处理。

对持续时间小于50ms的输入不作响应;5、各键设置不同优先级,多键同时按下时,视为优先级较高的按键被按下;二、功能模块图3 模块delta其VHDL语言如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_unsigned.all;entity keyboard4_4 isport(rst : in std_logic;clk_in : in std_logic;keyin : in std_logic_vector(3 downto 0);scan : out std_logic_vector(3 downto 0);leds : out std_logic_vector(3 downto 0);state : out std_logic;VGA : out std_logic_vector(3 downto 0) );end keyboard4_4;architecture keyboard4_4_arch of keyboard4_4 is----********************************************* component debouncingport( key : IN STD_LOGIC ;clk,clr : IN STD_LOGIC ;dly_out : OUT STD_LOGIC ) ;end component ;--*********************************************。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

信息科学与技术学院 EDA 课程设计报告

题目名称:基于FPGA 的键盘扫描电路 学生姓名:王彪 学 号:2010508115 专业年级:电信10级(2)班 指导教师:钟福如老师 时 间:

2010.1.13

目录

1 课程设计综述——————————————————————

2 1.1 课程设计的题目———————————————————— 2

1.2 题目要求——————————————————————— 2

2 方案选择———————————————————————— 2

3 整体电路的设计及分析——--——————————————— 3 3.1 顶层电路图—————————————————————— 3

3.2 各模块功能原理分析—————————————————— 4

4 心得体会——————————————————————— 12

1.课程设计综述

1.1 课程设计的题目

基于FPGA的键盘扫描电路。

1.3 题目要求

(1)、键盘按钮数为4,系统时钟10MHz。

(2)、能识别出所按按钮。

(3)、按钮被按下后,视为此按钮输入一次,若按钮长时间不松,(时限1S)后每隔0.5S 视为再次输入,直至按钮松开。

(4)、要求能对按钮按下时指令的抖动能正确处理。

对持续时间小于50ms的输入不作响应。

(5)、各键设置不同优先级,多键同时按下时,视为优先级较高的按键被按下。

2.方案选择

根据题目要求,需要4个按钮的键盘,通过查阅资料我选择通用的2*2行列式键盘,判断键盘中有无按键按下是通过行线送入扫描信号,然后从列线读取状态得到的。

其方法是依次给行线送低电平,检查列线的输入。

如果列线信号全为高电平,则代表低电平信号所在的行中无按键按下;如果列线有输入为低电平,则低电平信号所在的行和出现低电平的列的交点处有按键按下。

原理框图如下所示:

由题知输入的是10MHz的系统时钟,我们需要通过一个分频器来输出一个1KHz的计数频率来扫描键盘以及一个40Hz(即25ms)的消除抖动的频率来计算是否属于抖动按键,计数值用来计算当前键盘扫描值,4按钮的话计数值则是00、01、10和11 ,若有按键信号发生则送计数值到按键检测电路和按键编码电路供确定按键位置用。

键盘扫描电路提取列按键并和计数值进行比较得到哪一行被按下,并可通过对计数值的分解得打哪一列有按键,提取该值供计数器电路和消抖电路使用。

我们用一个状态机来实现消抖电路,按键抖动为50ms,我们通过对按键进行两次采样判断是否属于抖动,则输入时钟用40Hz(25ms),通过两次采样得到50ms的判断值,若按键信号一直有效则属于有效按键。

键盘编码电路实现了计数值到对应编码的转换。

3.整体电路的设计及分析

3.1 顶层电路图

3.2 各模块功能原理分析

3.2.1 分频模块(SCAN_GEN)

该模块的模型如左所示,输入信号为系统时钟信号

10MHz,输出为两个分频后的信号。

具体代码如下所示:

对键盘扫描的分频我们定义的计数器为13位(8192大于5000)才能实现一万分频得到1KHz的信号,对于消抖电路的计数器则设为17位(131072>125000)才能实现二万五千分频得到40Hz的信号,由于该模块要求的分频数太高,软件仿真不出,所以实际仿真的时候我们改成了100个时钟信号分频为10个和25个时钟信号的模拟。

该电路仿真图如下所示:

我们把CLK设置为100个时钟,由图可知,当CLK发生5个上升沿变化时,scan_f 发生一次翻转,实现了10分频,当CLK发生10个上升沿变化时,scan_dd发生一次翻转,实现了20分频。

从而实现了该电路的基本功能。

3.2.2 计数电路(SCAN_COUNT)

该模块的模型如左所示,输入信号为分频电

路产生的键盘扫描频率以及键盘扫描电路产生

的按键信号,输出的是供键盘扫描电路和编码电

路使用的计数值。

具体代码如下所示:

由于是2*2的键盘,我们只需要定义计数值为2位(00、01、10、11)即可表示所有的键位,当按键信号是高电平即无按键输入时,计数值一直在00、01、10和11中循环,当有按键输入时,把此时的计数值输出供键盘扫描电路和按键编码电路使用。

3.2.3 键盘扫描模块(KEY_SCAN)

该模块的模型如左所示,输入信号为按

键产生的列信号,并和另一个从计数模块

输入的计数信号进行比较得到该按键在哪

一行,并产生按键信号和优先列信号。

具体代码如下所示:

该电路的主要思路在于计数值、列信号和行信号的对应关系,如下表所示:

第二列第一列

计数值

A B

第一行10 1 0 0 0 0 1 0 1

第二行01 1 0 1 0 0 1 1 1

表中A判断在第几行,0表示在第一行,1表示在第二行,B判断哪一列有按键供按键信号的赋值,0表示第一列,1表示第二列。

仿真图如下所示:

第一个100ns内,计数值为00,输入为00,即两列都有按键输入,则是第一行的两个键都被按下,第一行为低电平且按键信号变为低电平,我们设置的是第一列优先,所以输出的第一列是低电平,第二列是高电平。

第二个100ns内,计数值为01,输入为01,则是第一行的第二列被按下且按键信号为低电平。

第4个100ns到第6个100ns内,输入的列信号是11,则无按键输入,按键信号为高电平。

3.2.4 消抖模块(DEBOUNCE)

该模块的模型如左所示,从分频电路得到消

抖需要的40HZ(25ms)的时钟信号,并从键盘扫

描电路得到按键信号,并判断该按键是否有效。

消抖电路的原理是:对一个按键信号,对它进行取样,如果连续两次取样都为低电平,则认为信号已经处于稳定状态,这时输出一个低电平的按键信号。

否则只要有一次取样不为低电平,则认为是抖动,将其丢弃。

为了实现此目的,我们可以设置一个状态机如下所示:

x/y:表示输入和输出。

‘/’左侧的为输入信号,‘/’右侧的为输出信号。

当按键按下时,为低电平。

按键松开后为高电平。

设定一个状态机,有S0、S1、S2这3个状态,我们进行两次采样,采样间隔为25ms,则总采样时间为50ms,完成了题目要求,S0是初态,按键真值为1,当采样信号的上升沿到来时,我们对按键值进行判断,若为0则表示按下,跳入S1状态,若为1则保持在S0状态,此时输出按键真值为1。

若进入S1状态,下一个上升沿到来时继续对按键值进行判断,若为0则表示还是按住的,进入S2状态,若为1则表示已经松开,为抖动按键,再次进入S0状态。

S2状态后,此时已经过了两个采样周期(50ms),则说明此按键为有效按键,输出有效按键为0,在S2状态若继续得到按键为0则表示连续输入,则按键一直被按下,直到得到按键为1的信号重新进入S0状态。

可以看到,当两个采样周期内按键信号都有效时,在下一个上升沿到来时按键信号为有效,当只有一个采样周期内有效则按键真值输出的还是无效电平,当一只按键则按键真值一直有效。

3.2.5 键盘编码模块(CODE_TRAN)

该模块的模型如左所示,取的是系统时

钟信号以及供编码用的计数信号,输出的是

编码后的按键对应值。

具体代码如下所示:

计数值和按键编码的关系如下表所示:

计数值编码后的值

00 001

01 010

10 011

11 100

仿真后的波形如下所示:

当输入的计数值为0、1、2、3即00、01、10、11时,输出的是1、2、3、4即001、010、011和100,完成了编码的要求。

3.2.6 顶层模块

模块模型如3.1所示,仿真波形如下所示:

当输入信号是00时,在SCAN_F的上升沿到来时开始电路开始扫描,此时计数值为10,则为第二行,ROW1和ROW0为01 。

输入信号经过了两个采样周期,则为有效的按键信号,则按键真值信号在下一个采样信号的上升沿变为有效低电平,00的编码是011,是第二行的第一列,该位的按键编码值为3 。

初步完成了整体的要求。

4.心得体会

通过本次课程设计,让我受益颇丰。

拿到题目时,我并没有太多的头绪,经过大量相关方面的书籍查阅和对读秀中各种相关方便资料的查阅之后才有了一定的设计思路。

本次实验的模块很多,各个模块的联系和产生的信号以及所用的信号之间的关系有点复杂,在做本次课程设计时需要一个清晰的头脑才能完成。

本次设计中了解到太高频率的分频是难以仿真实现的,只能通过低频率的模拟才能仿真出波形,实验中还遇到了很多常识性的问题,如更改器件中的内容之后需要把该器件生成的原先的文件删除之后再仿真才能得到正确的模型。

课程设计中了解到了很多以前不知道的知识,如状态机的设置,消抖电路的实现等关键电路的设计。

本次实验的成功也使得我对学习EDA的热情高涨,不足和不懂之处还有许多,望老师能够多加指导。

参考文献:

[1] 潘松黄继业•EDA技术实用教程——VHDL版(第四版)•科学出版社,2011

[2] 罗力凡等•基于VHDL的FPGA开发快速入门技巧实例•人民邮电出版社,2009

[3] 杨晓慧杨永健•基于FPGA的EDA/SOPC技术与VHDL•国防工业出版社,2007。