将图片导入allegro PCB的方法如下

怎么把原理图导入pcb

怎么把原理图导入pcb

要将原理图导入PCB软件中,并去除标题以及避免文中有相

同的文字,可以按照以下步骤进行操作:

1. 打开PCB软件,创建一个新的PCB项目。

2. 在原理图软件中,检查并确保没有重复的标题文字。

如果有重复的标题文字,进行修改或删除。

3. 导出原理图为常见的标准格式,如DXF、DWG、OrCAD

等。

可以通过使用“导出”或“另存为”功能来实现。

4. 在PCB软件中,选择“导入”或“打开”选项,选择刚才导出

的原理图文件。

5. 在导入原理图的窗口中,查找并选中“去除标题”或“不导入

标题”等选项。

这个选项的名称可能因PCB软件而异,可以查

阅软件的用户手册或进行在线搜索以找到相应的选项。

6. 确认导入选项后,继续进行导入操作。

导入完成后,将会显示原理图在PCB软件中的布局。

7. 对于任何有重复文字的元件或标签,可以手动修改它们,以确保没有重复文字的存在。

完成上述步骤后,你应该能够成功导入原理图到PCB软件中,并去除标题以及避免文中有相同的文字。

Allegro PCB Editor使用流程简介

本文档主要介绍Cadence的PCB设计软件Allegro PCB Editor的基本使用方法,其中封装库的建立不再赘述,参见“Cadence软件库操作管理文档”。

目录一、创建电路板 (2)1、新建电路板文件 (2)2、设置页面尺寸 (2)3、绘制电路板外框outline (3)4、电路板倒角 (4)5、添加装配孔 (5)6、添加布局/布线允许区域(可选) (7)二、网表导入和板层设置 (7)1、网表导入 (7)2、板层设置 (8)三、布局 (9)1、手动布局 (9)2、布局时对元器件的基本操作 (10)3、快速布局 (11)4、按ROOM方式布局 (12)5、布局复用 (15)四、设置约束规则 (17)1、设置走线宽度 (17)2、设置过孔类型 (18)3、间距规则设置 (19)五、布线 (20)1、设置走线格点 (20)2、添加连接线 (20)3、添加过孔 (21)4、优化走线 (21)5、删除走线 (21)六、敷铜 (22)1、设置敷铜参数 (22)2、敷铜 (23)七、PCB后处理 (25)1、检查电路板 (25)2、调整丝印文本 (27)3、导出钻孔文件 (28)4、导出光绘文件 (29)一、创建电路板1、新建电路板文件原理图成功导出网表进行PCB设计之前,首先需要根据实际情况建立电路板文件(.brd),主要是设置PCB板的外框尺寸(软件中称为outline)、安装孔等基本信息。

启动Allegro PCB Editor软件:选择“File-New”,在新建对话框中设置电路板存放路径,名称等信息:点击“OK”2、设置页面尺寸这里的页面尺寸并不是电路板的实际尺寸,而是软件界面的允许范围,根据实际电路板的大小设置合理的页面尺寸。

选择“Setup-Design Parameters”范围设置(Extents)中的Left X和Lower Y分别代表页面最坐下角的坐标,初次启动软件时,默认原点(0,0)为页面的最左下角。

每天进步一点点------AllegroPCB

每天进步⼀点点------AllegroPCB Allegro PCB1.如何在allegro中取消花焊盘(⼗字焊盘)set up->design parameter ->shape->edit global dynamic shape parameters->Thermal relief connects ->Thru pins ,Smd pins -> full contact2.allegro 中如何设置等长setup -> constraints->electrical->net->routing->Min Max Propagation delays选择要等长的net->右击->create->pin pair->选择pin修改 prop daly 的min 和max项3.如何设置allegro的快捷键修改⽂件 $inst_dir\share\pcb\text\env 或 $inst_dir\pcbevn\env快捷键定义如下:alias F12 zoom outalias ~R angle 90 (旋转90 度)alias ~F mirror (激活镜相命令)alias ~Z next (执⾏下⼀步命令)alias End redisplay(刷新屏幕)alias Del Delete(激活删除命令)alias Home Zoom fit(全屏显⽰)alias Insert Define grid(设置栅格)alias End redisplayalias Pgdown zoom outalias Pgup zoom inalias F12 custom smoothalias Pgup slidealias Pgdown donealias Home hilightalias End dehilightalias Insert add connectalias Del Delete4.如何在allegro中删除有过孔或布线的层时不影响其他层1.输出specctra的dsn⽂件allegro->file->export->router->demo.dsn->run2.产⽣session⽂件specctra(pcb router)->file->write->session->demo.ses->ok3.删除某⼀层中的布线和过孔delete(ctrl+D)->..4.删除allegro中的板层setup->cross section->⿏标右键->delete5.导⼊session⽂件allegro->file->import->router->demo.ses->run也可先将通过该层的过孔先替换成顶层焊盘,删除该层以后再替换回来5.如何在Allegro中同时旋转多个零件1.Edit->Move 在Options中Rotation的Point选User Pick2 再右键选Term Group 按住⿏标左键不放并拉⼀个框选中器件多余的可⽤Ctrl+⿏标左键点击去掉.3. 选好需整体旋转的器件后右键complete.4. 提⽰你Pick orgion ⿏标左键选旋转中⼼.5 下⾯右键选rotate 即可旋转了.6.allegro 16.0 透明度设置display->colour/visibility->display->OpenGL->Global transparency->transparent7.allegro Drill hole size is equal or larger than smallest pad size.Pad will be drilled away.提⽰Drill hole size is equal or larger than smallest pad size.Pad will be drilled away.不⽤理睬这⼀提⽰8.ALLEGRO 如何⽣成钻孔⽂件Manufacture -> NC -> Drill Customization->auto generate symbolsManufacture -> NC -> Drill LegendManufacture -> NC ->NC parameters->enhanced excellon format->closeManufacture -> NC -> NC Drill->auto tool select->optimize drill head travel9.CAM350如何正确导⼊钻带⽂件导进去后MACRO->PLAY->选择(CAM350--SCRIPTS)PADS_DRILL->选择钻带的REP⽂件还没测试过,rep⽂件从哪⼉来的呢10.allegro 如何设置route keepin,package keepin1.setup->area->route keepin,package keepin ->画框2.edit ->z-copy->options->package keepin,route keepin->offset->50->点击外框11.allegro 中如何禁⽌显⽰shape完全禁⽌的⽅法没找到setup->user preference editor->display->display_shapefill->输⼊⼀个较⼤的数shape在显⽰时就不是那么显眼了set-user preference editor-shape-no shape fill(v)12.如何在allegro设置⾃定义元件库路径在下⾯两个位置添加⾃定义元件的路径Setup->User Preferences Editor->Design_paths->padpathSetup->User Preferences Editor->Design_paths->psmpath1.在allegro中如何修改线宽在Allegro的Setup->constraints⾥的set standard values中可定义每⼀层⾛线的宽度,⽐如,可以定义VCC和GND的线宽为10 Mil。

(整理)从CAPTURE到ALLEGRO PCB EDITOR通过第三方格式输出网表

从CAPTURE到ALLEGRO PCB EDITOR通过第三方格式输出网表

从CAPTURE导出网表:

打开工程管理器页面,鼠标左键选中*.dsn文件。

从菜单Tools中选中Create Netlist

可能会弹出下图所示的对话框。

点击“Yes”后将打开下图所示的网表参数设置选项框。

选择生成第三方格式网表的选项卡“Other”,按照下图红色框内所示设置好以后,点击“确定”,将在指定的路径下生成网表。

导入网表前的准备工作

将telesis格式的网表导入PCB时需要使用器件封装的device信息。

如何生成device文件:

用PCB EDITOR打开某封装的*.dra文件,在菜单File下选择Create Device命令,程序将在当前目录下生成与*.dra同名的*.txt文件。

逐一生成设计中所有元器件的device文件后,可以将他们整理到一个文件夹下,例如命名device文件夹;然后需要在PCB EDITOR中将用户环境变量devpath指向其对应的路径。

该环境变量在菜单Setup-User Preference中进行设置

在下面的界面中,点击Path,然后library,选择devpath

弹出下图所示的对话框。

按照下图所示的步骤设置正确的DEVICE库路径

用同样的方法可以设置焊盘库及器件封装库的库路径padpath及psmpath

从PCB EDITOR中导入网表

做好了上述的准备后,可以将网表导入到PCB中了。

打开PCB EDITOR,新建一个brd文件。

在菜单File中选择Import-Logic,如下图所示

按照下图所示的步骤导入网表。

allegro pcb 基本操作

allegro pcb 基本操作:

Allegro PCB基本操作主要包括以下几个方面:

1.打开和保存文件:使用Allegro PCB Designer软件打开已存在的PCB文件或创建一个

新的PCB文件。

在保存文件时,可以选择保存为不同的版本,以避免出现兼容性问题。

2.导入和导出数据:使用Allegro PCB Designer软件可以导入和导出多种格式的数据,

如Gerber、IPC-D-356等。

这些数据可以在不同的软件之间进行转换,以便于数据的共享和交流。

3.绘制和编辑电路板:在Allegro PCB Designer软件中,可以使用各种工具绘制电路板,

如线条、圆形、矩形等。

同时,还可以添加元件、电源、接地等元素。

在编辑电路板时,可以进行移动、复制、删除等操作,以确保电路板的准确性和完整性。

4.调整元件封装:在添加元件到电路板时,需要选择合适的元件封装。

在Allegro PCB

Designer软件中,可以根据实际情况调整元件封装的参数和布局,以确保电路板的可制造性和可靠性。

5.生成报表和文件:在完成电路板的绘制和编辑后,可以生成各种报表和文件,如BOM

表、Gerber文件、IPC-D-356文件等。

这些报表和文件可以用于生产制造、物料采购等环节,以确保生产流程的顺利进行。

Allegro软件操作技巧

5

Allegro 软件操作技巧-lingling1350@

2) (如上右图,其它操作同前) 3)上两步得到的网络列表分别拷到《U_管脚调整》表中。

再做成 lis 文件。

14、让两孔间的线等间距:ROUTE---RESIZE/RESPACE---SPREAD BETWEEN VOIDS。 对于两孔间有多跟线的情况同样适用。当然假如所有的线都用这种方法等间 距的话必然很费时, 修线时可以把格点改大、采用偶数小格点的方法就很容易让 两根线等间距了。 15、添加测试点 分为自动添加和手动添加两种,关键在于参数设置。 1) 自动添加

6

Allegro 软件操作技巧-lingling1350@

设置好参数后,点 Generetetesrpoints 就会给底层每个网络加上测试点。

7

Allegro 软件操作技巧-lingling1350@

另外,测试点之间保持 75mil 以上的间距、测试点与焊盘之间要也保持适当 的间距。

12

Allegro 软件操作技巧-lingling1350@

Байду номын сангаас

图a

图b

3)加粗:EDITCHANGE线宽为 50,如下图 c 所示: 实际上,电源平面比顾平面内缩 40,结合第一步 OFFSET 填 15、第三步加粗 到 50,不难得出,经过这一番折腾后,确实内缩了 40 吧。如果需要改变内缩大 小,自己算一下具体数值就行了。

2)16.3: 16.3 创建区域规则:Shanpe Add Rect,Options 参数设置如下图(区域 名称 BGA08 自动会出现在规则管理器中) 画区域铜 在规则管理器中的

3

Allegro 软件操作技巧-lingling1350@

Cadenceallegro菜单解释

Cadence allegro菜单解释——file已有 320 次阅读2009-8-16 19:17|个人分类:工作|关键词:Cadence allegro file 菜单解释每一款软件几乎都有File菜单,接下来详细解释一下allegro与其他软件不同的菜单。

new新建PCB文件,点new菜单进入对话框后,drawing type里面包含有9个选项,一般我们如果设计PCB就选择默认第一个board即可。

如果我们要建封装库选package symbol即可,其他7个选项一般很少用,大家可以理解字面意思就可以知道什么意思了。

open打开你所要设计的 PCB文件,或者封装库文件。

recent designs打开你所设计的PCB文件,一般是指近期所设计的或者打开过的PCB文件。

save保存save as另存为,重命名。

importimport 菜单包含许多项,下面详细解释一下我们经常用到的命令。

logic 导入网表,详细介绍在allegro基础教程连载已经有介绍,在此不再详细介绍。

artwork 导入从其他PCB文件导出的.art的文件。

一般很少用词命令。

命令IPF和stream 很少用,略。

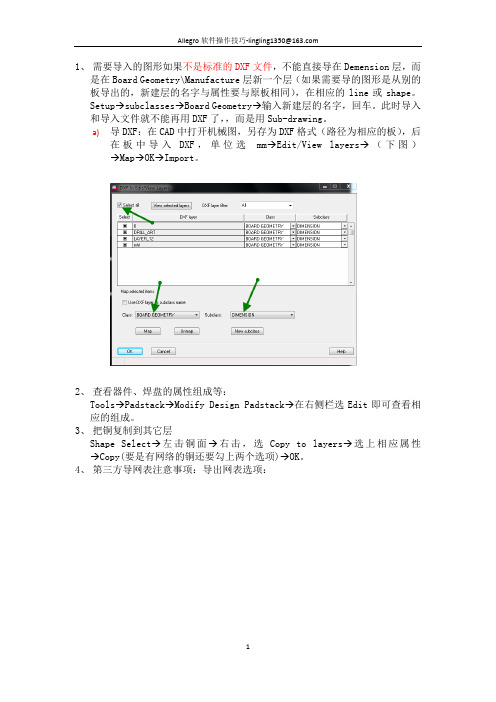

DXF 导入结构要素图或者其他DXF的文件。

导入方法如下:点import/DXF后,在弹出的对话框选择,在DXF file里选择你要导入的DXF的路径,DXF units 选择MM,然后勾选use default text table和incremental addition,其他默认即可。

再点edit/view layers弹出对话框,勾选select all,DXF layer filter选择all,即为导入所有层的信息,然后在下面的class里选择board geometry,subclass选择assembly_notes,因为一般导入结构要素图都是导入这一层,然后点ok,进入了点import/DXF后弹出的对话框,然后点import即可将结构要素图导入。

Allegro教程-17个步骤

Allegro教程-17个步骤Allegro是Cadence推出的先进PCB设计布线工具。

Allegro提供了良好且交互的工作接口和强大完善的功能,和它前端产品CadenceOrCADCapture的结合,为当前高速、高密度、多层的复杂PCB设计布线提供了最完美解决方案。

Allegro拥有完善的Constraint设定,用户只须按要求设定好布线规则,在布线时不违反DRC就可以达到布线的设计要求,从而节约了烦琐的人工检查时间,提高了工作效率!更能够定义最小线宽或线长等参数以符合当今高速电路板布线的种种需求。

软件中的Constraint Manger提供了简洁明了的接口方便使用者设定和查看Constraint宣告。

它与Capture的结合让E.E.电子工程师在绘制线路图时就能设定好规则数据,并能一起带到Allegro 工作环境中,自动在摆零件及布线时依照规则处理及检查,而这些规则数据的经验值均可重复使用在相同性质的电路板设计上。

Allegro除了上述的功能外,其强大的自动推挤push和贴线hug走线以及完善的自动修线功能更是给用户提供极大的方便;强大的贴图功能,可以提供多用户同时处理一块复杂板子,从而大大地提高了工作效率。

或是利用选购的切图功能将电路版切分成各个区块,让每个区块各有专职的人同时进行设计,达到同份图多人同时设计并能缩短时程的目的。

用户在布线时做过更名、联机互换以及修改逻辑后,可以非常方便地回编到Capture线路图中,线路图修改后也可以非常方便地更新到Allegro中;用户还可以在Capture与Allegro之间对对象的互相点选及修改。

对于业界所重视的铜箔的绘制和修改功能,Allegro提供了简单方便的内层分割功能,以及能够对正负片内层的检阅。

对于铺铜也可分动态铜或是静态铜,以作为铺大地或是走大电流之不同应用。

动态铜的参数可以分成对所有铜、单一铜或单一对象的不同程度设定,以达到铜箔对各接点可设不同接续效果或间距值等要求,来配合因设计特性而有的特殊设定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

将图片导入allegro PCB的方法如下:

1,将附件的软件安装,打开软件,点击1-select BMP file挑选保存的BMP格式的公司logo,

如下截图:

2,然后设置参数,因为第一次可能大小不太好把我,先尝试设置参数,如果不满意可以删除重新导入,

3,点击3-make out.plt

4,生成完成以后会在图片目录下生成一个out.plt的文件;

5,打开allegro PCB,执行file-import-IPF,浏览到IPF的文件,点击ok即可导入,点击OK后,图片是挂在鼠标上的,这个时候可以选择导入的class/subclass比如(Silk_Top)。

然后放置到合

适的位置,

6,结果如下:

另外一个问题,如果要在PCB上直接挖空一块区域可以使用board geometry/outline来挖空,比如现在有一个200x200的方框是board geometry/outline,如果我们在这个200X200的板框内再画一个100X100的board geometry/outline的方框,那么最后成板就是一个200X200的PCB 中间挖空了一个100X100的洞。