PCI Interface 讯号说明

主板信号

主板上各种信号说明一2007年08月26日星期日 13:20六、LAN LINK接口信号说明1. LAN_CLK I Lan I/F Clock(网络时钟)这个信号由Lann Chipset驱动输出,它的频率范围在5~50Mhz。

2. LAN_RXD[2:0] I Received Data(接收数据)这些信号是由Lan Chipset驱动输出到南桥。

n3. LAN_TXD[2:0] O Transmit Data(传输数据)这些信号是南桥驱动输出到Lan Chipset。

n4. LAN_RSTSYNC O Lan Reset(Lan Chip 复位信号)七、EEPROM 接口信号说明1. EE_SHCLK O EEPROM Shift Clock(EEPROM时钟)n 这个信号由南桥驱动输出到EEPROM。

2. EE_DIN I EEPROM Data In(EEPROM数据输入)这个信号是由EEPROM传数据到南桥。

n3. EE_DOUT O EEPROM Data Out(EEPROM数据输出) n 这个信号是由南桥传数据到EEPROM。

4. EE_CS O EEPROM Chip Select(片选信号)当这个信号有效时EEPROM被选择。

n八、PCI接口信号说明1. AD[31:0] I/O Address Data Bus(地址数据总线)n 是用来传送起始地址。

在内存或组态的交易期间,此地址的分辨率是一个双字组(Double Word)(即地址可被四整除),在读取或写入的交易期间,它是一个字节特定地址。

2. PAR I/O Parity Signal(同位信号)n 在地址阶段完成后一个频率,或是所有写入交易的数据阶段期间,在IDRY#被驱动到僭态后一个频率,由Initiator驱动。

所有读取交易的数据阶段期间,在TRDY#被驱动到僭态后一个频率,它也会被目前所寻址的Target驱动。

CPU Interface讯号说明

第二節CPU Interface訊號說明(1).A20GATE A20M#(2).RCIN# INIT# RESET(3).FERR# IGNNE#(4).SMI# SMIACT#(5).INTR NMIHub Interface說明Firmware Hub訊號說明: FWH[3:0]FWH[4]A20GATE(A20 GATE)SuperI/O的port92暫存器中,SGA20 bit若設為1,則A20GATE輸出為High,若設為0,則A20GATE輸出為Low。

A20M#(Mask A20位址位元20遮蔽)A20M#訊號是由ICH輸出至CPU的訊號。

此訊號是讓CPU 在Real Mode(真實模式)時模擬8086只有1M Byte(1百萬位元組)位址空間,當超過1Mbyte位址空間時A20M#為LOW,A20被驅動為0而使位址自動折返到第一個1M Byte 位址空間上。

RCIN#(Keyboard Controller Reset Processor鍵盤控制重置CPU)RCIN#訊號是由SuperI/O輸出至ICH。

鍵盤控制SuperI/O 產生RCIN#訊號至ICH,經由ICH再輸出INIT#訊號至CPU,進而達到重置CPU的目的。

INIT(Initialization啟始)為一由ICH輸出至CPU的訊號,與RESET功能上非常類似,但與RESET不同的是CPU內部L1 Cache和浮點運算操作狀態並沒被無效化。

但TLB(位址轉換參考暫存器)與BTB(分歧位址暫存器)內資料則被無效化了。

INIT另一點與RESET不同的是CPU必須等到在指令與指令之間的空檔才會被確認,而使CPU進入啟始狀態。

RESET(重置)當RESET為”HIGH”時CPU內部被重置到一個已知的狀態並且開始從位址OFFFFFFFOH讀取重置後的第一個指令。

CPU內部的TLB(位址轉換參考暫存器)、BTB(分歧位址暫存器)以及SDC(區段位址轉換快取記憶體)當重置發生時內部資料全部都變成無效。

南桥内部所有信号详解(中文解释)

南桥内部所有信号详解(中文解释)原创丗重庆-陈阿信南桥所有信号讲解(1)DMIDMI[0]TXN/P:O Direct Media Interface Differential Transmit Pair0DMI[0]RXP/N:I Direct Media Interface Differential Receive Pair0DMI_ZCOMP:I Impedance Compensation Input:这个信号决定了DMI输入的阻抗;DMI_IRCOMP:O Impedance/Current Compensation Output:这个信号决定了DMI输出的阻抗和偏置电流;(2)PCI EXPRESSPETp/n[1]:O PCI Express*Differential Transmit Pair1(3)LAN CONNECTORLAN_CLK:I频率范围在5MHz to50MHz.LAN_RXD[2:0]I接收数据:用这些信号向LAN控制器传输数据控制信号,这些信号均有上拉衰减电阻;LAN_TXD[2:0]O传输数据:LAN控制器用这些信号去给LAN IC 传输数据和命令信号。

LAN_RSTSYNC O LAN重置/同步:LAN IC的重置/同步信号;原创丗重庆-陈阿信(4)EEPROM InterfaceEE_SHCLK O这个信号对EPROM提供时钟。

EE_DIN I EEPROM Data In:这个信号从EPROM向南桥提供数据,有上拉电阻。

EE_DOUT O这个信号从南桥向EPROM提供数据。

EE_CS O EPROM芯片的选择信号;(5)Firmware Hub Interface/LPCFWH[3:0]/LAD[3:0]I/O输入输出的多元地址信号。

FWH[4]/LFRAME#O输出的多元帧数据信号。

(6)PCI InterfaceAD[31:0]I/O复合的地址数据信号,在第一个传输周期传输地址信号,在接下来的传输周期传输数据信号;在FRAME#有效时,是地址期,对于I/O操作,它是一个字节地;对于存储器操作和配置操作,则是双字地址。

PCI总线标准协议(中文版)

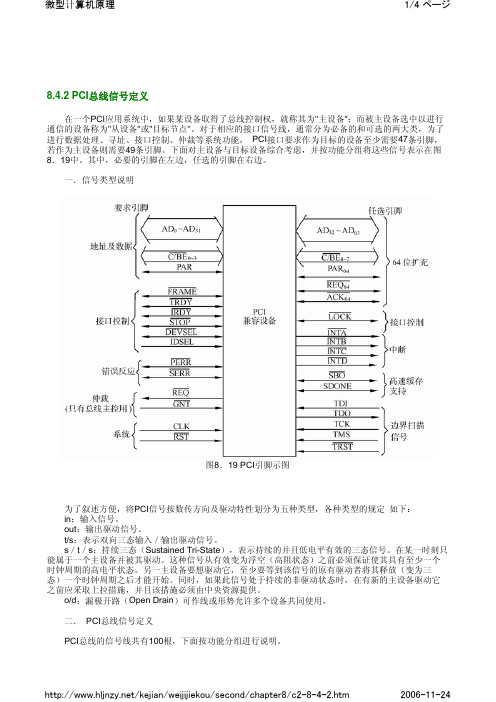

8.4.2 PCI总线信号定义在一个PCI应用系统中,如果某设备取得了总线控制权,就称其为"主设备";而被主设备选中以进行通信的设备称为"从设备"或"目标节点''。

对于相应的接口信号线,通常分为必备的和可选的两大类,为了进行数据处理、寻址、接口控制、仲裁等系统功能, PCI接口要求作为目标的设备至少需要47条引脚,若作为主设备则需要49条引脚。

下面对主设备与目标设备综合考虑,并按功能分组将这些信号表示在图8.19中。

其中,必要的引脚在左边,任选的引脚在右边。

一.信号类型说明图8.19 PCI引脚示图为了叙述方便,将PCI信号按数传方向及驱动特性划分为五种类型,各种类型的规定 如下:in:输入信号。

out:输出驱动信号。

t/s:表示双向三态输入/输出驱动信号。

s/t/s:持续三态(Sustained Tri-State),表示持续的并且低电平有效的三态信号。

在某一时刻只能属于一个主设备并被其驱动。

这种信号从有效变为浮空(高阻状态)之前必须保证使其具有至少一个时钟周期的高电平状态。

另一主设备要想驱动它,至少要等到该信号的原有驱动者将其释放(变为三态)一个时钟周期之后才能开始。

同时,如果此信号处于持续的非驱动状态时,在有新的主设备驱动它之前应采取上拉措施,并且该措施必须由中央资源提供。

o/d:漏极开路(Open Drain)可作线或形势允许多个设备共同使用,二. PCI总线信号定义PCI总线的信号线共有100根,下面按功能分组进行说明。

1.系统引线CLK in:时钟输入,为所有PCI上的接口传送提供时序。

其最高频率可达66MHz,最低频率一般为0(DC),这一频率也称为PCI的工作频率。

对于PCI的其他信号,除、、、之外,其余信号都在CLK的上升沿有效(或采样)。

in:复位,用来使PCI专用的特性寄存器和定时器相关的信号恢复规定的初始状况。

PCI总线信号说明

PCI總線信號定義PCI局部總線的信號線共有100根,下面按功能分組進行說明。

1.CLK IN:系統時鐘信號,對於所有的PCI設備都是輸入信號。

其頻率最高可達33MHz,最低頻率一般為0Hz(DC),這一頻率也稱為PCI的工作頻率。

對於PCI的其它信號,除RST#﹑IRQB#﹑IRQC#﹑IRQD#之外,其余信號都在CLK的上升沿有效(或采樣)。

2.RST# IN:用來使PCI專用的特性寄存器和定序器相關的信號恢復規定的初始狀態。

至PCI定序器之外的設備復位後如何變化,不屬於本說明的範圍。

但必要的PCI 配置寄存器,其復位狀態是明確規定的。

每當復位時,PCI的全部輸出信號一般都應驅動到第三態。

SERR#信號為高陰狀態,SBD#和SDONE可驅動到低電平(如果未提供三態輸出)。

REQ#和GNT# 必須同時驅動到第三態,不能在復位期間為高或為低。

為防止AD﹑C/BE#及PAR在復位期產浮動,可由中心設備將它們驅動到邏輯低,但不能驅動為高電平。

RST#和CLK可以不同步,但要保證其撤消邊沿沒有反彈。

當設備請求引導系統時,將響應復位,復位後響應系統引導。

3.AD〔31: : 00〕T/S它們是地址﹑數據多路復用的輸入/輸出信號。

在FRAME#有效時,是地址期;在IRDY#和TRDY#同時有效時,是數據期。

一個PCI總線的傳輸中包含了一個地址信號期和接著的一個(或無限個)數據期。

PCI總線支持突發方式的讀寫功能。

地址期為一個時鐘周期,該周期中AD〔31: : 00〕線上含有一物理地(32位)。

對I/O操作,它是一個字節地址;若是存儲器操作和醳操作,則是雙字地址。

在數據期,AD〔07: : 00〕為最低字節,AD〔31: : 24〕為最高字節。

當IRDY#有效時表示寫數據穩定有效,,而TRDY#有效時表示讀數據穩定有效。

4.C/BE〔3: : 0〕#T/S:它們是總線命令和字節使能多路復用信號線。

在地址期中,這四條線上傳輸的是總線命令;在數據期內,它們傳輸的是字節使能信號,用來表示在整個數據期中,AD〔31: : 00〕上哪些字節為有效數據。

PCI设备操作

备注 检查 PCI BIOS 是否 存在,及版 本号

查找指定 厂商和设 备号的 PCI 设备

查找指定 类代码和 索引号的 PCI 设备

36

读配置字节

AH:B1H AL:08H

Pointer

38H

保留,Reserved

3CH

优先级请求 时间片请求 中断引脚

中断线

MAX Lat

MIN Gnt

Interrupt pin Interrupt Line

表 5.1 PCI 设备的配置空间 在这 64 个字节中,第一个 32 位的地址包含了 DeviceID 和 VendorID,VendorID 是一 个 16 位的数,它由 PCISIG 分配,代表了制造这个板卡的厂商,如果插槽没有安装板卡, 从这个位置读出的值就为 FFFFH。DeviceID 由厂商自己分配,代表设备的类型。通过这两 个值就可以唯一的确定板卡。 Base Address,即基址寄存器,是 32 位寄存器,如果从这个位置读出的值最低位是 1, 代表 IO 地址,否则代表内存地址。系统加电后,引导程序通过向基址寄存器写入全 1,并 重新读回,如果认为最低位为 0,整个地址可以分成高位的全“1”部分,和低位的全“0” 部分。引导程序可以判断出全“0”部分是 PCI 设备自己寻址空间,因而可以确定板卡需要 资源的大小,并给它分配一块空闲的 I/O 或内存空间,并把分配地址的首地址写回到基址寄 存器。驱动程序可以通过读这个基址寄存器取得基地址,再加上设备的偏移地址就可以访问 这个设备的寄存器了。 例 1(PCI 设备资源配置): 以第一个基址寄存器为例,BIOS 对它进行配置的过程如下:

pci16位总线使用说明

16位总线操作模板(2009年5月7日)

1PCI16位总线操作模板

1.1功能描述

PCI总线操作模板

1.2调用时加载文件

pci_16_main.v

pci.ucf

dram_16_16_4k.xco

1.3调用示例

无

1.4接口说明

无

1.5使用流程

在“//在此添加自定义IO信号接口名称//”添加自定义IO接口名称。

在“//在此添加自定义IO接口定义//”添加自定义IO接口定义。

在“//在此添加自定义寄存器//”添加自定义寄存器。

在“//设置方向,写0是输出,写1是输入//”设置接口方向

在状态0修改项目编号,在状态2修改地址位置和板卡编号。

在“//添加用户代码//”处添加用户代码状态。

在“//在此添加自定义例化//”添加调用模块的例化。

2更改记录

1.更改时间:无

2.更改内容:无

3.应用项目:无。

PCI信号定义说明

PCI信号定义说明(中文版)1. AD[31:0] (PCI ADDRESS / DATA BUS)地址与数据总线讯号,在FRAME#启动后地址才有效,在PCLK第一个CLOCK 动作初始化时,FRAME#动作后,输出为地址与数据,写入周期,输入为数据,读取周期 TRDY# 与IRDY#会动作,高阻抗时,为数据转换周期或RESET#动作2. C/BE[3:0]# (PCI COMMAND /BYTE ENABLES)FRAME#启动后,CLOCK第一个CLOCK,周期为PCI命令, 再下一个周期为允许命令,命令在FRAME#后有效,数据在TRDY#与IRDY#后有效3. DEVSEL# (PCI DEVSEL SELECT)确定外部外围连结之响应讯号,高阻抗时,为停止周期或RESET#动作时4. FRAME# (PCI CYCLE FRAME)PCI 总线起始讯号5. GNT[4:0]# (PCI BUS GRANT)PCI 总线控制认可讯号6. IRDY# (INITIATOR READY)数据读取写入讯号7. LOCK# (PCI BUS LOCK)总线锁住讯号8. PAR (PCI BUS PARITY)地址与位传送之同位检错讯号9. PCLK (PCI CLOCK)PCI 时脉讯号10.PGNT# (PCI GRANT TO PERIPHERAL BUS CONTROLLER)PCI 总线对外部外围装置之需求同意认可讯号11. PERQ# (PCI REQUEST FROM PERIPHERAL BUS CONTROLLER)外围处理器对PCI总线要求讯号12. REQ[4:0]# (PCI BUS REQUEST)PCI 总线需求讯号13. RESET# (RESET)系统重置讯号14. SERR# (SYSTEM ERROR)系统错误侦测讯号可产生NMI 不可屏蔽中断15. STOP# (PCI BUS STOP)PCI 总线放弃或重试数据传送之讯号16. TRDY# (TARGET READY)PCI 总线数据读取传送讯号17.WSC# (WRITE SNOOP COMPLETE)I /O APIC 芯片有上时之中断讯息传送讯号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCI - Peripheral Component Interconnect

PCI 总线由Intel 在1993 年所發表. 是一高速总线. 支援32 bits , 33 MHz. 最後版本可支援至64 bits , 66 MHz. 但在PC 只支援到32 bits , 33 MHz.

下圖為PCI 系統之架構方塊圖.

( 取材自PCI 規格)

PCI bus 和Processor 是分開的. PCI 是由Chipset所控制. 所以PCI 可支援不同的CPU. 也可支援非Intel 相容的CPU. 在PCI bus 上可掛上支援PCI 架構的不同功能IC. 例如LAN , SCSI , Graphics 等. 而傳統的ISA bus 由Chipset 轉換. 也制定出PCI Slot 的規格. 根據此規格設計的PCI 介面卡可使用於任何PCI 系統. 每一PCI 系統最多可支援四個PCI Slot. 而PCI Slot 支援5V 和3.3V. 如下圖:

( 取材自PCI 規格)

PCI bus 的特性有:

∙高性能:

∙支援Burst Mode. 可一次傳送多筆資料. 此可有效提升讀和寫的效率. 特別在顯示系統上.

∙支援Bus master. 可獲得bus 的主控權.

∙可支援同時存取CPU 和記憶體.

∙支援Plug and Play.

∙支援不同的CPU.

支援5V 和 3.3V 的環境.PCI Interface 訊號說明

附表一

當它代表指令致能時,其義意如下:

當它代表位元組致能時,其義意如下:。