EP1C3T144C8芯片引脚对照表[0]

VGA彩条信号显示控制器设计解析

编号:EDA技术实训实训(论文)说明书题目:VGA彩条信号显示控制器设计院(系):信息与通信学院专业:电子信息工程学生姓名:***学号: ********** 指导教师:付强、陈小毛、归发第2013 年1 月4 日本设计采用EDA技术,通过FPGA芯片实现了实现VGA彩条信号的显示的设计,本文采用VHDL 硬件描述语言描述VGA彩条信号的显示电路,完成对电路的功能仿真。

通过按键来实现横彩条、竖彩条、棋盘式方格图案的选择。

显示图像分辨率为640×480,刷新率为60Hz。

与传统的设计方式相比,本设计由于采用了FPGA芯片来实现,它将大量的电路功能集成到一个芯片中,并且可以由用户自行设计逻辑功能,提高了系统的集成度和可靠性。

关键词:电子设计自动化、可编程门阵列、硬件描述语言、状态机This design used the EDA technology, through the FPGA chip realized the realization of the signal that striped VGA is adopted in this paper, the design of the VHDL hardware description language describe VGA striped signal display circuit and the completion of the function of the circuit simulation. By pressing buttons horizontal striped, perpendicular striped, chessboard type pane design choice. Display image resolution for 640 x 480, refresh rate of 60 Hz ac. Compared with the traditional design methods, the design with FPGA chip to achieve, it will be a lot of circuit function integration to a chip, and can be by the user to design logical function, improve the system integrity and reliability.Keywords:Electronic Design Automatic technology,Flied Programmable,Gate Array, Hardware Description Language, State Machine1. 绪论 (1)1.1 EDA技术的发展 (1)1.2 课程设计的任务 (1)2. 系统设计 (2)2.1 系统的工作原理 (2)2.2 VGA显示原理 (2)2.3 键盘驱动 (4)3 系统设计 (4)3.1图像信号产生模块的设计 (4)3.2 视频输出接口电路部分设计 (5)3.3 模式控制与显示部分设计 (6)3.4 VGA显示模块 (6)4 课程设计心得 (9)5 致谢 (10)参考文献 (11)附录 (12)附录A 总原理图 (12)附录B 实验现象 (12)附录C 引脚分布图 (14)附录D 实验程序 (14)1.绪论1.1 EDA技术的发展我们已经进入数字化和信息化的时代,其特点就是各种数字产品的广泛应用。

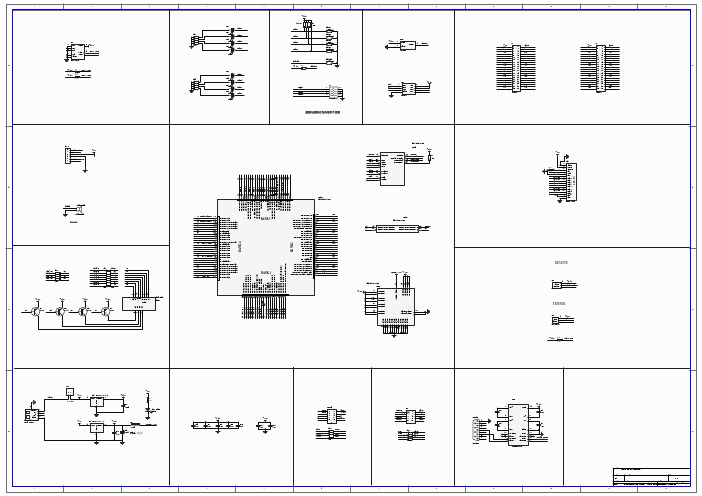

FPGA 开发板原理图 EP1C3T144C8

2

U1

1 2 3

A1 A2 A3

VCC

7 4

SCL WP SDA GND

AT24C16

8 +3.3V

6 AT24_SCL 5 AT24_SDA

A

+3.3V R2 4.7K

+3.3V R3 4.7K

AT 24 _SCL AT 24 _SD A

3

4

5

6

7

8

D1 LED1

D2

R5

LED

LED2

D3 LED

GND GND

22 23

MSEL 0 MSEL 1

nCE

21 20

nCE n CE O

U3D EP1C3T144C8

16 17

16 17

CLK0, LVDS CLK1p CLK1, LVDS CLK1n

CLK2, LVDS CLK2p CLK3, LVDS CLK2n

93 CLKIN 92 92

VDDA_1.2V +1.2V

EP1C3T144C8 U3B

+3.3V

DATA 13

TDI 95 TDO 90 TCK 88 TMS 89

DATA0

TDI TDO TCK TMS

DCLK CONF_DONE

nCONFIG nSTATUS

24 86 14 87

DCL K nCONF_DOWN nCONFIG nSTATUS

R11 4.7K

6 8

9 C3

12 C4

72 UART_RXD0 72

71

71

70 UART_TXD0 70

69

69

68

ep1c3管脚排列及功能

CycloneII特殊管脚的使用解析

CycloneII特殊管脚的使用 EP2C5T144C8N/EP2C5Q208C8N 1/1.I/O, ASDO 在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。

在AS 模式下,这个脚是CII 向串行配置芯片发送控制信号的脚。

也是用来从配置芯片中读配置数据的脚。

在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效,配置完成后,该脚就变成三态输入脚。

ASDO 脚直接接到配置芯片的ASDI 脚(第5 脚)。

2/2.I/O,nCSO 在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用.在AS 模式下,这个脚是CII 用来给外面的串行配置芯片发送的使能脚。

在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效。

这个脚是低电平有效的。

直接接到配置芯片的/CS 脚(第1 脚)。

3/3.I/O,CRC_ERROR 当错误检测CRC 电路被选用时,这个脚就被作为CRC_ERROR 脚,如果不用默认就用来做I/O。

但要注意,这个脚是不支持漏极开路和反向的。

当它作为CRC_ERROR 时,高电平输出则表示出现了CRC 校验错误(在配置SRAM 各个比特时出现了错误)。

CRC 电路的支持可以在setting 中加上。

这个脚一般与nCONFIG 脚配合起来用。

即如果配置过程出错,重新配置. 4/4.I/O,CLKUSR 当在软件中打开Enable User-supplled start-up clock(CLKUSR选项后,这个脚就只可以作为用户提供的初始化时钟输入脚。

在所有配置数据都已经被接收后,CONF_DONE 脚会变成高电平,CII 器件还需要299 个时钟周期来初始化寄存器,I/O 等等状态,FPGA 有两种方式,一种是用内部的晶振(10MHz),另一种就是从CLKUSR 接进来的时钟(最大不能超过100MHz)。

有这个功能,可以延缓FPGA 开始工作的时间,可以在需要和其它器件进行同步的特殊应用中用到。

EP1C3T144FPGAdevelopboardmanual(开发板原理图)

EP1C3T144FPGAdevelopboardmanual(开发板原理图)FPGA develop board manual ALTERA Cyclone EP1C3T144ALTERA Cyclone 系列的fpga是altera 公司针对底端用户推出的一个系列的fpga。

具有成本低,使用的方便的优点,规模从3000到20000LE。

这一块实验板用的EP1C3T144的芯片,有3000LE逻辑资源,另外还有13条M4K RAM (共6.5Kbyte),另外还有还有一个数字锁相环。

这些资源能够足够应付电子设计竞赛和日常教学的需要,也可以作为初学者入门学习fpga的工具。

1. 开发板介绍1.1. 总体介绍开发板的电路图,如附录所示,电路图一共可分为9个部分:电源部分、按键和LED、下载配置部分、复位部分、外部时钟、滤波电容、用户扩展接口、5 1单片机接口、FPGA 芯片。

1.2. 具体介绍1.2.1. 电源部分板子由外部提供5V电源,使用的圆头插座的封装,可以直接用5V的电源适配器插上使用,不需要直流稳压电源,FPGA的IO的电源是3.3V,内核的电压是1.5V,所以用上两个LEO,一个将5V转到3.3V,另一个将3.3V转到1.5V,加上一些滤波电容,板上的其他外设的电源均是3.3V,另外有3.3V的电源指示灯,表示电源是否正常,还有防反插二极管,防止电源反插,对器件造成损坏。

1.2.2. 按键和LED板上提供4个拨码按键和4个led,分别接到fpga的8个IO引脚上,具体的引脚可以参看电路图或者丝印。

对于初学者,按键和led 可以用外当成最简单的外设,用和来控制这些外设。

对于用该板作开发的用户来说,可以把按键当成键盘控制,而把led当成提示来用。

1.2.3. 下载配置部分大家都知道fpga是sram型的可编程逻辑器件,不像rom型可编程器件cpld那样,通过jtag就可以直接把代码固化片子里面。

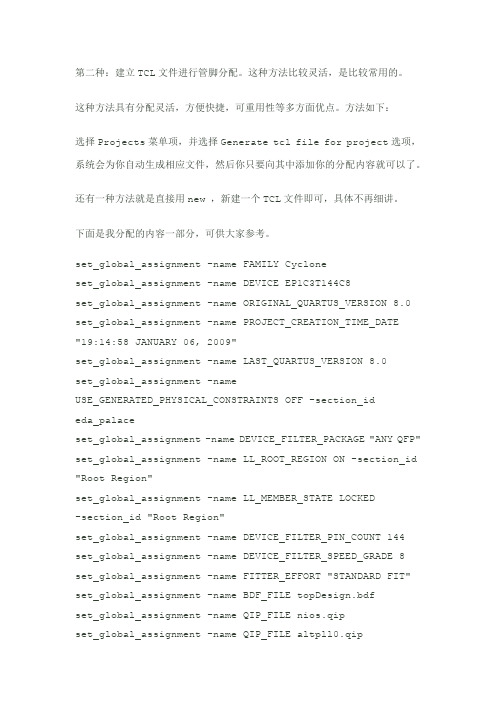

FPGA引脚分配方法

第二种:建立TCL文件进行管脚分配。

这种方法比较灵活,是比较常用的。

这种方法具有分配灵活,方便快捷,可重用性等多方面优点。

方法如下:选择Projects菜单项,并选择Generate tcl file for project选项,系统会为你自动生成相应文件,然后你只要向其中添加你的分配内容就可以了。

还有一种方法就是直接用new ,新建一个TCL文件即可,具体不再细讲。

下面是我分配的内容一部分,可供大家参考。

set_global_assignment -name FAMILY Cycloneset_global_assignment -name DEVICE EP1C3T144C8set_global_assignment -name ORIGINAL_QUARTUS_VERSION 8.0 set_global_assignment -name PROJECT_CREATION_TIME_DATE "19:14:58 JANUARY 06, 2009"set_global_assignment -name LAST_QUARTUS_VERSION 8.0set_global_assignment -nameUSE_GENERATED_PHYSICAL_CONSTRAINTS OFF -section_ideda_palaceset_global_assignment -name DEVICE_FILTER_PACKAGE "ANY QFP" set_global_assignment -name LL_ROOT_REGION ON -section_id "Root Region"set_global_assignment -name LL_MEMBER_STATE LOCKED-section_id "Root Region"set_global_assignment -name DEVICE_FILTER_PIN_COUNT 144 set_global_assignment -name DEVICE_FILTER_SPEED_GRADE 8 set_global_assignment -name FITTER_EFFORT "STANDARD FIT" set_global_assignment -name BDF_FILE topDesign.bdfset_global_assignment -name QIP_FILE nios.qipset_global_assignment -name QIP_FILE altpll0.qipset_global_assignment -name USE_CONFIGURATION_DEVICE ON set_global_assignment -name STRATIX_DEVICE_IO_STANDARD "3.3-V LVTTL"set_global_assignment -name PARTITION_NETLIST_TYPE SOURCE -section_id Topset_global_assignment -name PARTITION_COLOR 14622752-section_id Topset_location_assignment PIN_72 -to addr[7]set_location_assignment PIN_69 -to addr[6]set_location_assignment PIN_70 -to addr[5]set_location_assignment PIN_67 -to addr[4]set_location_assignment PIN_68 -to addr[3]set_location_assignment PIN_42 -to addr[2]set_location_assignment PIN_39 -to addr[1]set_location_assignment PIN_40 -to addr[0]set_location_assignment PIN_48 -to data[15]set_location_assignment PIN_47 -to data[14]set_location_assignment PIN_50 -to data[13]set_location_assignment PIN_49 -to data[12]set_location_assignment PIN_56 -to data[11]set_location_assignment PIN_55 -to data[10]set_location_assignment PIN_58 -to data[9]set_location_assignment PIN_57 -to data[8]set_location_assignment PIN_61 -to data[7]set_location_assignment PIN_62 -to data[6]set_location_assignment PIN_59 -to data[5]set_location_assignment PIN_60 -to data[4]set_location_assignment PIN_53 -to data[3]set_location_assignment PIN_54 -to data[2]set_location_assignment PIN_51 -to data[1]set_location_assignment PIN_52 -to data[0]set_location_assignment PIN_16 -to clkset_location_assignment PIN_38 -to csset_location_assignment PIN_141 -to led[3]set_location_assignment PIN_142 -to led[2]set_location_assignment PIN_143 -to led[1]set_location_assignment PIN_144 -to led[0]set_location_assignment PIN_33 -to reset_nset_location_assignment PIN_41 -to rdset_location_assignment PIN_71 -to wrset_location_assignment PIN_105 -to mosiset_location_assignment PIN_107 -to sclkset_location_assignment PIN_106 -to ssset_location_assignment PIN_73 -to motor[0]set_location_assignment PIN_74 -to motor[1]set_location_assignment PIN_75 -to motor[2]set_location_assignment PIN_76 -to motor[3]set_instance_assignment -name PARTITION_HIERARCHY root_partition -to | -section_id Top# Commit assignmentsexport_assignmentsFPGA 点滴(2008-09-30 09:44:45)转载标签:杂谈以此记录心得以及重要的知识点。

引脚表

附录E LP-2900开发装置FPGA引脚分配LP-2900以Altera公司EPF10K10TC144-4型或EP1C3T144C8型FPGA为核心,外部接口资源有8个电平按键、6个脉冲按键、2个8位的DIP拨动开关,1个3×4的键盘阵列、34个发光二极管、6个以动态扫描方式连接的共阴七段显示器,1个8×8的双色发光二极管阵列,1个音频蜂鸣器,一个16×2字符的液晶显示屏。

另外还有1片8位的逐次比较模数转换器ADC0804和1片8位的R-2R倒T网络的数模转换器AD7528。

由于开发装置上FPGA 芯片的I/O引脚已经在硬件上与各外部设备相连,设计时必须按照引脚连接关系进行FPGA 引脚分配。

以下按LP2900开发装置面板的划分区域介绍各外设与EPF10K10TC144或EP1C3T144C8的接口关系,由于FPGA的I/O端口有限,所以某些外设受相同的FPGA引脚控制,使用时需要注意。

1.FPGA主板FPGA主板独立于LP-2900的面板,主板上有一片Altera的FLEX10K系列芯片EPF10K10TC144或CYCLONE系列的芯片EP1C3T144C8、一个EPROM插座或一片配置芯片EPS1和一个复位按键RESET。

主板外围有一圈LED发光二极管,每一个都与EPF10K10TC144-4的一个I/O端口对应连接。

使用者可以通过LED了解FPGA相应I/O端口的状态。

当端口信号为高电平时,LED亮;低电平时,LED灭。

2.电平按键与开关(J区)J区位于LP2900开发装置面板左下方,有8个带LED显示的电平按键SW1~SW8和2组8位的DIP拨动开关SW9~SW24,位置分布见附录C,与FPGA的连接关系见表E-1。

SW1~SW8按键按下时灯亮,FPGA相应的I/O端口输入高电平;反之灯灭,端口输入低电平。

SW9~SW24拨向上FPGA相应的I/O端口输入高电平;拨向下时FPGA端口输入低电平。

EP1C6Q240C8封装和部分引脚的功能分析

EP1C6Q240C8封装和部分引脚的功能分析图U21A图U21B图U21C图U21D第一部分:封装图U21A、U21B、U21C、U21D表示的是同一块芯片EP1C6Q240C8,有240个引脚,采用的是PQFP封装(即Plastic Quad Flat Package,塑料方块平面封装),PQFP封装的芯片的四周均有引脚,而且引脚之间距离很小,管脚也很细,一般大规模或超大规模集成电路采用这种封装形式.用这种形式封装的芯片必须采用SMT(Surface Mount Technology,表面组装技术)将芯片边上的引脚与主板焊接起来。

对于SMT技术,个人理解,即表面组装技术,一般用来焊接一些引脚在几百以上的芯片,比如说BGA,PGA一般都采用这种技术;例如笔记本主板上的intel北桥芯片,一般都采用球形封装,又如比较古老的Intel 965底部球形引脚大约有600多个,现在笔记本流行用的P43、P45、P55、X58,从P43一代引脚多达几千个甚至更多,这样做的好处是节约面积,坏处是测试的时候比较麻烦,像BGA这种封装的芯片一般焊上去之后,顶部要引出几个接点,以防止在使用过程中坏掉,方便用万用表或者示波器来测试各个通路便于修理.对于这几种类型的芯片,除了PQFP少数罕见的高手能手工焊接之外,一般都采用贴片机来进行专门的焊接工作。

这里简单介绍一下这两种封装:PQFP/PFP封装具有以下特点1.适用于SMD表面安装技术在PCB电路板上安装布线。

2.适合高频使用。

2.操作方便,可靠性高。

3.芯片面积与封装面积之间的比值较小。

4.Intel系列CPU中80286、80386和某些486主板采用这种封装形式。

这里的SMD表示的是贴片组装器件;BGA球栅阵列封装随着集成电路技术的发展,对集成电路的封装要求更加严格.产品的功能性,当IC的频率超过100MHz时,传统封装方式可能会产生所谓的“CrossTalk(串扰)”现象,而且当IC的管脚数大于208 Pin时,传统的封装方式有其困难度。

EP1K30TC144-3N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

重新配置ACEX 1K设备能力,货物可实现完整测试之前,让设计师专注于 模拟和设计验证. ACEX 1K器件可重构消除库存管理门阵列设计和 测试向量生成故障覆盖率.

表4 示出一些常见设计ACEX 1K器件性能. 所有性能结果与SynopsysDesignWare或获得 LPM功能.实行特殊设计方法不要求 该应用程序;设计人员只需推断或以实例化一个函数 Verilog HDL语言,VHDL,Altera硬件描述语言(AHDL),或原理图 设计文件.

用逻辑诸如计数器,加法器,状态机,和多路复用器.嵌入式和逻辑 阵列结合提供高性能和嵌入式门阵列高密度,使设计人员能够实现整个 系统在单个设备上.

Units

MSPS µs MHz MHz

13

Tools

ACEX 1K器件是在系统上电与存储在一个Altera串行配置设备或由系统

控制器提供数据进行配置.

Altera提供EPC16,EPC2,EPC1和EPC1441配置设备,

芯片中文手册,看全文,戳

2003年 5月 ,版本 . 3.4

ACEX 1K

可编程逻辑器件系列

®

数据表

特征...

■ 可编程逻辑器件(PLD),提供低成本

系统级可编程单芯片(SOPC)集成在一个单一

设备

– 为实现宏功能增强嵌入式阵列

如高效内存和专门逻辑功能

– 每个嵌入式阵列高达16位宽度双端口能力

– 多达六个全局时钟信号和四个全局清除信号

■ 强大I / O引脚

– 个人三态输出使能控制每个引脚

– 每个I / O引脚漏极开路选项

– 可编程输出摆率控制,以降低开关

noise

– 钳到V

CCIO 在销逐针基础用户可选

altera EP1k30引脚说明

EP1k30TC144引脚说明

(1)在列表中未出现的其他管脚为用户I/O管脚。

(2)该引脚是专用引脚,不能用作用户I/O管脚。

(3)如果该引脚不用做器件级信号或配置功能,则可用作用户I/O。

(4)配置后该引脚可以用作用户I/O。

(5)该引脚在用户模式时为三态。

(6)可选择的JTAG引脚TRST管脚在144个引脚的TQFP封装中并不使用。

(7)这个管脚驱动ClockLock和ClockBoost电路。

(8)这个管脚显示了ClockLock和ClockBoost电路的状态。

当ClockLock和ClockBoost电路锁定在输入时钟上或产生内部时钟时,LOCK为高电平;否则输出低电平。

该引脚是可选择的,当不使用该引脚时,该引脚可以用作用户I/O。

(9)该引脚是锁相环ClockLock和ClockBoost电路的电源和地。

为了保证一定的噪声阻抗,该电源和地应该和器件所使用的其他电源和地之间进行隔离。

如果不使用锁相环,该引脚应该连接到VCCINT或GNDINT。

(10)用户I/O引脚,包括专门的输入信号,专门的时钟引脚和所有的I/O引脚。