数字电路课程设计用各种芯片资料管脚图

四人抢答器电路设计数字电子技术课程设计

题目:抢答器电路设计一、设计任务与要求(1)可容纳四组参赛的数字式抢答器。

(2)当某台参赛者按下抢答开关时,由数码管显示该台编号并伴有声响。

此时,抢答器不再接收其他输入信号。

(3)电路具有定时功能。

要求回答问题的时间≤60秒(显示为00~59),时间显示采用倒计时方式。

当达到限定时间时,发出声响提示。

(4)具有计分功能。

要求能设定初始分值,能进行加减分。

(5)在复位状态下台号数码管不作任何显示(灭灯)。

二、方案设计与论证抢答器的基本工作原理:1、当主持人按下“开关”按钮后,选手可以通过按按钮的快慢来决定由谁来回答,按得快的选手的编号显示在电子显示管上并伴有响声。

2、此后选手输入被锁住,如果主持人按下复位键则编号显示处不作任何显示。

3、然后主持人就按下计时开关,选手开始作答,作答的时间少于60秒,以倒数的方式进行,而且通过显示屏把时间显示出来。

4、当选手作答仅剩10秒时,开始通过喇叭响来做提示。

如果到了显示“00”时,计时器不再进行倒数而停留在“00”状态。

5、此时选手仍没有作答成功,则主持人会对该选手进行减分处理,如果在“00”之前作答成功则加分,分数也是通过计分器显示出来。

6、之后主持人按下开关,所有的显示及工作状态回到初始状态以便进行下一次答题。

原理框架图(图1)图1.原理框架图方案一、对照上面原理框架图,各个主要的部分选用对应功能的芯片进行设计,如果在仿真时没能找到相应的芯片则用相近的。

比如在选手抢答时的输入用74148优先编码器进行编码让一个输入有效,并用七段显示译码器显示出台号。

方案二、对照框架图,选用各种逻辑站以及相关的逻辑函数进行设计,编号进直接把锁存器的输出转化8421BCD码,并通过逻辑函数表达式的方式输入到显示译码器中让其显示出来。

通过比较可以得出方案一更可行,理由在于芯片组上集成的功能要强大些,且用的元器件的数目会相对少一些这样会更美观而且不容易出错。

三、单元电路设计与参数计算1、封锁电路封锁电路的主要功能是分辨选手按键的先后,并能把第一个抢答者的编号锁存起来,并使其他选手的按键操作无效。

十二进制计数器

郑州科技学院《数字电子技术》课程设计题目十二进制计数器学生姓名丁洪宝专业班级电科一班学号201031018院(系)电气工程学院指导教师袁玉霞完成时间 2013年03月15日目录1实验概述 (1)1.1计数器设计目的 (2)1.2计数器设计组成 (2)2十二进制计数器设计描述 (2)2.1设计原理 (2)2.2设计的思路 (3)2.3设计的实现 (4)3十二进制计数器的设计与仿真 (5)3.1基本电路分析设计 (5)3.2计数器电路的仿真 (8)4总结 (9)参考文献 (11)附录1:实验电路图 (12)附录2:元器件清单 (13)1 实验简述计数器是一个用以实现计数功能的时序部件,它不仅可用来及脉冲数,还常用作数子系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

计数器种类很多。

按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。

根据计数制的不同,分为二进制计数器、十进制计数器和任意进制计数器。

根据计数器的增减趋势,又分为加法、减法和可逆计数器。

还有可预制数和可变程序功能计数器等等。

目前,无论是TTL还是CMOS集成电路,都有品种较齐全的中规模集成计数器。

使用者只要借助于器件手册提供的功能和工作波形图以及引出端的排列,就能正确运用这些器件。

计数器在现代社会中用途中十分广泛,在工业生产、各种和记数有关电子产品。

如定时器,报警器、时钟电路中都有广泛用途。

在配合各种显示器件的情况下实现实时监控,扩展更多功能。

1.1计数器设计目的1)每隔1s,计数器增1;能以数字形式显示时间。

2)熟练掌握计数器的各个部分的结构。

3)计数器间的级联。

4)不同芯片也可实现十二进制。

1.2 计数器设计组成1)用两个74LS160芯片和一个与非门实现。

2)当定时器递增到12时,定时器会自动返回到01显示,然后继续计时。

本设计主要设备是两个74LS160同步十进制计数器,并且由200HZ,5V电源供给。

74ls148管脚图引脚功能表真值表逻

74ls148管脚图引脚功能表真值表逻

有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的。

于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。

不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

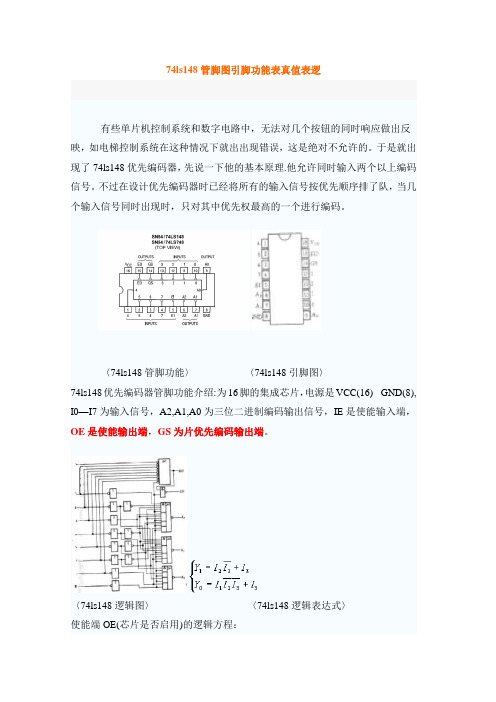

〈74ls148管脚功能〉〈74ls148引脚图〉

74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8), I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS为片优先编码输出端。

〈74ls148逻辑图〉〈74ls148逻辑表达式〉

使能端OE(芯片是否启用)的逻辑方程:

<74ls148真值表>

由74ls148真值表可列输出逻辑方程为:

A2 = (I4+I5+I6+I7)IE

A1 = (I2I4I5+I3I4I5+I6+7)·IE

A0 = (I1I2I4I6+I3I4I6+I5I6+I7)·IE

用两个74ls148优先编码器芯片扩展为十六线-四线优先编码器的电路连线图。

篮球比赛30秒倒计时电路设计

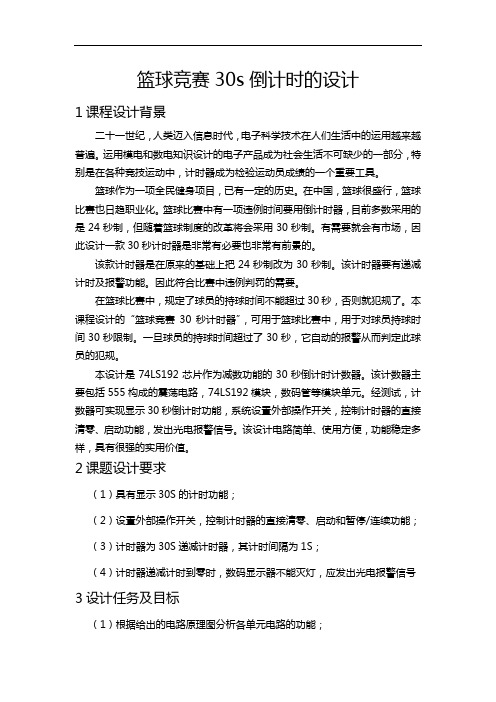

篮球竞赛30s倒计时的设计1课程设计背景二十一世纪,人类迈入信息时代,电子科学技术在人们生活中的运用越来越普遍。

运用模电和数电知识设计的电子产品成为社会生活不可缺少的一部分,特别是在各种竞技运动中,计时器成为检验运动员成绩的一个重要工具。

篮球作为一项全民健身项目,已有一定的历史。

在中国,篮球很盛行,篮球比赛也日趋职业化。

篮球比赛中有一项违例时间要用倒计时器,目前多数采用的是24秒制,但随着篮球制度的改革将会采用30秒制。

有需要就会有市场,因此设计一款30秒计时器是非常有必要也非常有前景的。

该款计时器是在原来的基础上把24秒制改为30秒制。

该计时器要有递减计时及报警功能。

因此符合比赛中违例判罚的需要。

在篮球比赛中,规定了球员的持球时间不能超过30秒,否则就犯规了。

本课程设计的“篮球竞赛30秒计时器”,可用于篮球比赛中,用于对球员持球时间30秒限制。

一旦球员的持球时间超过了30秒,它自动的报警从而判定此球员的犯规。

本设计是74LS192芯片作为减数功能的30秒倒计时计数器。

该计数器主要包括555构成的震荡电路,74LS192模块,数码管等模块单元。

经测试,计数器可实现显示30秒倒计时功能,系统设置外部操作开关,控制计时器的直接清零、启动功能,发出光电报警信号。

该设计电路简单、使用方便,功能稳定多样,具有很强的实用价值。

2课题设计要求(1)具有显示30S的计时功能;(2)设置外部操作开关,控制计时器的直接清零、启动和暂停/连续功能;(3)计时器为30S递减计时器,其计时间隔为1S;(4)计时器递减计时到零时,数码显示器不能灭灯,应发出光电报警信号3设计任务及目标(1)根据给出的电路原理图分析各单元电路的功能;(2)熟悉电路中所用到的各集成块的管脚及其功能;(3)进行电路的安装、调试,直到电路能达到规定的设计目标;(4)写出完整、详细的课程设计报告。

4课题设计框图5电路设计5.1设计原理分析设计任务,该系统包括秒脉冲发生器、计数器、译码显示电路、控制电路和报警电路5个部分构成。

数字电路课程设计---霓虹灯控制电路设计报告

表4 74LS04非门的真值表

4)74LS08与门的引脚图如图10所示,其真值表如表5所示:

图10 74LS08管脚图

表574LS08与门的真值表

3.2 实现控制功能的电路

1) 电路中有有3个74LS194芯片,共有5个状态,可以用74LS161和74LS138来实现,电路如图11所示:

广告彩灯作为广告的一个重要元素,也渐渐成为广告的灵魂,也成为了城市夜景的一道亮丽的风景线。

刚刚学完了数电知识,正好通过这次课程设计,进一步巩固了理论知识,而且全面掌握了课设的基本流程,此外,分析与解决问题的能力也得到了相应的提升。

此次设计我们用到了555定时器构成的秒脉冲发生器,74LS138,74LS161,JK触发器以及各种逻辑门电路来实现我的方案,充分利用了模电和数电的知识来不断地解决实验过程中发现的问题,这也是这次课程设计的目的和意义所在。

1)JK触发器的管脚图和真值分别如图7所示:Q Q

SD J CP K RD

图7 JK触发器管脚图

表2 JK触发器真值表

J

K

Qn+1

逻辑功能

0

0

Qn

保持

0

1

0

置0

1

0

1

置1

1

1

Qn

翻转

2)74LS00与非门的管脚图如图8所示,真值表如表3所示:

图8 74LS00管脚图

表3 74LS00的真值表

3)74LS04非门的引脚图如图9所示,真值表如表4所示:

图6信号分频及选择

JK触发器下降沿有效,J=K=1时,每来一个脉冲变化一次,因此它的输出是1.6S的信号,当Y3与Y4同时为1,根据电路,可以知道此时为单层灯移动,另外根据分频电路可以知道此时输出的也为0.8s的信号,而当Y3和Y4中有一个0时,电路为全部左移或全部右移的过程。此时电路输出的也为1.6s的信号,实现了分频和信号的选择的过程。

74ls147引脚图管脚图和功能真值表

74ls147引脚图管脚图和功能真值表优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最高的输入信号进行编码。

常用的集成优先编码器IC有10线-4线、8线-3线两种。

10线-4线优先编码器常见的型号为54/74147、54/74LS147,8线-3线优先编码器常见的型号为54/74148、54/74LS148。

下面我们以TTL中规模集成电路74LS147为例介绍8421→BCD码优先编码器的功能。

10线-4线8421 BCD码优先编码器74LS147的真值表见表3.5。

74LS147的引脚图如图3.5所示,其中第9脚NC为空。

74LS147优先编码器有9个输入端和4个输出端。

某个输入端为0,代表输入某一个十进制数。

当9个输入端全为1时,代表输入的是十进制数0。

4个输出端反映输入十进制数的BCD 码编码输出。

74LS147优先编码器的输入端和输出端都是低电平有效,即当某一个输入端低电平0时,4个输出端就以低电平0的输出其对应的8421 BCD编码。

当9个输入全为1时,4个输入出也全为1,代表输入十进制数0的8421 BCD编码输出。

表3.5 74LS147的真值表数字电路CD4511的原理(引脚及功能)CD4511是一个用于驱动共阴极 LED (数码管)显示器的 BCD 码—七段码译码器,特点:具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS电路能提供较大的拉电流。

可直接驱动LED显示器。

CD4511 是一片 CMOS BCD—锁存/7 段译码/驱动器,引脚排列如图 2 所示。

其中a b c d 为 BCD 码输入,a为最低位。

LT为灯测试端,加高电平时,显示器正常显示,加低电平时,显示器一直显示数码“8”,各笔段都被点亮,以检查显示器是否有故障。

BI为消隐功能端,低电平时使所有笔段均消隐,正常显示时, B1端应加高电平。

另外 CD4511有拒绝伪码的特点,当输入数据越过十进制数9(1001)时,显示字形也自行消隐。

数字集成电路课程设计74hc138

目录1.目的与任务 (1)2.教学内容基要求 (1)3.设计的方法与计算分析 (1)3.1 74H C138芯片简介 (1)3.2 电路设计 (3)3.3功耗与延时计算 (6)4.电路模拟 (14)4.1直流分析 (15)4.2 瞬态分析 (17)4.3功耗分析 (19)5.版图设计 (19)5.1 输入级的设计 (19)5.2 内部反相器的设计 (19)5.3输入和输出缓冲门的设计 (22)5.4内部逻辑门的设计 (23)5.5输出级的设计 (24)5.6连接成总电路图 (24)5.3版图检查 (24)6.总图的整理 (26)7.经验与体会 (26)8.参考文献 (26)附录 A 电路原理图总图 (28)附录B总电路版图 (29)集成1. 目的与任务本课程设计是《集成电路分析与设计基础》的实践课程,其主要目的是使学生在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础上,训练综合运用已掌握的知识,利用相关软件,初步熟悉和掌握集成电路芯片系统设计→电路设计及模拟→版图设计→版图验证等正向设计方法。

2. 教学内容基本要求2.1课程设计题目及要求器件名称:3-8译码器的74HC138芯片 要求电路性能指标:⑴可驱动10个LSTTL 电路(相当于15pF 电容负载); ⑵输出高电平时,OH I ≤20uA,min,OH V =4.4V; ⑶输出低电平时,OLI ≤4mA ,manOL V , =0.4V⑷输出级充放电时间r t =ft ,pdt <25ns ;⑸工作电源5V ,常温工作,工作频率workf =30MHZ ,总功耗maxP =15mW 。

2.2课程设计的内容 1. 功能分析及逻辑设计; 2. 电路设计及器件参数计算;3. 估算功耗与延时;4. 电路模拟与仿真;5. 版图设计;6. 版图检查:DRC 与LVS ;7. 后仿真(选做);8. 版图数据提交。

2.3课程设计的要求与数据1. 独立完成设计74HC138芯片的全过程;2. 设计时使用的工艺及设计规则: MOSIS:mhp_ns5;3. 根据所用的工艺,选取合理的模型库;4. 选用以lambda(λ)为单位的设计规则;3. 设计的方法与计算分析3.1 74HC138芯片简介74HC138是一款高速CMOS器件,74HC138引脚兼容低功耗肖特基TTL 系列图3-1 74HC138管脚图表3-1 74HC138真值表由于74HC138芯片是由两个2-4译码器组成,两个译码器是独立的,所以,这里只分析其中一个译码器。

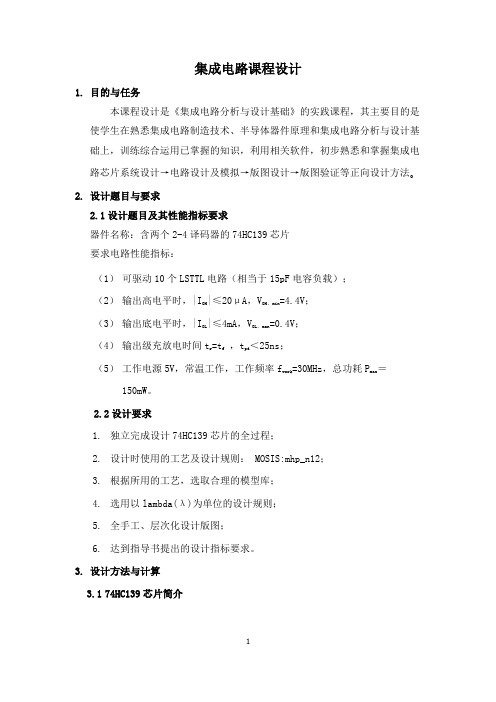

含两个2-4译码器的74HC139芯片版图

集成电路课程设计1. 目的与任务本课程设计是《集成电路分析与设计基础》的实践课程,其主要目的是使学生在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础上,训练综合运用已掌握的知识,利用相关软件,初步熟悉和掌握集成电路芯片系统设计→电路设计及模拟→版图设计→版图验证等正向设计方法。

2. 设计题目与要求2.1设计题目及其性能指标要求器件名称:含两个2-4译码器的74HC139芯片 要求电路性能指标:(1) 可驱动10个LSTTL 电路(相当于15pF 电容负载); (2) 输出高电平时,|I OH |≤20μA ,V OH ,min =4.4V ; (3) 输出底电平时,|I OL |≤4mA ,V OL ,man =0.4V ; (4) 输出级充放电时间t r =t f ,t pd <25ns ;(5) 工作电源5V ,常温工作,工作频率f work =30MHz ,总功耗P max =150mW 。

2.2设计要求1. 独立完成设计74HC139芯片的全过程;2. 设计时使用的工艺及设计规则: MOSIS:mhp_n12;3. 根据所用的工艺,选取合理的模型库;4. 选用以lambda(λ)为单位的设计规则;5. 全手工、层次化设计版图;6. 达到指导书提出的设计指标要求。

3. 设计方法与计算 3.1 74HC139芯片简介74HC139是包含两个2线-4线译码器的高速CMOS 数字电路集成芯片,能与TTL 集成电路芯片兼容,它的管脚图如图1所示,其逻辑真值表如表1所示:图1 74HC139芯片管脚图 表1 74HC139真值表计时只需分析其中一个2—4译码器即可,从真值表我们可以得出Cs 为片选端,当其为0时,芯片正常工作,当其为1时,芯片封锁。

A1、A0为输入端,Y0-Y3为输出端,而且是低电平有效。

2—4译码器的逻辑表达式,如下所示:01010A A C A A C Y s s ⋅⋅=++= 01011A A C A A C Y s s ⋅⋅=++=01012A A C A A C Y s s ⋅⋅=++= 01013A A C A A C Y s s ⋅⋅=++=74HC139的逻辑图如图2所示:图2 74HC139逻辑图3.2 电路设计本次设计采用的是m12_20的模型库参数进行各级电路的尺寸计算,其参数如下: NMOS: εox =3.9×8.85×10﹣12F/m μn =605.312×10﹣4㎡/Vst ox =395×10﹣10m V tn =0.81056V PMOS: εox =3.9×8.85×10﹣12F/m μp =219×10﹣4㎡/Vst ox =395×10﹣10m V tp =﹣0.971428V 3.2.1 输出级电路设计根据要求输出级电路等效电路图如图3所示,输入Vi 为前一级的输出,可认为是理想的输出,即V IL =Vss, V IH =V DD 。