正弦信号发生器方案设计

基于DSP设计正弦信号发生器

基于DSP设计正弦信号发生器一.设计目的设计一个基于DSP的正弦信号发生器二.设计内容利用基于CCS开发环境中的C54X汇编语言来实现正弦信号发生装置。

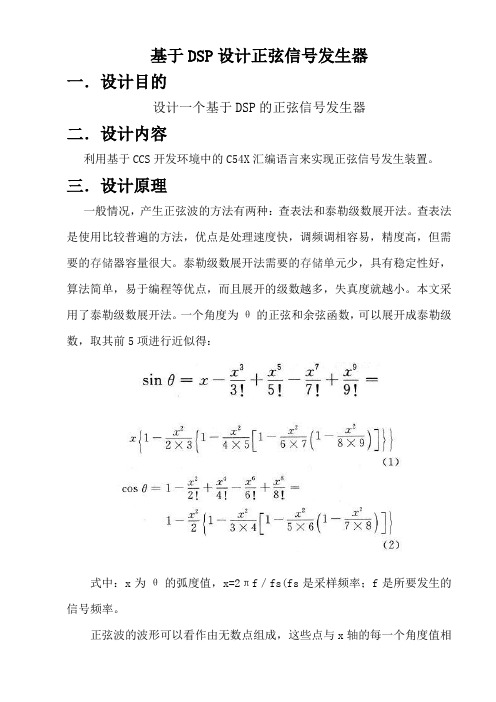

三.设计原理一般情况,产生正弦波的方法有两种:查表法和泰勒级数展开法。

查表法是使用比较普遍的方法,优点是处理速度快,调频调相容易,精度高,但需要的存储器容量很大。

泰勒级数展开法需要的存储单元少,具有稳定性好,算法简单,易于编程等优点,而且展开的级数越多,失真度就越小。

本文采用了泰勒级数展开法。

一个角度为θ的正弦和余弦函数,可以展开成泰勒级数,取其前5项进行近似得:式中:x为θ的弧度值,x=2πf/fs(fs是采样频率;f是所要发生的信号频率。

正弦波的波形可以看作由无数点组成,这些点与x轴的每一个角度值相对应,可以利用DSP处理器处理大量重复计算的优势来计算x轴每一点对应的y的值(在x轴取N个点进行逼近)。

整个系统软件由主程序和基于泰勒展开法的SIN子程序组成,相应的软件流程图如图。

三.总体方案设计本设计采用TMS320C54X系列的DSP作为正弦信号发生器的核心控制芯片。

通过计算一个角度的正弦值和余弦值程序可实现正弦波,其步骤如下:1.利用sinx和cosx子程序,计算0°~45°(间隔为0.5°)的正弦和余弦值2.利用sin(2x)=2sin(x)cos(x)公式,计算0°~90°的正弦值(间隔为1°)3.通过复制,获得0°~359°的正弦值4.将0°~359°的正弦值重复从PA口输出,便可得到正弦波四.软件操作DSP 集成开发环境 CCS是 Code Composer Studio 的缩写,即代码设计工作室。

它是 TI 公司推出的集成可视化 DSP 软件开发工具。

DSP CCS 内部集成了以下软件工具:◆ DSP 代码产生工具(包括 DSP 的 C 编译器、汇编优化器、汇编器和链接器)◆ CCS 集成开发环境(包括编辑、建立和调试 DSP 目标程序)◆ 实时基础软件 DSP/BIOS (必须具有硬件开发板)◆ RTDX、主机接口和 API(必须具有硬件开发板)在 CCS 下,用户可以对软件进行编辑、编译、调试、代码性能测试(profile)和项目管理等工作。

基于fpga的dds正弦信号发生器的设计和实现

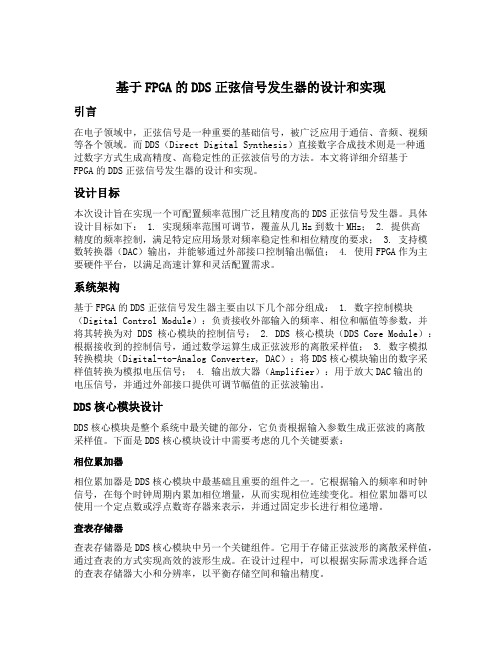

基于FPGA的DDS正弦信号发生器的设计和实现引言在电子领域中,正弦信号是一种重要的基础信号,被广泛应用于通信、音频、视频等各个领域。

而DDS(Direct Digital Synthesis)直接数字合成技术则是一种通过数字方式生成高精度、高稳定性的正弦波信号的方法。

本文将详细介绍基于FPGA的DDS正弦信号发生器的设计和实现。

设计目标本次设计旨在实现一个可配置频率范围广泛且精度高的DDS正弦信号发生器。

具体设计目标如下: 1. 实现频率范围可调节,覆盖从几Hz到数十MHz; 2. 提供高精度的频率控制,满足特定应用场景对频率稳定性和相位精度的要求; 3. 支持模数转换器(DAC)输出,并能够通过外部接口控制输出幅值; 4. 使用FPGA作为主要硬件平台,以满足高速计算和灵活配置需求。

系统架构基于FPGA的DDS正弦信号发生器主要由以下几个部分组成: 1. 数字控制模块(Digital Control Module):负责接收外部输入的频率、相位和幅值等参数,并将其转换为对DDS核心模块的控制信号; 2. DDS核心模块(DDS Core Module):根据接收到的控制信号,通过数学运算生成正弦波形的离散采样值; 3. 数字模拟转换模块(Digital-to-Analog Converter, DAC):将DDS核心模块输出的数字采样值转换为模拟电压信号; 4. 输出放大器(Amplifier):用于放大DAC输出的电压信号,并通过外部接口提供可调节幅值的正弦波输出。

DDS核心模块设计DDS核心模块是整个系统中最关键的部分,它负责根据输入参数生成正弦波的离散采样值。

下面是DDS核心模块设计中需要考虑的几个关键要素:相位累加器相位累加器是DDS核心模块中最基础且重要的组件之一。

它根据输入的频率和时钟信号,在每个时钟周期内累加相位增量,从而实现相位连续变化。

相位累加器可以使用一个定点数或浮点数寄存器来表示,并通过固定步长进行相位递增。

EDA正弦波信号发生器的设计

利用LPM 设计正弦信号发生器一、设计目的:进一步熟悉maxplu sII 及其LPM 设计的运用。

二、设计要求:1、利用原理图输入方式。

2、信号数据点值自行想法实现。

3、得出正确时序仿真文件。

三、设计原理:图1 正弦信号发生器结构框图图1所示的正弦波信号发生器的结构由三部分组成计数器或地址发生器(这里选择8位),正弦信号数据ROM (8位地址线,8位数据线),含有256个8位数据(一个周期)。

四、VHDL 顶层设计。

设计步骤:1、建立.mif 格式文件建立C 语言文件sin.cpp ,运行产生sin.exe 文件。

sin.cpp 程序代码:#include <iostream>#include <cmath>#include <iomanip>using namespace std;int main(){int i;float s;VHDL 顶层设计sin.vhd8位计数器 (地址发生器) 正弦波数据 存储ROM 产生波形数据cout<<"WIDTH=8;\nDEPTH=256;\n\nADDRESS_RADIX=HEX;\nDA TA_R ADIX=HEX;\n\nCONTENT\nBEGIN\n";for(i=0;i<256;i++){s=sin(atan(1)*8*i/256);cout<<" "<<i<<" : "<<setbase(16)<<(int)((s+1)*255/2)<<";"<<endl;}cout<<"END"<<endl;return 0;}把上述程序编译后,在DOS命令行下执行命令:sin.exe > sin.mif;将生成的sin.mif 文件。

EDA实验-正弦波信号发生器设计

实验八正弦信号发生器的设计一、实验目的1、学习用VHDL设计波形发生器和扫频信号发生器。

2、掌握FPGA对D/A的接口和控制技术,学会LPM_ROM在波形发生器设计中的实用方法。

二、实验仪器PC机、EDA实验箱一台Quartus II 6.0软件三、实验原理如实验图所示,完整的波形发生器由4部分组成:• FPGA中的波形发生器控制电路,它通过外来控制信号和高速时钟信号,向波形数据ROM 发出地址信号,输出波形的频率由发出的地址信号的速度决定;当以固定频率扫描输出地址时,模拟输出波形是固定频率,而当以周期性时变方式扫描输出地址时,则模拟输出波形为扫频信号。

•波形数据ROM中存有发生器的波形数据,如正弦波或三角波数据。

当接受来自FPGA的地址信号后,将从数据线输出相应的波形数据,地址变化得越快,则输出数据的速度越快,从而使D/A输出的模拟信号的变化速度越快。

波形数据ROM可以由多种方式实现,如在FPGA外面外接普通ROM;由逻辑方式在FPGA中实现(如例6);或由FPGA中的EAB模块担当,如利用LPM_ROM实现。

相比之下,第1种方式的容量最大,但速度最慢;,第2种方式容量最小,但速度最最快;第3种方式则兼顾了两方面的因素;• D/A转换器负责将ROM输出的数据转换成模拟信号,经滤波电路后输出。

输出波形的频率上限与D/A器件的转换速度有重要关系,本例采用DAC0832器件。

DAC0832是8位D/A转换器,转换周期为1µs,其引脚信号以及与FPGA目标器件典型的接口方式如附图2—7所示。

其参考电压与+5V工作电压相接(实用电路应接精密基准电压).DAC0832的引脚功能简述如下:•ILE(PIN 19):数据锁存允许信号,高电平有效,系统板上已直接连在+5V上。

•WR1、WR2(PIN 2、18):写信号1、2,低电平有效。

•XFER(PIN 17):数据传送控制信号,低电平有效。

•VREF(PIN 8):基准电压,可正可负,-10V~+10V.•RFB(PIN 9):反馈电阻端。

正弦信号发生器的设计

实验四正弦信号发生器的设计1. 实验的目的和要求熟悉QuartusII 及其LPM_ROM 与FPGA 硬件资源的使用方法。

2.实践内容或原理正弦信号发生器的结构由3部分组成,数据计数器或地址发生器、数据ROM 和D/A 。

性能良好的正弦信号发生器的设计,要求此3部分具有高速性能,且数据ROM 在高速条件下,占用最少的逻辑资源,设计流程最便捷,波形数据获最方便。

图1所示是此信号发生器结构图,顶层文件SINGT.VHD 在FPGA 中实现,包含2个部分:ROM 的地址信号发生器由5位计数器担任,和正弦数据ROM ,其原理图如图2所示。

据此,ROM 由LPM_ROM 模块构成能达到最优设计,LPM_ROM 底层是FPGA 中的EAB 或ESB 等。

地址发生器的时钟CLK 的输入频率f 0与每周期的波形数据点数(在此选择64点)以及D/A 输出的频率f 的关系是:640f f图1 正弦信号发生器结构图图2 正弦信号发生器原理图图3 正弦波的64个点的输入在Quartus II上完成正弦信号发生器设计,包括仿真和资源利用情况了解(假设利用Cyclone器件)。

最后在实验系统上实测,包括SignalTap II测试、FPGA中ROM的在系统数据读写测试和利用示波器测试。

最后完成EPCS1配置器件的编程。

3. 实验仪器(1)GW48系列SOPC/EDA实验开发系统(2)配套计算机及Quartus II 软件4.实践步骤或环节(1) 建立工程文件夹。

(2) 生成6位二进制计数器原理图。

(3)定制LPM_ROM元件。

(4)仿真。

(5)选择实验电路模式5,进行引脚下载配置。

(6)嵌入式逻辑分析仪的设置。

5. VHDL仿真实验(1)6位二进制计数器的仿真程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT6b ISPORT (CLK,RST,EN: IN STD_LOGIC;CQ: OUT STD_LOGIC_VECTOR (5 DOWNTO 0);COUT:OUT STD_LOGIC);END CNT6b;ARCHITECTURE behav OF CNT6b ISBEGINPROCESS(CLK,RST,EN)VARIABLE CQI:STD_LOGIC_VECTOR(5 DOWNTO 0); BEGINIF RST='1'THEN CQI:=(OTHERS=>'0');ELSIF CLK'EVENT AND CLK='1' THENIF EN='1' THENCQI:=CQI+1;END IF;END IF;IF CQI=63 THEN COUT<='1';ELSE COUT<='0';END IF;CQ<=CQI;END PROCESS;END behav;(2)RTL电路(3)时序仿真波形:(4)硬件验证选择试验箱的模式为模式5,时钟CLK选择为CLOCK0(PIN_28脚),频率f=65536Hz,EN对应的引脚编号PIN-233,RST对应的引脚编号PIN-234,COUT对应的引脚编号PIN-1,Q[7..0]对应的引脚编号PIN-20,19,18,17,16,15,14,13.(5)逻辑分析仪的测试波形6.实践教学报告要求(1)详细分析各模块的逻辑功能,及其他们工作原理,详细记录并分析实验内容和实验内容的过程和结果,完成实验报告。

正弦波信号发生器设计(课设)

课程设计I(论文)说明书(正弦波信号发生器设计)2010年1月19日摘要正弦波是通过信号发生器,产生正弦信号得到的波形,方波是通过对原信号进行整形得到的波形。

本文主要介绍了基于op07和555芯片的正弦波-方波函数发生器。

以op07和555定时器构成正弦波和方波的发生系统。

Op07放大器可以用于设计正弦信号,而正弦波可以通过555定时器构成的斯密特触发器整形后产生方波信号。

正弦波方波可以通过示波器检验所产生的信号。

测量其波形的幅度和频率观察是否达到要求,观察波形是否失真。

关键词:正弦波方波 op07 555定时器目录引言 (2)1 发生器系统设计 (2)1.1系统设计目标 (2)1.2 总体设计 (2)1.3具体参数设计 (4)2 发生器系统的仿真论证 (4)3 系统硬件的制作 (4)4 系统调试 (5)5 结论 (5)参考文献 (6)附录 (7)1引言正弦波和方波是在教学中经常遇到的两种波形。

本文简单介绍正弦波和方波产生的一种方式。

在这种方式中具体包含信号发生器的设计、系统的论证、硬件的制作,发生器系统的调制。

1、发生器系统的设计1.1发生器系统的设计目标设计正弦波和方波发生器,性能指标要求如下:1)频率范围100Hz-1KHz ;2)输出电压p p V ->1V ;3)波形特性:非线性失真~γ<5%。

1.2总体设计(1)正弦波设计:正弦波振荡电路由基本放大电路、反馈网络、选频网络组成。

2图1.1正弦波振荡电路产生的条件是要满足振幅平衡和相位平衡,即AF=1;φa+φb=±2nπ;A=X。

/Xid; F=Xf/X。

;正弦波振荡电路必须有基本放大电路,本设计以op07芯片作为其基本放大电路。

基本放大电路的输出和基本放大电路的负极连接电阻作为反馈网络。

反馈网络中两个反向二极管起到稳压的作用。

振荡电路的振荡频率f0是由相位平衡条件决定的。

一个振荡电路只在一个频率下满足相位平衡条件,这要求AF环路中包含一个具有选频特性的选频网络。

实验九定制LPM_ROM设计简单的正弦信号发生器

定制LPM_ROM设计简单的正弦信号发生器

实验名称:利用定制好的LPM_ROM设计简单的正弦信号发生器。

实验过程:

1:LPM_ROM的定制

图1 调用LPM_ROM

图2 LPM_ROM的参数设置

图3 加入初始化文件配置

2:LPM_ROM的仿真测试

图4 LPM_ROM仿真测试

3:波形分析

由图4可以看出,随着CLK的上升沿的出现,对应地址A的数据输出与初始化文件的数据完全吻合,实验得证。

再利用次模块完成一个简单的正弦信号发生器设计,该模块可以用来作为地址信号发生器(7位输出)和数据存储器(7位地址线,8位数据线),含有128个8位波形数据(一个正弦波形周期)。

4:正弦信号发生器的VHDL顶层设计

包括了对定制LPM_ROM时文件模块ROM78的例化调用。

图5 正弦信号发生器的VHDL描述

图6正弦信号发生器的仿真波形输出

5:波形分析

随着每个时钟上升沿的到来,输出端口将正弦波数据依次输出。

输出的数据与初始化配置文件相符。

6:观察RTL图

图7 正弦信号发生器的RTL电路图

分析:其中左边三个元件:加法器,寄存器构成7位计数器:其输出接右边ROM的地址输入端。

输出可接FPGA外的DAC,完成正弦波形输出。

实验结论:作为数据和程序的存储单位,ROM还有很多其他用处,如数字信号发生器的波形数据存储器,正弦信号发生器等。

正弦信号发生器设计

正弦信号发生器作者:程锟、晏婷婷、覃雄伟摘 要:本设计以凌阳SPCE061A 单片机为核心,基于直接数字频率合成(DDS )技术制作了一个频率值能任意调节的多功能信号源。

该信号源在1KHZ~10MHZ 范围能输出稳定可调的正弦波,并具有AM 、ASK 和PSK 等调制功能。

信号输出部分采用电流放大型宽带运放做电流放大,再用宽带电压运放做电压放大,很好地解决了带宽和带负载能力的要求。

系统采用液晶显示模组CPCL501显示和键盘控制功能,在Ω50负载电阻下输出的电压峰-峰值p p V -≥1V 可调。

一、方案论证与选择1.题目分析:本设计要求可以输出较宽频带且频率稳定度足够高的正弦信号,并且具有一定的负载能力,同时可输出指标满足要求的AM 、ASK 、PSK 信号。

综合题目指标要求及相关分析,得到该设计的功能框架图如图一所示。

本设计可分为以下几个部分:频率合成模块、AGC (自动增益控制)模块、幅度控制模块、功率放大模块、调制模块及人机交流模块。

图一 功能模块框图2.方案比较(1)正弦信号发生模块方案一:采用反馈型LC 振荡原理。

选择合适的电容、电感就能产生相应的正弦信号。

其中电容采用变容二极管,通过控制二极管的电压来改变电容, 最终控制输出信号频率。

此方案器件比较简单,但是难以达到高精度的程控调节,而且稳定度不高。

方案二:采用FPGA 器件。

将某一标准正弦信号经过高速采样后送到外部存储器中储存好,然后用一个计数器产生地址读出存储器中的数据后送到D/A 转换器件中输出,可以通过改变计数器的参数,改变地址信号,实现,也可以通过处理数据改变信号的幅度。

但是此方案的输出波形受时钟影响较大,且不易于控制步进和进行功能扩展。

方案三:采用直接频率合成集成芯片AD9851。

AD9851是AD 公司生产的DDS 芯片,带并行和串行加载方式,AD9851 内含可编程DDS 系统和高速比较器,能实现全数字编程控制的频率合成。

DDS正弦信号发生器的设计

高级数字系统设计实验——DDS正弦信号发生器设计姓名学号专业:通信与信息系统指导老师实验三 DDS 正弦信号发生器一、实验要求:利用LPM_ROM 设计一个DDS 正弦信号发生器,要求ROM 表长度为8位,频率控制字为8位,输出频率分辨率优于1Hz 。

二、设计方案 1、 方案流程图:由频率控制字提供,累加器在系统时钟控制下,来一个上升沿就累加一次频率控制字的值,累加器的位数高于8位,所以用其高8位作为正弦查表的地址,根据地址就能寻址到表内的值,该值通过DAC 转换再通过示波器就能显示波形。

累加器溢出一次就相当于正弦表寻址一圈,正弦信号经历一个周期。

2、参数设定系统时钟fclk :设定为50KHz ,频率控制字M :8位,取值范围:1~28-1, 分辨率:f=nfclk2 n 为累加器的位数,当系统时钟的频率越低,相位累加器的位数越高,所得到的频率分辨率就越高,累加器:为了使输出频率的分辨率能达到1Hz ,选定为16位, 输出频率:fout=n M fclk 2*=16250000M *=6553650000M*, 当M=1时,输出频率最小,fout=0.7629Hz ,当M=255时,输出频率最大,fout=0.7629*255=194.5496Hz 。

3、模块建立 1)累加器LIBRARY IEEE;USE IEEE.std_logic_1164.all;USE IEEE.std_logic_ARITH.ALL;USE IEEE.std_logic_unsigned.ALL;ENTITY add ISPORT(fclk : IN STD_LOGIC; --接入系统时钟rst : IN STD_LOGIC; --复位端fcontrol:IN STD_LOGIC_VECTOR(7 DOWNTO 0);--频率控制字8位asum:OUT STD_LOGIC_VECTOR(15 DOWNTO 0));--输出累加和END ENTITY;ARCHITECTURE behav OF add ISSIGNAL a:STD_LOGIC_VECTOR(15 DOWNTO 0);--累加器的暂存值SIGNAL fc:STD_LOGIC_VECTOR(7 DOWNTO 0);--频率控制字的寄存器BEGINfc<=fcontrol;PROCESS(fc,a,fclk,rst)BEGINIF(rst = '1' ) THENa <=(others=>'0');--复位端高电平有效ELSIF( fclk'event AND fclk = '1') THENa<=a+fc; --系统时钟来一个上升沿就累加一次频率控制字的值ELSENULL;END IF;asum<=a;--寄存器的值赋值给输出端END PROCESS;END behav;2)ROM表ROM表可以通过LPM宏功能模块来实现,通过MegaWizard管理器可以构建我们所需的存储单元,因为频率控制字为8位,DAC 采用实验箱上的THS5651为10位并行高速DAC,所以需要256个存储单元,每个单元为10bits。

信号发生器设计(正弦,方波,三角,多用信号发生器)

模拟电路课程设计报告设计课题:信号发生器设计班级:10通信工程三班学生姓名:陶冬波学号:2010550921指导教师:设计时间:目录一、信号发生器摘要--------------------3二、设计目的---------------------3三、设计内容和要求四、设计方案------------------------------------------34.1 RC桥式正弦波产生电路--------------------------------------3 4.2方波产生电路----------------------------------------------------6 4.3三角波产生电路-------------------------------------------------84.4多用信号发生器-------------------------------------------------9五、组装调试及元件清单---------------------------105.1 测试仪器---------------------------------------------------------10 5.2信号发生器元件清单-----------------------------------------------115.3调试中出现的故障、原因及排除方法----------------------11六、总结设计电路,改进措施----------------------116.1 正弦波产生电路改进措施--------------------------------------116.2多用信号发生器改进措施---------------------------------------11七、收获和体会-----------------------------------------12八、参考文献--------------------------------------------12信号发生器设计一、信号发生器设计摘要:本设计介绍了波形发生器的制作和设计过程,并根据输出波形特性研究该电路的可行性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

正弦信号发生器设计方案

一、方案比较论证

所有方案可按模拟式和数字式分为两大类

模拟式:

①利用电阻、电容、运放等传统器件搭建LC或RC正弦信号发生器。

通过改变电路中的

元件的参数值来调节输出频率。

这种方式成本低廉,但由于采用大量分立器件,受其工作原理的限制频率稳定度较低(只有10-3量级)。

另外实现扩展功能中的各种调制等也比较麻烦,电路复杂,调试困难,精度差。

②采用专用信号发生芯片MAX038来实现正弦信号波形的输出。

是美信公司的低失真单片

信号发生集成电路,内部电路完善,使用该器件能够产生精确的高频三角、锯齿、正弦及方波。

使用该芯片设计简单,但扩展功能电路部分实现起来和采用分立器件同样复杂,而且频率精度和稳度均难以达到要求。

③采用基于锁相环(PLL)技术或者非线性器件频率变换技术的频率合成器。

由晶体振荡

器和锁相环组成的系统中,前者保证工作频率稳定度,后者完成输出频率的调整,但是这时输出频率只能是晶体谐振频率的整数倍。

故虽然频率稳定能达到要求却很难做到频率输出范围1KHZ—10MHZ和100HZ步进的要求。

数字式:

①采用AD公司专用的DDS芯片AD9851合成FM和AM的载波,采用传统的模拟调制

方式来实现AM调制和FM调制。

但该方案需要额外的模拟调制FM和AM的调制电路,且制作和调制电路都比较麻烦,还难免引入一定的干扰,而且此方案中的PSK调制也不容易实现。

②采用AD公司的AD9856作为调制芯片,是内含DDS的正交调制芯片,可以实现多进

制的数字幅度调制,多进制的数字相位调制和多进制的数字幅度相位联合调制。

故AM 调制,PSK调、ASK调制都可以通过它实现但是AD9856不便于调频且控制复杂。

③利用微处理器和DAC实现DDS信号产生器。

微处理器能够实现DDS的电路结构,即

实现相位累加器、波形的数据表、同时实现数字/模拟转换器的控制时序。

利用微处理器完成加法运算需要读取的数据进行运算,再把运算结果送到目标单元。

由于微处理器工作的顺序性,这时的相位累加频率将比微处理器的时钟频率低得多。

同时微处理器还要完成人机交互的相关任务,故这种方案输出频率受到很大限制。

④利用微处理器和可编程逻辑器件实现DDS信号产生器。

微处理器程序执行的顺序性限

制了它的工作速度,可编程逻辑器件的并行运行能力使它适用于高速工作的场合。

同时FM、AM、PSK、ASK调制均由FPGA在数字域内完成,大大简化了电路,同时具有良好的精度和可控性。

微处理器完成键盘输入,液晶显示等人机交换任务。

综上所述:数字类的第四方案为最优选择。

二、总体设计

(1)总体框图如下所示

(2)考虑到单片机只是完成接收用户输入信息及显示的任务,故采用廉价的51单片机AT89S51,编程容易,使用方便。

键盘使用4x4的矩阵键盘方便用户直接键入所需要的频率和参数。

显示电路采用带字库的通用LCD12864,具有使用简单,单屏显示信息多的特点,能够提供良好的人机界面。

(3)DDS及调制电路模块

其由FPGA和DAC构成。

本设计采用Altera公司的Cyclone系列FPGA—EPIC3T144C8,此芯片有LE约3000个,片内RAM有52Kbit。

FPGA负责在数字域实现正弦波、FM、AM的合成,产生ASK和PSK调制信号并完成ASK、PSK、AM和FM的调制,然后输出波形。

(4)滤波电路及放大电路

滤波电路是采用美信的高速运放MAX4108设计的一个有源二阶低通滤波器,用以去除DDS合成信号固有的高次谐波,同时有两倍放大的功能。

(5)电源设计

高速DAC对模拟数字地之间的串扰敏感,模拟数字地之间的串扰对DAC输出信号的波形影响很大。

故本系统采用一个线性电源对模拟电路供电,采用一个开关电源对数字电路供电,模拟地和数字地之间通过一个磁珠相连。

这种设计实现了模拟数字电路尽可能大的隔离。

三、理论分析和参数设计

(1)载频参数设计

根据要求信号波形无明显失真,故一个信号周期内至少需插入16个点,而合成频率最高达10MHz,那么需要的FPGA和DAC接口数据传输速率为:

10M×16=160Mword/s

如此之高的频率传输可能很不稳定,为了解决波形失真和传输速率的矛盾,选用MAX5858A它是双路十位300M的DAC,内部含有4x/2x/1x插值滤波电路。

若采用4x插值则数据传输速率为

300Mwordps/4=75Mwordps

DDS输出的正弦波信号每秒钟有75M个插值点,并在DAC内部完成4阶插值和数字低通滤波,最后转化为实际电压输出。

这样既抑制了高频段输出正弦信号可能的失真,又降低了数据接口的传输速度,提高了系统的可靠性。

系统频率调整的步进是100Hz,DDS逻辑电路的工作时钟是75M,所以

75M/100=750000<219

所以,DDS的频率字只要多于20bit,频率调整步进就能小于100Hz。

(2)AM/FM调制参数设计

AM要求:产生1KHz的正弦调制信号;调制度在10%-100%之间程控调节,步进为10%。

本系统采用一个10bit的控制寄存器来保存调制度,其离散间隔为1/1024,高于步进10%的要求,调制度可以由用户自行设置,也可以用按键以1%或10%步进调整。

FM要求:产生1KHz的正弦调制信号;调制产生最大频偏为5KHz/10KHz两级程控调节。

AM和FM的调制信号均由另一个独立的DDS产生,在FPGA内部对信号完成数字调制。

(3)ASK/PSK调制参数设计

题目要求:产生码速率为10Kb/s的二进制基带序列信号,载波频率为100KHz。

ASK/PSK调制和AM/FM调制共用一套本振(即合成正弦信号的DDS模块)所以通过设定频率字可设置载波频率为需要100KHz.而码率为10Kb/s二进制基带序列信号则可以通过设置好的移位寄存器循环移位获得。

(4)滤波电路参数设计

由于最终方案采用DAC输出,而DAC的转换频率为75MHz,故需要一个截止频率在10MHz和75MHz之间的低通滤波器。

然而DAC的转换并不是理想的,输出信号的谐波干扰主要集中在二次谐波,所以选取截止频率为18MHz的有源二阶巴特沃斯低通滤波器,来保证达到题目的要求。

四、软件设计

(1)单片机接收用户由键盘输入的数据和控制指令,控制LCD的显示,向FPGA发送控制字。

整个软件流程如下所示:

(2)为了提供友好的提示界面,本系统设计了多级菜单界面,用户可通过选择菜单项设置输出信号的参数(频率,调制度,偏频等)。

用户确认输入后,单片机将设置的参数送至FPGA,使FPGA输出相应的信号。

(3)FPGA的数字逻辑电路负责在数字域实现FM和AM调制信号(经过离散化的)频率合成的主域ASK和PSK的调制信号,正弦波(载波)的频率组成,完成ASK、PSK、FM、AM 在数字域的调制,然后控制DAC形成正确的波形信号。

PSK调制的实现:本系统中PSK调制是通过调制信号延时作异或运算,然后经过DPSK 调制来间接实现,而DPSK的调制是通过降DDS相位累加器的相位步进瞬时设置为2π来实现反相.

FM调制通过给正弦波(载频)的频率字叠加一个偏移频率字来实现频率的转移;AM调制直接在FPGA内用数字乘法器实现;ASK调制直接用开关选通载频信号或截断载频信号实现.

整个逻辑设计框图如下图(2)所示:

五、硬件电路设计

根据总体设计方案,整个系统的硬件模块有:单片机控制模块、信号产生模块(FPGA)、DAC模块、滤波和放大。

(1)控制模块主要由单片机AT89851和LCD12864和4×4矩阵键盘组成,连接图如下图所示:

(2)整个系统的信号生成采用数字方式FPGA中实现,因此信号产生模块是整个系统的核心,可采用成品的EPIC3T144开发板。

(3)DAC采用MAX5858A,电路图如下图所示,其中OPA681是一片高带宽增益运放,MAX5858A的差分电流输出的电流范围可由R2设定,输出最大值为32×V refo/Rset。

当它取Ω有约10mA的最大电流输出,结合后取Rf为50Ω的电流-电压变换,输出范围为-500~500mV。

DAC电路

电源地的处理

(4)滤波部分采用一个二阶巴沃斯特低通滤波器电路,采用MAX4108运放完成。

同时作两倍电压放大。

滤波器实际如下图(4)所示:

滤波器电路

参考资料:《数字电路EDA技术入门与实战》,罗朝霞赫建国,人民邮电出版社,2009 《全国大学生电子设计竞赛试题精解选》,陈永真宁武等,电子工业出版社,2007。