161,160,74ls20等常用芯片的引脚图

74系列芯片引脚图及逻辑功能表

74LS20——4输入端双与非门管脚图及逻辑功能表

74LS21——4输入端双与门管脚图及逻辑功能表

74LS27——3输入端三或非门管脚图及逻辑功能表

74LS42——BCD/十进制译码器管脚图及逻辑功能表

74LS138——3-8线译码器管脚图及逻辑功能表

74LS54——4-2-3与或非门

74LS08——2输入4与门

74LS139——双2-4线译码器管脚图及逻辑功能表

74LS148——8-3线优先编码器管脚图及逻辑功能表

74LS151——八选一数据选择器管脚图及逻辑功能表

74LS153——双4选1数据选择器管脚图及逻辑功能表

74LS47——4线7段显示译码器,低电平有效,驱动共阳数码管

74LS55——双4输入与或非门

芯片管脚一览图

74ls00 2输入四与非门

74ls02 2输入四或非门

74ls04 六倒相器

74ls08 2输入四与门

74ls20 4输入双与非门

74ls32 2输入四或门

74ls74 正沿触发双d型触发器(带预置端和清除端) 74ls90 十进制计数器

74ls112 负沿触发双j-k触发器(带预置端和清除端) 74ls138 3-8线译码器/多路转换器

74ls153 双4选1数据选择器/多路选择器

74ls161 可预置四位二进制计数器(并清除异步)

74ls32或门74ls00与非门

74ls08 与门74ls138 3-8译码器

74ls139 四选一数据选择器74ls20 与非门

74ls112 下降沿触发j-k触发器可预置四位二进制计数器74ls161

六非门74LS04 十进制计数器74LS90

双4选1数据选择器74LS153 异或门74LS86

正沿触发双d型触发器74LS74 2输入四或非门74LS02。

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料

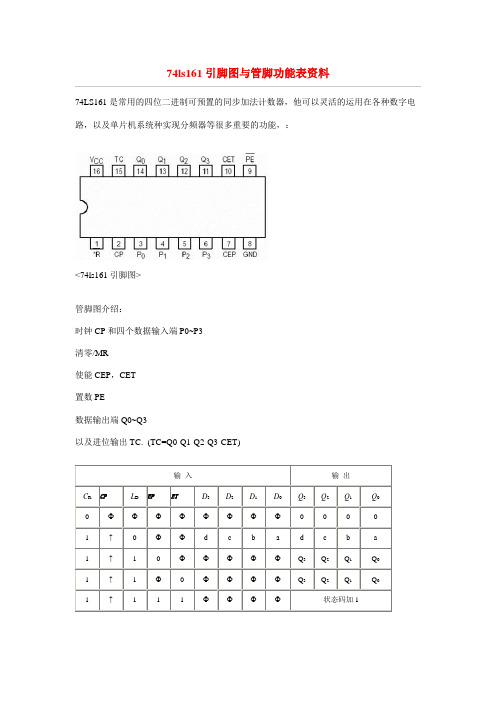

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

<74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)

输入输出

C R CP L

D EP ET D3D2D1D0Q3 Q2Q1Q0

0 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 0

1 ↑ 0 Ф Ф d c b a d c b a

1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1

<74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:<74ls161引脚图>管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)输入输出C R CP LD EP ET D3D2D1D0Q3 Q2Q1Q00 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 01 ↑ 0 Ф Ф d c b a d c b a1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1<74LS161功能表〉从74LS161功能表功能表中可以知道,当清零端CR=“0",计数器输出Q3、Q2、Q1、Q0立即为全“0",这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1"、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

<74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)

<74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:<74ls161引脚图>管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)<74LS161功能表>从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

二进制计数器电路简单,运算也方便,但人们最习惯的是十进制,所以在应用中常使用十进制计数器。

使用较多的十进制计数器是按照8421BCD码进行计数的电路,计数器由“0000”状态开始计数,每10个脉冲一个循环,也就是第10个脉冲到来时,由“1001”变为“0000”,就实现了“逢十进一” ,同时产生一个进位信号。

74LS160是集成同步十进制计数器,它是按8421BCD码进行加法计数的,74LS160的引脚图、逻辑功能与74LS161相同,只是计数状态是按照十进制加法规律来计数的,因此不再重述。

74ls161引脚图与管脚功能表资料

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:<74ls161引脚图>管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)输入输出C R CP LDEP ET D3D2D1DQ3Q2Q1Q0 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 01 ↑ 0 Ф Ф d c b a d c b a1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1<74LS161功能表>从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

161 的清除端是异步的。

当清除端C LEAR 为低电平时,不管时钟端C LOCK 状态如何,即可完成清除功能。

161 的预置是同步的。

当置入控制器L OAD 为低电平时,在C LOCK 上升沿作用下,输出端QA-QD 与数据输入端A-D 相一致。

对于54/74161,当C LOCK 由低至高跳变或跳变前,如果计数控制端E NP、ENT 为高电平,则L OAD 应避免由低至高电平的跳变,而54/74LS161 无此种限制。

74系列芯片引脚图及逻辑功能表

74LS11——3输入端3与门管脚图及逻辑功能表

74LS20——4输入端双与非门管脚图及逻辑功能表

74LS21——4输入端双与门管脚图及逻辑功能表

74LS27——3输入端三或非门管脚图及逻辑功能表

74LS42——BCD/十进制译码器管脚图及逻辑功能表

74LS138——3-8线译码器管脚图及逻辑功能表

74LS139——双2-4线译码器管脚图及逻辑功能表

74LS148——8-3线优先编码器管脚图及逻辑功能表

74LS151——八选一数据选择器管脚图及逻辑功能表

74LS153——双4选1数据选择器管脚图及逻辑功能表

74LS47——4线7段显示译码器,低电平有效,驱动共阳数码管

74LS55——双4输入与或非门74LS54——4-2-3与或非门

74LS08——2输入4与门

如有侵权请联系告知删除,感谢你们的配合!。