74LS90引脚图及引脚功能

74LS90引脚图及引脚功能

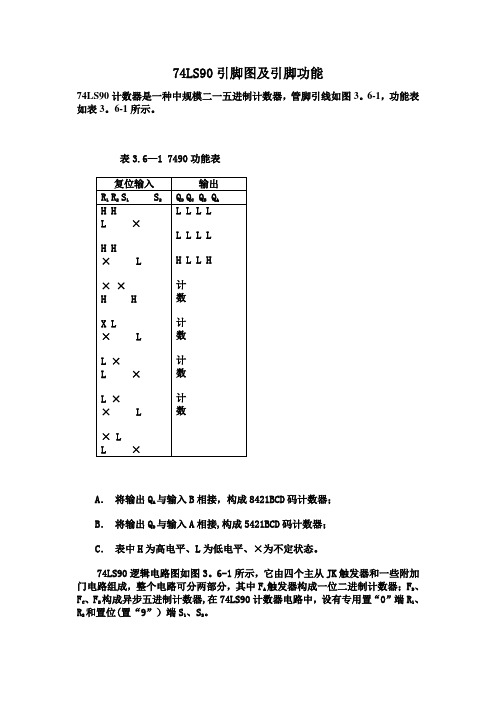

74LS90引脚图及引脚功能74LS90计数器是一种中规模二一五进制计数器,管脚引线如图3。

6-1,功能表如表3。

6-1所示。

表3.6—1 7490功能表A . 将输出Q A 与输入B 相接,构成8421BCD 码计数器; B . 将输出Q D 与输入A 相接,构成5421BCD 码计数器;C . 表中H 为高电平、L 为低电平、×为不定状态。

74LS90逻辑电路图如图3。

6-1所示,它由四个主从JK 触发器和一些附加门电路组成,整个电路可分两部分,其中F A 触发器构成一位二进制计数器;F D 、F C 、F B 构成异步五进制计数器,在74LS90计数器电路中,设有专用置“0”端R 1、R 2和置位(置“9”)端S 1、S 2。

74LS90具有如下的五种基本工作方式:(1)五分频:即由FD 、FC、和FB组成的异步五进制计数器工作方式。

(2)十分频(8421码):将QA 与CK2联接,可构成8421码十分频电路。

(3)六分频:在十分频(8421码)的基础上,将QB 端接R1,QC端接R2。

其计数顺序为000~101,当第六个脉冲作用后,出现状态QC QBQA=110,利用QBQC=11反馈到R1和R2的方式使电路置“0”。

(4)九分频:QA →R1、QD→R2,构成原理同六分频。

(5)十分频(5421码):将五进制计数器的输出端QD接二进制计数器的脉冲输入端CK1,即可构成5421码十分频工作方式。

此外,据功能表可知,构成上述五种工作方式时,S1、S2端最少应有一端接地;构成五分频和十分频时,R1、R2端亦必须有一端接地。

二-五-十进制异步加法计数器74LS90

2. 二-五-十进制异步加法计数器74LS90 ★ 从计数器命名可知:74LS90可以实现二进制、五进制加法计数功能,如果按照“低位片循环一周,向高位片进一位”的级联扩展方式,将二进制加法计数单元和五进制加法计数单元联系起来,就可以实现十进制加法计数器,此时,整个计数器组成了异步时序逻辑电路的结构,因此,74LS90被称为二-五-十进制异步加法计数器。

与74LS197的使用类似,74LS90通过级联组成十进制异步加法计数器时,也存在两种方式,下文中将详细介绍。

74LS90的芯片封装图和功能示意图如图8.3.16所示。

图8.3.17 二-五-十进制异步加法计数器74LS90 (a )芯片封装图 (b )功能示意图★ 分析图8.3.17,将得到的74LS90的管脚信息总结如下:74LS90的逻辑功能端包括2个下降沿有效的输入时钟信号端 和 、4个高有效的输入控制端 ,以及4个输出状态端 。

表8.3.10为74LS90的功能表,完整地表达了74LS90的逻辑功能。

表8.3.10 二-五-十进制异步加法计数器74LS90的功能表★ 分析表8.3.10,将得到的74LS90的逻辑功能完整总结如下:◆ 异步置9、高有效,为置数控制端。

0123 Q Q Q Q 、、、10 CLK CLK B 0A 0B 99A R R S S 、、、B 9A 9 S S 、74LS90没有提供输入数据端,当时, ,即输出状态被直接置为9。

◆ 异步清零、高有效, 为清零控制端。

◆ 计数器在不置数、不清零的前提下,时钟脉冲的下降沿工作,完成计数功能,有以下四种情况。

▲ 时钟信号从输入,则完成二进制加法计数,对应输出状态为; ▲ 时钟信号从输入,完成五进制加法计数,对应输出状态排列为 ,工作循环为000到100的递增循环, 为最高位; ▲ 时钟信号从 输入,且将二进制计数器的输出状态 作为五进制计数器的时钟信号,接入,则组成了“二进制单元先运行,五进制单元后运行”的级联结构,由此实现十进制加法计数功能,其输出状态排列为; ▲ 时钟信号从 输入,且将五进制计数器的输出最高位状态作为二进制计数器的时钟信号,接入,则组成了“五进制单元先运行,二进制单元后运行”的级联结构,由此实现的十进制加法计数器的输出状态排列为。

74LS74内部结构-引脚图-管脚-逻辑图(双D触发器)、原理图和真值表以及波形图分析

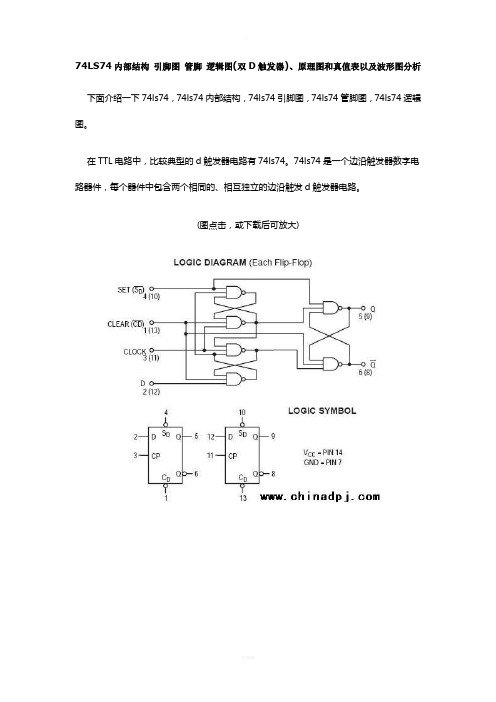

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)----------------------原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD =0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6 =Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q =D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q 3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

74LS90计数器

74LS90计数器是一种中规模二一五进制计数器,管脚引线如图3.6-1,功能表如

表3.6-1所示。

表3.6-1 7490功能表

A.将输出Q A与输入B相接,构成8421BCD码计数器;

B.将输出Q D与输入A相接,构成5421BCD码计数器;

C.表中H为高电平、L为低电平、×为不定状态。

74LS90逻辑电路图如图3.6-1所示,它由四个主从JK触发器和一些附加门电路组成,整个电路可分两部分,其中F A触发器构成一位二进制计数器;F D、F

C、F B构成异步五进制计数器,在74LS90计数器电路中,设有专用置“0”端R1、

R2和置位(置“9”)端S1、S2。

74LS90具有如下的五种基本工作方式:

(1)五分频:即由F D、F C、和F B组成的异步五进制计数器工作方式。

(2)十分频(8421码):将Q A与CK2联接,可构成8421码十分频电路。

(3)六分频:在十分频(8421码)的基础上,将Q B端接R1,Q C端接R2。

其计数顺序为000~101,当第六个脉冲作用后,出现状态Q C Q B Q A=110,利用Q

Q C=11反馈到R1和R2的方式使电路置“0”。

B

1)九分频:Q A→R1、Q D→R2,构成原理同六分频。

5)十分频(5421码):将五进制计数器的输出端Q D接二进制计数器的脉冲输入端CK1,即可构成5421码十分频工作方式。

此外,据功能表可知,构成上述五种工作方式时,S1、S2端最少应有一端接地;构成五分频和十分频时,R1、R2端亦必须有一端接地。

74LS90

74LS90功能:十进制计数器(÷2 和÷5)原理说明:本电路是由4 个主从触发器和用作除2 计数器及计数周期长度为除5 的3 位2 进制计数器所用的附加选通所组成。

有选通的零复位和置9 输入。

为了利用本计数器的最大计数长度(十进制),可将B 输入同QA 输出连接,输入计数脉冲可加到输入A 上,此时输出就如相应的功能表上所要求的那样。

LS90 可以获得对称的十分频计数,办法是将QD 输出接到A 输入端,并把输入计数脉冲加到B 输入端,在QA 输出端处产生对称的十分频方波。

真值表:Reset Inputs 复位输入 输出R0(1) R0(2) R9(1) R9(2) QD QC QB QA H H L X L L L L H H X L L L L L X X H H HLLHX L X L COUNT COUNT COUNT COUNTL X L X L X X L XLLXH=高电平 L=低电平 ×=不定 BCD 计数顺序(注1) Count 输出QD QC QB QA 0 L L L L 1 L L L H 2 L L H L 3 L L H H 4 L H L L 5 L H L H 6 L H H L 7 L H H H 8 H L L L 9HLL H5-2 进制计数顺序(注2) Count 输出QA QD QC QB 0 L L L L 1 L L L H 2 L L H L 3LLHH4 L H L L5 H L L L6 H L L H7 H L H L8 H L H H9 H H L L注1:对于BCD(十进)计数,输出QA 连到输入B 计数注2:对于5-2 进制计数,输出QD 连到输入A 计数图1 74LS90引脚图图2 74LS90逻辑图Symbol 符号Parameter 参数最小典型最大UNIT单位VCC Supply Voltage 电源电压 4.755 5.25V VIH High Level Input Voltage输入高电平电压2--V VIL LOW Level Input Voltage 输入低电平电压--0.8V IOH HIGH Level Output Current高电平输出电流---0.4mA IOL LOW Level Output Current低电平输出电流--8mAfCLK Clock Frequency (Note 5)时钟频率A to QA0-32MHz B to QB0-16fCLK Clock Frequency (Note 6)时钟频率A to QA0-20MHz B to QB0-10tW Pulse Width (Note 5)脉冲宽度A15--ns B30--Reset15--tW Pulse Width (Note 6)脉冲宽度A25--ns B50--Reset25--tREL Reset Release Time (Note 5)重置发布时间25--ns tREL Reset Release Time (Note 6)重置发布时间35--ns TA Free Air Operating Temperature工作温度0-70℃Note 5: CL = 15 pF, RL = 2 kW, TA = 25℃and VCC = 5VNote 6: CL = 50 pF, RL = 2 kW, TA = 25℃and VCC = 5Vover recommended operating free air temperature range (unless otherwise noted)Symbol 符号Parameter 参数Conditions 条件最小典型最大UNIT单位VI Input Clamp Voltage输入钳位电压VCC = 最小, II = -18mA---1.5VVOH HIGH Level OutputVoltage输出高电平电压VCC=最小,IOH=最大VIL=最大,VIH=最小 2.73.4-VVOL LOW LevelOutputVoltage输出低电平电压VCC = 最小, IOL = 最大VIL = 最大, VIH= 最小(Note 8)-0.350.5VIOL= 4mA, VCC =最小-0.250.4II Input Current @ MAXInput Voltage输入电流@最大输入电压VCC = 最大, VI =7V Reset--0.1mAVCC = 最大VI =5.5VA--0.2B--0.4IIH HIGH Level InputCurrent输入高电平电流VCC = 最大, VI =2.7VReset--20μAA--40B--80IIL LOW LevelInputCurrent输入低电平电流VCC = 最大, VI =0.4VReset---0.4mAA---2.4B---3.2IOS Short Circuit OutputCurrent短路输出电流VCC = 最大(Note 9)-20--100mAICC Supply Current电源电流VCC = 最大(Note 7)-915mA交流电气特性:Symbol 符号Parameter 参数To (Output)RL=2KUNIT单位CL=15pFCL=50pF最小最大最小最大fMax Maximum Clock Frequency最大时钟频率A to QA32-20-MHz B to QB16-10-tPLH Propagation Delay Time LOW-to-HIGHLevel Output低到高电平输出传递延迟时间A to QA-16-20nstPHL Propagation Delay Time HIGH-to-LOWLevel Output高到低电平输出传递延迟时间A to QA-18-24nstPLH Propagation Delay Time LOW-to-HIGHLevel Output低到高电平输出传递延迟时间A to QD-48-52nstPHL Propagation Delay Time HIGH-to-LOWLevel Output高到低电平输出传递延迟时间A to QD-50-60nstPLH Propagation Delay Time LOW-to-HIGHLevel Output低到高电平输出传递延迟时间B to QB-16-23nstPHL Propagation Delay Time HIGH-to-LOWLevel Output高到低电平输出传递延迟时间B to QB-21-30nstPLH Propagation Delay Time LOW-to-HIGHLevel Output低到高电平输出传递延迟时间B to QC-32-37nstPHL Propagation Delay Time HIGH-to-LOWLevel Output高到低电平输出传递延迟时间B to QC-35-44nstPLH Propagation Delay Time LOW-to-HIGHLevel Output低到高电平输出传递延迟时间B to QD-32-36nstPHL Propagation Delay Time HIGH-to-LOWLevel Output高到低电平输出传递延迟时间B to QD-35-44nstPLH Propagation Delay Time LOW-to-HIGHLevel Output低到高电平输出传递延迟时间SET-9 to QA,QD-30-35nstPHL Propagation Delay Time HIGH-to-LOWLevel Output高到低电平输出传递延迟时间SET-9 to QB,QC-40-48nstPHL Propagation Delay Time HIGH-to-LOWLevel Output高到低电平输出传递延迟时间SET-0 to AnyQ-40-52ns应用电路:图3 74LS90脉冲发生器电路图图4 简单的计数器电路(接受任何TTL兼容逻辑信号)。

74LS90的详细说明功能表

实验十七电子秒表一、实验目的1、学习数字电路中基本RS触发器、单稳态触发器、时钟发生器及计数、译码显示等单元电路的综合应用。

2、学习电子秒表的调试方法。

二、实验原理图17-1为电子秒表的电原理图。

按功能分成四个单元电路进行分析。

1、基本RS触发器图17-1中单元I为用集成与非门构成的基本RS触发器。

属低电平直接触发的触发器,有直接置位、复位的功能。

它的一路输出Q作为单稳态触发器的输入,另一路输出Q作为与非门5的输入控制信号。

按动按钮开关K2(接地),则门1输出Q=1;门2输出Q=0,K2复位后Q、Q状态保持不变。

再按动按钮开关K1,则Q由0变为1,门5开启, 为计数器启动作好准备。

Q 由1变0,送出负脉冲,启动单稳态触发器工作。

基本RS触发器在电子秒表中的职能是启动和停止秒表的工作。

2、单稳态触发器图17-1中单元Ⅱ为用集成与非门构成的微分型单稳态触发器,图17-2为各点波形图。

单稳态触发器的输入触发负脉冲信号vi 由基本RS触发器Q端提供,输出负脉冲vO通过非门加到计数器的清除端R。

静态时,门4应处于截止状态,故电阻R必须小于门的关门电阻ROff。

定时元件RC 取值不同,输出脉冲宽度也不同。

当触发脉冲宽度小于输出脉冲宽度时,可以省去输入微分电路的RP 和CP。

单稳态触发器在电子秒表中的职能是为计数器提供清零信号。

图17-1 电子秒表原理图3、时钟发生器图17-1中单元Ⅲ为用555定时器构成的多谐振荡器,是一种性能较好的时钟源。

,使在输出端3获得频率为50HZ的矩形波信号,当基本RS触发器调节电位器 RWQ=1时,门5开启,此时50HZ脉冲信号通过门5作为计数脉冲加于计数器①的计数输入端CP。

2图17-2单稳态触发器波形图图17-3 74LS90引脚排列4、计数及译码显示二—五—十进制加法计数器74LS90构成电子秒表的计数单元,如图17-1中单元Ⅳ所示。

其中计数器①接成五进制形式,对频率为50HZ的时钟脉冲进行五分频,在输出端QD取得周期为0.1S的矩形脉冲,作为计数器②的时钟输入。

74290芯片介绍

74290芯片介绍

常用异步集成计数器74LS290

74LS290芯片的符号图和管脚排列如下图所示。

其中,S9(1)、S9(2)称为置“9”端,R0(1)、R0(2)称为置“0”端;CP0、CP1端为计数时钟输入端,Q3Q2Q1Q0为输出端,NC表示空脚。

74LS290具有以下功能:

置“9”功能:当S9(1)=S9(2)=1时,不论其他输入端状态如何,计数器输出Q3 Q2 Q1 Q0=1001,而(1001)2=(9)10,故又称为异步置数功能。

置“0”功能:当S9(1)和S9(2)不全为1,并且R0(1)=R0(2)=1时,不论其他输入端状态如何,计数器输出Q3 Q2 Q1 Q0=0000,故又称为异步清零功能或复位功能。

计数功能:当S9(1)和S9(2)不全为1,并且R0(1)和R0(2)不全为1时,输入计数脉冲CP,计数器开始计数。

计数脉冲由CP0输入,从Q0输出时,则构成二进制计数器;计数脉冲由CP1输入,输出为Q2Q1Q0时,则构成五进制计数器;若将Q0和CP1相连,计数脉冲由CP0输入,输出为Q3Q2Q1Q0时,则构成十进制(8421码)计数器;若将Q3和CP0相连,计数脉冲由CP1输入,输出为Q3Q2Q1Q0时,则构成十进制(5421码)计数器。

因此,74LS290又称为“二—五—十进制型集成计数器”。

各种元器件引脚图

74LS86 异或门74LS00 与非门74LS02 或非门74LS11 三输入端与门74LS90功能:十进制计数器(÷2 和÷5)原理说明:本电路是由4 个主从触发器和用作除2 计数器及计数周期长度为除5 的3 位2 进制计数器所用的附加选通所组成。

有选通的零复位和置9 输入。

为了利用本计数器的最大计数长度(十进制),可将B 输入同QA 输出连接,输入计数脉冲可加到输入A 上,此时输出就如相应的功能表上所要求的那样。

LS90 可以获得对称的十分频计数,办法是将QD 输出接到A 输入端,并把输入计数脉冲加到B 输入端,在QA 输出端处产生对称的十分频方波。

真值表:H=高电平 L=低电平×=不定BCD 计数顺序(注1)5-2 进制计数顺序(注2)注1:对于BCD(十进)计数,输出QA 连到输入B 计数注2:对于5-2 进制计数,输出QD 连到输入A 计数74LS14 非门大部分情况下可以和74LS04非门通用74LS161 四位二进制同步加法计数器74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,这里我给大家介绍一下他的资料:74LS161 pdf 资料下载:/view.jsp?Searchword=74LS16174ls161引脚图管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

74LS90引脚图及引脚功能

74LS90计数器是一种中规模二一五进制计数器,管脚引线如图3.6-1,功能表如表3.6-1所示。

表3.6-1 7490功能表

A . 将输出Q A 与输入

B 相接,构成8421BCD 码计数器; B . 将输出Q D 与输入A 相接,构成5421BCD 码计数器;

C . 表中H 为高电平、L 为低电平、×为不定状态。

74LS90逻辑电路图如图3.6-1所示,它由四个主从JK 触发器和一些附加门电路组成,整个电路可分两部分,其中F A 触发器构成一位二进制计数器;F D 、F C 、F B 构成异步五进制计数器,在74LS90计数器电路中,设有专用置“0”端R 1、R 2和置位(置“9”)端S 1、S 2。

74LS90具有如下的五种基本工作方式:

(1)五分频:即由F D 、F C 、和F B 组成的异步五进制计数器工作方式。

(2)十分频(8421码):将Q A 与CK 2联接,可构成8421码十分频电路。

(3)六分频:在十分频(8421码)的基础上,将Q B 端接R 1,Q C 端接R 2。

其计数顺序为000~101,当第六个脉冲作用后,出现状态Q C Q B Q A =110,利用Q B Q C =11反馈到R 1和R 2的方式使电路置“0”。

(4) 九分频:Q A →R 1、Q D →R 2,构成原理同六分频。

(5)十分频(5421码):将五进制计数器的输出端Q D 接二进制计数器的脉冲输入端CK 1,即可构成5421码十分频工作方式。

此外,据功能表可知,构成上述五种工作方式时,S 1、S 2端最少应有一端接地;构成五分频和十分频时,R 1、R 2端亦必须有一端接地。