系统时序

推荐系统中的时序推荐算法(二)

时序推荐算法是一种根据用户的历史行为和时间信息,预测和推荐用户在未来可能感兴趣的物品的算法。

在推荐系统中,时序推荐算法是一种非常重要且具有挑战性的算法。

本文将探讨时序推荐算法的原理、常见的模型以及优缺点。

一、时序推荐算法的原理时序推荐算法的核心思想是分析用户在历史时间段内的行为序列,并根据行为序列的模式预测未来可能的行为。

时序推荐算法通常包含以下几个重要的步骤:1. 数据预处理:首先,需要对用户的历史行为数据进行预处理,将其转化为适合算法处理的格式。

这包括对用户行为进行编码、时间戳处理和特征筛选等。

2. 行为序列建模:在建模阶段,时序推荐算法通常会将用户的行为序列表示为一个状态序列。

常用的方法有马尔可夫链模型和循环神经网络模型。

马尔可夫链模型假设用户行为仅与前一时刻的状态有关,而循环神经网络模型则可以捕捉更长时间的时序依赖关系。

3. 时序分析与预测:在时序分析阶段,时序推荐算法会对用户的行为序列进行分析,探索其中的时序模式。

常用的方法包括序列模式挖掘、频繁模式挖掘和周期性模式挖掘等。

在预测阶段,算法会根据分析得到的模式预测用户未来的行为,从而实现个性化推荐。

二、常见的时序推荐算法模型1. 马尔可夫链模型(Markov Chain Models):马尔可夫链模型是一种基于概率的时序推荐算法。

它假设用户行为仅与前一时刻的状态有关,利用马尔可夫链的理论对用户行为进行建模和预测。

马尔可夫链模型简单且易于实现,但无法捕捉更长时间依赖关系。

2. 隐马尔可夫模型(Hidden Markov Models):隐马尔可夫模型是一种集合马尔可夫链和观测数据的统计模型,可以用于时序推荐算法中的状态预测。

隐马尔可夫模型能够考虑更长期的时间依赖关系,但模型参数的学习和推断过程相对较复杂。

3. 循环神经网络模型(Recurrent Neural Network Models):循环神经网络模型是一种具有记忆功能的神经网络模型,可以捕捉任意长度的时序依赖关系。

系统研发计划(时序图)

抓牛股着陆页研发完毕

抓牛股着陆页发布部署到线上 环境

解套着陆页研发完毕

解套着陆页发布部署到线上环 境

整体需求确定

与需求接口人确定系统整 体需求

着陆页打版功能上线

将版本内容管理功能、渠 道维护Βιβλιοθήκη 能、着陆页模版发布 部署到线上环境

抄底着陆页研发完毕

抄底着陆页发布部署到线上环 境

10月25日

11月10日

11月20日

11月22日

11月28日

12月8日

着陆页打版功能研发完毕

版本内容管理功能、渠道 维护功能、着陆页模版研发完 毕,提供业务部门和测试部门 测试

嵌入式系统设计中的时序逻辑优化技术

嵌入式系统设计中的时序逻辑优化技术嵌入式系统是指将软件和硬件融合在一起,以满足特定应用需求的系统。

其具有体积小、功耗低、性能稳定等特点,被广泛应用于智能家居、工业自动化、医疗设备等领域。

时序逻辑优化技术是嵌入式系统设计中的重要部分,它能够对时序路径进行优化,提高系统的工作速度和稳定性。

一、时序逻辑优化技术的需求一个典型的嵌入式系统中通常会涉及到时序逻辑的设计,如时钟、状态转移、通信等等。

在时序逻辑的设计和优化过程中,需要考虑以下几个方面的需求。

1. 时序要求时序要求是指时序电路中所涉及的信号的时间关系要求。

为使电路能够正常工作,每个端点的数据必须在一个确定的时间内准确到达。

如果这个时间太短,那么电路会出现时序失效,从而影响系统性能,甚至会导致电路故障。

因此,在时序电路的设计中,需要仔细考虑时序要求。

2. 频率要求频率要求是指电路的时钟频率要求,这与时序要求密切相关。

在时序电路的设计和优化中,需要对电路的时钟频率进行定量分析,以确定电路的工作频率和稳定性。

3. 电路复杂度随着电路的不断增加,电路的复杂度也在不断增加。

在复杂电路中,时序逻辑的设计和优化变得更加困难,因此需要使用更加先进的时序逻辑优化技术。

二、时序逻辑优化技术的作用时序逻辑优化技术,可以对时序路径进行优化,从而提高系统的性能和稳定性。

具体来说,时序逻辑优化技术可以发挥以下作用:1. 降低系统延迟在时序电路中,如果电路延迟较大,则数据的传输速度会受到影响。

通过时序逻辑优化技术,可以对电路中的延迟路径进行优化,从而降低系统的延迟,提高系统的传输速率。

2. 提高系统的工作速度在嵌入式系统中,速度是非常重要的,决定了系统的工作效率和响应能力。

通过时序逻辑优化技术,可以降低系统的延迟,从而提高系统的工作速度。

3. 降低功耗时序电路的功耗主要与时钟频率和电路延迟有关。

通过时序逻辑优化技术,可以优化电路的时钟频率,并通过简化时序逻辑路径来降低电路延迟,从而达到降低功耗的目的。

系统中的时序算法

系统中的时序算法时序算法是一种通过对事件发生的顺序进行分析和处理的算法。

它广泛应用于许多领域,包括计算机图形学、物理仿真、通信协议和生物信息学等。

时序算法的核心思想是根据事件发生的时间先后顺序来确定它们的关系和影响。

本文将介绍几种常见的时序算法及其应用。

一、离散事件模拟离散事件模拟是一种通过模拟事件的发生来研究和分析系统行为的方法。

它模拟的是离散事件系统,即系统的状态在离散的时间点上发生变化。

在离散事件模拟中,事件有严格的时间先后顺序,并且事件之间可以相互影响。

离散事件模拟的一个典型应用是网络通信协议的仿真。

在网络通信中,数据包之间的发送和接收顺序非常重要,因为错误的顺序可能导致数据包丢失或数据损坏。

通过离散事件模拟,可以模拟数据包的发送和接收过程,并验证通信协议的正确性和性能。

二、排序算法排序算法是一种根据元素的大小进行排序的算法。

时序排序算法是一种特殊的排序算法,它根据元素的时间先后顺序进行排序。

在时序排序算法中,元素的时间戳被用作排序的依据,而不是元素的值。

时序排序算法在许多领域有着广泛的应用,如事件日志的分析、订单处理的优化等。

通过时序排序算法,可以根据事件发生的时间顺序对数据进行排序,并找到事件发生的顺序规律和时间间隔。

三、物理仿真物理仿真是一种通过模拟物理系统来研究和分析其行为的方法。

物理系统中,事件的发生具有明确的时间顺序和影响关系。

时序算法在物理仿真中发挥着重要的作用,可以模拟物理系统中事件的发生和演化过程。

物理仿真的应用非常广泛,如游戏开发、虚拟现实等。

通过时序算法,可以模拟物体之间的碰撞、运动轨迹和相互作用等物理现象,从而实现真实的物理效果。

四、图形渲染图形渲染是一种将图形数据转化为可视结果的过程。

在图形渲染中,图形的绘制顺序非常重要,因为绘制的顺序决定了图形的覆盖关系。

时序算法在图形渲染中可以用来确定需要绘制的顺序。

图形渲染的一个常见应用是三维场景的渲染。

通过时序算法,可以根据物体的深度信息确定它们在屏幕上的绘制顺序,从而实现透视效果和物体的遮挡关系。

系统时序分析

第六章系统时序对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整地传送到接收端,就必须进行精确的时序计算和分析。

同时,时序和信号完整性也是密不可分的,良好的信号质量是确保稳定的时序的关键,由于反射,串扰造成的信号质量问题都很可能带来时序的偏移和紊乱。

因此,对于一个信号完整性工程师来说,如果不懂得系统时序的理论,那肯定是不称职的。

本章我们就普通时序和源同步系统时序等方面对系统时序的基础知识作一些简单的介绍。

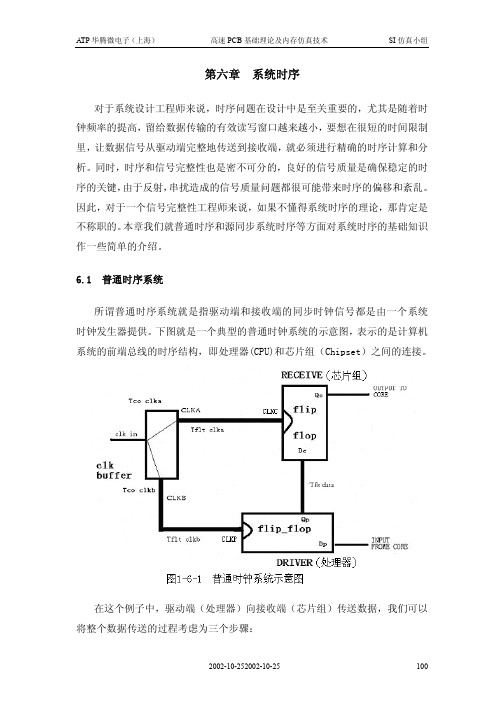

6.1 普通时序系统所谓普通时序系统就是指驱动端和接收端的同步时钟信号都是由一个系统时钟发生器提供。

下图就是一个典型的普通时钟系统的示意图,表示的是计算机系统的前端总线的时序结构,即处理器(CPU)和芯片组(Chipset)之间的连接。

在这个例子中,驱动端(处理器)向接收端(芯片组)传送数据,我们可以将整个数据传送的过程考虑为三个步骤:1.核心处理器提供数据;2.在第一个系统时钟的上升沿到达时,处理器将数据Dp锁存至Qp输出;3.Qp沿传输线传送到接收端触发器的Dc,并在第二个时钟上升沿到达时,将数据传送到芯片组内部。

一般来说,标准普通时钟系统的时钟信号到各个模块是同步的,即图中的Tflight clka 和Tflight clkb延时相同。

通过分析不难看出,整个数据从发送到接收的过程需要经历连续的两个时钟沿,也就是说,如果要使系统能正常工作,就必须在一个时钟周期内让信号从发送端传输到接收端。

如果信号的传输延迟大于一个时钟周期,那么当接收端的第二个时钟沿触发时,就会造成数据的错误读取,因为正确的数据还在传输的过程中,这就是建立时间不足带来的时序问题。

目前普通时序系统的频率无法得到进一步提升的原因就在于此,频率越高,时钟周期越短,允许在传输线上的延时也就越小,200-300MHz已经几乎成为普通时序系统的频率极限。

推荐系统中的时序推荐算法(七)

推荐系统中的时序推荐算法一、时序推荐算法的重要性时序推荐算法是推荐系统中的一种重要算法,它可以根据用户的历史行为和时间上的关联性,预测用户在未来的兴趣和需求,从而提供个性化的推荐结果。

时序推荐算法不仅可以增加用户对推荐系统的满意度,还可以提高推荐结果的点击率和转化率,对于电子商务、社交媒体等领域的应用具有重要意义。

二、时序推荐算法的基本原理时序推荐算法的基本原理是利用用户的历史行为数据和时间信息来建模用户的兴趣演化规律。

首先,通过对用户的历史行为进行分析,可以得到用户对不同物品的喜好程度。

然后,根据时间信息,可以发现用户的兴趣在不同时间段之间可能存在一定的变化。

最后,通过建立用户兴趣的时序模型,可以预测用户未来的兴趣和需求。

时序推荐算法的核心在于对用户兴趣的时序变化进行建模和预测。

三、常见的时序推荐算法1. 基于协同过滤的时序推荐算法基于协同过滤的时序推荐算法是一种基于用户行为的推荐方法,它通过分析用户在不同时间段的行为模式,来预测用户在未来的兴趣。

该算法利用协同过滤的思想,将用户行为看作时间序列数据,通过计算用户之间的相似度来预测用户的未来兴趣。

该算法具有较好的效果,但是对于新用户和冷启动问题存在一定的局限性。

2. 基于深度学习的时序推荐算法基于深度学习的时序推荐算法是近年来兴起的一种推荐方法,它利用神经网络模型来模拟用户兴趣的时序变化。

该算法可以自动学习用户的兴趣模式,并根据时间信息预测用户未来的兴趣。

基于深度学习的时序推荐算法具有较强的表达能力和预测能力,在推荐系统中具有广泛的应用前景。

四、时序推荐算法的挑战和解决方案1. 数据稀疏性问题时序推荐算法在建模过程中可能会遇到数据稀疏性问题,即用户的历史行为数据较少或不够丰富。

为了解决这一问题,可以采用增加物品特征、引入上下文信息、利用用户社交网络等方法来丰富数据。

2. 冷启动问题冷启动问题是指对于新用户或新物品,由于缺乏充足的历史行为数据,难以预测其未来的兴趣。

推荐系统中的时序推荐算法(五)

推荐系统是现代互联网应用中广泛使用的一种技术。

随着用户对个性化体验的需求增加,推荐系统的重要性也日益凸显。

时序推荐算法作为推荐系统中的一种重要算法,可以根据用户的历史行为和时间信息,预测用户可能感兴趣的物品,为用户提供更加精准的推荐。

一、时序推荐算法的概述时序推荐算法是基于时间序列分析的推荐算法。

它通过分析用户行为的时间先后顺序,挖掘用户的兴趣演化规律,从而预测用户未来可能感兴趣的物品。

时序推荐算法的核心思想是将用户的历史行为转化为时间序列数据,然后利用时间序列分析方法对数据进行建模和预测。

常用的时间序列分析方法包括滑动窗口、指数平滑、ARIMA模型等。

二、时序推荐算法的应用场景时序推荐算法广泛应用于各种推荐场景中,例如电商平台的商品推荐、视频网站的视频推荐、社交媒体的用户关注推荐等。

以电商平台为例,时序推荐算法可以通过分析用户的购买记录和浏览记录,预测用户未来可能购买的商品。

同时,可以根据用户的活跃时间和购买周期,调整推荐策略,提高推荐准确度。

三、时序推荐算法的关键技术1. 数据预处理:时序推荐算法需要对原始数据进行清洗和规范化处理。

需要考虑的因素包括数据缺失、异常值、离散化等。

2. 特征提取:时序数据中包含了丰富的信息,例如用户行为的时间间隔、购买频率等。

特征提取是时序推荐算法的关键步骤,可以通过统计方法或机器学习方法进行。

3. 模型建立:时序推荐算法可以使用各种时间序列分析方法建立预测模型,如ARIMA模型、指数平滑模型等。

同时,还可以结合机器学习方法,使用深度学习模型进行预测。

4. 模型评估:时序推荐算法的准确度对推荐效果至关重要。

可以使用交叉验证等方法进行模型评估,选择最优模型。

四、时序推荐算法的挑战和未来发展方向时序推荐算法面临着一些挑战,例如数据稀疏性、冷启动问题、时序模式识别等。

解决这些问题需要结合领域知识和创新算法。

未来,时序推荐算法可能会在以下几个方向上得到进一步的发展:1. 基于深度学习的时序推荐算法:深度学习在图像和自然语言处理等领域取得了重要突破,可以尝试将其应用于时序推荐算法中。

时序逻辑系统名词解释

时序逻辑系统名词解释

时序逻辑系统是一种用于描述电路或系统中时间相关事件的逻辑系统。

下面是一些常见的时序逻辑系统名词及其解释:

1. 时钟信号(Clock Signal):时钟信号是一个周期性的信号,用于同步电路和系统中的各个部分,以确保它们在正确的时间进行操作。

2. 时序逻辑电路(Sequential Logic Circuit):时序逻辑电路是一种电路,其输出值取决于电路内部状态和输入信号的组合。

时序逻辑电路包括触发器、寄存器、计数器等。

3. 触发器(Flip-flop):触发器是一种时序逻辑电路元件,用于存储二进制数据。

常见的触发器包括SR触发器、D触发器、JK触发器等。

4. 稳态(Steady State):稳态是指时序逻辑电路的输出值在输入信号稳定后达到稳定状态。

在稳态下,电路输出值不再变化。

5. 时序逻辑设计(Sequential Logic Design):时序逻辑设计是指将时序逻辑电路组合起来以实现特定功能的过程。

时序逻辑设计需要考虑时序逻辑电路的时序特性,包括时序分析和时序优化等。

6. 时序逻辑分析(Sequential Logic Analysis):时序逻辑分析是指分析时序逻辑电路在不同输入信号下的输出结果。

时序逻辑分析需要考虑电路的时序特性,包括时钟频率、信号延迟等。

7. 时序优化(Timing Optimization):时序优化是指通过优化电路结构和管脚布局等方法,以提高电路的时序性能,包括最大工作频率、最小时钟周期等。

时序逻辑系统的设计和分析需要深入理解这些术语的含义,并结合实际应用场景进行合理的选择和优化。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

系统时序适合Intel Chipset部门:FAE技术研发组V1.0EC_CLK_EN EC这是VCORE CHIP发出,此板没有使用CLOCK-工作条件输入电压输入电压Enable信号参考电压CLOCK-系统CLOCK1NAME User F NAME User F CLK_MCH_BCLK MCH HPLL166MHz CLK_MCH_BCLK#MCH HPLL166MHz CLK_CPU_BCLK CPU Bus Clock166MHz CLK_CPU_BCLK#CPU Bus Clock166MHz CLK_PCIE_LAN LAN99MHz CLK_PCIE_LAN#LAN99MHz CLK_MCH_3GPLL MCH PEG99MHz CLK_MCH_3GPLL#MCH PEG99MHz CLK_PCIE_NEWCARD NEWCARD99MHz CLK_PCIE_NEWCARD#NEWCARD99MHz CLK_PCIE_MINICARD1MINICARD99MHz CLK_PCIE_MINICARD1#MINICARD99MHzCLK_PCIE_PEG VGA PCIE busclock 99MHz CLK_PCIE_PEG#VGA PCIE busclock99MHzClk_PCIE_ICH DMI bus clock99MHz Clk_PCIE_ICH#DMI bus clock99MHz CLK_PCIE_MINICARD0WLAN99MHz CLK_PCIE_MINICARD0#WLAN99MHz CLK_PCIE_SATA SATA HDD99MHz CLK_PCIE_SATA#SATA HDD99MHz CLK_DREF MCH96MHz CLK_DREF#MCH96MHz CLK_DREFSS MCH VGA96MHz CLK_DREFSS#MCH VGA96MHzCLOCK-系统CLOCK2NAME User F NAME User F CLK_VGA27SS VGA27MHz CLK_VGA27FIX VGA27MHz CLK_USB48USB48MHz CLK_CBPCI Card Bus33MHz CLK_TPMPCI TPM33MHz CLK_DBGPCI2Debug 33MHz CLK_ICH14ICH14.318MHz CLK_ICHPCI ICH PCI33MHz CLK_SIO14Super I/O14.318MHz CLK_SIOPCI Super I/O33MHz CLK_KBCPCI LPC Bus33MHzPM_PWROK当EC第Pin55接收到CPU_PWRGD延时后,从Pin148发出PM_PWROK说明:当EC接收到CPU_PWRGD以后会先后发出EC_CLK_EN和PM_PWROK这里会把PM_PWROK有个延时动作,作用是让Clock工作后系统CLK到位,至于这个延时的时间是由软体RD在BIOS里面进行控制PWROKBUF_PLT_RST#1与PLT_RST#_SBCLK_ICHPCIPM_PWROK_R 其他输入南桥的频率,不会影响RST#PCI_RST#_ICHPLT_RST#_SBH_PWRGDRST#BUF_PLT_RST#_1用于NB,LAN,VGA BUF_PLT_RST#_2用于LPCBUF_PLT_RST#_3用于Super I/O,TPMPCI_RST#用于CardBus,Newcard 电源管理器,Mini CardCPU_RST#BUF_PLT_RST#_1PWROKCLK_MCH_3GPLLCLK_MCH_3GPLL#CLK_PCIE_ICH(DMI)CLK_PCIE_ICH#(DMI) VCC_AXMVCC_RXR_DMI_[1:2] VCC_PEG[1:5]+1.5VS_PCIE_ICH VCCDMIPLL H_CPURST#电压ClockCPU动作SB发出的H_PWRGDNB发出的H_CPURST#CPU动作VCOREVCCP_CPUGTL_REF这里说的CPU动作,只是指CPU工作,但是AD还没有传输.AD 传输动向CPU MCH DDR2/3VGA ICH EC BIOS FSBDMILPC F LAN WLAN NC RPSPCI-E???系统时序-HostBusH_A#[3:35]地址线H_D#[0:63]数据线H_ADSTB#[0:1]地址选通H_DSTBN#[0:3]数据选通H_DSTBP#[0:3]数据选通H_REQ#[0:4]请求命令H_DINV#[0:3]动态总线倒置H_ADS# 地址选通H_BNR#下一模块请求H_BPRI#总线优先权请求H_DEFER#延迟H_DRDY#数据读取H_DBSY#数据总线忙H_BR0#总线请求H_LOCK#锁定H_CPURST#CPU复位H_RS#[0:2]响应状态H_TRDY#目标准备H_HIT#侦测H_HITM#侦测修改系统时序-HostBus11.H_A#[3:35] I/O Address 地址总线这组地址信号定义了CPU的最大内存寻址空间为64GB。

在地址周期的第一个子周期中,这些Pin传输的是交易的地址,在地址周期的第二个子周期中,这些Pin传输的是这个交易的信息类型2.H_D#[0:63] I/O Data 数据线这些讯号线是数据总线主要负责传输数据。

它们提供了CPU与NB之间64 Bit的通道。

只有当DRDY#为Low时,总在线的数据才为有效,否则视为无效数据3.H_ADSTB#[0:1] I/O Address Strobes 地址选通这两个信号主要用于锁定A[35:3]#和REQ[4:0]#在它们的上升沿和下降沿。

相应的ADSTB0#负责REQ[4:0]#和A[16:3]#,ADSTB1#负责A[31:17]#Strobe Address BitsH_ADSTB#0H_A#[3:15] H_REQ#[0:4]H_ADSTB#1H_A#[16:35]4.H_DSTBN#[0:3] I/O Data Strobe 数据选通5.H_DSTBP#[0:3] I/O Data Strobe 数据选通Strobe Data BitsH_DSTBN#3 H_DSTBP#3H_D#[63:48] H_DINV#3H_DSTBN#2 H_DSTBP#2H_D#[47:32] H_DINV#2H_DSTBN#1 H_DSTBP#1H_D#[31:16] H_DINV#1H_DSTBN#0 H_DSTBP#0H_D# [15:0] H_DINV#06.H_REQ#[0:4] I/O Request Command 命令请求当总线拥有者开始一个新的交易时,由它来定义交易的命令7.H_DINV#[0:3] I/O Dynamic Bus Inversion 动态总线倒置表明了相关的数据是否翻转,数据线在电子特性上被驱动为低.8.H_ADS# I/O Address Strobe 地址选通当这个信号被宣称时说明在地址信号上的数据是有效的。

在一个新的交易中,所有Bus上的信号都在监控ADS#是否有效9.H_BNR# I/O Block Next Request 下一模块请求这个信号用来阻止当前请求的总线控制器发出新的请求,来动态的控制处理器的传输.10.H_BPRI# NB→CPU Bus Priority Request 总线优先权请求当BPRI#有效时,所有其他的设备都要停止发出新的请求,除非这个请求正在被锁定,总线所有者要始终保持BPRI#为有效,直到所有的请求都完成才能释放总线的控制权11.H_DEFER# NB→CPU Defer 延迟这个信号会结束当前的传输,用以个延迟指令或一个重试指令转入探测12.H_DRDY# I/O Data Ready 数据读取这个信号在数据传输的每个循环周期的开始有效13. H_DBSY# I/O Data Bus Busy 数据总线忙数据总线拥有者,使用这个信号来保证数据总线上的传输命令多于一周期,此时总线有数据正在处理14. H_BR0# I/O Bus Request 总线请求北桥在H_CPURST#有效期间,把此信号拉第低,处理器在H_CPURST#从无到有的时候,采样此信号,最小的设置时间是4HCLKS,最小的保持时间时2个时钟周期,最大的时20个HCLKS,当保持时间满足要求后,此信号需保持三态.15. H_LOCK CPU→NB Lock 锁定直到H_LOCK#取消后,所有的处理器总线周期才可以采样16. H_CPURST# NB→CPU CPU Reset CPU复位北桥输出,当北桥接收到BUF_PLT_RST#_1有效,并且有效后一毫秒发出,这个信号使处理器按一个已知状态开始运作17. H_RS#[0:2] NB→CPU Response Status 相应状态这个信号表明了相应的类型,如下表H_RS#[0:2]Response type000Idle state 空閑狀態001Retry response重試010Deferred response延遲011Reserved (Not driven by (G)MCH)保留100Hard Failure (Not driven by (G)MCH)硬件失效101Not data response正常,沒有數據110Implicit write back隱含回寫111Normal data response正常有數據系统时序-HostBus618. H_TRDY# NB→CPU Target Ready 目标准备当这个信号有效时表示可以接收数据19. H_HIT# I/O Hit 侦测这个信号表明了一个缓冲代理保持了请求总线上未被更改的副本,也可以由目的设备发出相关联的信号20. H_HITM# I/O Hit Modified 侦测修改这个信号表明了缓冲代理保持一个请求总线上被修改的指令,并假定这个代码器对提供请求总线有责任与H_HIT#相关联来扩展SNOOP窗口.系统时序-DMIDMI(Direct Media Interfact)直接媒体界面传输1. DMI_TXN[0:4] SB→NB Differential Transmit Pair 差分输出对2.DMI_TXP[0:4] SB→NB Differential Transmit Pair 差分输出对3.DMI_RXN[0:4] NB→SB Differential Receive Pair 差分输入对4.DMI_RXP[0:4] NB→SB Differential Receive Pair 差分输入对5.DMI_ZCOMP →SB Impedance Compensation Input 阻抗补偿输入这个信号用来决定DMI输入补偿6. DMI_IRCOMP SB→ Impedance/Current Compensation Output 阻抗/电流补偿输出这个信号用来决定DMI输出补偿或偏流系统时序-LPCLPC(Low Pin Count)低脚位计算1.LPC_AD[0:3] I/O Address Data 数据地址这四讯号线用来传输LPC Bus地址和数据2.LPC_FRAME# I/O LPC Frame LPC的周期框架当这个讯号有效时,指示开始或结束一个LPC周期3. LPC_DRQ#0 →SB DMA Request DMA请求当Super I/O上的Device需要用DMA 通道时,就会驱动这个讯号向南桥发出请求系统时序-FlashBus1.FA[0:19] I/O Address 地址线用来传输Flash Bus 地址2.FD[0:7] I/O Data 数据线用来传输Flash Bus 数据3.FRD# EC→BIOS Read 读取控制当有效时表示读取BIOS指令4.FWR# EC→BIOS write 写入控制当有效时表示写入BIOS指令5.FCS# EC→BIOS Chip Select片选信号当有效时表示BIOS这个CHIP 已经被选择FA2/BADDR0FA3/BADDR1FA4/PPENFA5/SHBMDebugCard功能说明1. 如M/B 上有預留NEWCARD debug 線路:可用Newcard connector 以LPC 或SMBUS 顯示post code. (優先權: LPC>SMBUS)2. 如M/B 上有拉LPC 訊號到FPC connector 12P:可用12P FFC 連接FPC connector,可顯示LPC post code.3. 如M/B 上無debug 線路:可用Newcard connector 以顯示SMBUS post code. Note: BIOS 的SMBUS post code 在Santa Rosa 平台以後才有支援.DebugCard开关介绍ON OFFSW1以DebugCard的Rom开机以M/B的Rom开机SW2Reserved ReservedSW3不Flash BIOS Flash BIOS (注1) SW4选择SIO 2E/2F选择SIO 4E/4F註1: debug card 需裝上LPC/FWH 的ROM.註2: 選擇SIO 位址,避免與M/B 上的SIO 位址相衝.2. LPC/FWH ROM connector:裝LPC/FWH 的ROM.(ISA 的不能用)3. LED function:POWER-ON LED(當+3V 電源來, 此LED 燈亮)Debug ROM LED(當switch 開關1 切換至ON, LED 燈亮) FLASH BIOS LED(當switch 開關3 切換至OFF, LED 燈亮)示波器代替DebugDebug卡侦测的是LPC Bus,我们可以利用示波器测量LPC 来判断主板“跑”到什么地方量测信号:LPC_AD[0:3],任意一个使用一块独立显卡的好板第一步确定9E,主板上电不上CPU,开机观察波形第二步确定E0.主板上CPU,不上内存,开机观察波形第三步确定显示,上CPU,内存不上显卡,开机观察波形记下以上三个步骤示波器“跑”的波形,然后在以后修板中就可以利用这三个点来确定主板有没有读内存,有没有跑到显示部分ENDDebug卡图片差分CLOCK差分Clock:大小相等,极性相反的一组Clock好处:比起单端Clock区有抗干扰特性差分对的参考点是由一对正极或一对负极交会处(P由负转正,N由正转负,或是双边触发),由于正负两种讯号都有,并以交会点做触发,所以对外界带来的正向干扰或是负向干扰都有抵抗的功能CLK_EN#。