高速源同步系统的时序分析

高速并行处理模式下同步时序研究

在这 种方 式下 的时 序 分 析 , 我 们 可 以理 解 相 关 的 一些 时序 参数 的具 体含 义 。 比如

钟偏 移等 。

建 立时 间 、 保持时间、

C P U数据接 口以及 芯片之间的并行互 连接 口等。这

些 高速 的数 据接 口基 本 工 作 在 1 0 0 MH z 频率以上, 每

Ke y wo r d s :h i g h — s p e e d c l o c k c i r c u i t ,s o u r c e s y n c h r o n o u s ,r e d u n d a n c y ,S DR AM

引 言

的走 线 分 配 给 各 个 S D R A M 芯 片 。 因 此 也 可 称 作

2 0 1 5年 第 1 1期

d o i : 1 0 . 1 1 8 3 2 / j . i s s n . 1 0 0 0 - 4 8 5 8 . 2 0 1 5 . 1 1 . 0 2 9

液 压 与 气 动

1 3 1

高速 并 行 处 理 模 式 下 同步 时序 研 究

查 环

1 0 0 0 9 7 ) ( 海 装 装 备 采 购 中心 , 北京

p o i n t s o me v a l u a b l e c o n c l u s i o ns f r o m t h e a na l y s i s o f t h e c a s e,a n d a l s o g i v e s o me r e a s o n a b l e a d v i c e s a bo u t p r i n c i p l e o f hi g h— s p e e d c i r c u i t PCB l a y o u t .

《2024年DDR4高速并行总线的信号完整性仿真分析》范文

《DDR4高速并行总线的信号完整性仿真分析》篇一一、引言随着电子技术的飞速发展,DDR4内存以其高速、大容量的特点,广泛应用于计算机、服务器等高端设备中。

DDR4高速并行总线作为数据传输的重要通道,其信号完整性的保障对于整个系统的性能至关重要。

本文将通过仿真分析的方法,对DDR4高速并行总线的信号完整性进行深入探讨。

二、DDR4高速并行总线概述DDR4(Double Data Rate 4)是一种高速内存技术,具有更高的数据传输速率和更低的功耗。

其总线结构采用并行传输方式,可以同时传输多条数据通道,极大地提高了数据的传输效率。

然而,高速并行传输带来的问题就是信号完整性的保障问题,需要通过一系列仿真分析和设计手段来解决。

三、信号完整性仿真分析方法针对DDR4高速并行总线的信号完整性仿真分析,我们主要采用以下方法:1. 建立仿真模型:根据DDR4总线的物理特性和电气特性,建立精确的仿真模型。

包括总线拓扑结构、传输线参数、负载阻抗等。

2. 仿真环境设置:设置仿真环境参数,如信号频率、传输速率、噪声干扰等。

这些参数将直接影响仿真结果的准确性。

3. 仿真过程:通过仿真软件对建立的模型进行仿真分析,观察信号在总线上的传输过程,分析信号的完整性和时序性。

4. 结果分析:根据仿真结果,分析信号完整性的影响因素,如传输线损耗、反射、串扰等,并提出相应的优化措施。

四、仿真结果与分析通过上述仿真分析方法,我们得到了DDR4高速并行总线的信号完整性仿真结果。

以下是部分结果的分析:1. 传输线损耗:仿真结果显示,随着信号频率的提高,传输线损耗逐渐增大。

为降低损耗,可采用差分传输线技术、优化拓扑结构等方法。

2. 反射问题:仿真发现,总线上的反射问题主要来自于阻抗不匹配。

为解决这一问题,可在总线关键位置设置匹配电阻,以减小反射。

3. 串扰问题:串扰是多个信号线之间相互干扰的问题。

通过优化布线策略、增加地线屏蔽等方法,可有效降低串扰对信号完整性的影响。

高速pcb设计与电路板分析课程讲义3

高速设计分析技术Agenda 课程安排High Speed Trends 高速设计趋势y gSynchronous Design 同步系统设计Source Synchronous Design 源同步系统设计-DDR2-DDR3Serial Link Design 高速串行设计-Interconnect consideration 互连考虑I t t id ti-Technologies 设计技术-8b/10b Encoding 8b/10b编码Trend towards serial connectivity向串行连接发展高速电路设计趋势Parallel I/O − Common Clock并行IO –共同时钟系统Pre-layout simulation for design exploration and post-layout simulation for verification可以通过SI前后仿真进行设计•Signal timing 信号时序•Signal noise 信号噪声•Undershoot and overshoot 过冲Parallel I/O − Common Clock (继续) 并行IO –共同时钟Increase data pin counts How to increase data rate? 如何提高数据速率Increase data pin counts 增加管脚Increase bus clock frequency 增加时钟频率But…… 但是……•Increase data pin counts − it’s more hard for PCB design(need more space for trace breakout, routing…..) 增加管脚造成PCB 设计困难•Increase clock frequency − it will reduce timing margin,destroy signal integrity (due to multi-drop top.), restrict data trace length, increase EMI…增加时钟频率使得时序紧张, 信号完整性问题突出, 走线线长约束严格, 电磁辐射增加…Parallel I/O − Source Synchronous并行I/O –源同步系统Provide guidelines for physical layout by sweeping the solution space 可以通过参数扫描分析确定电气约束Measurements for voltage and time specifications and worst case Measurements for voltage and time specifications and worst case report 得到最坏情况下的信号质量和时序要求Bus timing analysis 总线时序分析•Slew rate prorating/derating for Setup/Hold Time compensations (DDR2) 考虑边沿速率造成的的建立保持时间的补偿(DDR2)Increase bus clock frequency Parallel I/O − Source Synchronous (继续)并行I/O –源同步系统How to increase data rate? 如何提高数据速率Increase bus clock frequency 增加时钟频率From single strobe to dual strobe 采用读写数据采样时钟From single end strobe to differential strobe signaling 采用差分时钟•Increase bus clock frequency − there is no theoretical limit on bus clock frequency, but higher clock frequency will cause signal integrity depredation(due to multi ‐drop top.) But…… 但是……p (p p )增加时钟频率使得信号完整性问题突出…•From single strobe to differential strobe − for less timing margin while design migrates to high speed, differential strobe will increase valid timing window采用差分时钟提高速率但是因为速率提高, 时序参数更为紧张Parallel I/O -Integrating SI with Timing 并行接口分析–综合考虑SI 和时序Multiple TopologiesWaveformandSolution SpaceTiming Equation Signal Integrity and Timing Analysis integrated to one solution 信号完整性和时序分析组成一个完整的解决方案Vin_AC_HighVin_DC_HighVrefVin_DC_LowVin_AC_Low “Sim Start time” normalizedSerial I/O 串行I/OInterconnect loss of the channel (entire signal path) 考虑互连损耗Jitter controlled is required due to CDR 控制抖动Modeling complex drivers and receivers 需要更复杂的器件模型 Stress test the design with LARGE bit streams 要分析大量数据位传输S-parameter simulation (Time domain & Frequency Domain) S-参数分析, 时域和频域分析Agenda 课程安排High Speed Trends 高速设计趋势y gSynchronous Design 同步系统设计Source Synchronous Design 源同步系统设计-DDR2-DDR3Serial Link Design 高速串行设计-Interconnect consideration 互连考虑I t t id ti-Technologies 设计技术-8b/10b Encoding 8b/10b编码Synchronous Design 同步设计系统Sometimes called “Common Clock” 又叫共同时钟系统Clocks are distributed from a central point to all of the loads. 时钟信号由同一时钟源发送Max operating frequency is a function of Tco, Tpd, Setup, Hold, and M ti f i f ti f T T d S t H ld d Clock Skew最大工作频率由缓冲延时,传输延时,建立,保持时间和时钟偏移决定Synchronous Data Transfer 数据传输方式Clock 14HoldDriverT coFlight Time Setup23D0 D1 D2D0 D1 D2Driving ReceivingSynchronous Timing Terminology时序参数Cycle Time (Tcycle)时钟周期Clock Skew时钟偏移Cycle 1Cycle 2 Clock to Output (Tco)时钟输出延时Clock JitterSynchronous Timing Terminology (继续)时序参数Interconnect Delay (Tpd)互连传输延时Positive Interconnect Delay (Tpd)Negative Interconnect Delay (Tpd)Defining Tco Tco 定义Tco = time from clock rise to Vmeas into test load从时钟边沿进入器件到数据从器件输出有效的时间(数据输出接测试负载)DinClockOutput BufferInternal LogicClock rises t = 0V measT R L = 50 ΩTcoLoad for Tco measurement (from databook)Components of Tco Tco的组成ClockI t lClockDinOutputBufferInternalLogicR L= 50 Ωrisest = 0V measTcoInternal delay = from clock rise to the point where the output begins to switch内部逻辑时延External (buffer) delay = how long the buffer takes to drive the reference load to V meas缓冲器时延Clock Jitter 时钟抖动Clock Clock Jitter occurs when the clock period varies from one period to the nextDriverCycle 1Cycle 2one period to the next 考虑周期差抖动•Usually caused by PLLinstability in the clockdriver 通常由锁相环引起 Jitter increases / decreases the clock periodthe clock period,decreasing the effective clock cycle 抖动减小有效时钟周期Clock Skew 时钟偏斜Clock Driver t = 0Occurs when differentdevices see the clocktransition at differenttimesD0D0t = 1t = 2时钟到达不同器件的时延Increases / decreasesthe apparent clockcycle. Depending onwhich devices aredriving / receivingD1D2D1D2g g根据驱动接收不同变化Reduces the effectiveclock cycle 减小有效时钟周期内部偏斜和外部偏斜•时钟驱动器造成内部偏斜•而PCB布线和设计以及外部环境引起的偏斜被称为外C部偏斜tSKEW_INTRINSIC = 器件引起的偏斜tSKEW_EXTRINSIC = PCB + 布线+工作环境引起的偏斜tSKEW = tSKEW_INTRINSIC + tSKEW_EXTRINSIC内部偏斜-输出偏斜(tSK)•单一器件的指定输出之间的偏斜(JEDEC)•输出偏斜也称为引脚到引脚的偏斜。

高速总线的时序分析方法及DDR计算实例

高速总线的时序分析方法及DDR计算实例韩玉涛【摘要】随着高速存储器在通信系统和图像处理等领域的普遍使用,如果系统设计中的总线时序问题得不到满足,将会严重影响系统的运行稳定性.在详细介绍了高速总线的数学模型及时序分析方法的基础上,根据时序分析方法给出了SMP8634多媒体处理器与DDR DRAM接口连接的计算实例.【期刊名称】《常州工学院学报》【年(卷),期】2018(031)002【总页数】6页(P42-47)【关键词】DDR;高速总线;建立时间;保持时间;时序分析【作者】韩玉涛【作者单位】瑞为信息技术有限公司,广东深圳518000【正文语种】中文【中图分类】TN41随着处理器处理能力的快速提高,以及通信系统和图像处理等领域对数据高容量存储、大吞吐量传输的要求,DDR、DDR2以及DDR3 DRAM存储器得到了越来越广泛的应用。

这些存储器的工作频率都在100 MHz以上,高的可达1 GHz,这使得系统设计中的总线时序问题变得十分突出。

如果在系统设计中芯片的时序要求得不到满足,轻则会导致系统出现误码,处理能力降低,运行不稳定,严重的甚至会导致系统不能启动。

本文阐述高速数字总线的模型及时序分析方法,并给出SMP8634DDR多媒体处理器与DDR DRAM连接的计算实例。

1 高速总线模型高速总线模型如图1所示,U1和U2是两个在同一时钟CLOCK下工作的芯片,U1输出数据到U2。

图1 高速总线模型当U1输出数据时,U1在时钟上升沿后输出数据,然后输入芯片U2会在下一个时钟的上升沿去锁存数据总线上的数据,从上升沿到数据在数据总线上有效的时间称为时钟到数据的延时tCO。

图2表明了这种总线的时序关系。

图2 总线时序图tCLK:时钟CLOCK的周期。

tCO:芯片U1输出数据时,从时钟上升沿开始到数据出现在数据总线上的时间,此数据需要用到最大值tCOmax及最小值tCOmin。

tSU:芯片数据作为输入时,数据所需的建立时间(时钟上升沿前数据维持的时间),建立时间永远以最小值来计算。

系统时序分析

第六章系统时序对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整地传送到接收端,就必须进行精确的时序计算和分析。

同时,时序和信号完整性也是密不可分的,良好的信号质量是确保稳定的时序的关键,由于反射,串扰造成的信号质量问题都很可能带来时序的偏移和紊乱。

因此,对于一个信号完整性工程师来说,如果不懂得系统时序的理论,那肯定是不称职的。

本章我们就普通时序和源同步系统时序等方面对系统时序的基础知识作一些简单的介绍。

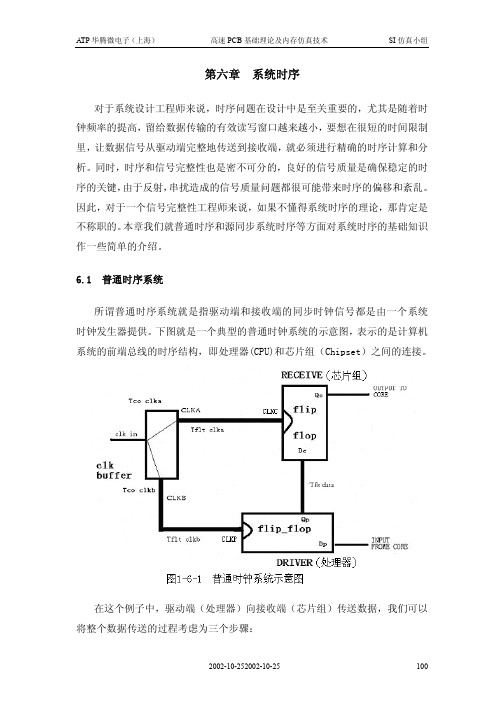

6.1 普通时序系统所谓普通时序系统就是指驱动端和接收端的同步时钟信号都是由一个系统时钟发生器提供。

下图就是一个典型的普通时钟系统的示意图,表示的是计算机系统的前端总线的时序结构,即处理器(CPU)和芯片组(Chipset)之间的连接。

在这个例子中,驱动端(处理器)向接收端(芯片组)传送数据,我们可以将整个数据传送的过程考虑为三个步骤:1.核心处理器提供数据;2.在第一个系统时钟的上升沿到达时,处理器将数据Dp锁存至Qp输出;3.Qp沿传输线传送到接收端触发器的Dc,并在第二个时钟上升沿到达时,将数据传送到芯片组内部。

一般来说,标准普通时钟系统的时钟信号到各个模块是同步的,即图中的Tflight clka 和Tflight clkb延时相同。

通过分析不难看出,整个数据从发送到接收的过程需要经历连续的两个时钟沿,也就是说,如果要使系统能正常工作,就必须在一个时钟周期内让信号从发送端传输到接收端。

如果信号的传输延迟大于一个时钟周期,那么当接收端的第二个时钟沿触发时,就会造成数据的错误读取,因为正确的数据还在传输的过程中,这就是建立时间不足带来的时序问题。

目前普通时序系统的频率无法得到进一步提升的原因就在于此,频率越高,时钟周期越短,允许在传输线上的延时也就越小,200-300MHz已经几乎成为普通时序系统的频率极限。

《DDR4高速并行总线的信号完整性仿真分析》范文

《DDR4高速并行总线的信号完整性仿真分析》篇一一、引言随着科技的快速发展,电子系统的数据传输速率和数据处理能力需求不断提高。

在众多数据传输技术中,DDR4(第四代双倍速率动态随机存取存储器)以其高速并行传输的特点被广泛应用。

然而,随着数据传输速率的增加,信号完整性的问题变得日益突出。

因此,对DDR4高速并行总线的信号完整性进行仿真分析显得尤为重要。

本文将详细探讨DDR4高速并行总线的信号完整性仿真分析的方法和结果。

二、DDR4高速并行总线概述DDR4是一种同步动态随机存取存储器,其数据传输速率远高于前几代产品。

它采用并行传输的方式,通过多条数据线同时传输数据,大大提高了数据传输效率。

然而,随着数据传输速率的增加,信号的衰减、反射、串扰等问题也逐渐凸显出来,影响了信号的完整性。

三、信号完整性仿真分析方法为了确保DDR4高速并行总线能够稳定、高效地传输数据,我们采用了信号完整性仿真分析的方法。

这种方法通过对总线系统进行建模,模拟实际工作情况下的信号传输过程,从而预测和分析可能出现的信号完整性问题。

1. 建模与仿真:首先,我们根据DDR4总线的实际结构和工作原理,建立了详细的物理模型。

然后,利用仿真软件对模型进行仿真,模拟信号在总线上的传输过程。

2. 信号衰减分析:在仿真过程中,我们重点关注信号的衰减情况。

通过分析信号在传输过程中的幅度变化,我们可以了解信号的衰减程度和原因。

3. 反射与串扰分析:除了信号衰减外,我们还关注信号的反射和串扰问题。

通过仿真分析,我们可以找出反射和串扰的来源,并采取相应的措施进行优化。

4. 时序分析:时序是高速总线设计中另一个关键因素。

我们通过仿真分析时序参数,确保数据的正确传输和接收。

四、仿真结果与分析通过仿真分析,我们得到了以下结果:1. 信号衰减:在高速传输过程中,信号的衰减是不可避免的。

然而,通过优化电路设计和采用适当的匹配措施,我们可以有效地减小信号的衰减程度。

高速数字电路设计中的时序分析方法

高速数字电路设计中的时序分析方法在高速数字电路设计中,时序分析方法是非常重要的一项工作。

时序分析主要是指在设计数字电路时,需要对电路中各个信号的传输时间进行准确的分析,以确保电路的正常工作和稳定性。

时序分析通常包括两个方面:时序约束的设置和时序分析工具的使用。

首先,时序约束的设置是时序分析的第一步。

时序约束是指在设计数字电路时,对各个输入信号和输出信号的传输时间做出的要求。

时序约束需要考虑到电路中各个逻辑门的延迟时间、传输线的延迟时间以及时钟信号的时间间隔等因素。

通过合理设定时序约束,可以有效地防止信号冲突和时序问题,确保电路的正常运行。

其次,时序分析工具的使用是时序分析的关键。

时序分析工具通常是指一些专门用于分析数字电路时序的软件,如时序仿真工具、时序分析器等。

通过这些工具,设计师可以快速准确地分析电路中各个信号的传输时间,检测潜在的时序问题并进行优化。

时序分析工具还可以帮助设计师通过仿真等方式验证电路的正确性,提高设计的可靠性和稳定性。

在使用时序分析工具时,设计师需要注意一些关键点。

首先,需要准确地进行信号传输路径的分析,确定信号从输入到输出的传输时间。

其次,需要合理设置时钟信号的频率和相位,以确保电路在正确的时钟信号下正常工作。

另外,还需要分析时序违反等问题,及时发现和修复潜在的时序问题。

总的来说,时序分析方法在高速数字电路设计中起着至关重要的作用。

通过合理设置时序约束和有效使用时序分析工具,设计师可以确保电路在高速工作时不会出现时序问题,提高设计的可靠性和稳定性。

因此,设计师需要不断学习和掌握时序分析方法,以应对日益复杂的数字电路设计挑战。

高速通信系统中的时钟与同步技术

高速通信系统中的时钟与同步技术在高速通信系统中,时钟与同步技术是至关重要的组成部分。

时钟和同步技术的精准性和稳定性直接影响了通信系统的性能和数据传输的可靠性。

本文将从时钟和同步技术的基本概念出发,探讨在高速通信系统中时钟与同步技术的应用及其重要性。

首先,时钟在通信系统中的作用不可忽视。

时钟信号是指导数据传输和处理的时间基准,是整个系统运行的“心脏”。

在高速通信系统中,数据传输的速度非常快,传输的数据量也非常大,时钟信号的同步性和准确性对于数据的传输和处理至关重要。

如果时钟信号不同步或者不准确,就会导致数据传输失真、丢失或者乱序,从而影响通信系统的性能和稳定性。

其次,同步技术在高速通信系统中的重要性也不可低估。

在多个设备之间进行数据传输时,各个设备之间的时钟信号必须保持同步,以确保数据的正确传输和处理。

同步技术可以通过各种方法来实现,比如外部时钟同步、内部时钟同步、自适应时钟同步等。

通过同步技术的应用,可以有效地避免数据传输中出现的时延、抖动等问题,提高通信系统的性能和可靠性。

在高速通信系统中,时钟与同步技术的选择和设计需要根据具体的应用场景和需求来确定。

不同的通信系统可能需要不同精度和稳定性的时钟信号,也可能需要不同的同步技术来实现设备之间的协同工作。

因此,在设计和部署高速通信系统时,需要综合考虑时钟与同步技术的选择和应用,以确保系统的高效运行和数据传输的可靠性。

总的来说,时钟与同步技术在高速通信系统中扮演着至关重要的角色。

精准和稳定的时钟信号以及有效的同步技术是保障通信系统性能和数据传输可靠性的关键。

只有在时钟与同步技术得到合理应用和有效管理的前提下,高速通信系统才能实现高效、稳定、可靠的数据传输和处理。

希望本文对时钟与同步技术在高速通信系统中的重要性有所启发,也希望读者能够在实际应用中加以重视和应用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

同步系统的时序分析关于高速信号的时序分析,主要针对两种最常见的同步时序系统:共同时钟同步系统与源同步系统。

共同时钟同步原理及时序分析所谓共同时钟,就是在数据传输过程中,驱动端和接受端共享一个时钟,而这个时钟是由外部的一个器件提供,并且是同一个缓冲器输出的同相位时钟信号。

如图1所示:图1:共同时钟拓扑结构OSC提供时钟输入,CLK_BUFFER则分兵分两路把时钟信号分别输出为CLK_A和CLK_ B到驱动端和接收端,暂时不考虑时钟A和B在Buffer内部的Skew与在PCB板上由于走线长度不统一(当然也包括时钟信号接收端的负载不同)所造成的总的Skew,即我们认为时钟A和B在理想状态下同时到达了TRA NS和RECEIVE。

当CLK_B到达TRA NS后,在第一个时钟的上升沿,TRA NS会将数据Dt锁存到Qt等待输出,直到Qt输出电平达到有效参考电平Vmeas (通常是高电平的一半左右),这段时间我们就称之为驱动端数据信号的Tco。

Qt输出数据信号,通过总线传输到RECEIVE的Dr,在CLK_A的第二个时钟上升沿到来之前把数据送至芯片组内部。

不难看出,如果要使得系统正常工作,必须在一个时钟周期内让数据信号从驱动端发送到接收端,即理论上图1中的Qt到Dr的斜线通道的传输延时要小于一个时钟周期。

如果传输延时大于一个时钟周期,则接收端的第二个CLK信号的上升沿到来时,正确的数据还在传输过程中,就会导致由于数据信号建立时间不足而导致错误的发生。

这就是接收端的数据对建立时间的要求。

上述分析得出结果就是数据信号要提前CLK_A的第二个上升沿到来,那么要提前多少呢?这就要满足接收端的setup time。

这就要求传输线尽可能地短,但是太短的传输线又带来另一个问题,就是如果数据信号提前CLK_A的第二个上升沿太多的时间,那么时钟的上升沿对数据信号进行锁存的时候,数据信号没有足够的hold on time来保证被正确地采样,同样也会导致数据出错。

综上所述,共同时钟的时序要求就是:数据信号传输线不能太长或者太重,太长导致数据来得太慢,接收端没有足够的数据建立时间;当然数据信号传输线也不能太短,太短导致数据信号提前接收端时钟的第二个上升沿太多,没有足够的数据保持时间。

这就是共同时钟的一个最重要的时序要求。

在实际的计算中,我们还会考虑到CLK_BUFFER内部的时钟固定偏斜,即CLK_A和CLK_B 的Tco之间的差值,时钟抖动Jitter,还需要控制时钟信号A和B在PCB板上的传输延时要尽可能相等,要对他们做等长,并且走线要一致。

Tcycle:时钟的周期Tco_clkb:时钟B在CLK_BUFFER内部从CLK_IN开始到CLK_B输出有效延时Tflt_clkb:时钟B在PCB板上的飞行时间,即从CLK_BUFFER输出有效电平到TRANS接收到的CLK信号达到有效电平Tco_data:TRANS中数据从CLK_B输入TRA NS开始到寄存器输出数据到达有效电平的延时Tflt_data:数据信号在PCB板上的飞行时间,从TRANS输出有效电平开始到RECEIVE接收到数据信号的延时Tco_clka: 时钟A在CLK_BUFFER内部从CLK_IN开始到CLK_A输出有效延时Tflt_clka:时钟A在PCB板上的飞行时间,即从CLK_BUFFER输出有效电平到RECEIVE接收到的CLK信号达到有效电平Jitter:接收端RECEIVE的时钟抖动Tsetup:数据的建立时间Tsetup margin:建立时间裕量Thold:数据的保持时间Thold margin:保持时间裕量图2:共同时钟数据建立时序分析第一个输入时钟开始到数据接收的总延时为Tdata_delay:Tco_clkb+Tflt_clkb+Tco_data+Tflt_data接收时钟CLK_A下一个时钟周期的总的延时为Tclk_delay:Tcycle+Tco_clka+Tflt_clka再加上建立时间、建立裕量与抖动的时间可以得出如下计算公式Tdata_delay+Tsetup+Tsetup margin+Tjitter=Tclk_delay因为要保证Tsetup margin>0所以得出:Tclk_delay-(Tdata_delay+Tsetup+Tjitter)>0代入Tdata_delay和Tclk_delay的关系式Tcycle+Tco_clka+Tflt_clka-(Tco_clkb+Tflt_clkb+Tco_data+Tflt_data+Tsetup+Tjitter)>0为了保证最恶劣的结果都能满足条件,我们把上式中前面的两个参数Tco_clka和Tflt_clka取最小值,把式中括号内的参数Tco_clkb、Tflt_clkb、Tco_data、Tflt_data都取最大值,Jitter取正值。

得到如下的关系式:Tcycle+Tco_clka_min+Tflt_clka_min-(Tco_clkb_max+Tflt_clkb_max+Tco_data_max+Tflt_data_ma x+Tsetup+Tjitter)>0化简得到:Tcycle+[Tco_clka_min+Tflt_clka_min-(Tco_clkb_max+Tflt_clkb_max)]-(Tco_data_max+Tflt_da ta_max+Tsetup+Tjitter)>0而上式中的Tco_clka_min+Tflt_clka_min-(Tco_clkb_max+Tflt_clkb_max)=Tskew,即为CLK_ A和CLK_B的总偏斜。

总偏斜分为器件内部固定偏斜与PCB走线造成的偏斜两部分。

器件内部的固定偏斜为Tco_clka_min-Tco_clkb_max,这个参数是固定的PCB走线造成的偏斜为Tflt_clka_min-Tflt_clkb_max,这个参数是可调的,单从建立时间来说,我们希望这个值越大越好。

上式中的后面的参数还有一个参数Tflt_data_max是可调的,但从建立时间来说,我们希望这个值越小越好,即Data的走线越短越好,接收端的负载越轻越好。

下面再来分析一下保持时间的时序要求图3:共同时钟数据保持时序分析同样,得出两组方程式CLK_A的延时为:Tclka_delay=Tco_clka+Tflt_clka 注意这里的方程式与建立时间的不同,少了一个Tcycle,因为在数据接收端的参考时钟是第二个上升沿数据延时为:Tdata_delay:Tco_clkb+Tflt_clkb+Tco_data+Tflt_data保持时间、保持时间裕量、抖动的关系式为:Tdata_delay=Tclka_delay+Thold+Thold margin+Tjitter同样要保证Thold margin>0所以得出如下的关系式:Tdata_delay-(Tclka_delay+Thold+Tjitter)>0代入上述方程得到:Tco_clkb+Tflt_clkb+Tco_data+Tflt_data-(Tco_clka+Tflt_clka+Thold+Tjitter)>0为了满足最坏的条件,上式中前面的参数Tco_clkb、Tflt_clkb、Tco_data、Tflt_data全部取最小值,而后面的参数Tco_clka和Tflt_clka要取最大值,得到如下的关系:Tco_clkb_min+Tflt_clkb_min+Tco_data_min+Tflt_data_min-(Tco_clka_max+Tflt_clka_max+Thold+T jitter)>0化简得到:Tco_clkb_min+Tflt_clkb_min-(Tco_clka_max+Tflt_clka_max)+Tco_data_min+Tflt_data_min-(Thold+Tjitter)>0上式中Tco_clkb_min-Tco_clka_max为CLK_BUFFER内部的时钟偏斜,是固定的。

Tflt_clkb_min-Tflt_clka_max是PCB板上布线所产生的时钟偏斜,我们希望这个结果越大越好同时希望Tflt_data_min越大越好,负载越重越好。

与建立时序分析时正好相反。

综合建立时序与保持时序,得出如下两组关系式:Tcycle+[Tco_clka_min+Tflt_clka_min-(Tco_clkb_max+Tflt_clkb_max)]-(Tco_data_max+Tflt_data _max+Tsetup+Tjitter)>0Tco_clkb_min+Tflt_clkb_min-(Tco_clka_max+Tflt_clka_max)+Tco_data_min+Tflt_data_min-(Tho ld+Tjitter)>0其中有几个数据是可调的,即(Tflt_clka_min-Tflt_clkb_max)、(Tflt_clkb_min-Tflt_clka_max)、Tflt_data_max、Tflt_data_min,如果保证时钟走线延时相等,则(Tflt_clka_min-Tflt_clkb_max)=0、(Tflt_clkb_min-Tflt_clka_max)=0,要使得上述两组不等式同时成立,必须保证Tflt_data值在一定的区间内。

若这种情况下方程式无解,则必须要考虑调整CLK_A和CLK_B的飞行时间。

共同时钟向源同步时钟的演变及时序分析接下来对共同时钟做进一步的改进,从正常的共同时钟系统来看,我们希望CLK_BUFFER出来的两根CLK信号到驱动端和接收端的飞行时间尽可能相等,因为这样有助于我们进行时序计算,从而进行走线约束。

但是发现,当数据信号长度被约束在一个时钟周期的延时里,如果数据信号的走线一定,要想提高系统时钟的频率,那么势必降低了系统的时钟裕量,从而要求数据信号走线延时降低。

当达到一定的条件时候,再上升系统时钟频率,建立时序与保持时序的不等式的结果将是无解。

那么出现这种情况怎么办呢?上述分析也提到了,要考虑调整CLK_A和CLK_B的飞行时间,来满足裕量。

从建立裕量不等式来看,我们希望(Tflt_clka_min-Tflt_clkb_max)值越大越容易满足要求,而从保持时序不等式来看,又希望(Tflt_clkb_min-Tflt_clka_max)值越大越好。

这是一对矛盾的表达式,那么我们是否有其他的方法来同时满足接收端得建立时序要求和保持时序的要求?我们可以暂时控制其中一个表达式,让其最大化满足建立时序和保持时序其中一个要求,然后再想办法满足另一个时序。