计算机系统结构winDLX流水线实验报告

体系结构windlx流水线实验报告

实验一基本实验----by 王琳PB072104321. 实验目的:1)熟悉计算机流水线基本概念2)了解DLX基本流水线的各段的功能3)了解各种不同指令在流水线中的实际流动情况4)对流水线做性能分析5)了解影响流水线效率的因素——数据相关、结构相关、控制相关,了解相关的种类6)了解解决数据相关的方法2. 实验平台:WinDLX仿真器WinDLX简介:●是一个图形化、交互式的DLX流水线仿真器。

●可以装入DLX汇编语言程序,然后单步,设断点或是连续执行该程序.●CPU的寄存器,流水线,I/O和存储器都可以用图形表示出来●提供了对流水线操作的统计功能.●可以装载文件名为*.s的文件.●要求的硬件平台是IBM-PC兼容机.●WinDLX是一个Windows应用程序,运行DOS3.3以上和Windows3.0以上的操作系统.●WinDLX软件包中带有说明文件及教程,可以供使用者进一步了解仿真器的使用方法和DLX处理器的原理.大家再进行实验前应该仔细阅读这些文档.3. 实验内容:1)在仿真器上分别运行单条指令:Load指令、Store指令、分支指令、寄存器ALU指令、立即数ALU指令,记录它们在流水线中的执行情况●Lw:观察此流水线时空图,可以发现:转移指令引起的延迟仅为1 clocks,另2 stalls 是trap指令引起的,这个执行结果似与不采用forwarding技术的前提相违,只能理解为对于无条件的转移指令,新的PC值在EX阶段即已被写入。

●Sw:●Beqz:由此图可见,对于分支指令,总是用not-taken的策略来处理,并且也认为新的PC值也在EX阶段即已被写入,且cond条件也在EX段被算出(这显然是一个极不合理的假设,究竟为何分支指令的延迟为1 stall有待进一步探究)●寄存器ALU指令●立即数ALU指令2)仿真器运行一段无相关的程序,记录它的执行情况,计算流水线的加速比、吞吐率与效率。

系统结构-流水线工作分析报告

系统结构-流水线工作分析报告第一篇:系统结构-流水线工作分析报告《计算机系统结构课内实验》实验报告一、实验目的及要求1、加深对计算机流水线基本概念的理解;2、理解MIPS结构如何用5段流水线来实现,理解各段的功能和基本操作;3、加深对数据冲突、结构冲突的理解,理解这两类冲突对CPU 性能的影响。

4、进一步理解解决数据冲突的方法,掌握如何应用定向技术来减少数据冲突引起的停顿。

加深对计算机流水线基本概念的理解;二、实验环境采用指令级和流水线操作级模拟器WinDLX;三、实验内容1、用WinDLX模拟器进行结构相关的分析①生成汇编程序structure_d.s。

用WinDLX模拟器运行该程序。

②通过模拟,找出存在结构相关的指令对,以及导致结构相关的部件。

③记录由结构相关引起的暂停时钟周期数,计算暂停时钟周期数占总执行周期数的百分比。

2、用WinDLX模拟器进行数据相关分析①添加data.s程序。

②通过Configuration菜单中的选项,设定在不采用定向技术的情况下,用WinDLX模拟器运行程序data_d.s。

记录数据相关引起的暂停时钟周期数以及程序执行的总时钟周期数,计算暂停时钟周期数占总执行周期数的百分比。

③在采用定向技术的情况下,用WinDLX模拟器再次运行程序data_d.s。

记录数据相关引起的暂停时钟周期数以及程序执行的总时钟周期数,计算暂停时钟周期数占总执行周期数的百分比。

3、用WinDLX模拟器分析指令调度①生成schedule-before.s及schedule-after.s程序。

②通过Configuration菜单中的选项,将除法单元数设置为3,将加法﹑乘法﹑除法的延迟设置为3个时钟周期。

③用WinDLX模拟器运行调度前的程序schedule-before.s。

记录程序执行过程中各种相关发生的次数以及程序执行的总时钟周期数。

④用WinDLX模拟器运行调度后的程序schedule-after.s,记录程序执行过程中各种相关发生的次数以及程序执行的总时钟周期数。

流水线实验报告

流水线实验报告一、实验目的本次实验旨在探究流水线技术在计算机体系结构中的应用,并了解流水线的工作原理与效果。

通过对流水线的实验,掌握流水线操作的过程和相关概念,并通过实践了解其对计算机性能的提升作用。

二、实验器材与软件环境实验使用的器材为一台配有Intel Core i7处理器的计算机。

软件环境为Windows 10操作系统,使用C语言编译器进行代码编写和实验运行。

三、实验内容1. 流水线概述流水线是一种用于提高计算机处理器效率的技术。

它将任务划分为多个阶段,使得每个阶段都能并行地处理不同的任务。

通过将多个任务拆分并在不同的阶段同时进行,可以显著提高计算机处理速度。

2. 流水线原理流水线工作原理如下:1) 将任务划分为多个子任务,并在不同的阶段上并行执行。

2) 每个阶段的任务之间通过专门的寄存器传递数据。

3) 每个阶段的任务完成后,将结果写入寄存器,供下一个阶段使用。

4) 流水线的效果取决于各个阶段的任务执行时间,如果存在某个阶段的任务耗时较长,则可能导致整个流水线效率下降。

3. 流水线的实现实验中我们使用C语言编写一段简单的代码来模拟流水线的实现过程。

我们通过将输入的整数加1后输出,来模拟流水线的工作状态。

cinclude <stdio.h>int main() {int input[5] = {1, 2, 3, 4, 5};int output[5];int i;for (i = 0; i < 5; i++) {output[i] = input[i] + 1;}for (i = 0; i < 5; i++) {printf("%d\n", output[i]);}return 0;}上述代码将输入数组中的每个元素加1后,输出到屏幕上。

在这个过程中,我们可以将输入和输出视为流水线中的阶段,每个阶段都有固定的任务。

4. 实验结果与分析在实验中,我们输入数组为{1, 2, 3, 4, 5},运行结果如下:23456可以看到,实验结果符合我们的预期,每个输入元素都成功地加1后输出。

计算机系统结构实验三.

计算机系统结构实验实验三:DLX 流水线运行分析一、实验目的通过本实验,熟悉 WinDLX 模拟器的操作和使用,了解 DLX 指令集结构及其特点。

二、实验内容(1) 用 WinDLX 模拟器执行求阶乘程序 fact.s 。

执行步骤详见“WinDLX教程”。

这个程序说明浮点指令的使用。

该程序从标准输入读入一个整数,求其阶乘,然后将结果输出。

该程序中调用了 input.s 中的输入子程序,这个子程序用于读入正整数。

(2)输入数据“3”采用单步执行方法,完成程序并通过上述使用 WinDLX,总结 WinDLX的特点。

(3)注意观察变量说明语句所建立的数据区,理解 WinDLX 指令系统。

三、实验步骤1.双击 Code 图标,从左到右依次为代表存储器内容的三栏信息:地址 (符号或数字)、命令的十六进制机器代码和汇编命令。

点击主窗口中的 Execution 开始模拟。

按 F7 键开始执行。

这时,窗口中带有地址“$TEXT”的第一行变成黄色。

按下 F7 键,模拟就向前执行一步,第一行的颜色变成橘黄色,下一行变成黄色。

这些不同颜色指明命令处于流水线的哪一段。

命令“jalInputUnsigned”在 IF 段,“addi r1, r0, 0x1000”在第二段ID。

其他方框中带有一个“X”标志,表明没有处理有效信息。

2.再次按下 F7 键,代码窗口中的颜色会再改变,红色表明命令处入第三段“intEX”。

再按下 F7,在代码窗口中,黄色出现在更下面的位置,并且是唯一彩色行。

打开 Clock Cycle Diagram 窗口。

它显示流水线的时空图。

第一条命令正在 MEM 段,第二条命令在 intEX 段,第四条命令在 IF 段。

而第三条命令指示为“aborted”。

其原因是:第二条命令(jal)是无条件分支指令,但只有在第三个时钟周期, jal 指令被译码后才知道,这时,下一条命令 movi2fp 已经取出,但需执行的下一条命令在另一个地址处,因而,movi2fp 的执行应被取消,在流水线中留下气泡。

计算机系统结构实验报告要点

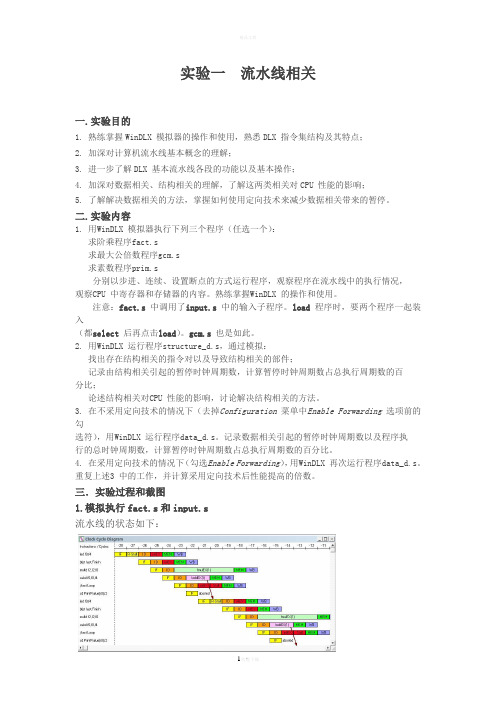

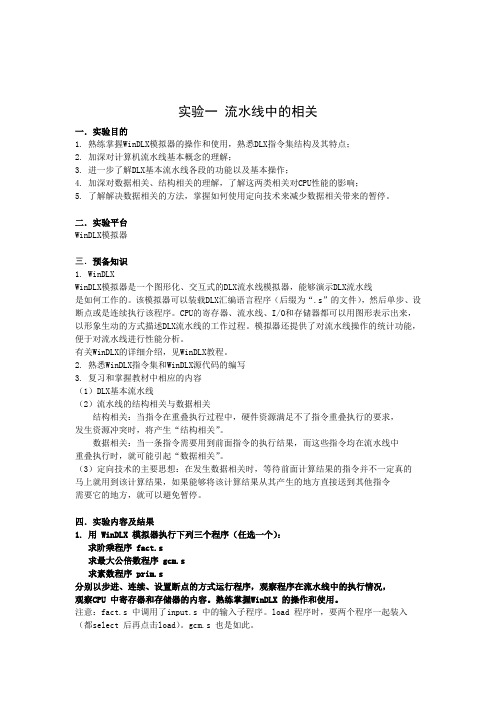

实验一流水线相关一.实验目的1. 熟练掌握WinDLX 模拟器的操作和使用,熟悉DLX 指令集结构及其特点;2. 加深对计算机流水线基本概念的理解;3. 进一步了解DLX 基本流水线各段的功能以及基本操作;4. 加深对数据相关、结构相关的理解,了解这两类相关对CPU 性能的影响;5. 了解解决数据相关的方法,掌握如何使用定向技术来减少数据相关带来的暂停。

二.实验内容1. 用WinDLX 模拟器执行下列三个程序(任选一个):求阶乘程序fact.s求最大公倍数程序gcm.s求素数程序prim.s分别以步进、连续、设置断点的方式运行程序,观察程序在流水线中的执行情况,观察CPU 中寄存器和存储器的内容。

熟练掌握WinDLX 的操作和使用。

注意:fact.s 中调用了input.s 中的输入子程序。

load 程序时,要两个程序一起装入(都select 后再点击load)。

gcm.s 也是如此。

2. 用WinDLX 运行程序structure_d.s,通过模拟:找出存在结构相关的指令对以及导致结构相关的部件;记录由结构相关引起的暂停时钟周期数,计算暂停时钟周期数占总执行周期数的百分比;论述结构相关对CPU 性能的影响,讨论解决结构相关的方法。

3. 在不采用定向技术的情况下(去掉Configuration 菜单中Enable Forwarding 选项前的勾选符),用WinDLX 运行程序data_d.s。

记录数据相关引起的暂停时钟周期数以及程序执行的总时钟周期数,计算暂停时钟周期数占总执行周期数的百分比。

4. 在采用定向技术的情况下(勾选Enable Forwarding),用WinDLX 再次运行程序data_d.s。

重复上述3 中的工作,并计算采用定向技术后性能提高的倍数。

三.实验过程和截图1.模拟执行fact.s和input.s流水线的状态如下:在执行求阶乘程序fact.s 之后,输入值5,查看寄存器的值为120,结果正确。

计算机系统结构winDLX流水线实验报告

计算机科学与技术学院《计算机体系结构》课程实验学号:班级:专业:学生姓名:年月日实验报告seqi r5,r3,10下面两条指令中,因为加法指令要读r1,而执行到此操作时乘法指令仍对r进行操作,因此出现了数据相关multu r1,r1,r4add r1,r1,r3图1 数据相关(2)控制相关:以图2中出现的控制相关为例下面两条指令中,因为第一条指令出现跳转指令时,存储指令的取指将作废,所以出现控制相关jal InputUnsignedsw PrintfValue(r3),r1图2 控制相关(3)结构相关:以图3中出现的结构相关为例下面两条指令中,因为当第二条乘法指令需要使用乘法器时,第一条乘法指令仍在使用乘法器,所以出现结构相关mult r2,r0,r0mult r3,r0,r0图3 结构相关3、主程序Variance.s的代码.data ;.data标识下面的数据放在数据区中;输入语句,指示你输入要求多少个数的方差Prompt: .asciiz "Please input An integer which is array's size value>0: ";输入语句,指示你输入要求方差的数PromptLast: .asciiz "Please input the integer :";输出格式,表示求出的方差按什么格式输出PrintfFormat: .asciiz "the Variance is : %g ";表示下面采用字对齐.align 2;求出方差存入r11中div r11,r2,r8output:;将方差存入Variance所指存储空间中sw Variance,r11;转换为双精度并输出lf f2,Variancecvti2d f0,f2sd Printf,f0addi r14,r0,PrintfPartrap 5 ;调用中断,格式化输出转化为标准输出over:trap 0 ;调用系统中断,0表示程序执行结束4、样例输出,以图4中数据为例输入需要求方差数的个数为4,4个数分别为3,5,6,2,输出结果为2图4 输出界面5、尽量减少和消除程序中出现的相关。

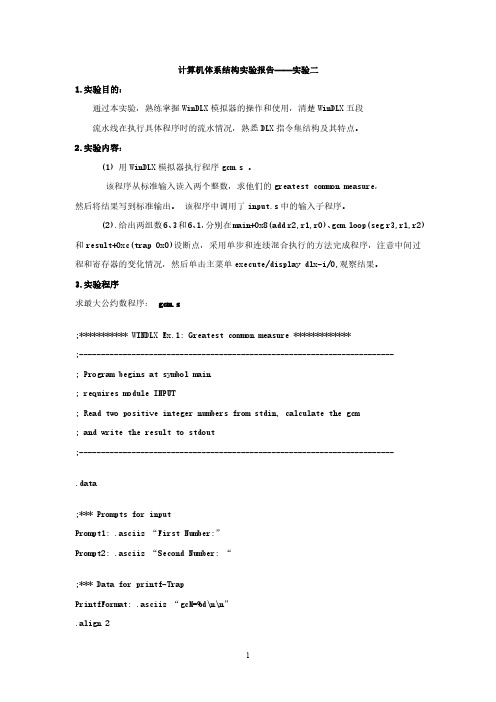

计算机体系结构实验报告——实验二

计算机体系结构实验报告——实验二1.实验目的:通过本实验,熟练掌握WinDLX模拟器的操作和使用,清楚WinDLX五段流水线在执行具体程序时的流水情况,熟悉DLX指令集结构及其特点。

2.实验内容:(1)用WinDLX模拟器执行程序gcm.s。

该程序从标准输入读入两个整数,求他们的greatest common measure,然后将结果写到标准输出。

该程序中调用了input.s中的输入子程序。

(2).给出两组数6、3和6、1,分别在main+0x8(add r2,r1,r0)、gcm.loop(seg r3,r1,r2)和result+0xc(trap0x0)设断点,采用单步和连续混合执行的方法完成程序,注意中间过程和寄存器的变化情况,然后单击主菜单execute/display dlx-i/0,观察结果。

3.实验程序求最大公约数程序:gcm.s;***********WINDLX Ex.1:Greatest common measure*************;------------------------------------------------------------------------;Program begins at symbol main;requires module INPUT;Read two positive integer numbers from stdin,calculate the gcm;and write the result to stdout;------------------------------------------------------------------------.data;***Prompts for inputPrompt1:.asciiz“First Number:”Prompt2:.asciiz“Second Number:“;***Data for printf-TrapPrintfFormat:.asciiz“gcM=%d\n\n”.align2PrintfPar:.word PrintfFormatPrintfValue:.space4.text.global mainmain:;***Read two positive integer numbers into R1and R2 addi r1,r0,Prompt1jal InputUnsigned;read uns.-integer into R1add r2,r1,r0;R2<-R1addi r1,r0,Prompt2jal InputUnsigned;read uns.-integer into R1Loop:;***Compare R1and R2seq r3,r1,r2;R1==R2?bnez r3,Resultsgt r3,r1,r2;R1>R2?bnez r3,r1Greaterr2Greater:;***subtract r1from r2sub r2,r2,r1j Loopr1Greater:;***subtract r2from r1sub r1,r1,r2j LoopResult:;***Write the result(R1)sw PrintfValue,r1addi r14,r0,PrintfPartrap5;***endtrap0该程序中调用了input.s中的输入子程序。

计算机体系结构实验报告

实验一流水线中的相关一.实验目的1. 熟练掌握WinDLX模拟器的操作和使用,熟悉DLX指令集结构及其特点;2. 加深对计算机流水线基本概念的理解;3. 进一步了解DLX基本流水线各段的功能以及基本操作;4. 加深对数据相关、结构相关的理解,了解这两类相关对CPU性能的影响;5. 了解解决数据相关的方法,掌握如何使用定向技术来减少数据相关带来的暂停。

二.实验平台WinDLX模拟器三.预备知识1. WinDLXWinDLX模拟器是一个图形化、交互式的DLX流水线模拟器,能够演示DLX流水线是如何工作的。

该模拟器可以装载DLX汇编语言程序(后缀为“.s”的文件),然后单步、设断点或是连续执行该程序。

CPU的寄存器、流水线、I/O和存储器都可以用图形表示出来,以形象生动的方式描述DLX流水线的工作过程。

模拟器还提供了对流水线操作的统计功能,便于对流水线进行性能分析。

有关WinDLX的详细介绍,见WinDLX教程。

2. 熟悉WinDLX指令集和WinDLX源代码的编写3. 复习和掌握教材中相应的内容(1)DLX基本流水线(2)流水线的结构相关与数据相关结构相关:当指令在重叠执行过程中,硬件资源满足不了指令重叠执行的要求,发生资源冲突时,将产生“结构相关”。

数据相关:当一条指令需要用到前面指令的执行结果,而这些指令均在流水线中重叠执行时,就可能引起“数据相关”。

(3)定向技术的主要思想:在发生数据相关时,等待前面计算结果的指令并不一定真的马上就用到该计算结果,如果能够将该计算结果从其产生的地方直接送到其他指令需要它的地方,就可以避免暂停。

四.实验内容及结果1. 用 WinDLX 模拟器执行下列三个程序(任选一个):求阶乘程序 fact.s求最大公倍数程序 gcm.s求素数程序 prim.s分别以步进、连续、设置断点的方式运行程序,观察程序在流水线中的执行情况,观察CPU 中寄存器和存储器的内容。

熟练掌握WinDLX 的操作和使用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

multu r1,r1,r4

add

r1,r1,r3

图 1 数据相关

(2)控制相关:以图 2 中出现的控制相关为例

下面两条指令中,因为第一条指令出现跳转指令时,存储指令的取指将

作废,所以出现控制相关

jal

InputUnsigned

sw

PrintfValue(r3),r1

6

图结构相关为例 下面两条指令中,因为当第二条乘法指令需要使用乘法器时,第一条乘

;.global 标识 main 可以被全局访问

main:

;将 Prompt 字符串首地址放入 r1 寄存器中

addi r1,r0,Prompt

;跳转向 InputUnsigned 标识的地址,调用 input 子函数读取

数组大小的值

jal

InputUnsigned

8

;将 input 函数读取的数放入寄存器中

3

5、了解影响流水线效率的因素 6、了解各类相关及解决方法

四、实验内容: 使用 WinDLX 模拟器,对 Variance.s 做如下分析:

(1) 分析 Variance.s 和 Input.s 输入顺序不同时产生的影响。 (2) 分析 Variance.s 中汇编语言含义,同时分析程序执行流程。 (3) 观察程序中出现的数据/控制/结构相关。指出程序中出现上述现 象的指令组合。 (4) 考察增加运算部件对性能的影响。 (5) 考察增加 forward 部件对性能的影响。 (6) 观察转移指令在转移成功和转移不成功时候的流水线开销。 注意:除(4)以外,加、乘、除部件都只有一个,本问题中所有部件延迟设置为: 加法:2 个延迟周期;乘法:5 个延迟周期;除法 19 个延迟周期。 五、实验器材(设备、元器件): IBM PC 兼容机 Windows 3.0 以上的操作系统

计算机科学与技术学院

《计算机体系结构》课程实验

学 号: 班 级: 专 业: 学生姓名:

年月 日

1

实验报告

学生姓名:

学 号:

时间: 地点:

实验课程名称:计算机体系结构

一、实验名称:流水线中的相关-求 n 个数的方差

二、实验原理:

1、WinDLX WinDLX 模拟器是一个图形化、交互式的 DLX 流水线模拟器,能够演示

一条指令所使用,从而产生数据相关; (3)控制相关:当程序执行到某个分支语句时,顺序执行的下一条语句将被

跳过而去执行分支语句中满足条件的那条指令,从而产生控制相关。

三、实验目的: 1、通过该模拟实验,进一步掌握和巩固流水线的基本知识; 2、初步掌握在特定体系结构下的汇编代码的编写和优化; 3、培养运用所学知识解决实际问题的能力 4、对流水线性能分析

法指令仍在使用乘法器,所以出现结构相关

mult

r2,r0,r0

mult

r3,r0,r0

图 3 结构相关

3、主程序 Variance.s 的代码

.data

;.data 标识下面的数据放在数据区中

;输入语句,指示你输入要求多少个数的方差

Prompt: .asciiz "Please input An integer which is array's size value>0: "

; .word 在存储器中顺序存放列出的字

PrintfPar:

.word PrintfFormat

;在存储区中空出相应大小的区域

Printf:

.space

8

Variance:

.space

8

PrintfValue: .space 1024

.text

;.text 标识下面的代码存放在代码区中

.global main

2、流水线执行过程: 指令执行的5个阶段

(1)取指令周期 (2)指令译码/读寄存器周期 (3)执行/有效地址计算周期 (4)存储器访问/分支完成周期 (5)写回周期

2

3、流水线中的相关: (1)结构相关:当某一条机器指令需要访问物理器件时,如加法器,此时加法

器正被另一条机器指令使用,从而产生结构相关; (2)数据相关:当某一条指令需要访问某个寄存器时,此时这个寄存器正被另

2、程序中出现的三种相关 (1)数据相关:以图 1 中出现的两个数据相关为例

下面两条指令中,因为第二条指令要读 r3,而执行到此操作时加载指令

5

仍对 r3 进行操作,因此出现了数据相关

lbu

r3,0(r2)

seqi r5,r3,10

下面两条指令中,因为加法指令要读 r1,而执行到此操作时乘法指令仍 对 r 进行操作,因此出现了数据相关

点击 Variance.s 点击 select 按钮 点击 Input.s 点击 select 按钮 点击 load 按钮 3、按 F7 键程序顺序执行观察 6 个子窗口的情况。 七、实验数据及结果分析: 1、先装入 Variance.s 再转入 Input.s 时,因为程序顺序执行,地址顺序符合程 序执行顺序,程序能够正确执行;顺序相反时,因为 Input.s 的地址高,而程序顺序 执行到 Input.s 时将没有正确的输入窗口,程序执行到输出结果时,也不会出现结 果

DLX 流水线是如何工作的。该模拟器可以装载 DLX 汇编语言程序(后缀为“.s”的

文件),然后单步、设断点或是连续执行该程序。CPU 的寄存器、流水线、I/O 和存

储器都可以用图形表示出来,以形象生动的方式描述 DLX 流水线的工作过程。模

拟器还提供了对流水线操作的统计功能,便于对流水线进行性能分析。

4

六、实验步骤及操作: 1、双击 WinDLX 图标运行 WinDLX。装入测试程序之前,先初始化 WinDLX 模拟器:点击 File 菜单中的 Reset all 菜单项,弹出一个“Reset DLX”对话框。然 后点击窗口中的“确认”按钮即可。 2、选择 File / Load Code or Data,按如下步骤操作,可将 Variance.s 和这两个 程序装入主存:

7

;输入语句,指示你输入要求方差的数

PromptLast: .asciiz "Please input the integer :"

;输出格式,表示求出的方差按什么格式输出

PrintfFormat: .asciiz "the Variance is : %g "

;表示下面采用字对齐

.align 2