一种采用新触发器的高速CMOS前置分频器

可编程分频器

高速CMOS 可编程分频器的研究与设计欧雨华 严利民(上海大学微电子研究与开发中心,上海 200072)来源:微计算机信息摘要:本文通过对CMOS 可编程分频器原理的分析与研究,提出了一种新的可实现任意分频的可编程分频器结构,这种结构大大提高了可编程分频器的输入带宽,同时功耗不大,抗干扰能力强,可适用于锁相环、频率综合器的设计中。

该设计在宏力CMOS 0.18um 工艺下通过仿真和验证,输入频率可以达到3.3G Hz 。

关键词:可编程分频器 CMOS 0.18um 工艺 高输入带宽 锁存器1. 介绍可编程高带宽分频器在锁相环、频率综合器、FM 调制器等方面有着广泛的应用[1]。

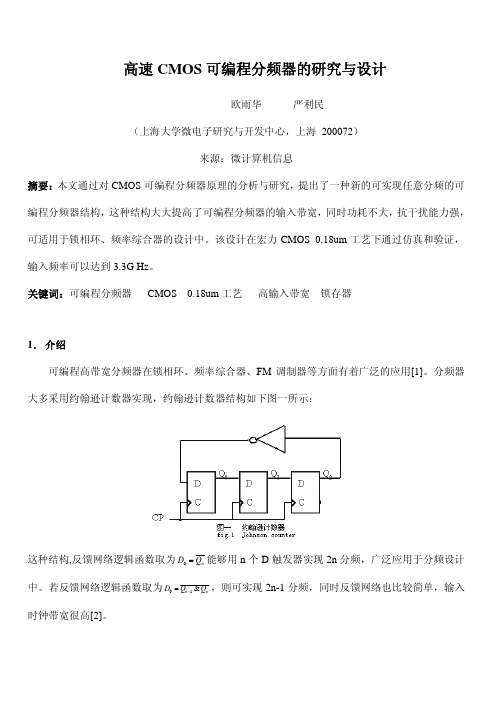

分频器大多采用约翰逊计数器实现,约翰逊计数器结构如下图一所示:这种结构,反馈网络逻辑函数取为0n D Q =能够用n 个D 触发器实现2n 分频,广泛应用于分频设计中。

若反馈网络逻辑函数取为01&n n D Q Q −=,则可实现2n-1分频,同时反馈网络也比较简单,输入时钟带宽很高[2]。

根据以上的分析可知,实现任意分频的可编程分频器的结构如下图二所示。

这种结构可编程分频器就是利用图二所示的选择器来控制反馈网络函数为n Q 、1&n n Q Q −、1n Q −或21&n n Q Q −−,依此类推,这种结构用N 个D 触发器可以实现2至2N 任意分频。

但是,使用这种结构,反馈网络选择器MUX 逻辑将设计得相当复杂,反馈组合逻辑延时t p 将严重制约着输入带宽[3],早期很多人花了很多精力去研究设计这个MUX ,以求尽量提高可编程分频器的输入带宽,但效果不明显。

2. 任意分频的可编程分频器结构上图二结构,由于组合逻辑的延时过大而限制了整个分频器的最高输入时钟频率[3]。

本文提出一种方法,将D 触发器打开成两个单个锁存器[3],同时将图二中选择器(逻辑复杂、延迟长)拆分成逻辑简单、延迟短的选择器整合到锁存器之间,大大提高分频器输入带宽[2]。

cd40110芯片工作原理

cd40110芯片工作原理

CD40110是一种CMOS逻辑芯片,通常用于数字电路中的计数器

和频率分频器。

它包含了四个独立的数字计数器,每个计数器都可

以独立地配置为向上计数、向下计数或者自由运行。

它还可以通过

外部时钟信号来控制计数速度,因此非常适合用于时序控制和频率

分频的应用。

CD40110芯片的工作原理主要基于内部的逻辑门电路和触发器。

当外部时钟信号输入时,芯片内部的计数器会根据时钟信号的边沿

触发进行计数。

当计数器达到设定的最大值时,它会重新从零开始

计数,从而实现循环计数的功能。

此外,CD40110还具有预置功能,可以通过外部输入信号对计

数器进行预置,从而实现特定的计数起点。

这使得它在数字系统中

的定时和控制应用中非常有用。

总的来说,CD40110芯片的工作原理是基于内部逻辑门和触发

器的组合,通过外部时钟信号和预置信号来实现计数器的计数和控

制功能,从而在数字电路中发挥重要作用。

精品文档-扩频通信技术及应用(第二版)(暴宇)-第8章

第8章 扩频系统的方案设计(二) 随后模式控制电平被设置为低电平, 计数器被预设为它 们具体的编程值, 再次重复以上过程。 这样, 总的可编程 分频比为M=N×P+A, P和P+1分别代表模式电平分别为高和低 电平时的双模分频比, A是“÷A计数器”的分频比, 它在 这里起吞食计数器的作用, N是“÷N计数器”的分频比, 它在这里起主程序分频器的作用。

第8章 扩频系统的方案设计(二)

8.1.2 1. 目前用得最多的DDS芯片是AD公司的AD985X系列, 该系

列从AD9850到AD9858, 型号一应俱全, 性能和功能有所不 同。 AD9850~AD9854为纯DDS芯片,结构基本相同, 性能略 有差异。 这些芯片已推出好几年了, 所以价格适中, 应用 较广。 表8-1对这些芯片作了简单比较。

第8章 扩频系统的方案设计(二)

第8章 扩频系统的方案设计(二)

7、 8: φR、 φV鉴相器输出端。 鉴相器(PD)的 输出可由环路误差信号组合输出, 该鉴相器是具有鉴频功能 的数字式鉴相器。 参考频率源的频率经参考分频器分频后送 入PD, 作为鉴相器的参考频率fR; 压控振荡器VCO的输出频 率fo, 经吞脉冲程序分频器分频后பைடு நூலகம்fV也送到PD, 作为鉴相 频率。

第8章 扩频系统的方案设计(二)

fR和fV在PD中进行鉴频鉴相, 如果fV>fR或fV的相位超前 于fR相位, jV输出一负脉冲, 脉冲宽度与超前相位成正比, 而jR基本保持高电平; 如果fV<fR或fV的相位滞后于fR 相位,jR输出一负脉冲, 脉冲宽度与滞后相位成正比, 而jV 基本保持高电平; 若fV=fR, jV和jR相位相同, 两者都保 持高电平, 且各自输出非常窄的同相负脉冲。

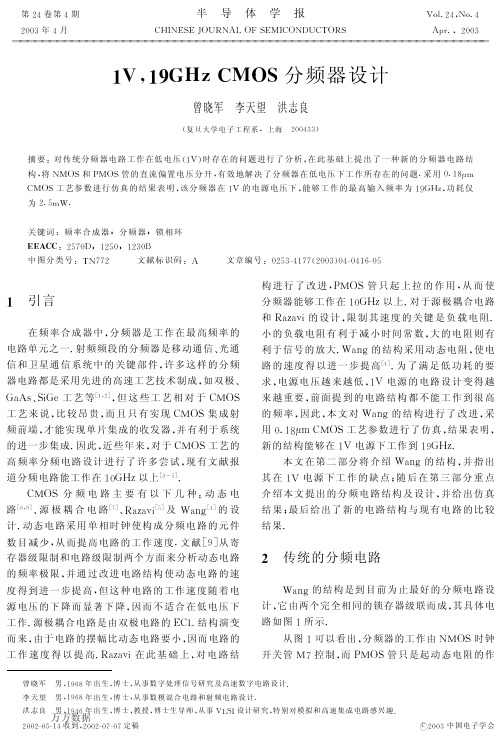

1V19GHz CMOS分频器设计

F ’ F H G I JKL MN O分频器设计

曾晓军 李天望 洪志良

复旦大学电子工程系 ’ 上海 P ! ) ) " * * Q

摘要 R对传统分频器电路工作在低电压 P 时存在的问题进行了 分 析 ’ 在此基础上提出了一种新的分频器电路结 = #Q 构’ 将 (71/和 S 有效地解决了分频器在低电压下工作所存在的问题 & 采用 ) T = @ 71/管的直流偏置电压分开 ’ U V 该分频器在 = 能够工作的最高输入频率为 = 功耗仅 > ’ # 的电源电压下’ W ,X + 71/工艺参数进行仿真的 结 果 表 明 ’ 为! T B VY& 关键词 R 频率合成器 Z 分频器 Z 锁相环 R! B C ) Z= ! B ) Z= ! * ) [ [ \ L L 8 ] 中图分类号 R9 文献标识码 R4 C ! (C 文章编号 R) ! B * A " = C C P ! ) ) * Q ) " A ) " = ? A ) B

*! ’ ( )

" $’ %" $ # + , . , / 0 12 ( 3 ( 2 , +4 5 6 5 7 5 ) 1 &

方 便 地 构 成 分 频 器< 其 工 作 原 理 与 R# / )的 结 构 相 似< 不 同 的 是 图 E中 时 钟 开 关 管 = >?8和 O>?8 采用不同的直流偏置 < 有效地解决了图 !电路在 ! J 电源 下的偏 置问 题 < 从而大大提高了分频器的工作 速度 * 在图 E中 < 通 过 合 理 设 计 电 阻 及 电 容 的 值< 以 及外加的偏置电压 S 就可以控制 = < T U8 = >?8管的

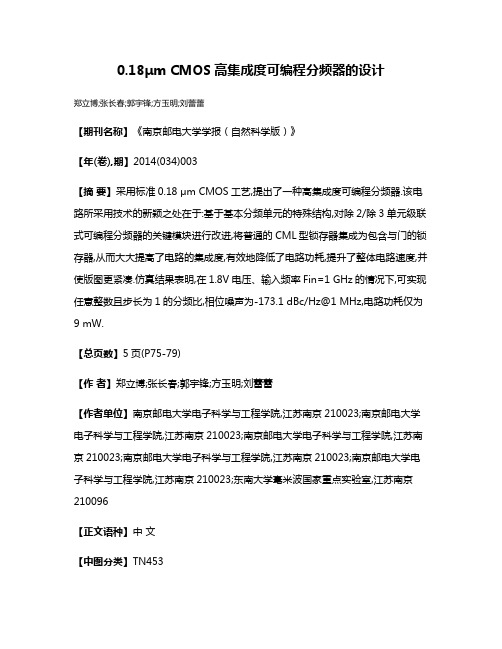

0.18μm CMOS高集成度可编程分频器的设计

0.18μm CMOS高集成度可编程分频器的设计郑立博;张长春;郭宇锋;方玉明;刘蕾蕾【期刊名称】《南京邮电大学学报(自然科学版)》【年(卷),期】2014(034)003【摘要】采用标准0.18 μm CMOS工艺,提出了一种高集成度可编程分频器.该电路所采用技术的新颖之处在于:基于基本分频单元的特殊结构,对除2/除3单元级联式可编程分频器的关键模块进行改进,将普通的CML型锁存器集成为包含与门的锁存器,从而大大提高了电路的集成度,有效地降低了电路功耗,提升了整体电路速度,并使版图更紧凑.仿真结果表明,在1.8V电压、输入频率Fin=1 GHz的情况下,可实现任意整数且步长为1的分频比,相位噪声为-173.1 dBc/Hz@1 MHz,电路功耗仅为9 mW.【总页数】5页(P75-79)【作者】郑立博;张长春;郭宇锋;方玉明;刘蕾蕾【作者单位】南京邮电大学电子科学与工程学院,江苏南京210023;南京邮电大学电子科学与工程学院,江苏南京210023;南京邮电大学电子科学与工程学院,江苏南京210023;南京邮电大学电子科学与工程学院,江苏南京210023;南京邮电大学电子科学与工程学院,江苏南京210023;东南大学毫米波国家重点实验室,江苏南京210096【正文语种】中文【中图分类】TN453【相关文献】1.0.18μm CMOS 1:20分频器电路设计 [J], 邢立冬;朱刘松;蒋林2.基于0.18μm CMOS标准单元的可编程分频器设计 [J], 何小虎;胡庆生3.基于0.18μm CMOS工艺的ZigBee分频器设计 [J], 蒋雪琴4.应用于DVB-T的0.18μm CMOS工艺数字可编程分频器芯片设计 [J], 景永康;陈莹梅;章丽5.0.18μm CMOS PLL频率综合器中可编程分频器的设计与实现 [J], 何小虎;胡庆生;肖洁因版权原因,仅展示原文概要,查看原文内容请购买。

6GHz新型高速低功耗分频器

图的面积和复杂性;而基于 D 触 发 器 的 多 模 分 频 器 结 构 简 单 ,工 作 频 率 范 围 较 宽 ,被 广 泛 应 用 于 时 钟 频 率小于20GHz的锁相环频率合成器中 . [3]

文中提出了一种基于典型 D 触发器的改进型 二分频单元,并在此 基 础 上 构 建 了 一 种 新 型 可 编 程 分 频 器 .在 响 应 较 高 频 率 的 前 提 下 ,该 分 频 器 结 构 可 以大幅度的降低功耗和面积开销.

收 稿 日 期 :2011-02-13;修 回 日 期 :2011-03-18 基 金 项 目 :国 家 自 然 科 学 基 金 项 目 (61070036)

2

微电子学与计算机

2011 年

元 结 构 ,如 图 2 所 示 .为 了 提 高 其 对 输 入 时 钟 的 响 应 频率和实现分频模 数 的 变 化,采 取 了 一 系 列 的 改 进 措施.

6 GHz Novel High-Speed Low-Power Frequency Divider

ZUO Hong-jian,GUO Yang,MA Zhuo

(School of Computer Science,National University of Defense Technology,Changsha 410073,China)

径上的传播延时,增 加 二 分 频 单 元 可 以 响 应 的 最 大

图 3 基 于 双 模 分 频 器 的 吞 脉 冲 分 频 器

基于双模分频器级联组成的多模分频器如图4 所示,它的可编程 部 分 一 般 由 基 本 的 模 2/3 分 频 单 元组成,每个模2/3分频单 元 包 含 4 个 D 触 发 器 和 3个与门,若要实现 N 位 可 编 程,至 少 需 要 4N 个 D 触发器;这样的实现 方 式 会 大 大 增 加 电 路 的 面 积 和 功耗;此外,在不增 加 扩 展 电 路 的 前 提 下,这 种 分 频 器 的 分 频 系 数 只 能 在 2N ~2N+1-1 之 间 取 值 .

超高速低压CMOS-CML缓冲器和锁存器的设计

超高速低压CMOS CML缓冲器和锁存器的设计摘要-一个超高速电流模式逻辑(CML)的综合研究和新型再生CML锁存器的设计将会被说明。

首先,提出一种新的设计过程,系统地设计了一个锥形的CML缓冲器链。

接下来,将介绍两个高速再生锁存电路,能够在超高速数据速率运行。

实验结果表明,这种新的锁存结构相比传统的CML锁存电路在超高频率有更高的性能。

它也表明,无论是通过实验以及使用效率的分析模型,为什么CML缓冲器优于CMOS反相器在高速低压的应用。

1.引言电信网络传输的数据量迅速增长,最近引起对千兆通信网络的高速电路设计的重视。

波分复用(WDM)和时分多路复用(TDM)将是发达国家在下一代传输系统使用的。

大量的容量传输实验已经使用每一个通道数据速率为10Gb/s的用于SONET OC-192和40Gb/s的用于SONET OC-768的WDM系统。

高速集成电路(IC)技术,具有很高的数据速率,因此用于WDM和TDM系统。

纳米CMOS技术的进步已使CMOS集成电路接替砷化镓和InP器件迄今声称的领域。

设计一个高速CMOS电路在MOS器件操作非常具有挑战性。

在千兆系统块,通信系统需要由利用最少数量有源器件的简单电路来实现。

部分在通信收发器处理高速信号的电路块可能要放弃使用pMOS器件,因为它们低劣的单位增益频率。

这反过来对超高速电路设计有约束。

缓冲器和锁存器是许多有一个通信收发器和一个串行链路的高速块的核心。

作为一个千兆通信系统的例子,图1描绘了一个典型的光收发器的框图。

前端的电流模式逻辑(CML)的锥形缓冲区链,串行到并行的转换器,时钟和数据恢复(CDR),复用器和解复用器广泛使用高速缓冲器和锁存器。

传统的CMOS反相器显示出一些缺点,使得它们不能被广泛使用于高速低压电路。

首先,CMOS反相器实质上是一个单端电路。

回想一下,在千兆赫的频率范围内,短的片上线充当耦合输电线路。

电磁耦合导致了电路中的严重运作失灵,特别是单端电路。

高速双模前置分频器的速度优化设计

sn l・h s ・lc ( S C d n mi CMOSa dp e d igep a eco kT P ) y a c — - n s u oNMOStc n lg r u pwi o e e h oo yaep t t f r h u h t

i pr e e ss e m ov m ntofi pe d.By t e H S C E sm u a i n,t a m u pe a i l c  ̄ e ue c a t h PI i l to he m xi m o r tng c o k q n yh s

c n l m pr a ty i ove o p r d w ih t t tc C M O ic is d c m a e t he s a i S c r u t.

Ke o d : P d n m i F; a — o u u r s a e ; x m u o e a i g c o k f e u n y y W r s TS C y a cDF Du lm d l s e c l r ma i m p r t l c r q e c ; p n

在 高速 高频 的锁 相环 频率合 成器 设计 中, 高速

工 展 到动态 C MOS 逻辑 。 动态 C MOS 辑 形式 多种 逻 多 样 [] 1,我 们 认 为 凡 是 具 有 时 钟 控 制 、 预 充 电 ( 放 电)作 用 的 C 或 MOS逻辑 就称 为动态 C MOS逻 辑 。按 时钟 相数 可 分为 准两 相 时钟 CMOS ( su o ped

r a he shi h a . GHz i he 0. 1m e c d a g s17 n t 8x CM O S t c nol y a V up y vola . e h og nd 5 s pl t ge whi h i i ni — c ss g f i

一种高速分频器[发明专利]

专利名称:一种高速分频器

专利类型:发明专利

发明人:王海时,李芝友,梁怀天,杨燕,谭菲菲,姜丹丹,唐婷婷,王天宝

申请号:CN201810140070.5

申请日:20180211

公开号:CN108111163A

公开日:

20180601

专利内容由知识产权出版社提供

摘要:本发明公开了一种高速分频器,包括减法电路、反相电路和加法电路。

减法电路接收N位分频比信号和输入时钟信号并提供减法信号;反相电路接收所述减法信号并提供减反信号;加法电路接收所述减反信号和分频比信号的高(N‑1)位,其提供进位信号。

在偶数分频情况下,该高速分频器可以获得占空比为50%的进位信号作为分频信号,避免了频率抖动;在奇数分频情况下,将进位信号进行补偿或调节,同样可以获得占空比为50%的分频信号。

申请人:成都信息工程大学

地址:610225 四川省成都市双流县西南航空港经济开发区学府路一段24号

国籍:CN

代理机构:成都九鼎天元知识产权代理有限公司

代理人:钱成岑

更多信息请下载全文后查看。

一种高速分频器[发明专利]

专利名称:一种高速分频器

专利类型:发明专利

发明人:蒋培珍

申请号:CN201810484674.1申请日:20180520

公开号:CN108770284A

公开日:

20181106

专利内容由知识产权出版社提供

摘要:本发明公开了一种高速分频器,包括第一保护壳,所述第一保护壳内壁的上表面与基座的下表面固定连接,所述基座上表面的左侧和右侧均与挡板的底端固定连接,所述挡板的顶部套接有滑套,所述滑套内壁套接有滑杆,所述滑杆的右端与限位板的左侧面固定连接,所述滑杆的左端与L形固定板的右侧面固定连接,所述挡板的左侧面与第一伸缩机构的右端固定连接,所述第一伸缩机构的左端与L形固定板的右侧面固定连接。

本发明通过设置散热片、通风口、防尘网、第一伸缩杆、第一弹簧、滑块和螺栓,从而对分频器电路板进行快速的安装和拆卸,同时散热片和防尘网达到了散热防尘的双重效果,提升了使用性能,从而达到最佳使用效果。

申请人:苏州沃森优金电子科技有限公司

地址:215000 江苏省苏州市高新区滨河路588号3幢1123室

国籍:CN

更多信息请下载全文后查看。