扩频时钟(SSC)简介

SSC扩频时钟

SSC扩频时钟展开全文SSC,全称Spread Spectrum Clocking,即扩频时钟。

由于信号的能量过于集中在其载波频率位置,导致信号的能量在某一频点位置处的产生过大的辐射发射。

为了有效地降低EMI辐射,芯片厂家在设计芯片时也给容易产生EMI的信号增加了SSC扩频时钟的功能,频率变化的时钟,其频谱能量被分散在一定频谱范围上。

当前PCIE、SATA、SAS、USB3.0等高速芯片都支持SSC的功能。

采用SSC的功能可以有效的降低信号所产生的EMI。

配图来源于网络,侵删说到扩频,会想到分频和倍频,也有过混淆的情况。

分频和倍频说的是CPU与总线、外设之间工作频率的关系。

为什么会有分频、倍频?是因为有些外部设备达不到CPU的工作频率,一般情况下,CPU 的工作频率永远是高于外部设备的,为了协调CPU与外部设备的工作时序,就只有进行分频和倍频处理。

CPU的频率,即主频为外频与倍频两者的乘积。

SSC不仅对时钟振荡频率(基波)有抑制作用,对高次谐波(准确地说是基频的奇次谐波)的峰值也有抑制作用。

SRIS - Separate Refclk Independent SSC. 独立参考扩频;SRNS - Separate Refclk with No SSC。

独立参考无扩频;SRNS允许600ppm,而SRIS允许5600ppm(其中SSC允许5000ppm,TX/RX允许600ppm);一般芯片支持SRIS也会支持SRNS。

+0%~-0.5%这个说的是扩频类型。

扩频类型有三种:中心扩频,向上扩频还有向下扩频。

由于中心和向上扩频都会产生超过系统时钟的频率,会对系统造成影响,所以一般使用向下扩频。

30KHz~33KHz这个说的是被调制信号频率范围内的变化速度。

调制频率太快,后级的PLL电路可能跟踪不上,应远小于源时钟的频率,以免引起时序问题(建立/保持时间等);调制频率太慢,会产生人耳可识别的声音的频率范围(20Hz~20KHz)音噪。

扩频时钟SSC测量

力科应用简介 No.738L.A.B.SSC测量使用DSO进行更多的扩频时钟测量扩频时钟(SSC)在电子系统中正越来越明显。

使用已知调制波对时钟调频会扩大时钟的频谱,以降低峰值频谱功率。

这种峰值功率电平下降是必须的,以满足更严格的电磁干扰标准。

为保证采用这种SSC技术的系统能够正确运行,必须了解实际调制特点。

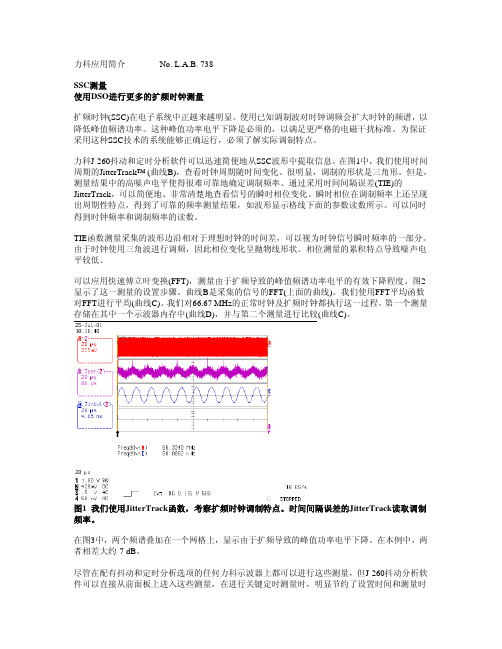

力科J-260抖动和定时分析软件可以迅速简便地从SSC波形中提取信息。

在图1中,我们使用时间周期的JitterTrack™ (曲线B),查看时钟周期随时间变化。

很明显,调制的形状是三角形。

但是,测量结果中的高噪声电平使得很难可靠地确定调制频率。

通过采用时间间隔误差(TIE)的JitterTrack,可以简便地、非常清楚地查看信号的瞬时相位变化。

瞬时相位在调制频率上还呈现出周期性特点,得到了可靠的频率测量结果,如波形显示格线下面的参数读数所示。

可以同时得到时钟频率和调制频率的读数。

TIE函数测量采集的波形边沿相对于理想时钟的时间差,可以视为时钟信号瞬时频率的一部分。

由于时钟使用三角波进行调频,因此相位变化呈抛物线形状。

相位测量的累积特点导致噪声电平较低。

可以应用快速傅立叶变换(FFT),测量由于扩频导致的峰值频谱功率电平的有效下降程度。

图2显示了这一测量的设置步骤。

曲线B是采集的信号的FFT(上面的曲线)。

我们使用FFT平均函数对FFT进行平均(曲线C)。

我们对66.67 MHz的正常时钟及扩频时钟都执行这一过程。

第一个测量存储在其中一个示波器内存中(曲线D),并与第二个测量进行比较(曲线C)。

图1 我们使用JitterTrack函数,考察扩频时钟调制特点。

时间间隔误差的JitterTrack读取调制频率。

在图3中,两个频谱叠加在一个网格上,显示由于扩频导致的峰值功率电平下降。

在本例中,两者相差大约-7 dB。

尽管在配有抖动和定时分析选项的任何力科示波器上都可以进行这些测量,但J-260抖动分析软件可以直接从前面板上进入这些测量,在进行关键定时测量时,明显节约了设置时间和测量时间。

i2c时钟频率

i2c时钟频率I2C时钟频率1. 简介:I2C(Inter-Integrated Circuit)总线,又被称为串行程序总线,它是一种最基本的无控制协议,常被应用在现代的微处理器或微控制器的总线上,它的优点是可以用最少的线路完成接线,有效控制芯片之间的数据传输,用于配置、控制和传输各种非常多的设备。

I2C总线的最终效率在很大程度上取决于传输的时钟频率,时钟频率越高,则传输效率越高。

2. I2C时钟频率:(1)标准速率SCL(Standard-mode Clock):100kHz,意思就是每秒传输100千次数据。

(2)低速率SCL(Low-Speed Clock): 10kHz,意思就是每秒传输10千次数据。

(3)快速率SCL(Fast-mode Clock):400kHz,意思就是每秒传输400千次数据。

(4)高速率SCL(High-speed Clock):1MHz,意思就是每秒传输1000千次数据。

(5)超高速率SCL(Ultra-High-Speed Clock):3.4MHz,意思就是每秒3400千次数据。

3. 对于不同频率的选择:(1)SCL标准速率:一般用于短距离传输和消耗功耗较小,传输距离多达5米之外的传输应用,由于频率较低,改变有线长度无需改变硬件参数。

(2)SCL低速率:一般用于短距离和节省能耗的应用,由于时钟发送的频率接近SCL标准速率,因此允许数据传输速率可达20kb/s。

(3)SCL快速率:主要用于短距离的应用,数据传输速率可达200kb/s,距离不能超过5m。

(4)SCL高速率:一般用于高速数据传输,数据传输速率可达1Mb/s,但是不支持半双工传输。

(5)SCL超高速率:用于支持3.4Mb/s高速数据传输,可以支持1MB/s速率的半双工传输,但是不允许超过3m的距离。

4. 总结:I2C总线最终效率在很大程度上取决于传输的时钟频率,它有SCL标准速率100kHz,SCL低速率10kHz,SCL快速率400kHz,SCL高速率1MHz,SCL超高速率3.4MHz等多种频率,用户可根据具体的应用场景以及产品的特性,合理选择最佳的传输时钟频率,保证应用的高效性性能。

ssc 扩频 波形

ssc 扩频波形

SSC,即序列扩频编码(Sequence Spread Coding),是一种将原始信号通过乘以一个扩频序列来实现频谱扩展的技术。

扩频序列通常是一个伪随机序列,具有良好的自相关性和互相关性,以实现信号的解扩和抗多径干扰的能力。

扩频波形是一种特殊的信号形式,其带宽远大于其携带的信息带宽。

通过扩频,可以将信息编码到一个很宽的频带中,使得信号具有更强的抗干扰能力和隐蔽性。

在SSC中,扩频波形是通过将原始信号与一个扩频序列相乘来实现的。

这个扩频序列是一个伪随机二进制序列,具有良好的自相关性和互相关性。

通过与扩频序列的相乘,原始信号的频谱被扩展到一个很宽的频带中,实现了扩频的效果。

SSC扩频波形的测量可以通过示波器等仪器来进行。

在测量时,需要将示波器的触发模式设置为“边沿触发”,以便准确地捕捉到信号的起始时刻。

同时,还需要对示波器的垂直灵敏度和水平时基进行调整,以便准确地测量信号的幅度和周期等参数。

总之,SSC扩频波形是一种具有特殊性质的信号形式,其测量需要使用专业的仪器和技巧。

通过掌握这些知识,可以更好地理解SSC扩频技术的工作原理和应用。

HDMI1.3版本和HDMI1.4版本的区别

HDMI1.3版本和HDMI1.4版本的区别HDMI1.4提出的新内容:1、HDMI线缆将拥有100Mbps⽹络传输能⼒,相当于整合了百兆⽹线。

通过此功能,附带宽带连接功能的电视机不仅可以利⽤HDMI端⼝与其他设备(游戏机和硬盘录像机)共享视频⾳频信号,还可以同时共享互联⽹连接。

2、分辨率⽀持提升到了4096 x2160,30Hz的标准,新增的⾳频返回频道(ARC),还可以把⾳频信号发送到外部放⼤器,让⽤户获得更佳的⾳频体验。

3、HDMI1.4标准带来了HEC(HDMIEthernetChannel)⽀持,最⾼分辩率达到4096 x2160,30Hz(4K),远远⾼于1080P 的概述4、⽀持⾳频回授通道(Audio Return Channel) ,省去⼀条S/PDIF线缆,让电视可向上传送⾳频信号⾄A/V接收器,并通过HDMI线缆处理与播放。

5、HDMI1.4不能和之前的HDMI 1.3以下等版本规定的线缆兼容,⼀次彻底的技术提升。

综上所⽰,HDMI1.4的普及意味着1.3的淘汰,当然,还有⼀定的共存时间留给⽤户的。

HDMI似乎是与⾼清标准画上了等号。

⽆论是在液晶电视、蓝光播放器,还是HTPC、投影机上,这个⼩⼩的接⼝都是必不可少的,有了它就意味着这个设备进⼊了次时代影⾳播放器的⾏列。

⽽就在⼤多数⼈还在争论是否更先进的DisplayPort将会取代HDMI的时候,HDMI1.4版悄然登场。

不过,尽管HDMI新版本增添了不少功能,但并不是每项技术都是必备的,所以为了让消费者能够明确功能,不⾄于花冤枉钱,近⽇,HDMI标准授权机构对1.4版本发布了新规范。

LLC发布的HDMI新规范 此外,对于除线缆以外的其它相关设备,则最晚应在2012年元⽉1⽇前去除所有版本号标识。

⽽对于⼴⼤的HDMI⼚商来说,应该在产品上加上明确的标识,如“HDMIv.1.4withAudioReturn Channel andHDMIEthernetChannel”(HDMI1.4版⽀持ARC⾳频回授通道和HEC以太⽹通道),避免笼统的HDMI1.4这样的标识使消费者蒙受损失。

扩频时钟SSC技术,即展频

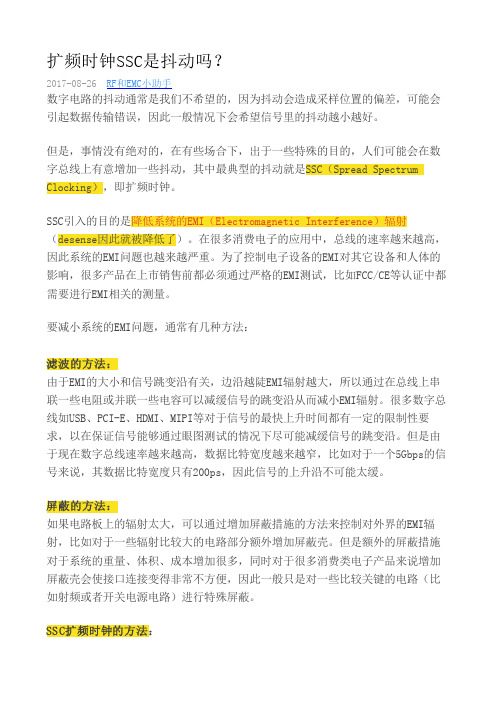

扩频时钟SSC是抖动吗?2017-08-26 RF和EMC小助手数字电路的抖动通常是我们不希望的,因为抖动会造成采样位置的偏差,可能会引起数据传输错误,因此一般情况下会希望信号里的抖动越小越好。

但是,事情没有绝对的,在有些场合下,出于一些特殊的目的,人们可能会在数字总线上有意增加一些抖动,其中最典型的抖动就是SSC(Spread Spectrum Clocking),即扩频时钟。

SSC引入的目的是降低系统的EMI(Electromagnetic Interference)辐射(desense因此就被降低了)。

在很多消费电子的应用中,总线的速率越来越高,因此系统的EMI问题也越来越严重。

为了控制电子设备的EMI对其它设备和人体的影响,很多产品在上市销售前都必须通过严格的EMI测试,比如FCC/CE等认证中都需要进行EMI相关的测量。

要减小系统的EMI问题,通常有几种方法:滤波的方法:由于EMI的大小和信号跳变沿有关,边沿越陡EMI辐射越大,所以通过在总线上串联一些电阻或并联一些电容可以减缓信号的跳变沿从而减小EMI辐射。

很多数字总线如USB、PCI-E、HDMI、MIPI等对于信号的最快上升时间都有一定的限制性要求,以在保证信号能够通过眼图测试的情况下尽可能减缓信号的跳变沿。

但是由于现在数字总线速率越来越高,数据比特宽度越来越窄,比如对于一个5Gbps的信号来说,其数据比特宽度只有200ps,因此信号的上升沿不可能太缓。

屏蔽的方法:如果电路板上的辐射太大,可以通过增加屏蔽措施的方法来控制对外界的EMI辐射,比如对于一些辐射比较大的电路部分额外增加屏蔽壳。

但是额外的屏蔽措施对于系统的重量、体积、成本增加很多,同时对于很多消费类电子产品来说增加屏蔽壳会使接口连接变得非常不方便,因此一般只是对一些比较关键的电路(比如射频或者开关电源电路)进行特殊屏蔽。

SSC扩频时钟的方法:扩频时钟的方法是在数字系统的时钟源头进行轻微的调频,从而降低EMI辐射的峰值功率。

HDMI_DP

DisplayPort是一个不需要版权费就可以随意使用的接口标准,虽然H DMI和DisplayPort看起来有着同样的功能,又同样都是高速数字串行链接,但是在结构上它们却完全不同。

物理特性H DMI和DisplayPort在相同的基础架构以及差分同轴双绞线上运行,都使用高速低电压差分信号来传输数据,但二者的相同点仅此而已。

虽然从外表来看这两个标准十分相似,但结构上却有着巨大的不同。

这些不同决定了链路的性能与其成本、兼容性、鲁棒性以及易执行能力。

HDMI标准现定义了四种连接器,A至D。

除了T ype B外,其余都是19针。

T ype C与D针对便携应用和小体积设备。

两个标准所使用的线缆略有不同。

HD MI1.0至1.3使用4个屏蔽同轴差分对、4个单端控制信号,电源(+5V)以及地线。

HD MI1.4增加了音频回传通道和以太网通道,所以信号的构架有所不同。

HDMI1.4使用的是4个同轴对、1个非屏蔽差分对、3个单端信号、电源(+5V)以及地线。

这意味着,HD MI1.4和HD MI1.3使用不同的线缆。

如果在H DMI1.4系统中使用一根非HDMI1.4线缆,那么音频回传和以太网的功能将会丧失。

但是,H DMI1.3的所有功能以及HD MI1.4的其他新功能(如3D)则都可以保留。

DisplayPort定义了两种接头,全尺寸(Full Size)和迷你(Mini)。

两种接头都有20针,但迷你接头的宽度大约是全尺寸的一半,它们的尺寸分别为7.5mm x 4.5mm与16mm x 4.8mm。

建立完整链路需要5个同轴对、3 个单端信号,以及电源与地线。

DisplayPort本身的可扩展性允许在更少导线的情况下建立低带宽的DisplayPort链接,但是很少有人这么做,因为这有可能给终端用户带来令人困惑的兼容性问题。

DisplayPort则使用8B/10B编码,这是一种通信中的常用方式,能够将链路时钟嵌入至数据流中。

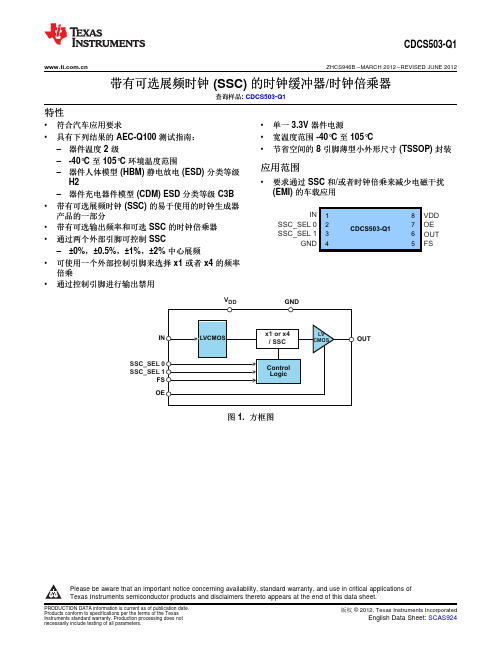

带有可选展频时钟 (SSC) 的时钟缓冲器 时钟倍乘器

OUTV SSC_SEL SSC_SEL INSSC_SEL 0SSC_SEL 1GNDVDD OE OUT FSCDCS503-Q1ZHCS946B –MARCH 2012–REVISED JUNE 2012带有可选展频时钟(SSC)的时钟缓冲器/时钟倍乘器查询样品:CDCS503-Q1特性•符合汽车应用要求•单一3.3V 器件电源•具有下列结果的AEC-Q100测试指南:•宽温度范围-40°C 至105°C–器件温度2级•节省空间的8引脚薄型小外形尺寸(TSSOP)封装–-40°C 至105°C 环境温度范围应用范围–器件人体模型(HBM)静电放电(ESD)分类等级•要求通过SSC 和/或者时钟倍乘来减少电磁干扰H2(EMI)的车载应用–器件充电器件模型(CDM)ESD 分类等级C3B •带有可选展频时钟(SSC)的易于使用的时钟生成器产品的一部分•带有可选输出频率和可选SSC 的时钟倍乘器•通过两个外部引脚可控制SSC–±0%,±0.5%,±1%,±2%中心展频•可使用一个外部控制引脚来选择x1或者x4的频率倍乘•通过控制引脚进行输出禁用图1.方框图Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.CDCS503-Q1ZHCS946B–MARCH2012–REVISED 说明CDCS503-Q1是一款带有可选频率倍乘的可展频、LVCMOS输入时钟缓冲器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SSC是英文Spread Spectrum Clocking的缩写,中文意思为“扩频时钟”,当下的绝大多数高速芯片,如PCIE、SATA、SAS、等都支持SSC功能。

那么SSC究竟是干什么的呢

SSC的主要目的是减小EMI辐射。

EMI一直是高速系统设计的难点,在传统设计中,主要通过滤波、接地、屏蔽等方法来减小EMI辐射,这些方法都是通过改变/切断EMI辐射路径来达到减小EMI辐射的目的,往往设计成本比较高,另外还有一种更好的治本方法,那就是在EMI源头上做文章,减小EMI的产生,SSC技术就是其中一种。

学过信号与系统课程的同学都知道,对于固定频率的时钟,所有能量都集中在其基频上,其频谱很窄,但幅度很高,对外辐射能量很大,而对于频率变化的时钟,其能量会分散在一定频率范围上。

如上图所示,SSC时钟频谱平均分布在一定范围内,幅度很小,不会产生太大的EMI辐射。

一般用扩展率δ来衡量时钟扩展的深度,假设扩展前时钟频率为fc,频率扩展范围为Δf,则有:

向下方向扩频率:δ = -Δf /fc *100%

中心方向扩频率:δ = ±1/2Δf/fc *100%

向**向扩频率:δ = Δf/fc*100%

扩频率不能太小,也不能太大,太小了达不到预期效果,太大了不能满足总线的时序要求,引起系统误码,大多数高速芯片的SSC扩频率在%左右。

扩频的方法如下:假设有某时钟Y(t) = Asin2πfct,用w(t)波形来对基频时钟进行扩频,则扩频后的时钟Y’(t) = Asin2π(fc+w(t))t,未经扩频的时钟频谱是位于fc 的一条谱线,幅度为:A2/2,由于该频谱只是一条谱线,其幅度与频谱带宽B无关。

但是,扩频时钟的频谱幅度取决其带宽B。

由于扩频时钟的功率在Δf频带内分布相当均匀,其幅度为:A2B/(2Δf),这样,我们可以得到EMI抑制率S为:S = 10log((A2/2)/( A2B/(2Δf))) = 10log(Δf/B),单位为dB。

SSC的调制率通常用fm表示,也就是w(t)的周期,在该周期内SSC时钟频率变化Δf 并返回到初始频率。

调制波形代表扩频时钟频率随时间的变化曲线,通常为锯齿波,如下图所示。

SSC 的使用会影响到串行数据眼图的测量效果,因此在进行信号眼图测量验证时需要选择合适的锁相环。

一阶PLL往往不能跟踪SSC 带来的频率变化。

测出来的眼图质量很差,而二阶PLL能很好的跟踪时钟频率的变化,所以在测试带SSC功能的SerDes眼图时,注意将CDR的PLL设为二阶。