ModelSim-Altera_6.5仿真入门教程

使用ModelSim仿真入门

1.点击 ModelSim实验 下载实验文档,保存并解压到D:盘根目录下。

2.启动 ModelSim6.0,执行 File 菜单下的 Change Directory... 命令。

在随后弹出的对话框中,选择 D:\exam 文件夹,点击“OK”按扭。

3.执行 File->New 菜单下的 Library 命令,在随后弹出的对话框上,点击“OK”按钮,建立 work 库。

4.执行 File->New 菜单下的 Project 命令,在随后弹出的对话框的 Project Name 栏,输入 counter,点击“OK”按钮。

5.点击“Use Current Ini”按钮。

6.点击“Add Existing File”图标。

在随后弹出的对话框上,通过点击“Browse...”按钮,选中 D:\exam文件夹下的 tb.v、counter.v 文件,然后点击“OK”按钮。

点击 Add Item to Project 对话框的“Close”按钮。

7.在 Workspace 窗口里,点击右键。

在弹出菜单中点击 Compile 下的 Compile All 命令。

8.在 Simulate 菜单下,点击 Start Simulation... 命令。

9.在随后弹出的对话框中,将 Design Unit 项设为 work 库下 tb 单元,将 Resolution 设为 ns,然后点击“OK”按钮。

10.执行 View->Debug Windows 菜单下的 Wave 命令,打开 Wave 窗口。

11.在 Objects 窗口下,点击右键。

在弹出菜单下,点击 Add to Wave 下的 Signals in Design 命令。

12.在 Transcript 窗口里,输入 run 10 ms 命令。

13.进入 Wave 窗口,观察各个信号的波形,是否与原设计相符。

14.在 Wave 窗口里,双击 cnt 的波形,打开 dataflow 窗口,观察各个信号传递关系。

在quartusII中用modelsim-altera仿真

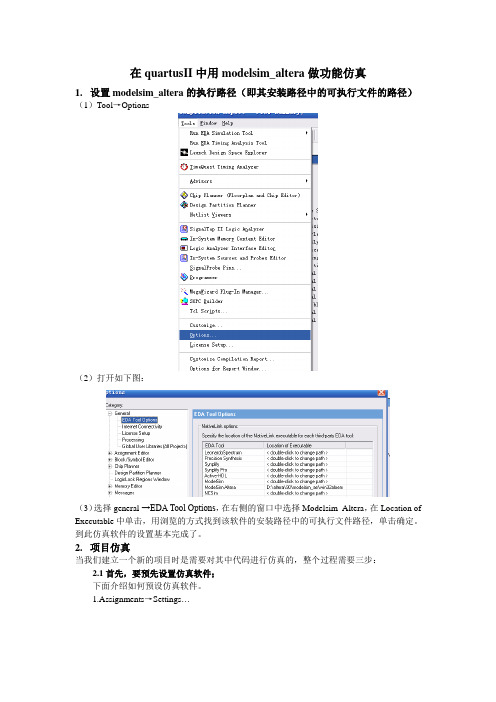

在quartusII中用modelsim_altera做功能仿真1.设置modelsim_altera的执行路径(即其安装路径中的可执行文件的路径)(1)Tool→Options(2)打开如下图:(3)选择general →EDA Tool Options,在右侧的窗口中选择Modelsim_Altera,在Location of Executable中单击,用浏览的方式找到该软件的安装路径中的可执行文件路径,单击确定。

到此仿真软件的设置基本完成了。

2.项目仿真当我们建立一个新的项目时是需要对其中代码进行仿真的,整个过程需要三步:2.1首先,要预先设置仿真软件;下面介绍如何预设仿真软件。

1.Assignments→Settings…2.打开如下界面3选择“Simulation”,右侧设置按上图设置。

2.2其次,仿真之前需要编写测试平台,测试平台有两种的方法:●直接建立XX.v文件●在quartusII中自动生成测试平台模板文件,文件为XX.vt文件下面介绍如何自动生成测试平台模板文件。

1.Processing→Start→Start Test Bench Template Writer注意:要生成testbench模板的前提条件是为项目选择预用的仿真软件,然后模块必须编译成功。

Testbench模板生成后的默认路径为:项目目录\simulation\modelsim\项目名.vt(因为刚才在预设置仿真软件时的“Output Directory”选择的是默认的值simulation\modelsim)。

2.对于自动生成的测试平台模版需要打开修改测试激励信号,这里不做介绍,很简单的。

2.3改写完后要在项目里添加测试平台文件到项目里。

1.Assignments→Settings…2.在打开界面做如下操作:(1)选择“Compile test bench”,然后单击“Test Benches…”(2)打开下面的窗口(3)单击“New”打开下面的窗口,且按图中填写相关信息这个窗口是用来输入testbench的资料和选择testbench的路径的。

ModelSim-Altera使用方法.pdf[1]

![ModelSim-Altera使用方法.pdf[1]](https://img.taocdn.com/s3/m/2731177ba26925c52cc5bf90.png)

平台软件:ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition 内容1 设计流程使用ModelSim仿真的基本流程为:图1.1 使用ModelSim仿真的基本流程2 开始2.1 新建工程打开ModelSim后,其画面如图2.1所示。

图2.1 ModelSim画面1. 选择File>New>Preject创建一个新工程。

打开的Create Project对话框窗口,可以指定工程的名称、路径和缺省库名称。

一般情况下,设定Default Library Name 为work。

指定的名称用于创建一个位于工程文件夹内的工作库子文件夹。

该对话框如图2. 2所示,此外还允许通过选择.ini文件来映射库设置,或者将其直接拷贝至工程中。

图2.2 创建工程的对话框2. 按照图2.3所示,设置Project Name为LED_FLOW,Project Location为D: /led_flow。

图2.3 输入工程信息当单击OK按钮后,在主体窗口的下方将出现Project标签,如图2.4所示。

图2.4 Project标签3. 之后,将出现Add Items to the Project的对话框,如图2.5所示。

图2.5 在工程中,添加新项目2.2 在工程中,添加新项目在Add Items to the Project对话框中,包括以下选项:∙Create New File——使用源文件编辑器创建一个新的Verilog、VHDL、TCL 或文本文件∙Add Existing File——添加一个已存在的文件∙Create Simulation——创建指定源文件和仿真选项的仿真配置∙Create New Folder——创建一个新的组织文件夹1. 单击Create New File。

打开图2.6所示窗口。

图2.6 创建工程文件夹2. 输入文件名称:LED_FLOW,然后选择文件类型为Verilog。

modelsim仿真必会教程

Modelsim功能仿真新手教程By wangjun850725@操作系统:win7软件版本:modelsim6.5se本文只针对初学者,让他们少走点弯路,modelsim软件本身感觉还是比较难以使用的。

本人才疏学浅,但有颗助人的心。

大神请跳过,不要鄙视我。

如有错误,请不吝指点。

QQ群:41143927建立工程省略N字,这没有什么好说的。

几乎所有的软件都是以工程为基础的。

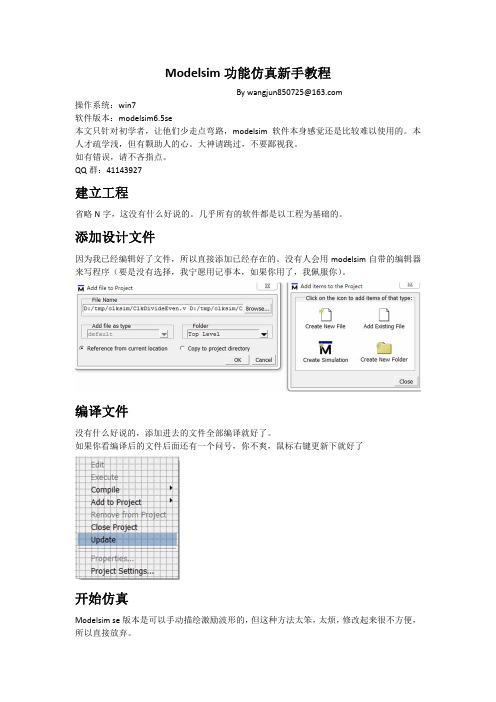

添加设计文件因为我已经编辑好了文件,所以直接添加已经存在的。

没有人会用modelsim自带的编辑器来写程序(要是没有选择,我宁愿用记事本,如果你用了,我佩服你)。

编译文件没有什么好说的,添加进去的文件全部编译就好了。

如果你看编译后的文件后面还有一个问号,你不爽,鼠标右键更新下就好了开始仿真Modelsim se版本是可以手动描绘激励波形的,但这种方法太笨,太烦,修改起来很不方便,所以直接放弃。

Simulate里有个start simulate,点开这里有几点要说明下1.要点开work库,找到你testbench对应的那个模块2.Resolution选不选关系不大,如果你设计文件指定了仿真时间的话3.Optimization,要把这个勾去掉,不然会优化掉很多信号,这里也坑了我很久。

功能仿真只要这么多,如果做后仿,library里要添加已经编译好的器件库,SDF里要添加.vo,.sdo文件观察波形添加信号到波形窗口的方法有很多,刚学手动添加,后来肯定是要在脚本里指定的,下面会有首先要把设计中的信号添加到wave窗口里。

鼠标左键按住不放,将对应的模块拖到wave窗口里,这是最简单的办法。

如果设计的模块多了,每个模块的信号不能很好的被区分,就可以在每个模块的中间插入一个Divider,信号旁边右键就可以看到,最好给起个名字如果你的模块层次非常的多,信号的路径名字就会占据本来就不大的屏幕时很不爽的。

菜单Wave‐>Wave preference‐>Display signal path里面改成1就可以了运行仿真在Transcript窗口里输入Run 1ms搞定,波形神马的就出现了。

手把手教你使用Modsim做仿真

手把手教你使用Modsim做仿真使用Altera的fpga已有两年了,由于之前有做单片机编程经验,时序都是写好上板测,系统做大了之后,觉得效率比较低,于是想使用Modsim来做仿真,以直观地看出每个时钟内信号的状态。

本文目的是了解使用Modsim的步骤,作者已预先写好了源码和测试代码。

使用软件平台:ModelSim-Altera 6.5b + Quartus II 9.11,打开Modsim软件后,通过File / New / Project 建立工程,如图1-1所示:图1-1 建立工程2,此时出现图1-2界面,需要设定工程名称和保存路径,库文件使用默认路径,图1-2 设定工程名称和路径3,创建好工程和路径之后点击“OK”按钮,可出现添加文件的选项窗口,如图1-3所示:图1-3添加文件的选项窗口4,此处由于已编辑好了所有文件,因此选择“Add Existing File”选项,找到文件保存位置并添加,界面如图1-4所示:图1-4 添加文件到工程5,选择好已写好的文件,点击“打开”可添加进工程,如图1-5所示:图1-5 已添加必要文件6,此时可以通过“编译”按钮进行编译和查错,在编译通过之后可看到文件状态“Status”由“?”变为“√”,在消息窗口中有文件编译完成的提示,如图1-6所示:图1-6 编译通过7,编译完成之后可开始仿真,选中“Library / work / testfile”点击鼠标右键,选择“Simulate”,如图1-7所示:图1-7 Simulate 选项8,此时modsim软件出现图1-8所示界面:图1-8 仿真界面9,在左侧“sim”显示区域空白处点击鼠标右键,添加需要查看波形的寄存器名称,并点击“run”开始仿真,程序计算完毕,将显示出仿真的波形,如图1-9所示:图1-9 仿真结果出现波形之后,可通过“放大/缩小”选项和时间渐进条来查看波形。

仿真时间如果不合适,可自行设定,并回到图1-7所示位置,重新开始仿真。

modelsim仿真流程

modelsim仿真流程

ModelsIm仿真流程 ModelSim是一个功能强大且广泛使用的数字电路和模拟软件。

它能够模拟各种不同的电路,包括FPGA、ASIC、流片等,并且可以仿真VHDL、Verilog和SystemC等语言编写的代码。

本文将介绍ModelSim的仿真流程。

1. 建立仿真环境首先,我们需要创建一个仿真环境。

这意味着我们需要创建一个Project文件夹,将仿真所需要的所有文件(包括设计文件、仿真模型以及测试文件等)都放在里面。

我们可以选择使用ModelSim自带的Project Manager工具或者直接使用终端命令行来完成这个工程。

2. 编译设计文件下一步是编译设计文件。

这意味着我们需要把设计文件转换为ModelSim可以理解的仿真模型。

我们可以使用vlib命令来建立一个仿真库,然后使用vlog命令来编译设计文件。

编译完成后,我们需要使用vsim命令进入仿真环境。

3. 进行仿真在仿真界面中,我们可以加载测试文件,然后使用run命令来进行仿真。

这将模拟电路在一个虚拟的环境中运行,并产生仿真结果。

我们可以使用ModelSim提供的信号跟踪和波形查看工具来观察电路的运行状态并分析仿真结果。

4. 仿真结束仿真完成后,我们可以使用exit命令退出仿真环境,并使用ModelSim提供的波形分析和统计工具来评估仿真结果。

如果需要进行更详细的分析,我们可以将波形数据导出到其他工具进行进一步处理。

总之,ModelSim是一个非常强大的数字电路和模拟软件。

掌握其基本操作和仿真流程,可以帮助我们更高效地进行数字电路设计和开发工作。

modelsim使用教程

modelsim使用教程ModelSim是一款常用的硬件描述语言(HDL)仿真工具,本教程将向您介绍如何使用ModelSim进行仿真。

步骤1:安装ModelSim首先,您需要下载和安装ModelSim软件。

在您的电脑上找到安装程序并按照提示进行安装。

步骤2:创建工程打开ModelSim软件,点击"File"菜单中的"New",然后选择"Project"。

在弹出的对话框中,选择工程的存储位置,并为工程命名。

点击"OK"完成工程创建。

步骤3:添加设计文件在ModelSim的工程窗口中,右键点击"Design"文件夹,选择"Add Existing File"。

然后选择包含您的设计文件的目录,并将其添加到工程中。

步骤4:配置仿真设置在工程窗口中,右键点击"Design"文件夹,选择"Properties"。

在弹出的对话框中,选择"Simulation"选项卡。

在"Top level entity"字段中,选择您的设计的顶层模块。

点击"Apply"和"OK"保存设置。

步骤5:运行仿真在ModelSim的工具栏中,找到"Simulate"按钮,点击并选择"Start Simulation"。

这将打开仿真窗口。

在仿真窗口中,您可以使用不同的命令来控制和观察设计的行为。

步骤6:查看仿真结果您可以在仿真窗口中查看信号波形、调试设计并分析仿真结果。

在仿真窗口的菜单栏中,您可以找到一些常用的查看和分析工具,如波形浏览器、信号分析器等。

步骤7:结束仿真当您完成仿真时,可以选择在仿真窗口的菜单栏中找到"Simulate"按钮,并选择"End Simulation"以结束仿真。

modelsim新手入门仿真教程

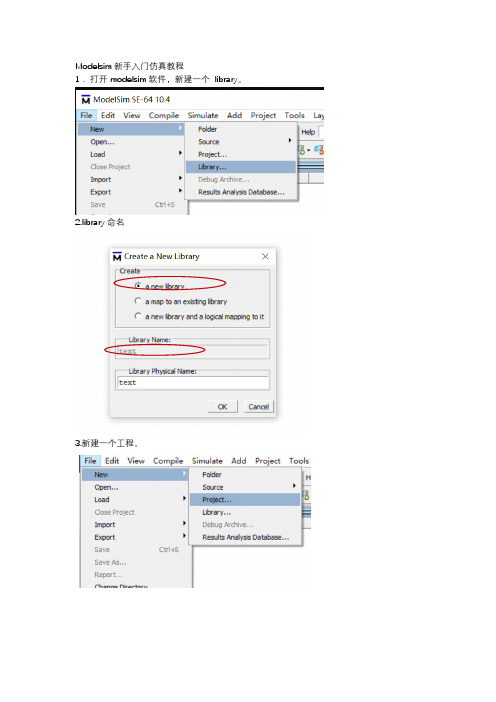

Modelsim新手入门仿真教程1.打开modelsim软件,新建一个library。

2.library命名3.新建一个工程。

3.出现下面界面,点击close。

4.新建一个verilog文件键入主程序。

下面以二分之一分频器为例。

文件代码:module half_clk(reset,clk_in,clk_out); input clk_in,reset;output clk_out;reg clk_out;always@(negedge clk_in)beginif(!reset)clk_out=0;elseclk_out=~clk_out;endendmodule编辑完成后,点击保存。

文件名要与module后面的名称相同。

5.再新建一个测试文件,步骤同上面新建的主程序文件,文件名后缀改为.vt程序代码如下:`timescale 1ns/100ps`define clk_cycle 50module top;reg clk,reset;wire clk_out;always #`clk_cycle clk=~clk;initialbeginclk=0;reset=1;#10 reset=0;#110 reset=1;#100000 $stop;endhalf_clk m0(.reset(reset),.clk_in(clk),.clk_out(clk_out));Endmodule6.添加文件,编译文件先右键点击左边空白处,选择add to project→existing File选择刚刚新建的两个文件。

按ctrl键可以同时选择两个,选择打开,下一步点击ok7选中其中一个,右键,选择complie→complie all出现两个勾,说明编译通过。

出现×,说明文件编译出错,双击×,可以查看错误。

8.终于可以仿真了选择simulate→start simulate。

选择刚刚新建的库里面的top,或者测试文件名称,左下角的enable optimization一定要去掉勾,有勾的画不会出来波形,一定要去掉勾!一定要去掉勾!一定要去掉勾!(本人也不清楚原因,都是初学者,嘻嘻)跳出界面,右键测试文件,选择如下图接下来,选择仿真,run→run all点击缩小键,如图,就可以看到波形啦到此结束!初学者,如有错误,欢迎指出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

平台软件:ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition内容1 设计流程使用ModelSim仿真的基本流程为:图1.1 使用ModelSim仿真的基本流程2 开始2.1 新建工程打开ModelSim后,其画面如图2.1所示。

图2.1 ModelSim画面1. 选择File>New>Preject创建一个新工程。

打开的Create Project对话框窗口,可以指定工程的名称、路径和缺省库名称。

一般情况下,设定Default Library Name为work。

指定的名称用于创建一个位于工程文件夹内的工作库子文件夹。

该对话框如图2.2所示,此外还允许通过选择.ini文件来映射库设置,或者将其直接拷贝至工程中。

图2.2 创建工程的对话框2. 按照图2.3所示,设置Project Name为LED_FLOW,Project Location为D:/led_flow。

图2.3 输入工程信息当单击OK按钮后,在主体窗口的下方将出现Project标签,如图2.4所示。

图2.4 Project标签3. 之后,将出现Add Items to the Project的对话框,如图2.5所示。

图2.5 在工程中,添加新项目2.2 在工程中,添加新项目在Add Items to the Project对话框中,包括以下选项:•Create New File——使用源文件编辑器创建一个新的Verilog、VHDL、TCL或文本文件•Add Existing File——添加一个已存在的文件•Create Simulation——创建指定源文件和仿真选项的仿真配置•Create New Folder——创建一个新的组织文件夹1. 单击Create New File。

打开图2.6所示窗口。

图2.6 创建工程文件夹2. 输入文件名称:LED_FLOW,然后选择文件类型为Verilog。

图2.7 输入工程文件信息3. 单击OK,关闭本对话框。

新的工程文件将会在工程窗口显示。

单击Close,以关闭Add Items to the Project。

图2.8 新的设计文件LED_FLOW.v4. 双击打开LED_FLOW.v文件(注意:若是Verilog文件已经关联了其他的文本编辑器,则双击后在关联的文本编辑器中打开)。

图2.9 LED_FLOW代码输入窗口在LED_FLOW.v输入下面的测试平台代码:view sourceprint?01`timescale1ns/1ns02module LED_FLOW;0304reg CLOCK_50M;05reg RST_N;06wire[9:0] LED;0708led led_inst09(10 .clk_50M(CLOCK_50M),11 .reset_n(RST_n),12 .led(LED)13);1415initial16begin17 CLOCK_50M = 0;18 while(1)19 #10 CLOCK_50M = ~CLOCK_50M; 20end2122initial23begin24 RST_N = 0;25 while(1)26 #10 RST_N = 1;27end2829initial30begin31 $display($time,"CLOCK_50M=%d RST_N=%d LED =%d", CLOCK_50M, RST_N, LED);32end3334endmodule录入完代码后,单击Save。

图2.10 输入testbench代码5. 选择File>New>Source>Verilog,创建新的Verilog文件,如图2.11所示。

图2.11 创建新的Verilog文件6. 录入下面的代码,录入画面如图2.12 所示。

view sourceprint?1`timescale1ns/1ns2module led(3 input clk_50M, // System clock 50MHz4 input reset_n, // System reset5 output reg[9:0] led // led6);78reg[13:0] counter = 0;9reg[3:0] state = 0;view sourceprint?01always@ (posedge clk_50M, negedge reset_n)02 if(!reset_n)03 counter <= 0;04 else05 counter <= counter + 1'b1;0607always@ (posedge counter[13])08 if(!reset_n)09 state <= 0;10 else11 begin12 if(state == 4'b1001)13 state <= 0;14 else15 state <= state + 1'b1;16 end1718always@ (posedge clk_50M, negedge reset_n)19 if(!reset_n)20 led <= 0;21 else22 begin23 case(state)24 4'b0000: led <= 10'b00000_00001;25 4'b0001: led <= 10'b00000_00010;26 4'b0010: led <= 10'b00000_00100;27 4'b0011: led <= 10'b00000_01000;28 4'b0100: led <= 10'b00000_10000;29 4'b0101: led <= 10'b00001_00000;30 4'b0110: led <= 10'b00010_00000;31 4'b0111: led <= 10'b00100_00000;32 4'b1000: led <= 10'b01000_00000;33 4'b1001: led <= 10'b10000_00000;34 default: led <= 10'b00000_00001;35 endcase36 end3738endmodule图2.12 录入新文件7. 选择File>Save,输入文件名:led.v,单击Save,如图2.13所示。

图2.13 保存led.v8. 选择Project>Add to Project>Existing File,如图2.14所示。

图2.14添加文件到工程中9. 单击Browse,选择led.v,如图2.15 所示。

图2.15 选择待加入工程的文件10. 单击打开,在Add file to the project窗口,单击OK。

2.3 编译文件在Project标签下的Status列的问号,表示文件尚未编译进工程,或者在最后编译前,源文件有所改动。

欲编译文件,选择Compile<Compile ALL,或者右击Project标签,选择Compile>Compile All。

1. 倘若此处没有错误,编译成功的消息,就会在Transcript窗口如图2.6所示。

图2.16 编译成功3 仿真工程3.1 开始仿真1. 单击Library图标,选择work,单击+以展开选项,然后选择LED_FLOW。

单击右键,选择编译,如图3.1所示。

图3.1 单击Simulate2. 单击Simulate,到达图3.2所示画面。

图3.2 仿真窗口4. 在图3.2中,单击LED_FLOW,单击右键,然后选择Add>To Wave>All Items in region,然后单击左键。

出现图3.3所示画面。

图3.3 Add To Wave3.2 仿真设置1. 完成上述最后一步后,波形窗口出现。

图3.4 波形窗口2. 在Run Length列输入仿真时间长度为10ms,如图3.5所示。

图3.5 设置Run Length3. 单击Run按钮,如图3.6所示。

图3.6 运行仿真4. 运行若干秒后,将会如图3.9所示的仿真结果。

图3.7 显示仿真结果5. 连续单击Zoom Out图标,可查看仿真的完整波形,如图3.8所示。

图3.8 波形窗口6. 单击鼠标所指的+,展开LED_FLOW的波形,如图3.9所示。

图3.9 展开波形通过放大/缩小波形,可以观察到LED的值在保持变化,即LED的时序效果。

若将其移植到Quartus II 中,适当配置后,经过综合、时序分析、引脚分配、配置及下载等,即可实现跑马灯的效果。

至此,仿真的所有进程完毕。