数字电路第三章

数字电路讲义 第三章

是构成数字电路的基本单元之一

CMOS 集成门电路 用互补对称 MOS 管构成的逻辑门电路。

TTL 集成门电路 输入端和输出端都用 三极管的逻辑门电路。

CMOS Complementary Metal-Oxide-Semiconductor TTL 即即 Transistor-Transistor Logic 按功能特点不同分 普通门 输出 三态门 CMOS (推拉式输出) 开路门 传输门 EXIT

E

B UBE(sat) iB ≥ IB(sat) E C

三极管 截止状态 等效电路

UCE(sat)

三极管 饱和状态 等效电路

EXIT

逻辑门电路

开关工作的条件

截止条件 uBE < Uth 可靠截止条件为 uBE ≤ 0

VCC U CE(sat) RC VCC RC

饱和条件

iB > IB(Sat)

逻辑门电路

[例] 下图中,已知 ROFF 800 ,RON 3 k,试对应 输入波形定性画出TTL与非门的输出波形。

A 3.6 V 0.3 V

逻辑0 (a)

逻辑1

O Ya t

(b)

解:图(a)中,RI = 300 < ROFF 800 相应输入端相当于输入低电平, O 也即相当于输入逻辑 0 。 Yb 不同因此 TTLY 系列, R R 不同。 ON、 OFF UOH 。 a 输出恒为高电平 图(b)中,RI = 5.1 k > RON 3 k 相应输入端相当于输入高电平, O 也即相当于输入逻辑 1 。 Yb A 1 A 因此,可画出波形如图所示。

0. 3 O

t

EXIT

逻辑门电路

二、三极管的动态开关特性

数字电路第三章习题答案

数字电路第三章习题答案

3-10

F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B F F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B

数字电路第三章习题答案

3-11

试用六个与非门设计一个水箱控制电路。图为水箱示意图。A、B、C是三个电极。 当 电极被水浸没时,会有信号输出。水面在A,B间为正常状态,点亮绿灯G;水面在B、 C间或在A以上为异常状态,点亮黄灯Y;水面在C以下为危险状态.点亮红灯R。

3531736半加器的设计1半加器真值表2输出函数3逻辑图输入输出被加数a加数b4逻辑符号31837ab改为用与非门实现函数表达式变换形式

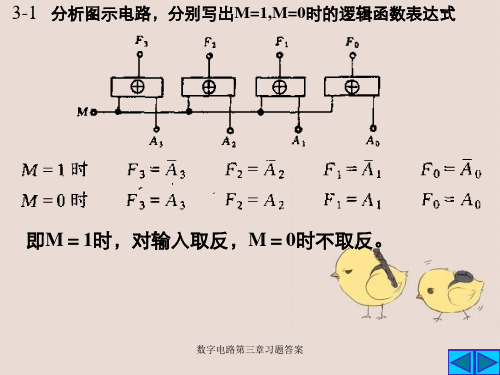

3-1 分析图示电路,分别写出M=1,M=0时的逻辑函数表达式

即M=1时,对输入取反,M=0时不取反。

数字电路第三章习题答案

3-2 分析图示补码电路,要求写出逻辑函数表达式,列出真值表。

3-10 试用与非门设计一个逻辑选择电路。

S1、S0为选择端,A、B为数据输入端。 选择电路的功能见下表。选择电路可 以有反变量输入。

数字电路第三章习题答案

3-10

F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B F F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B FS 1 S 0A B S 1 S 0(A B )S 1 S 0(A BA)B

数字电路第三章习题答案

3-5

Ai 0 0 0 0 1 1 1 1

Si Ai BiCi Ai BiCi Ai BiCi Ai BiCi

数字电路第三章答案

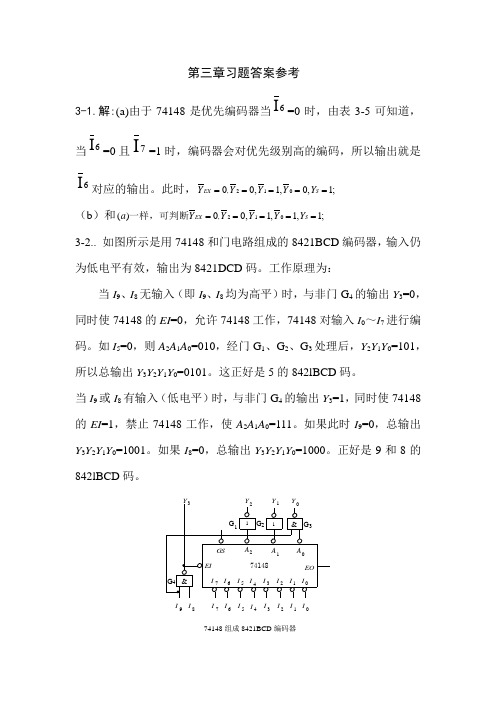

第三章习题答案参考3-1.解:(a)由于74148是优先编码器当6I =0时,由表3-5可知道,当6I =0且7I=1时,编码器会对优先级别高的编码,所以输出就是6I 对应的输出。

此时,,21000,1,0,1;EXS YY Y Y Y =====(b )和,210()00,1,1,1;EX S a Y Y Y Y Y =====一样,可判断3-2.. 如图所示是用74148和门电路组成的8421BCD 编码器,输入仍为低电平有效,输出为8421DCD 码。

工作原理为:当I 9、I 8无输入(即I 9、I 8均为高平)时,与非门G 4的输出Y 3=0,同时使74148的EI =0,允许74148工作,74148对输入I 0~I 7进行编码。

如I 5=0,则A 2A 1A 0=010,经门G 1、G 2、G 3处理后,Y 2Y 1Y 0=101,所以总输出Y 3Y 2Y 1Y 0=0101。

这正好是5的842lBCD 码。

当I 9或I 8有输入(低电平)时,与非门G 4的输出Y 3=1,同时使74148的EI =1,禁止74148工作,使A 2A 1A 0=111。

如果此时I 9=0,总输出Y 3Y 2Y 1Y 0=1001。

如果I 8=0,总输出Y 3Y 2Y 1Y 0=1000。

正好是9和8的842lBCD 码。

I I 457I 162I I I 03I I I 98I74148组成8421BCD 编码器3-3由于74147时优先编码器,优先级别为从9到1依次降低,而且是低电平有效,对照引脚图与真值表所以有(1)引脚为1.3.5时,看引脚5,即是8I,输出为:0111(2)引脚为2.4.10时,看引脚10,即是9I,输出为:0110(3)引脚为3.5.11时,看引脚5,即是8I,输出为:0111(4)引脚为4.10.12时,看引脚10,即是9I,输出为:0110(5) 引脚为5.10.13时,看引脚10,即是9I,输出为:0110(6) 引脚为10.11.13时,看引脚10,即是9I,输出为:01103-4(1)解:F1(A,B,C)=AB+C=1m+m3+m5+m6+m7=71m mmmm365实现的电路图如下:(2)解:F2(A,B,C)=m1+m2+m4+m5+m6=m6m1m5m2m4实现的电路图如下:(3)解:F 3(A,B,C )=∑)(5,3,1m =531m m m 实现的电路图如下:(4)解:F 4(A,B,C )=∑),(6,2,10m =6210m m m m 实现的电路图如下:(5)解:F 5(A,B,C )=∑),(6,5,30m =6530m m m m 实现的电路图如下:(6)解:F 6(A,B,C )=∑),(7,5,21m =7521m m m m 实现的电路图如下:(7)解:F7(A,B,C)=∑)m=72(7,6,3,mm2m3m6实现的电路图如下:(8)解:F8(A,B,C)=∑)m=7(7,4,1mm41m实现的电路图如下:3-5(1)解:F1(A,B,C,D)= ∑)9107811132m14,35,612,,,(14,,,,,,,=14mmmmmmmmmmmmm61091112131m823475实现的电路图如下:(2)解:F2(A,B,C,D)= )11102145m,(15,,,,=15mmmmm10142m115实现的电路图如下:=12mmmmmmm7896452m实现的电路图如下:(4)解:F4(A,B,C,D)= ∑)1011,61m4(14,,,,,,12=14mmmmmmm611120m1041实现的电路图如下:=15mmmmmmm911813472m实现的电路图如下:(6)解:F6(A,B,C,D)= ∑)4,27m9,,,,(11 =11mmmmm290m74实现的电路图如下:3-6 解:利用真值表,可以将Y 换成Y ,易得如下的表达式:A A A A Y123=A A A A Y 01231=A A A Y122=A A A Y 0123=A A A Y 0124= A A A Y125=A A A Y126=A A A Y 0127=A A Y38=A A Y 039=3-7解:根据题3-6的结果,F 1(A,B,C,D)= YY Y 52=A A A A A A A A A A 0120120123=A 3同理可得:F 2(A,B,C,D)= Y Y Y 641=A 3 F3(A,B,C,D)= Y Y Y 973=A A 03波形图如下:3-8解:波形如图所示:3-9解:图中的C in接地,为0,得全加器的函数式: S=B ABA+C o u t=AB+(A+B) C in得:1ACD BCDF=+2()() AB AB CD DF=++ 3-10设计如图所示:3-12解:(1)在八选一选择器74151中令A2=A ,A1=B ,A0=C 将F 1 (A,B)加多一个C ,换成F 1 (A,B,C)得F 1(A,B)= F1(A,B,C)=∑),,(543,2m 得D2=D3=D4=D5= 1 D0=D1= D6=D7=0(2)在八选一选择器74151中令A2=A ,A1=B ,A0=CF2(A,B,C)=∑),,(421,0m 得D0=D1=D2=D4=1 D3=D5=D6=D7=0(3)在八选一选择器74151中令A2=A ,A1=B ,A0=CF3(A,B,C)=∑),,(7,6,5,421m 得D1=D2=D4= D5=D6=D7=1 D0=D3= 0(4)在八选一选择器74151中令A2=A ,A1=B ,A0=CF4(A,B,C)=∑),,(6,5,4,321,0m 得D0=D1=D2=D3=D4=D5=D6=1 D7=0(5)在八选一选择器74151中令A2=A ,A1=B ,A0=C F4(A,B,C,D)=∑),,(13,12,1198,3m得D4= D6=1 D1= D5=D D0= D2= D3=D7=0(6)在八选一选择器74151中令A2=A ,A1=B ,A0=CF6(A,B,C)=∑),(6,5,30m 得D0= D3= D5=D6=1 D1=D2= D4=D7=0(7)在八选一选择器74151中令A2=A ,A1=B ,A0=CF7(A,B,C)=∑),(7,6,31m 得D1= D3= D6= D7=1 D0 =D2= D4= D5= 0(8)在八选一选择器74151中令A2=A ,A1=B ,A0=CF8(A,B,C,D)=∑),,(13,1110,54,3m得D2= D5=1 D1= D6 =DD0= D3= D4=D7=03-13解:设计如图所示:14解:输出的逻辑图如下:得逻辑表达式:Y=DBAA++CDBBA15解:如图所示:。

数字电路教案-阎石-第三章-逻辑门电路

第3章逻辑门电路3.1 概述逻辑门电路:用以实现基本和常用逻辑运算的电子电路。

简称门电路.用逻辑1和0 分别来表示电子电路中的高、低电平的逻辑赋值方式,称为正逻辑,目前在数字技术中,大都采用正逻辑工作;若用低、高电平来表示,则称为负逻辑。

本课程采用正逻辑。

获得高、低电平的基本方法:利用半导体开关元件的导通、截止(即开、关)两种工作状态.在数字集成电路的发展过程中,同时存在着两种类型器件的发展。

一种是由三极管组成的双极型集成电路,例如晶体管-晶体管逻辑电路(简称TTL电路)及射极耦合逻辑电路(简称ECL电路).另一种是由MOS管组成的单极型集成电路,例如N-MOS逻辑电路和互补MOS(简称COMS)逻辑电路。

3。

2 分立元件门电路3。

3.1二极管的开关特性3.2.2三极管的开关特性NPN型三极管截止、放大、饱和3种工作状态的特点工作状态截止放大饱和条件i B=0 0<i B<I BS i B>I BS工作特点偏置情况发射结反偏集电结反偏u BE〈0,u BC〈0发射结正偏集电结反偏u BE>0,u BC〈0发射结正偏集电结正偏u BE〉0,u BC〉集电极电流i C=0 i C=βi B i C=I CSce间电压u CE=V CC u CE=V CC-i C R cu CE=U CES=0.3Vce间等效电阻很大,相当开关断开可变很小,相当开关闭合3.2。

3二极管门电路1、二极管与门2、二极管或门u A u B u Y D1D20V 0V 0V 5V 5V 0V 5V 5V0V4。

3V4。

3V4.3V截止截止截止导通导通截止导通导通3。

2.4三极管非门3。

2。

5组合逻辑门电路1、与非门电路2、或非门电路3.3 集成逻辑门电路一、TTL与非门1、电路结构(1)抗饱和三极管作用:使三极管工作在浅饱和状态。

因为三极管饱和越深,其工作速度越慢,为了提高工作速度,需要采用抗饱和三极管。

构成:在普通三极管的基极B和集电极C之间并接了一个肖特基二极管(简称SBD)。

数字电子技术 第三章 组合逻辑电路

2021/6/10

23

3.2.2 二进制编码器

由于每次操作只有一个输入信号,即输入IR、IY、IG 具有互斥性,根据表3.5,将输出变量取值为1对应的输入 变量相加,可得输出Y1、Y0与输入IR、IY、IG之间的逻辑 关系表达式如下。

Y0 = IR + IG Y1 = IY + IG

对Y1、Y0两次取非,得

5. 断开开关S1、S2,观察发光二极管的发光情况,记 录观察到的结果。

2021/6/10

39

3.3.1 任务描述

图3.18所示是开关S1闭合、S2断开时,观察到的现象。

2021/6/10

图3.18 闭合S1、断开S2时观察到的现象

40

3.3.2 二进制译码器

1. 译码器的基本功能 二进制译码真值表如表3.11所示。

2021/6/10

27

3.2.2 二进制编码器

表中的“×”号表示:有优先级高的输入信号输入时, 优先级低的输入信号有输入还是无输入,不影响编码器的 输出。

2021/6/10

28

3.2.2 二进制编码器

3. 集成8线-3线优先编码器 集成8线-3线优先编码器74LS148、74LS348的引脚排 列完全相同,如图3.12(a)所示。

第四步,判断逻辑电路的逻辑功能。其方法是:根据

真值表进行推理判断。在实际应用中,当逻辑电路很复杂

时,一般难以用简明扼要的文字来归纳其逻辑功能,这时

就用真值表来描述其逻辑功能。

2021/6/10

7

3.1.2 组合逻辑电路的分析

2. 分析举例 【例3.1】 试分析图3.1所示电路的逻辑功能。

解:画出图3.1所示电路的逻辑图如图3.4所示。

数电第三章讲解

(1) 传输门组成的异或门

B=0

A

B

TG1断开, TG2导通

L=A B=1

TG1导通, TG2断开

L=A

TG1

L

TG2

2. 传输门的应用

(2) 传输门组成的数据选择器

C=0

X

TG1导通, TG2断开

L=X

C=1

Y

TG2导通, TG1断开

C

L=Y

VDD TG1 L

TG2

3.3 CMOS逻辑门电路的不同输出结构及参数

3.3.1 CMOS逻辑门电路的保护和缓冲电路 3.3.2 CMOS漏极开路和三态门电路 3.3.3 CMOS逻辑门电路的重要参数

3.3.1 输入保护电路和缓冲电路

采用缓冲电路能统一参数,使不同内部逻辑集成逻辑门电路 具有相同的输入和输出特性。

VDD

vi

基本逻辑

vo

功能电路

输入保护缓冲电路 基本逻辑功能电路 输出缓冲电路

异或门电路324cmos传输门双向模拟开关5v0v电路tg逻辑符号5v0v1传输门的结构及工作原理tp2vttn2v的变化范围为0到5v0v5v0v到5vgsp5v0v到5v5到0v开关断开不能转送信号c00vc15v5v0v5v0v2v5v2v5vgsn5vtg1断开tg2导通tg1导通tg2断开tg1导通tg2断开tg2导通tg1断开tg2tg133cmos逻辑门电路的不同输出结构及参数331cmos逻辑门电路的保护和缓冲电路332cmos漏极开路和三态门电路333cmos逻辑门电路的重要参数331输入保护电路和缓冲电路基本逻辑功能电路基本逻辑功能电路输入保护缓冲电路输出缓冲电路采用缓冲电路能统一参数使不同内部逻辑集成逻辑门电路具有相同的输入和输出特性

数电第三章门电路

§3.4 TTL门电路

数字集成电路:在一块半导体基片上制作出一个 完整的逻辑电路所需要的全部元件和连线。 使用时接:电源、输入和输出。数字集成电 路具有体积小、可靠性高、速度快、而且价 格便宜的特点。

TTL型电路:输入和输出端结构都采用了半导体晶 体管,称之为: Transistor— Transistor Logic。

输出高电平

UOH (3.4V)

u0(V)

UOH

“1”

输出低电平

u0(V)

UOL

UOL (0.3V)

1

(0.3V)

2 3 ui(V)

1 2 3 ui(V)

阈值UT=1.4V

传输特性曲线

理想的传输特性 28

1、输出高电平UOH、输出低电平UOL UOH2.4V UOL 0.4V 便认为合格。 典型值UOH=3.4V UOL 0.3V 。

uA t

uF

截止区: UBE< 死区电压, IB=0 , IC=ICEO 0 ——C、 E间相当于开关断开。

+ucc

t

4

0.3V

3.2.3MOS管的开关特 恒流区:UGS>>Uth , UDS

性: +VDD

0V ——D、S间相当于 开关闭合。

R

uI

Uo

Ui

NMO S

uO

夹断区: UGS< Uth, ID=0 ——D、S间相当于开关断开。

3.3.4 其它门电路

一、 其它门电路

其它门电路有与非门、或非门、同或门、异或门等等,比如:

二、 门电路的“封锁”和“打开”问题

A B

&

Y

C

当C=1时,Y=AB.1=AB

电子技术 数字电路 第3章 组合逻辑电路

是F,多数赞成时是“1”, 否则是“0”。

0111 1000 1011

2. 根据题意列出真值表。

1101 1111

(3-13)

真值表

ABCF 0000 0010 0100 0111 1000 1011 1101 1111

3. 画出卡诺图,并用卡 诺图化简:

BC A 00

00

BC 01 11 10

010

3.4.1 编码器

所谓编码就是赋予选定的一系列二进制代码以 固定的含义。

一、二进制编码器

二进制编码器的作用:将一系列信号状态编制成 二进制代码。

n个二进制代码(n位二进制数)有2n种 不同的组合,可以表示2n个信号。

(3-17)

例:用与非门组成三位二进制编码器。 ---八线-三线编码器 设八个输入端为I1I8,八种状态,

全加器SN74LS183的管脚图

14 Ucc 2an 2bn2cn-1 2cn

2sn

SN74LS183

1 1an 1bn 1cn-11cn 1sn GND

(3-39)

例:用一片SN74LS183构成两位串行进位全加器。

D2

C

D1

串行进位

sn

cn

全加器

an bn cn-1

sn

cn

全加器

an bn cn-1

1 0 1 1 1 AB

AC

F AB BC CA

(3-14)

4. 根据逻辑表达式画出逻辑图。 (1) 若用与或门实现

F AB BC CA

A

&

B

C

&

1 F

&

(3-15)

(2) 若用与非门实现

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(c)图P3.7(c)电路可划分为三个与非门电路、两个反相 器电路和一个或非门电路,如图所示。从输入Байду номын сангаас输出逐级写 出输出的逻辑函数式:

E (AB ),F (CD )',G (EF ),H (INH G )

' '

'

Y I ' H ( AB)' (CD)' ' ( INH ) ' ( AB CD)' ( INH )'

Vcc VCE ( sat )

I BS

10 0.1 A 0.32mA 3 ( RC RCE ( sat ) ) 30 (1 0.02) 10

iB I BS

【题3.13】试分析图3.13中各电路的逻辑功能,写出输出逻 辑函数式。

(a) Y=AB

(b)Y=A+B

VOD VOL 5 0.33 0.9k ' 3 6 I OL(max) | m I IL | 5.2 10 10 10

R L(min)

0.9k

R

L

20k

V

CE (sat )

0.1 V

R

CE (sat )

R1 R2 RE 3.97k R1 R2

解:R L 的最大允许值为:

R L(max)

VOD VOH 5 4.4 31.6k 6 6 nI OH mI IH 2 5 10 9 1 10

R L 的最小允许值为:

VOD VOL 5 0.33 RL (min) 0.9k ' 3 6 I OL (max) | m I IL | 5.2 10 9 10

I

IL

0.4mA

R( 2 max)

V 5I

max

IL( max ) IL( max )

0.4 K 0.2K 5 0.4

54 K 10K 5 0.02

R 1 R 2

V

CC

V

IH ( max )

因此 R ( 1 max)

R 1 R 2

( max )

(d)图P3.7(d)电路可划分为两个反相器电路和两个传输 门电路,如图所示。从输入到输出逐级写出输出的逻辑函数 式:

Y A B AB

' '

【题3.8】 试画出图3-8(a)(b)两个电路的输出电压波形 ,输入电压波形如图(c)所示。

输出电压波形 如右图所示:

【题3.9】 在图3-21所示电路中,G1和G2是两个OD输出结构 的与非门74HC03,74HC03输出端MOS 管截止电流为I OH (max) 5uA 导通时允 许的最大负载电流为IOL(max) 5.2mA 这时对应的输出电压VOL(max)=0.33V。 负载门G3-G5是3输入端或非门74HC27, 每个输入端的高电平输入电流最大值 IIH (max) 1uA ,低电平输入电流最 为 大值为 IIL(max) 1uA ,试求在 VOD 5V 、、、、 并且满足 VOH 4.4V , VOL 0.33V 的情况下, R L 的取值的允许范围。

VOD VOL 5 0.4 K 0.68k ' I OL(max) | m I IL | 8 3 0.4

0.68k

R L(min)

R

L

4.29k

【题3.29】试说明下列各种门电路哪些可以将输出端并联使 用(输入端的状态不一定相同): (1)具有推拉式输出级的TTL电路; (2)TTL电路的OC门; (3)TTL电路的三态输出门; (4)互补输出结构的CMOS门; (5)CMOS电路的OD门; (6) CMOS电路三态输出门。 解:(1)、(4)不可; (2)、(3)、(5)、(6)可以

5I IH

max

R

2( max )

(10 0.2)K 9.8K

【题3.23】计算图P3.23电路中上拉电阻R _1的取值范围。其中 G _1、G _ 2、G _ 3是74LS系列OC门,输出管截止时的漏电 流IOH 100 A, 输出低电平V OL 0.4V ? 时允许的最大负载电流 IOL(max ) 8mA。G _ 4、G _ 5、G _ 6为74LS系列与非门,它们 的输入电流

' ' '

'

Y D A1B1C1 A B C ( A B C)

' ' ' '

'

(b)图P3.7(b)电路可划分为五个反相器电路和一个或非 门电路,如图所示。从输入到输出逐级写出输出的逻辑函数 式:

Y ( A1 B1 C1 )

'

( A' B ' C ' )' ABC

I

IL

0.4mA, I IH 20 A。给定V _ CC 5V, 要求

OC门的输出高低电平满足V OL 0.4V ,V OH 3.2V。

R L(max)

V DD VOH 5 3.2 K 4.29k nI OH mI IH 0.1 3 0.02 6

(c ) Y (A B )

(d)

Y

1时) A(当(G 1 G 2 ) 0时) 高阻态 (当(G 1 G 2 )

【题3.14】指出图3.14中各门电路的输出时什么状态(高电 平、低电平、高阻态)。已知这些门电路都是74系列TTL电 路。

解:

Y1为低电平, Y2为高电平, Y3为高电平, Y4为低电平, Y5为低电平,Y6为高阻态, Y7为高电平, Y8为低电平。

vE

vI 10 vE v I 5.1V 5.1 18

10 5.1V 2.2V 5.1 18

5 10 vE 5 5.1V 1.69V 5.1 18

vE VBE 1.69 0.7 iB A 0.25mA 3 RE 3.97 10

16 mA

V

OH

3.2 V

-0.4mA

V

OL

0.4 V

NL

I OL (max) I IL

16 10 1.6

V

OH

3.2 V

1 IOH (max) 1 0.4 NH 103 5 2 I IH 2 40

V

IH

4V

V

IL

0.4 V

I

IH

20 A

第三章 门电路

解:两种情况下的电压波形图如图A3.4所示。

【题3.7】试分析图3.7中各电路图的逻辑功能,写出输出的 逻辑函数式。

(a)图P3.7(a)电路可划分为四个反相器电路和一个三输 入端的与非门电路,如图所示。从输入到输出逐级写出输出 的逻辑函数式,

A1 A ,B1 B , C1 C , D ( A1B1C1 )

故 R L 的取值范围应为:

0.9k

R

L

31.6k

I

OH ( max )

5A

I

OL( max )

5.2mA

0.33 V

I

OL( max )

Y (A

1 A2 B 1 B 2 C 1C 2 D 1 D 2)

'

R L(max)

V DD VOH 5 4.4 20k 6 6 nI OH mI IH 4 5 10 10 10

【题3.15】说明图P3.15中各门电路的输出是高电平还是低电 平。已知它们都是74HC系列的CMOS电路。

解:Y1为高电平,Y2为高电平,Y3为低电平,Y4为低电 平

V I

OH

3.2 V, V OL 0.4V

40 A。 V OL 0.4V

IH

I

I

OH ( max )

OL( max )