多功能数字计时器

H5CR多功能数字计时器说明书

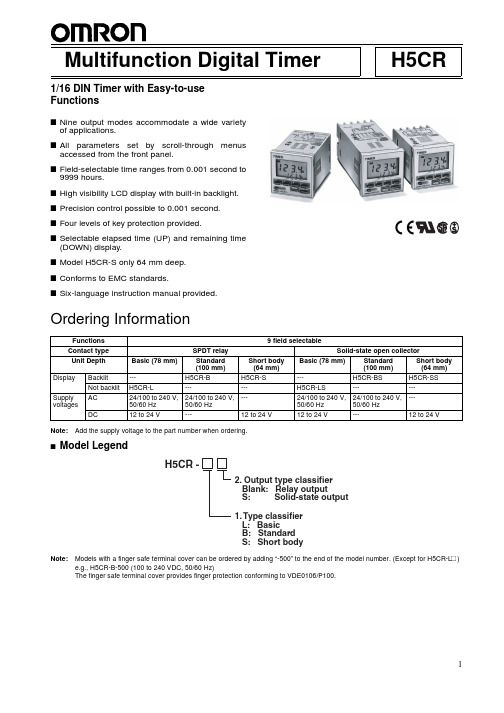

H5CRMultifunction Digital Timer1/16 DIN Timer with Easy-to-use FunctionsI Nine output modes accommodate a wide varietyof applications.I All parameters set by scroll-through menusaccessed from the front panel.I Field-selectable time ranges from 0.001 second to 9999 hours.I High visibility LCD display with built-in backlight.I Precision control possible to 0.001 second.I Four levels of key protection provided.I Selectable elapsed time (UP) and remaining time(DOWN) display.I Model H5CR-S only 64 mm deep.I Conforms to EMC standards.ISix-language instruction manual provided.Ordering InformationNote:Add the supply voltage to the part number when ordering.IModel LegendNote:Models with a finger safe terminal cover can be ordered by adding “-500” to the end of the model number. (Except for H5CR-L #)e.g., H5CR-B-500 (100 to 240 VDC, 50/60 Hz)The finger safe terminal cover provides finger protection conforming to VDE0106/P100.RC+Functions 9 field selectableContact type SPDT relay Solid-state open collectorUnit Depth Basic (78 mm)Standard (100mm)Short body (64mm)Basic (78 mm)Standard (100mm)Short body (64mm)Display Backlit ---H5CR-B H5CR-S---H5CR-BS H5CR-SSNot backlit H5CR-L------H5CR-LS------Supply voltagesAC 24/100 to 240V, 50/60 Hz 24/100 to 240V, 50/60 Hz ---24/100 to 240V, 50/60 Hz 24/100 to 240V, 50/60 Hz ---DC12 to 24 V---12 to 24 V12 to 24 V---12 to 24 VIAccessories (Order Separately)Note:1.Y92A-48G is a finger safe terminal cover which is attached to the P3G-08 Socket.2.Supplied with each Unit.SpecificationsNameModelHard cover Y92A-48Soft coverY92A-48F1Track Mounting/Front Connecting Socket (for H5CR-L # only)---P2CF-08Finger safe type P2CF-08-E Back Connecting Socket (for H5CR-L # only)---P3G-08Finger safe typeP3G-08 with Y92A-48G (see note 1)Finger Safe Terminal Cover for H5CR-B #/-S #Y92A-48T Flush Mounting Adapter (see note 2)Y92F-30ModelH5CR-L (Basic type)H5CR-B (Standard type)H5CR-S (Short body type)Classification Digital timerMountingFlush or Surface mounting Flush mountingExternal connections 8P socket Screw terminals (M3.5 screw)Enclosure ratings IP40IP54 (panel surface)Display modes Elapsed time (UP), remaining time (DOWN)Output modes A, A-1, A-2, A-3, b, b-1, d, E, FReset system Power reset (except A-3, b-1, and F modes), External, manual, automatic resets (internal according to A-1, b, b-1, d, and E mode operation)Input signals Start, reset inputsStart, reset, gate, key protect inputsInput method No-voltage input: Via opening and closing of contactControl outputs SPDT contact output and transistor output (NPN open collector)Display LCD without backlight LCD with backlight Digits4 digitsMax. time settings 9.999 s (0.001 s units), 99.99 s (0.01 s units), 999.9 s (0.1 s unit), 9999 s (1 s unit), 99 min 59 s (1 s unit), 999.9 min (0.1 min unit), 9999 min (1 min unit), 99 hr 59 min (1 min unit), 999.9 hr (0.1 hr unit), 9999 hr (1 hr unit)Memory backup Backup time for power interruption: Approx. 10 years at 20 C Mounting method DIN track mounting, surface mounting, and flush mounting Flush mounting Approved standardsUL508, CSA C22.2 No. 14Conforms to EN61010-1IRatingsICharacteristicsModelH5CR-L (Basic type)H5CR-B (Standard type)H5CR-S (Short body type)Rated supply voltage100 to 240 VAC (50/60 Hz)24 VAC (50/60 Hz)12 to 24 VDC (permissible ripple: 20% max.)100 to 240 VAC (50/60 Hz)24 VAC (50/60 Hz)12 to 24 VDC (permissible ripple: 20% max.)Operating voltage range 85% to 110% of rated voltagePower consumption Approx. 3 VA at 50 Hz, 240 VAC; approx. 1 W at 24 VDCApprox. 5 VA at 50 Hz, 240 VAC Approx. 2 W at 24 VDCReset and control signals Min. pulse width 1 ms/20ms selectable Gate ---Min. pulse width: Approx. 20 ms Key protect ---Response time: 1 sOne-shot time0.1 to 20 s (select from 7 kinds) or sustainedPower reset (except A-3, b-1, and F mode)Min. power opening time: 0.5 s Signal, reset, gate inputsNo-voltage input ON impedance: 1 k W max. (Approx. 2 mA when 0 W )ON residual voltage:2 V max.OFF impedance:100 k W min.Key protect input---No-voltage inputON impedance: 1 k W max. (Approx. 2 mA when 0 W )ON residual voltage:1 V max.OFF impedance:100 k W min.Control outputs Contacts: 5 A at 250 VAC, resistance load (cos f = 1)Transistor output: Open collector 100mA at 30 VDC max. residual voltage 2 V max. (Approx. 1 V)Ambient temperature –10 C to 55 C (with no icing)Storage temperature –25 C to 65 C (with no icing)Ambient humidity 35% to 85%Case Light grayRepeat accuracy (including temperature and voltage effects)Power start: 0.01% 0.05 s max.Control signal start: 0.005% 0.03 s max. *(rate for set value)Insulation resistance 100 M W min. (at 500 VDC) (between current-carrying terminal and exposed non-current-carrying metal parts, and between non-continuous contacts)Dielectric strength 2,000 VAC, 50/60 Hz for 1 min (between current-carrying terminal and exposed non-current-carrying metal parts) for 100 to 240 VAC type 1,000 VAC for 24VAC/12 to 24 VDC transistor output typeSurge voltage3 kV (between power terminals) for 100 to 240 VAC type, 1 kV for 24 VAC/12 to 24 VDC type4.5 kV (between current-carrying terminal and exposed non-current-carrying metal parts) for 100 to 240 VAC type, 1.5 kV for 24 VAC/12 to 24 VDC typeNoise immunity 2 kV (between power terminals)( 480 V for 12 to 24 VDC) and 600 V (between input terminals), square-wave noise by noise simulator (pulse width: 100 ns/1 m s, 1-ns rise)Static immunity Malfunction: 8 kV; destruction: 15 kVVibration Destruction 10 to 55 Hz with 0.75-mm single amplitude each in three directions Malfunction 10 to 55 Hz with 0.5-mm single amplitude each in three directions ShockDestruction 294 m/s 2 (30G) each in three directions Malfunction98 m/s 2 (10G) each in three directions Life expectancy Mechanical 10 million operations min.Electrical100,000 operations min. (5 A at 250 VAC in load resistance)EMC(EMI):EN50081-2Emission Enclosure:EN55011 Group 1 class A Emission AC Mains:EN55011 Group 1 class A (EMS):EN50082-2Immunity ESD:EN61000-4-2: 4 kV contact discharge (level 2)8 kV air discharge (level 3)Immunity RF-interference:ENV50140:10 V/m (80 MHz to 1 GHz) (level 3)Immunity Conducted Disturbance:ENV50141:10 V (0.15 to 80 MHz) (level 3)Immunity Burst:EN61000-4-4: 2 kV power-line (level 3)2 kV I/O signal-line (level 4)WeightH5CR-L: Approx. 105 g, H5CR-B: Approx. 160 g, H5CR-S: Approx. 120 gNomenclatureIFactory SettingsThe following table shows the timer settings when it is shipped. Please change the settings as necessary to suit the system before opera-tion. Settings and the display receive power from the internal battery and are therefore unaffected by external power interruptions.Note:With the initial settings, there will be no output even if the power supply is connected. External inputs and outputs cannot be used without a power supply.1213Model H5CR-B (Standard)/H5CR-S (Short body)H5CR-L (Basic)Time range - -. - -s Present value 0.00 s Presets0.00 s UP/DOWN mode UPOutput mode A: Signal on delay (I)Output time Sustained Input signal time 20 ms Key protect level KP-1---OperationI Block DiagramI I/O FunctionsInputs Start signal Stops timing in A-2 and A-3 (power on delay) modes. Starts timing in other modes.Reset Resets present value (to zero in UP modes, to preset in DOWN mode).Count inputs are not accepted while reset input is ON.Reset indicator lit while reset input is ON.Gate Inhibits timer operation.Key protect Makes keys inoperative according to key protect level.Key protected indicator lit while key protect input is ON.Effective when power supply is turned off.Effective when protect terminals are shorted.Outputs Control output (OUT)Outputs made according to designated output mode when corresponding preset is reached.I Operational OverviewThis flowchart shows operation common to all H5CR models. Refer to the following Setting Item Table for details on the operation of specific models.I Setting Item TableNote: 1.Changes made in setting mode become effective when run mode is entered.2.The time range setting appears first when setting mode is entered.3.*The key protection function is not included in the H5CR-L.<KP-4><KP-3>I ExamplesRun ModeChanging the Set ValueT o change the set value from 3 hr 5 min to 4 hr 5 min, press the 3key so that the number 4 appears in the hour’s place.•Pressing keys 1 through 4 increments the corresponding col-umn by 1.•The columns can be changed in any order, but the output willbe turned ON if the set value is less than the present value.•Nonsignificant zeros are suppressed on the set value display.Note:Read Changing Set Values in the Precautions section,page16, before changing the Timer set value during op-eration.Setting ModeChanging Settings in the Set Mode1.Press the MODE key to switch from run mode to set mode.•The Timer will continue operation if switched from run mode to set mode during operation.•The MODE key will be locked if the key protection function is enabled.•Settings changed in the set mode are not effective until run mode is entered. As the operating conditions will change in this case, always reset operation with the RESET key or a re-set input.2.Press the MODE key to scroll successively through the items that can be set.3.Changing the selected item•Press the MODE key until the desired item appears.•Change the item setting by pressing keys 1 through 4. (Pressthe DISPLAY key to switch back from set mode to run mode.)ITiming ChartsThe gate input is not included in the H5CR-L.Output mode A: Signal ON delay 1 (Timer resets when power comes ON.)Output mode A-1: Signal ON delay 2 (Timer resets when power comes ON.)Output mode A-2: Power ON delay 1 (Timer resets when power comes ON.)Output mode A-3: Power ON delay 2 (Timer does not reset when power comes ON.)Power Start signalGate ResetControl outputSet valueTiming diagramUPDOWNSet valueTiming starts when the start signal goes ON.While the start signal is ON, the timer starts when the power comes ON or when the reset input goes OFF .The control output is controlled using a sustained or one-shot time period.Basic OperationPower**Start signal inputTimingOutput* Output is instantaneous when setting is 0.** Start signal input is disabled during timing.Power Start signalGate ResetControl outputSet valueTiming diagramUPDOWNSet valueTiming starts when the start signal goes ON, and is reset when the start signal goes OFF .While the start signal is ON, the timer starts when the power comes ON or when the reset input goes OFF .The control output is controlled using a sustained or one-shot time period.*Output is instantaneous when setting is 0.Basic OperationPower Start signal inputTimingOutputPower Start signalGate ResetControl outputSet valueTiming diagramUPDOWNSet valueTiming starts when the reset input goes OFF .The start signal disables the timing function (i.e., same function as the gate input).The control output is controlled using a sustained or one-shot time period.*Output is instantaneous when setting is 0.Basic OperationPower TimingOutputPower Start signalGate ResetControl outputSet valueTiming diagramUP DOWNSet valueTiming starts when the reset input goes OFF .The start signal disables the timing function (i.e., same function as the gate input).The control output is controlled using a sustained or one-shot time period.*Output is instantaneous when setting is 0.Basic OperationPower TimingOutputSustainedOutput mode b-1: Repeat cycle 2 (Timer does not reset when power comes ON.)Power Start signalGate ResetControl output* Normal output operation will not be possible if the set time is too short.Set the value to at least 100 ms (contact output ** Start signal input is disabled during timing.TimingTiming Timing Timing Timing starts when the start signal goes ON.The control output is turned ON when time is up.While the start signal is ON, the timer starts when the power comes ON or when the reset input goes OFF .* Normal output operation will not be possible if the set time is too short.Set the value to at least 100 ms (contact output ** Start signal input is disabled during timing.Basic OperationPower Start signal OutputTimingTiming Timing Timing Timing starts when the start signal goes ON.The status of the control output is reversed when time is up (OFF at start).While the start signal is ON, the timer starts when the power comes ON or when the reset input goes OFF .* Normal output operation will not be possible if the set time is too short.Set the value to at least 100 ms (contact output ** Start signal input is disabled during timing.Sustained Basic OperationStart signal TimingTimingTiming starts when the start signal goes ON.The control output comes ON when time is up.While the start signal is ON, the timer starts when power comes ON or when the reset input goes OFF .Basic OperationStart signal * Normal output operation will not be possible if the set time is too short.Set the value to at least 100 ms (contact output ** Start signal input is disabled during timing.Sustained TimingTimingNote:A twin timer can be created by using one of the repeat modes. For example, if the set value is 60 s and the one shot time is 10 s in repeat mode, the control output will turn OFF for 50 s and ON for 10 s. (In the first cycle, however, the control output will turn OFF for 60 s.) In this way, the work of two timers can be performed by a single timer.Output mode E: Interval (Timer resets when power comes ON.)Output mode F: Cumulative (Timer does not reset when power comes ON.)* Output functions only during start signal input when setting is 0.** Start signal input is enabled during timing.Power Start signal OutputTimingTiming starts when the start signal comes ON.The control output is reset when time is up.While the start signal is ON, the timer starts when power comes ON or when the reset input goes OFF .* Output is disabled when the setting is 0.** Start signal input is disabled during timing.Basic OperationPower Start signal OutputTimingStart signal enables timing (timing is stopped when the start signal is OFF or when the power is OFF).A sustained control output is used.* Output is instantaneous when setting is 0.SustainedBasic OperationPower Start signal OutputTimingTiming10 s50 s 60 sDimensionsNote:All units are in millimeters unless otherwise indicated.484884.063.760.714.344.8 x 44.8 484866444.8 x 44.8H5CR-LSurface/Flush Mounting H5CR-BFlush MountingH5CR-S Flush Mounting4848100644.8 x 44.8IDimensions with Y92F-30 Flush Mounting Adapter4858685.95848610092.8AH5CR-BH5CR-SPanel CutoutsPanel cutouts areas shown below.(according to DIN43700).Y92F-30Flush mounting adapterPanel Y92F-30Flush mounting adapterPanel Note 1. The mounting panel thicknessshould be 1 to 4 mm.2. It is possible to mount timers side by side, but only horizontally.H5CR-LP2CF-08584866460 min.60 min.45+0.6-045+0.6-0+10A = {48n - 2.5 + (n -1) x 4}Panel Flush mountingadapter P3G-08Rear surfaceconnection socket44.8 x 44.8With Y92A-48F1 attached.44.8 x 44.8+1A = (51n - 5.5)With Y92A-48 attached.IAccessories (Order Separately)Eight, M3.5 x 7.5 semsT wo, 4.5 dia.holes70 max.50 max.20.3 max.7.83 4.535.44P2CF-08-E (Finger Safe Terminal Type)Conforming to VDE0106/P10050 max.40±0.270 max.M3.5 x 7.5 semsT wo, 4.5 dia. holes7.835.421.5 max.20.31931.35 4.54527 dia.45 4.917Back Connecting SocketP3G-08Terminal Arrangement/Internal Connections (Bottom View)Finger Safe Terminal CoverConforming to VDE0106/P100Y92A-48G(Attachment for P3G-08 Socket)Y92A-48T(Attachment for H5CR-B (/-S ()Hard Cover Y92A-48Soft Cover Y92A-48F1T welve, 6.4 dia. holes3447.7 x 47.748 x 4847.416.524.627.6InstallationI Terminal ArrangementNote:Do not connect unused terminals.I ConnectionsPrecautionsIPower Supplies•The input circuit is not insulated from the power supply circuit.The internal circuit might be damaged by a surrounding AC cir-cuit, so use an insulated AC power supply with equipment con-nected to the input circuit.•If power is interrupted for less than 10 ms, operation will continue normally. If power is interrupted for between 10 and 500 ms, op-eration will be inconsistent, and timing may stop or reset, de-pending on the mode.•Connect the power supply voltage through a relay or switch in such a way that the voltage reaches a fixed value immediately.•Depending on switching frequency, current surges may degrade relay contacts; relays with a capacity greater than 10 A are rec-ommended.IInput and Output•Do not use external sources to increase the voltage of input sig-nals (control signal, reset, gate, and key protection).•Be sure that the load of the control output (contact, transistor) is less than the maximum values indicated in the specifications. If the output load exceeds the recommended value, the life span of the contact output type will be shortened dramatically, and the transistor of the transistor output type will be damaged.•The transistor output is insulated from the internal circuitry by a photocoupler, so either NPN or PNP transistors can be used.ISelf-diagnostic Function•The following displays will appear if an error occurs. The present value and output enter the same status as after pressing the RE-SET key.IChanging Set Values•The Timer set value can be changed while the timer is operating,so a high value can be set temporarily to inactivate the timer, or a low value can be set to activate the timer more quickly. (If the set value is changed accidentally during operation, the timer might be activated. Therefore, turn the key protection input ON unless the set value is being changed.)•To avoid changing the output when changing the set value, it is recommended to begin changing the set value by entering a large number in the higher digit.IOperation with a Set Value of 0•Operation with a set value of 0 will vary depending on the output mode. For details, refer to Timing Charts.IOperating Environment•When using the Timer in an area with much electronic noise,separate the Timer, wiring, and the equipment which generates the input signals as far as possible from the noise sources. It is also recommended to shield the input signal wiring to prevent electronic interference.•Organic solvents (such as paint thinner), as well as very acidic or basic solutions might damage the outer casing of the Timer.IOther•When the Timer is installed in a control box and tests are con-ducted which may damage the Timer ’s internal circuitry (for ex-ample, a test measuring the maximum voltage difference between the control circuit and metal components), remove the Timer from the control box or short circuit the terminals.&DXWLRQThis product contains a lithium battery. Lithium batteries ex-plode if incinerated. Dispose of the Digital Timer as a non-com-bustible item.DisplayError Output status CorrectionSetCPU OFFPress RESET keyNo change MemorySet at the factoryA AIn the interest of product improvement, specifications are subject to change without notice.ALL DIMENSIONS SHOWN ARE IN MILLIMETERS.To convert millimeters into inches, multiply by 0.03937. T o convert grams into ounces, multiply by 0.03527.Cat. No. L035-E1-4B OMRON CorporationIndustrial Automation CompanyMeasuring and Supervisory Controls Department Shiokoji Horikawa, Shimogyo-ku Kyoto, 600-8530 JapanT el: (81)75-344-7108/Fax: (81)75-344-7189Printed in Japan 0401-1.5C。

数字电子计时器

数字电子计时器吴东城(常州工学院计算机信息工程学院10计一,江苏常州213002)摘要:该数字电子计时器是用数字电路技术实现时、分、秒计时的装置,具有计时及校时功能。

该数字电子计时器的时间周期为24小时,计时器显示时、分、秒,计时器的时间对应现实生活中的时钟的一秒。

根据日常生活中的观察,数字电子计时器设计成型后供扩展的方面很多——涉及到定时自动报警、按时自动打铃、定时广播、定时启闭路灯等。

因此,与机械式时钟相比具有更高的可视性和精确性,而且无机械装置,具有更长的使用寿命,所以研究数字钟及扩大其应用,有着非常现实和实际的意义。

数字电子计时器是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

目前,数字钟的功能越来越强,并且有多种专门的大规模集成电路可供选择。

但从知识储备的角度考虑,本设计是以中小规模集成电路设计数字钟的一种方法。

数字钟包括组合逻辑电路和时序电路关键词:计时器;计数器;校时;组合逻辑电路;时序逻辑电路;译码。

0 概述0.1课题的现状:由于该课题应用较为普遍,所以实现方法很多。

基于单片机原理实现,用数字电路实现,用EDA技术实现,还可用F201448技术工艺,当然,还可以通过编程实现。

0.2本课题设计的目的、意义:数字电子计时器是一种用数字电路技术实现时、分、秒计时的装置,与机械式计时器相比具有更高的准确性和直观性,企且无机械装置,具有更长的使用寿命,因此应该得到广泛使用。

本次课程设计的目的,就是为了了解数字电子计时器的原理,从而学会制作数字电子计时器,而且通过计时器的制作机一部了解各种在制作中用到的中小规模集成电路的作用及实用方法,且由于数字电子计时器包括组合逻辑电路和时序逻辑电路,通过它可以进一步学习和掌握两种电路的原理与使用方法。

0.3课题内容、要求、达到的性能指标:(1)根据计时器的方框图和指定器件,完成计时器的主体电路设计及实验;(2)利用异步时序电路的方法,设计一个24进制的时空电路,要求当计数器运行到23时59分59秒是,秒个位计数器在接受一个秒脉冲信号后,计数器自动显示为00时00分00秒,完成进制的计时要求;(3)具有校时、分、秒;(4)在实验板上安装、调试出课题所要求的计时器;(5)画出逻辑电路图,时序图,并写出报告。

二十四小时计时器南理工EDAquartus应用

实验一 二十四小时数字计时器、实验内容及题目简介利用QuartusII 软件设计一个数字钟,并下载到SmartSOPC 实验系统中,可以完成00:00:00到23:59:59的计时功能,并在控制电路的作用下具有保持、清零、快速校 时、快速校分、整点报时等功能。

、实验设计要求(1)设计基本要求(2)设计提高部分要求1、使时钟具有整点报时功能(当时钟计到59' 53”时开始报时,在59' 53” , 59 '55” ,59 ' 57”时报时频率为512Hz,59' 59”时报时频率为1KHz,); 2、闹表设定功能; 3、自己添加其他功能;三、方案论证数字钟整体框图如下图所示1、能进行正常的时、分、秒计时功能; 2、3、 分别由六个数码管显示时分秒的计时; K1是系统的使能开关(K 仁0正常工作, K1=1时钟保持不变);4、5、 K2是系统的清零开关(K2=0正常工作, K3是系统的校分开关(K3=0正常工作,K2=1时钟的分、秒全清零); K3=1时可以快速校分); 6、 K4是系统的校时开关(K4=0正常工作, K4=1时可以快速校时);本实验的目的是利用QuartusII软件设计一个多功能的数字计时器,使该计时器具有计时,显示,清零,较分,校时及整点报时功能。

依据上述数字钟电路结构方框图可知,秒计时器和分计时器均为60进制,小时计时器是24进制计数器。

当秒计时器对1HZ时钟脉冲信号计数到60时,产生一个进位脉冲,使分计时器的数值加1,同样,分计时器计数到60时,使小时计时器的数值加一。

秒计数模块和分计数模块的核心是模60的计数器,时计数模块的核心为模24的计数器,并且采用同步计数的方法,即三个模块的时钟信号均来自同一个频率信号。

当数字钟走时出现误差时,通过校时电路对时,分的时间进行校正,其中校时电路和清零电路只需在原有电路的基础上采用一定的逻辑门电路实现。

多功能数字电子钟设计

数字逻辑课程设计-多功能数字电子钟多功能数字钟的设计与仿真一.设计任务与要求设计任务:设计一个多功能数字钟。

要求:1.有“时”、“分”、“秒”(23小时59分59秒)显示且有校时功能。

(设计秒脉冲发生器)2.有整点报时功能。

(选:上下午、日期、闹钟等)3. 用中规模、小规模集成电路及模拟器件实现。

4. 供电方式: 5V直流电源二.设计目的、方案及原理1.设计目的(1)熟悉集成电路的引脚安排。

(2)掌握各芯片的逻辑功能及使用方法。

(3)了解面包板结构及其接线方法。

(4)了解多功能数字钟的组成及工作原理。

(5)熟悉多功能数字钟的设计与制作2.设计思路(1)设计数字钟的时、分、秒电路。

(2)设计可预置时间的校时电路。

(3)设计整点报时电路。

3.设计过程3.1.总体设计方案及其工作原理为:数字钟原理框图入图1所示,电路一般包括一下几个部分:振荡器、星期、小时、分钟、秒计数器、校时电路、报时电路。

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。

由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定。

通常使用石英晶体振荡器电路构成数字钟,但也可以用555定时器构成。

图1 系统框图数字钟计时的标准信号应该是频率相当稳定的1HZ秒脉冲,所以要设置标准时间源。

数字钟计时周期是24小时,因此必须设置24计数器,秒、分、时由数码管显示。

ﻫ为使数字钟走时与标准时间一致,校时电路是必不可少的。

设计中采用开关控制校时电路“时”“分”“秒”计数器进行校时操作。

3.2.各独立功能部件的设计(1)分、秒计时器(60进制),时计数器(24进制),星期计数器(7进制)如下图,图中蓝色线为高电平+5v,绿色为接地线,红色线为时钟脉冲。

获得秒脉冲信号后,可根据60秒为一分,60分为一小时,24时为一个计数周期的计数规则,分别确定秒、分、时的计数器。

由于秒和分的显示都为60进制,因此他们可有两级十进制计数器组成,其中秒和分的个位为十进数器,十位为六进制计数器,可利用两片74160集成电路来实现。

WMF数字快速计时器说明书

数字定时器Stellen Sie durch Drücken des MIN und SEC Felds die gewünschte Zeit ein. Drücken Sie die START/STOP Taste um den Kurzzeitmesser zu starten.Durch Drücken der START/STOP Taste können Sie die Zeit unterbrechen und wieder starten.Durch gleichzeitiges Drücken der MIN und SEC setzen Sie die Zeit auf 00:00 zurück.Wenn Sie bei 00:00 die START/STOP Taste drücken, läuft die Zeit vor-wärts und Sie können den Kurzzeitmesser als Stoppuhr nutzen.Bei Nichtgebrauch erlischt das Display nach kurzer Zeit.Bitte beachten Sie Den Kurzzeitmesser keinen extremen Temperaturschwankungen ausset-zen. Verschmutzungen mit einem feuchten Tuch abwischen.CE-Konformität Dieses Gerät ist funkentstört entsprechend der geltenden EG-Richtlinie 004/108/EG.Hinweis: Unter extremen elektromagnetischen Einflüssen, z.B. bei Betreiben eines Funkgerätes in unmittelbarer Nähe des Kurzzeitmessers, kann eine Beeinflussung des Anzeigewertes verursacht werden. Nach Digitaler KurzzeitmesserTechnische DatenMaximale Zeiteinstellung: 99 min und 59 secEin-/Abschaltknopf auf der RückseiteZwei 1,5 V Batterien AAA (im Lieferumfang enthalten)Bitte lesen Sie die Bedienungshinweise vollständig durch, bevor Sie den Kurzzeitmesser zum ersten Mal benutzen.Bewahren Sie die Anleitung zum Nachlesen bitte sorgfältig auf.Falls Sie den Kurzzeitmesser an einen anderen Benutzer weitergeben, händigen Sie ihm die Anleitung zusammen mit dem Produkt aus.Vor dem ersten GebrauchÖffnen Sie den Batteriefachdeckel auf der Rückseite und entnehmen Sie die Batterien. Entfernen Sie die Schutzfolie und legen Sie die Batterien entsprechend der Polaritätszeichen wieder ein. Schließen Sie den Deckel. Hinweise zur BedienungStellen Sie den kleinen Schieber auf der Rückseite auf ON.Der Touch Screen reagiert auf Berührung.stelle für das Recycling von elektrischen und elektroni- schen Geräten abgegeben werden muss. Weitere Informa- tionen erhalten Sie über Ihre Gemeinde, die kommunalen Entsorgungs-betriebe oder das Geschäft, in dem Sie das Produkt gekauft haben.Sicherheitshinweise für Lithiumbatterien (CR2032/CR2430)• Bei Lithiumbatterien handelt es sich um Lithium-Mangan-Zellen. Wenn Sie den Kurzzeitmesser über einen längeren Zeitraum nicht benutzen, sollten Sie die Batterien aus dem Gerät nehmen.• Bitte nie die Lithiumbatterien öffnen, ins Feuer werfen oder Stößen aussetzen, da möglicherweise giftige Dämpfe austreten oder Explosi-onsgefahr besteht.• Fassen Sie ausgelaufene Zellen nie mit bloßen Händen an.• Bei Kontaminierung der Augen oder Hände unbedingt mit viel Wasser spülen, bei Reizungen der Haut oder Augen sollten Sie einen Arzt aufsuchen.• Entsorgen Sie nur vollständig entladene oder verpolungssicher ver-packte Zellen, entsprechend den örtlichen Entsorgungsvorschriften.• Setzen Sie die Zellen nicht direkter Sonneneinstrahlung und großer Hitze aus, da ansonsten die Gefahr von Überhitzung besteht. Halten Sie eine Lagertemperatur von < 40°C ein.Ende des Störeinflusses ist das Produkt wieder bestimmungsgemäß benutzbar, ggfls. ist ein Wiedereinschalten erforderlich.Gesetzliche Hinweispflicht zur EntsorgungAltbatterienBatterien gehören nicht in den Hausmüll. Als Verbrauchersind Sie gesetzlich dazu verpflichtet, gebrauchte Batterienzurückzugeben. Sie können Ihre alten Batterien bei den öf-fentlichen Sammelstellen in Ihrer Gemeinde oder überall dortabgeben, wo Batterien der betreffenden Art verkauft werden.Hinweis:Diese Zeichen finden Sie auf Batterien:Li = Batterie enthält LithiumAl = Batterie enthält AlkaliMn = Batterie enthält ManganCR (Li); AA (Al, Mn); AAA (Al, Mn)Elektrische/Elektronische GeräteDas Symbol auf dem Produkt oder seiner Verpackung weistdarauf hin, dass dieses Produkt nicht als normaler Haus-haltsabfall zu behandeln ist, sondern an einer Annahme-The touch screen reacts to contact. Set the desired time by pressing the MIN and SEC field. Press the START/STOP button to start the cooking timer.By pressing the START/STOP button you can stop and restart the timing process.Pressing MIN and SEC simultaneously will reset the time to 00:00.If you press the START/STOP button when the display reads 00:00, the time starts to run and you can use the cooking timer as a stopwatch.When not in use the display goes out after a short period of time.Please note Do not expose the cooking timer to any extreme fluctuations in temperature. Wipe off marks with a damp cloth.CE conformity This device is shielded from interference and voltage peaks in accord-ance with the applicable EC Directive 004/108/EC. Note: under extreme electromagnetic influences, for instance when a radio is operated in the immediate vicinity of the cooking timer, the readout may be affected. The product can be used again normally once the disruptive influence is no longer present, although it may be necessary to switch it back on.Digital cooking timerTechnical dataMaximum time setting: 99 mins and 59 secsOn/off button on the backTwo 1.5 V AAA batteries (included in the delivery)Please read the instructions for use thoroughly before using the cook-ing timer for the first time.Please keep the instructions in a safe place for subsequent reference. If you pass on the cooking timer to another user, give him the instruc-tions along with the product.Before using for the first timeOpen the battery compartment on the back and remove the batteries. Remove the protective film and replace the batteries, observing the polarity signs. Close the lid.How to use the cooking timerPosition the small slider on the back to ON.Safety instructions for lithium batteries (CR2032/CR2430)• Lithium batteries contain lithium-manganese cells. The batteries should be removed from the device if you will not be using the cooking timer for a long period of time.• Never open the lithium batteries, discard them into a fire or subject them to any impact as toxic vapours may escape as a result and there is also the risk of the batteries exploding.• Never touch discharged batteries with your bare hands.• In the event of contamination of the eyes or skin, immediately rinse with plenty of water, you should seek medical advice if the eyes or skin become irritated.• Only dispose of completely discharged batteries or batteries pa-ckaged so as to protect against reverse polarity, and in accordance with the local disposal regulations.• Do not expose the batteries to direct sunlight or extreme heat, as otherwise there is the danger of overheating.• Ensure the storage temperature is < 40°C.Obligatory legal notification regarding disposalUsed batteriesBatteries should not be placed with household refuse. As aconsumer, you are legally obliged to return used batteries.You can leave used batteries at the public collection pointsin your community or hand them in wherever batteries ofthe type in question are sold.Note:You will find these letters on batteries:Li = battery contains lithiumAl = battery contains an alkaliMn = battery contains manganeseCR (Li); AA (Al, Mn); AAA (Al, Mn)Electric/electronic devicesThe symbol on the product or its packaging indicates that this product must not be treated as normal household waste, but must be taken to a collection point for the recycling of electric and electronic devices. Further information can be obtained from your community, the munici-pal disposal operators or the shop where you bought the product.L‘écran tactile réagit au toucher. Fixez le temps souhaité en appuyant sur les champs MIN et SEC. Appuyez sur la touche START/STOP pour démarrer le minuteur.En appuyant sur la touche START/STOP, vous pouvez interrompre le temps et redémarrer.En appuyant simultanément sur MIN et SEC, vous remettez le compteur à zéro.Si vous appuyez sur la touche START/STOP à 00:00, le temps commence à s‘écouler et le minuteur peut vous servir de chronomètre.En cas de non utilisation, l‘écran s‘éteint au bout d‘un court instant.Attention N‘exposez pas le minuteur à des écarts de températures extrêmes.Essuyez les saletés à l‘aide d‘un chiffon humide.Conformité CE Cet appareil est antiparasité conformément à la directive 004/108/CE en vigueur.Consigne : L‘influence électromagnétique extrême, par ex. une radio en service à proximité immédiate du minuteur, peut affecter la valeur affichée. Une fois ces perturbations terminées, le produit est à nouveau Minuteur numériqueCaractéristiques techniquesRéglage du temps maximum : 99 min et 59 secBouton marche/arrêt sur la face arrièreDeux piles AAA de 1,5 V (comprises dans la livraison)Veuillez lire attentivement les conseils d‘utilisation avant d‘utiliser le minuteur pour la première fois.Conservez précieusement le mode d‘emploi après l‘avoir lu.Si vous confiez le minuteur à un autre utilisateur, remettez-lui aussi le mode d‘emploi.Avant la première utilisationOuvrez le couvercle du compartiment à piles sur la face arrière et retirez les piles. Retirez la pellicule de protection et reposez la pile en respectant les signes de polarité. Fermez le couvercle.Conseils d‘utilisationRéglez le petit curseur sur ON sur la face arrière.électroniques. Vous obtiendrez des informations plus détaillées auprès de votre commune, des déchetteries communales ou du magasin où vous avez acheté le produit.Consignes de sécurité pour les piles en lithium (CR2032/CR2430)• Pour les piles en lithium, il s‘agit de la catégorie lithium-manganèse. Si vous n‘utilisez pas le minuteur pendant une longue période, il vaut mieux enlever les piles de l‘appareil.• N‘ouvrez jamais les piles en lithium, ne les jetez pas au feu et ne les exposez pas à des chocs car vous multipliez les risques d‘explosion ou que des vapeurs toxiques se dégagent.• N‘attrapez pas les piles usées à mains nues.• Rincez immédiatement à grande eau en cas de contamination des yeux ou des mains et en cas d‘irritation de la peau ou des yeux, nous vous invitons à consulter un médecin.• Éliminez uniquement des piles emballées selon la bonne polarité et complètement déchargées conformément aux prescriptions d‘élimination.• N‘exposez pas les piles aux rayons directs du soleil ou à une forte chaleur car elles risquent de se surchauffer.• Maintenez une température de stockage < 40 °C.opérationnel et un redémarrage serait judicieux, le cas échéant.Obligation légale d‘éliminationPiles usagéesLes piles ne se jettent pas dans les ordures ménagères. Entant que consommateur, vous êtes légalement tenus derestituer les piles usagées. Vous pouvez déposer vos pilesusagées dans les centres de collecte publics de votre com-mune ou auprès de n‘importe quel point de vente de pilesdu même type.Consigne :Vous trouverez ces caractères sur les batteries :Li = la pile contient du lithiumAl = la pile contient de l‘alcaliMn = la pile contient du manganèseCR (Li) ; AA (Al, Mn) ; AAA (Al, Mn)Appareils électriques/électroniquesLe symbole sur le produit ou son emballage indique que le produit ne doit pas être traité comme les ordures ménagères et doit être remis à un centre de collecte pour le recyclage des appareils électriques etLa pantalla táctil reacciona al tocarla. Ajuste el tiempo deseado pulsando los campos de MIN y SEC. Pulse la tecla START/STOP para activar el avisador de cocina.Al pulsar la tecla START/STOP, podrá parar y volver a iniciar el tiempo.Si pulsa al mismo tiempo MIN y SEC, el tiempo volverá a ponerse a 00:00.Si pulsa la tecla START/STOP con el tiempo a 00:00, este comenzará a contar hacia delante y podrá utilizar el avisador como temporizador.Si tras un breve periodo de tiempo la pantalla no se utiliza, se apaga.Atención No exponga al avisador de cocina a cambios extremos de temperatura.Limpie la suciedad con un paño húmedo.Conformidad CE Este aparato no interfiere en las ondas electromagnéticas, de conformi-dad con la normativa vigente CE 004/108/CE. Advertencia: bajo cargas extremas electromagnéticas, como por ejemplo el funcionamiento de una radio al lado del avisador de cocina, podría producirse una interferencia en el valor del indicador. Una vez eliminada la interferencia, ya puede volver a utilizar el aparato confor-Avisador de cocina digitalDatos técnicosAjuste temporal máximo: 99 min y 59 sBotón de conexión/desconexión en la parte traseraDos pilas de 1,5 V AAA (incluidas en el envío)Léase las indicaciones de manejo al completo antes de utilizar elavisador de cocina por primera vez. Guárdese las instrucciones de forma segura para una posterior consulta y lectura.Si va a pasar el avisador de cocina a otro usuario, no olvide entregarle también las instrucciones de uso junto con el producto.Antes del primer usoAbra la tapa del compartimento de pilas colocada en la parte trasera y sá- quelas. Elimine el adhesivo protector y vuelva a introducir las pilas tenien-do en cuenta los correspondientes símbolos de polaridad. Cierre la tapa. Indicaciones de usoColoque el pequeño cursor de la parte trasera en posición ON.municipal de basuras y eliminación o en el comercio donde adquirió el producto.Advertencias de seguridad para pilas de litio (CR2032/CR2430)• Las pilas de litio son células de litio y manganeso. Si no va a utilizar el avisador de cocina durante un largo tiempo, es recomendable que saque las pilas del aparato.• No abra nunca las pilas de litio, ni las arroje al fuego o las agujere, ya que es posible que salga gas tóxico e incluso exista peligro de explosión.• No toque nunca las pilas con líquido derramado con las manos desnudas.• En caso de contacto con ojos o manos, lávese inmediatamente con agua abundante y si aparece irritación en la piel o los ojos consulte al médico.• Deposite en la basura solo las pilas completamente descargadas o las envueltas en seguridad de polarización según las normativas de eliminación locales vigentes.• No exponga nunca las pilas a la luz solar directa o a una fuente de calor elevada ya que existe peligro de sobrecalentamiento.• Almacenar a una temperatura inferior a 40 ºC.me a su uso; a veces es necesario reiniciarlo.Obligación legal de advertencia para la eliminaciónPilas usadasLas pilas no pueden depositarse en la basura doméstica.Como consumidor, usted está obligado por la ley a devolverlas pilas usadas. Puede depositar sus pilas usadas en puntosoficiales de recogida de su municipio o dejarlas en cualquiercomercio que venda pilas de esa clase.Nota:En las pilas encontrará estos símbolos:Li = la pila contiene litioAl = la pila contiene metal alcalinoMn = la pila contiene manganesoCR (Li); AA (Al, Mn); AAA (Al, Mn)Aparatos eléctricos y electrónicosEl símbolo colocado en el producto o en su envase indica que no debe tratarse como si fuera un residuo normal doméstico, sino que debe lle-varse a un punto de recogida para el reciclaje de aparatos electrónicos yeléctricos. Podrá obtener más información en su ayuntamiento, oficinaIl touchscreen reagisce al contatto. Impostare il tempo desiderato premendo su MIN e SEC. Premere il tasto START/STOP per azionare il timer da cucina.Premendo il tasto START/STOP è altresì possibile interrompere e ripren-dere il conteggio.Premendo contemporaneamente i tasti MIN e SEC, il timer da cucina viene resettato su 00:00. Impostato su 00:00, il timer da cucina può es-sere utilizzato come cronometro, premendo i tasti START/STOP. In caso di non utilizzo, il display si spegne automaticamente dopo alcuni istanti.AttenzioneNon esporre il timer a oscillazioni estreme di temperatura.Rimuovere lo sporco con un panno umido.Conformità CEQuesto dispositivo è radioschermato in conformità alla direttiva CE vigente: 004/108/CE.Nota: a causa di influssi elettromagnetici estremi, per esempio attivan-do un apparecchio radio nelle immediate vicinanze del timer da cucina, è possibile che il valore visualizzato subisca delle alterazioni. Terminata l’interferenza, il prodotto è di nuovo utilizzabile secondo gli scopi edTimer digitale da cucinaDati tecniciTempo massimo impostabile: 99 min e 59 sec.Pulsante di attivazione/disattivazione del timer, posizionato nella parte posteriore. Due batterie di tipo AAA, da 1,5 V (incluse nella fornitura).Leggere attentamente le istruzioni per la manutenzione prima di iniziare a utilizzare il timer da cucina. Conservare scrupolosamente il presente manuale per consultazioni future.Se il timer da cucina viene ceduto a un altro utente, quest’ultimo deve entrare in possesso anche del relativo manuale.Prima dell’uso inizialeAprire il coperchio del vano batterie sul lato posteriore, quindi prendere le batterie. Rimuovere la pellicola di protezione e riposizionare le batte-rie rispettando la polarità. Chiudere il coperchio. Consigli per l‘usoPosizionare il piccolo pulsante posteriore su ON.2120più dettagliate è possibile rivolgersi all’ufficio comunale, al servizio locale di smaltimento dei rifiuti oppure al nego-zio in cui è stato acquistato il prodotto.Indicazioni di sicurezza per le batterie al litio (CR2032/CR2430)• Per “batteria al litio” si intende una batteria a bottone litio-manga-nese. Si consiglia di rimuovere le batterie dell’apparecchio in caso di non utilizzo prolungato del timer da cucina.• Non aprire in nessun caso le batterie al litio, non gettarle nel fuoco e non esporle a sollecitazioni di alcun genere poiché si potrebbero sprigionare vapori velenosi o verificare rischi di esplosione.• Non afferrare mai a mani nude le batterie con perdite.• In caso di contatto con gli occhi o le mani, risciacquare con molta acqua. In presenza di irritazioni cutanee o oculari si consiglia di contattare un medico.• Smaltire le batterie a bottone completamente esaurite o imballate per impedire l’inversione delle polarità, in conformità alle disposizio-ni locali in materia di smaltimento.• Non esporre le batterie a bottone alla luce diretta del sole e a tempe-rature molto elevate perché altrimenti si rischia il surriscaldamento.• Rispettare la temperatura di stoccaggio inferiore a 40 °C.eventualmente è necessaria una sua riaccensione.Obbligo di avviso secondo la legge sulle batterie Batterie esauriteLe batterie esaurite non devono essere considerate rifiuti domestici. Il consumatore è tenuto per legge alla restituzio-ne delle batterie scariche. È possibile restituire gratuita-mente le batterie usate al proprio rivenditore o consegnarle ai centri di raccolta comunali.Nota:sulle batterie sono riportate le seguenti sigle:Li = la batteria contiene litio Al = la batteria contiene alcaliMn = la batteria contiene manganese CR (Li); AA (Al, Mn); AAA (Al, Mn)Dispositivi elettrici/elettroniciQuesto simbolo sul prodotto o sulla confezione indica che il prodotto non deve essere considerato come un normale rifiuto domestico, ma deve invece essere consegnato a un punto di raccolta appropriato peril riciclo di apparecchi elettrici ed elettronici. Per ricevere informazioni2322同时点击 MIN 和 SEC 按键将时间重置到 00:00。

多功能光电计时器操作说明简表与使用说明书

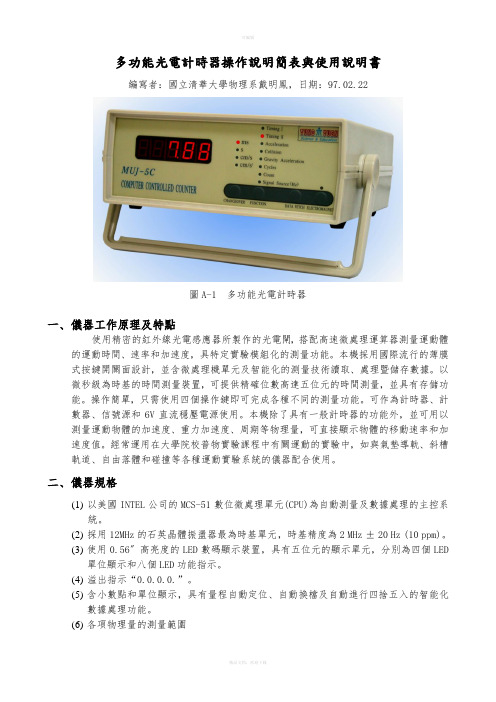

多功能光電計時器操作說明簡表與使用說明書編寫者:國立清華大學物理系戴明鳳,日期:97.02.22圖A-1 多功能光電計時器一、儀器工作原理及特點使用精密的紅外線光電感應器所製作的光電閘,搭配高速微處理運算器測量運動體的運動時間、速率和加速度,具特定實驗模組化的測量功能。

本機採用國際流行的薄膜式按鍵開關面設計,並含微處理機單元及智能化的測量技術讀取、處理暨儲存數據。

以微秒級為時基的時間測量裝置,可提供精確位數高達五位元的時間測量,並具有存儲功能。

操作簡單,只需使用四個操作鍵即可完成各種不同的測量功能。

可作為計時器、計數器、信號源和6V直流穩壓電源使用。

本機除了具有一般計時器的功能外,並可用以測量運動物體的加速度、重力加速度、周期等物理量,可直接顯示物體的移動速率和加速度值。

經常運用在大學院校普物實驗課程中有關運動的實驗中,如與氣墊導軌、斜槽軌道、自由落體和碰撞等各種運動實驗系統的儀器配合使用。

二、儀器規格(1)以美國INTEL公司的MCS-51數位微處理單元(CPU)為自動測量及數據處理的主控系統。

(2)採用12MHz的石英晶體振盪器最為時基單元,時基精度為2 MHz ±20 Hz (10 ppm)。

(3)使用0.56〞高亮度的LED數碼顯示裝置,具有五位元的顯示單元,分別為四個LED單位顯示和八個LED功能指示。

(4)溢出指示“0.0.0.0.”。

(5)含小數點和單位顯示,具有量程自動定位、自動換檔及自動進行四捨五入的智能化數據處理功能。

(6)各項物理量的測量範圍(a)速度範圍為:0.00~1000.0 cm/s(b)加速度範圍為:±0.00~1200.0 cm/s2(c)計數範圍為:0~99999(d)計時範圍為:0.00 ms~999.99 s(e)0.01 ms數量級以上確保五位有效數字顯示。

(7)可存儲20個時間數據,在周期測量中存儲21個時間數據(前20個振動周期和一個n次(最多9999周期)振動的累加時間總和。

多功能数字计时器实验报告.

多功能数字计时器实验报告姓名:***学号:************专业:信息对抗指导老师:***实验时间:2015年9月18日目录1.电路基础功能设计要求介绍2.电路原理简介3.单元电路设计3.1脉冲发生电路3.2计时电路3.3译码显示电路3.4清零电路3.5校分电路3.6报时电路4.总电路图5.拓展电路5.1启停电路5.2动态显示电路6.附录6.1元件清单6.2芯片引脚图和功能表7.实验感受与体会8.参考文献一、电路基础功能设计要求介绍设计制作一个0分00秒~9分59秒的多功能计时器,设计要求如下:a.设计一个脉冲发生电路,为计时器提供秒脉冲(1HZ),为报时电路提供驱动蜂鸣器的高低脉冲信号(1KHZ、2KHZ);b.设计计时电路:完成0分00秒~9分59秒的计时、译码、显示功能;c.设计清零电路:具有开机自动清零功能,并且在任何时候,按动清零开关,可以对计时器进行手动清零.d.设计校分电路:在任何时候,拨动校分开关,可进行快速校分.(校分隔秒)e.设计报时电路:使数字计时器从9分53秒开始报时,每隔一秒发一声,共发三声低音,一声高音;即9分53秒、9分55秒、9分57秒发低音(频率1kHz),9分59秒发高音(频率2kHz)f.系统级联.将以上电路进行级联完成计时器的所有功能.二、电路原理简介工作原理:由振荡器产生的稳定的高频脉冲信号,作为数字钟的时间基准,再经分频器输出标准秒脉冲.秒个位计数器记满10后向秒十位计数器进位,秒十位计满6后向分进位同时置零. 计数器的输出经译码器送显示器.记时出现误差时可以用校时电路进行校分.扩展电路必须在主体电路正常运行的情况下才能进行功能扩展。

数字计时器由计时电路、译码显示电路、脉冲发生电路、校分电路、清零电路和报时电路这几部分组成。

其原理框图如下:三、单元电路设计1.脉冲发生电路脉冲信号发生电路完成为计时电路提供计数脉冲的功能。

实验中采用32768Hz的石英- 4 - 晶体多谐振荡器作为脉冲信号源。

数字计时器

电工电子综合实验报告—数字计时器院系:电光学院专业:通信工程班级:07042201学号:0704220100姓名:* * *指导教师:李元浩时间:2009.09.17—2009.09.20目录1.设计电路功能要求(1)2.设计电路原理图(1)3.电路逻辑原理图及工作原理(2)4.各单元电路原理及逻辑设计4.1脉冲发生电路(2-3)4.2计时电路(3-4)4.3显示电路(4)4.4清零电路(5)4.5校分电路(5)4.6报时电路(6)5.电路安装与调试说明(6-7) 6.对电路的改进意见(7)7.收获体会及建议(7)8.设计参考资料(7)9.附录(8-10)1.设计电路功能要求本实验要求设计一个0分00秒-9分59秒的多功能数字计时器。

数字计时器是由脉冲发生电路,计时电路,译码显示电路,和控制电路等几部分组成。

其中控制电路由清零电路,校分电路,和报时电路组成。

该数字计时器可以在控制电路的作用下具有开机清零、手动清零、快速校分和整点报时功能。

①.设计一个脉冲发生电路,为计时器提供秒脉冲,为报时电路提供驱动蜂鸣器发声的脉冲信号;②.设计计时和显示电路,将分及秒的个位、十位分别在七段显示器上显示出来,从0分0秒开始,计到9分59秒,然后重新计数。

将分及秒的个位、十位分别在七段显示器上显示出来,七段显示器循环显示数字000~959;③.设计清零电路,实现手动及开机清零;④.设计校分电路,在校分开关控制下实现分校正;⑤.设计报时电路,使数字计时器实现在9分53秒、9分55秒、9分57秒低音(1KHz)报时,以及在9分59秒高音(2KHz)报时;2.设计电路原理图图2-1 电路原理图3.电路逻辑原理图及工作原理数字计时器的原理方框图如图3-1所示,该电路系统由脉冲发生电路、计时和显示电路、清零电路、校分电路和报时电路和其它附加电路等几部分组成的。

脉冲发生电路由振荡器和分频器组成,振荡器产生稳定的高频脉冲信号,作为数字钟的时间基准,再经分频器输出标准的秒脉冲,同时也可得到其他不同频率的脉冲。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电工电子综合试验( )多功能数字计时器设计姓名:学号:专业:通信工程学院:电子工程与光电技术学院指导老师:完成时间:目录一、设计内容简介 (3)二、设计要求 (3)三、设计原理 (3)1、整体电路设计原理 (3)2、各部分电路的设计及原理 (4)(1)脉冲电路 (4)(2)计时电路 (5)(3)译码显示电路 (6)(4)清零电路 (7)(5)校分电路 (8)(6)报时电路 (9)3、附加电路:起停电路设计及原理(7分57秒自动停止5秒) .. 94、电路仿真波形 (10)四、实验中遇到的问题及解决方法 (12)五、实验心得 (13)六、附录 (14)1、器件清单 (14)2、各元件的引脚图及功能表 (14)3、总电路图 (18)4、参考文献 (19)一、设计内容简介本实验采用中小规模集成电路设计一个数字计时器。

要求可以完成0分00秒~9分59秒的计时功能,并在控制电路的作用下具有开机清零,快速校分,整点报时的功能。

数字计时器是由脉冲发生电路,计时电路,译码显示电路,和控制电路等几部分组成。

其中控制电路由清零电路,校分电路和报时电路组成。

二、设计要求1、设计一个脉冲发生电路,为计时器提供秒脉冲、为报时电路提供驱动蜂鸣器的脉冲信号。

2、设计一个计时电路,完成0分00秒~9分59秒的计时功能。

3、设计报时电路,使数字计时器从9分53秒开始报时,每隔一秒发一声,共发三声低音,一声高音;即9分53秒、9分55秒、9分57秒发低音(频率1kHz),9分59秒发高音(频率2kHz)。

4、设计校分电路,在任何时候,拨动校分开关,可以2HZ进行校分。

5、设计清零电路,具有开机自动清零功能,并且在任何时候,按动清零开关,可以进行计时器清零。

6、系统级联调试,将以上电路进行级联完成计时器的所有功能。

7、可增加数字计时器附加功能,例如数字计时器定时功能、电路起停功能、电路采用动态显示等。

三、设计原理1、整体电路设计原理数字计时器是由脉冲发生电路、计时电路、译码显示电路和控制电路等几部分组成的,其中控制电路由校分电路、清零电路和报时电路组成。

其中由秒脉冲电路为计时器提供1hz的计时脉冲,而计时电路则完成相应的计时功能,并由显示电路显示出来,控制电路则均与计时电路有关。

具体的原理框图如下:2、各部分电路的设计及原理(1)脉冲电路器件:32768Hz晶体管、20MΩ电阻、20PF电容、10PF电容、CC4060、74LS74 功能:为计时电路提供计数脉冲。

原理:实验中采用32768Hz的石英晶体多谐振荡器作为脉冲信号源。

经分频器CD4060的多级分频,从Q14可获得2Hz输出信号(Q4和Q5提供2kHZ,1kHZ留报时电路备用)。

再将2Hz的脉冲信号经二分频电路得到1Hz的秒脉冲信号。

二分频电路由D触发器实现。

将D触发器的D端与Q端接在一起实现,Q端的输出信号即为1Hz的秒脉冲信号。

(2)计时电路器件:CD4518、74LS161、74LS00功能:完成0分00秒~9分59秒的计时功能原理:计时电路由分计数器、秒十位计数器、秒个位计数器构成。

秒个位计数器用CD4518A直接实现十进制计数功能;秒十位计数器是由74LS161做成一个从0000~0101的模六计数器实现;分位也是用CD4518A直接实现十进制计数功能。

将脉冲信号发生器生成的1HZ脉冲信号送入秒个位计数器(CD4518A)的CP端,秒个位的Q1、Q4通过一个与非门接入74LS161的时钟端作为时钟信号完成秒个位与十位的级联,与非门实现1001到1000的下降沿跳变。

秒十位记数的模六用反馈置数法实现。

将计数位2Q1、2Q3与非后作为驱动信号送入分计数器(CD4518A)的EN端,完成分计数。

(3)译码显示电路器件: CC4511、300Ω电阻、LED共阴数码管。

功能:实现计时时的数字显示原理:显示电路由三片CD4511显示译码器和三个七段共阴数码管组成。

四线七线译码器CD4511的LT,BI分别接高电平, LE端接低电平,此时器件处于译码状态。

再将译码器的输出分别与数码管的相应端对接,并在数码管接地端串联进300欧姆的电阻用以限流,这样令共阴极七段LED数码管进行循环显示。

而译码器CD4511的输入则由秒个位,秒十位,分位的输出接入。

(4)清零电路器件:CC4069、10KΩ电阻、22μF电容。

功能:具有开机自动清零功能,并且在任何时候,按动清零开关,可以进行计时器清零。

原理:开机时,电容上的电压不能突变,电容两端为低电平,经过第一个非门输出高电平,接到CC4518的管脚7和15,实现秒个位和分位的清零。

在经过第二个非门输出低电平,接到74LS161的管脚1,实现秒十位的清零。

开机后,开关打开为正常工作状态,按下开关后,电容被短路,第一个非门的输入端为低电平,两个非门的输出端分别为高电平和低电平,实现控制清零功能。

(5)校分电路器件:22μf电容,10kΩ电阻,74LS00功能:在任何时候,拨动校分开关,可以2HZ进行校分。

原理:开关打开时,正常计数:电容两端为高电平,输入秒信号的与非门被选通,输入校分信号的与非门被封锁,秒进位产生的脉冲送至分计数器的时钟端。

开关闭合时,开始校分:电容两端为低电平,输入校分信号的与非门被选通,输入秒信号与非门被封锁,校分信号(2HZ由CC4060的Q14得到)送至分计数器的时钟端。

(6)报时电路器件:74LS21、74LS32、蜂鸣器、三极管。

功能:使数字计时器从9分53秒开始报时,每隔一秒发一声,共发三声低音,一声高音;即9分53秒、9分55秒、9分57秒发低音(频率1kHz ),9分59秒发高音(频率2kHz )。

原理:因为分位,和秒十位均为9(1001),和5(0101)所以用一个与门控制条件。

秒个位分为低音和高音,其中低音部分为3(0011),5(0101),7(0111),利用卡诺图化简得1Q 2+1Q 3在与1HZ 信号相并;而高音部分只有9(1001)与2KHZ 信号相并。

最后将低音和高音部分的结果用或门输出,即可实现报时功能。

3、附加电路:起停电路设计及原理 (7分57秒自动停止5秒)器件:74LS161,74LS21功能:电路在在7分57秒自动停止5秒后又重新开始计数。

原理:用74161的置数功能。

通过与门控制74161的置数点。

当没到设定的停止时间时,置数信号端一直是低电平,74161一直进行置数,使得在置数输入端预置的0111置数至D Q C Q B Q A Q 端,而由C Q 端与1Hz 求与后输入秒个位的CP 端,正常计数。

当到达7分57秒,置数端输入高电平,74161正常计数, 0111,1000,1001,1010,1011,这5秒内C Q 端输出“0”信号,1HZ 信号与C Q 求与被锁住,计时器停止5秒。

直至1100,C Q 端重新输出为1,开始正常计数。

完成自动起停功能。

4、电路仿真波形(1)秒个位波形(2)秒十位波形(3)分位波形四、实验中遇到的问题及解决方法1、搭完秒脉冲电路后用示波器检测发现波形不正常解决方法:先检查电路联线发现没有问题。

于是怀疑是不是CC4060集成片出现问题。

更换集成片还是出现同样问题。

再检查石英晶体管时才发现由于几个电容距离太近管脚想接触造成短路,分开后,电路正常工作。

2、搭完计时电路时,秒分位的数码显示管总是在0,1之间跳变。

解决方法:一开始以为是数码管的问题,仔细数码管的接入电路,发现没有问题。

于是怀疑是数码管坏掉,换了一个后还是出现同样的问题。

于是推断问题不是出在数码管上。

开始检测输入数码管的74LS161的电路,发现74LS161cr 非端口空置。

接电源后,电路正常运行3、搭清零电路时发现清零电路无效解决方法:从清零电路开始检测,这一次检查的比较快。

发现问题还是出现在三个mr端口上。

因为原来的秒个位,分位的电路cr端口接地,自己在搭建清零电路时忘了改,出现错误。

4、报时电路在9分58秒蜂鸣器也发出声音解决方法:这问题其实是交给老师检测时才发现的。

因为那天已经下课了没来得及改。

回去想了下,其实问题是很简单的。

因为其他的鸣声是没有问题的。

所以打得电路连接是不会出现问题的。

出现问题的只有可能是控制秒个位条件的输入电路(1Q2+1Q3)。

第二天检查后发现连错了一根线,改过来后电路正常。

5、搭建附加电路时,由于面包板插不下,故拆掉部分电路,当拆完报时电路和清零电路后突然发现计时电路不能正常工作解决方法:一开始以为拆错线,很紧张,因为此时面包板上的连线太多了。

根本不知道拆错哪根线。

以为要返工,重连所有电路。

但是自己不太甘心,检查错误症状,发现与先前的计时电路错误有相似之处,想是不是也是cr端口的错误。

突然想起搭建清零电路时改过cr端的连接。

而刚才拆电路是并未还原cr端口的电路。

直接改掉电路搭建成功。

6、附加电路一开始自己设计的是3‘53,但并没有按照设想的那样。

电路在3’57时也出现暂停。

解决方法:先检查电路没问题。

后来检查自己设计思路时出现问题。

因为开始时是用1Q控制在7(0111)时也出现暂停,于是修改电路,改成7’57时停5b秒。

电路成功。

五、实验心得这次实验我收获很多。

相比于刚结束的eda实验,最大的不同是需要动手实际搭建电路,这对自己的动手能力有极大的提高。

实验的时间还是比较长的,我们组用了四天时间。

虽然有四天时间,但是我还是感觉时间蛮紧的。

首先是电路的设计与仿真,因为有老师的提示,并且自己也查阅了大量的资料,而自己的数电也学得还可以,所以设计时遇到的问题还不是很大。

但是仿真时还是遇到了不少麻烦。

首先是在仿真软件multisim中找不到所需的集成片如CC4060,查询资料后后来换了几个软件后找到在proteus中进行仿真。

这浪费很多时间。

实际操作时,发现这次搭建的电路很复杂,因为电路比较大元器件很多,这就要合理地布局,幸亏老师提供了样板。

但最难的还是连线,因为线路很多,非常容看错,连错,这时检查非常不方便。

自己一开始搭建时为了追求速度,出现几处错误,检查了很长时间才找出来,这让我明白了欲速则不达。

另外检查时,需要很耐心,要沉住气,还要十分的细心,因为错误可能只是一根线路插错位置,也许这对男生来说要求比较高。

还有实验中老师说可以问他两个问题,但是自己最终还是坚持住了,从始至终都是自己独立完成的,这还是很有成就感的。

虽然过程是艰辛的,但自己还是从中收获了很多,无论是对课本知识的理解与活学活用,还是自己的动手能力都得到很大提高。

另外从中养成的细心,耐心的品质更是使自己受益匪浅。

六、附录1、器件清单元器件清单:2、各元件的引脚图及功能表引脚图:功能表:CC4511逻辑功能表输入输出LT BI LE D C B A g f e d c B a 字符测灯0××××××11111118灭零10×00000000000消隐锁存111××××显示LE=0→1时数据110000001111110110000100001101CC4518逻辑功能表74LS74逻辑功能表74LS161逻辑功能表3、总电路图4、参考文献a)《数字电路》蒋立平著南京理工大学2001b)《电子线路实践教程》王建新、姜萍科学出版社2003c)《实验电子技术》李振声主编国防工出版社2001。