第六章 时序逻辑电路的VHDL语言描述

VHDL语言的主要描述语句

VHDL语言的主要描述语句按照语句的执行顺序对VHDL语言进行分类,包含两类语句:●并行描述语句该语句的执行与书写顺序无关,总是同时被执行●顺序描述语句从仿真的角度,该语句是顺序执行的进程语句(PROCESS)是最典型的并行语句,一个构造体可以有几个进程语句同时存在,而且并发执行。

但是进程部的所有语句都是顺序语句。

一、顺序描述语句顺序描述语句只能用在进程和子程序中,它和其他高级语言一样,其语句是按照语句的出现的顺序加以执行的。

如下分别介绍有关的顺序描述语句.1.WAIT语句进程在执行过程中总是处于两种状态:执行或挂起,进程的状态变化受等待语句的控制,当进程执行到等待语句,就被挂起,并等待再次执行进程.等待语句的格式:*WAIT 无限等待*WAIT ON 敏感信号变化*WAIT UNTIL 条件满足*WAIT FOR 时间到(1)WAIT ON格式:WAIT ON 信号[,信号]例5-1PROCESS(a,b)BEGINy<=a AND b;END PROCESS;该例中的进程与下例中进程相同:例5-1PROCESSBEGINy<=a AND b;WAIT ON a,b;END PROCESS;例5-2PROCESS(a,b)BEGINy<=a AND b;WAIT ON a,b;END PROCESS;(2)WAIT UNTIL 直到条件满足格式: WAIT UNTIL 布尔表达式当进程执行到该语句时,被挂起;若布尔表达式为真时,进程将被启动.例: WAIT UNTIL ((x*10)<100)(3)WAIT FOR 等到时间到格式: WAIT FOR 时间表达式当进程执行到该语句时,被挂起;等待一定的时间后,进程将被启动.例: WAIT FOR 20 ns;WAIT FOR (a*(b+c);(4)多条件WAIT 语句例: WAIT ON nmi,interrupt UNTIL ((nmi=TRUE) OR (interrupt=TRUE)) FOR 5 us 该等待有三个条件:第一,信号nmi和interrupt 任何一个有一次刷新动作第二, 信号nmi和interrupt 任何一个为真第三, 已等待5 us只要一个以上的条件被满足,进程就被启动.*注意:多条件等待时,表达式的值至少应包含一个信号量的值。

第六章 时序逻辑电路的VHDL语言描述

第5章

组合逻辑电路的VHDL描述

2. 时钟的下降沿描述

判断的条件为: Clk’LAST_VALUE’=‘1’ AND 钟信号是明确给出的,只有‘1’和 ‘0’,所以用判断条件也可为(maxplus中支持的格式): clk’EVENT AND clk=‘1’ (上升沿) clk’EVENT AND clk=‘0’ (下降沿)

END ENTITY asynch_latch ;

第5章

组合逻辑电路的VHDL描述

ARCHITECTURE behave OF asynch_latch IS BEGIN PROCESS ( clk, reset, datain, lock ) BEGIN IF ( reset = ‘1’ ) THEN -- 异步复位信号 dataout <= '0' ; ELSIF ( clk=‘1’ AND clk‘EVENT) THEN IF ( lock = '1' ) THEN dataout <= datain ; END IF ; END IF ; END PROCESS ; END ARCHITECTURE behave ;

第5章

组合逻辑电路的VHDL描述

LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; ENTITY clock_inst IS END ENTITY clock_inst ; PROCESS ( clock_signal ) -- 显式表示 BEGIN IF ( clock_signal = '1' ) THEN 其他处理语句; END IF ; END PROCESS ;

第5章

组合逻辑电路的VHDL描述

《VHDL语言程序设计》课程教学大纲

《VHDL语言程序设计》课程教学大纲课程简介课程简介:本课程为软件工程专业嵌入式专业方向的专业课,是开发基于FPGA/CPLD嵌入式系统的必备基础。

主要内容包括FPGA/CPLD目标器件的结构和工作原理、EDA技术和工作流程、VHDL基础知识、VHDL实用方法和设计深入、原理图输入法、LPM宏功能模块实用方法、状态机设计以及EDA优化设计。

目的是为后续课程的学习和嵌入式系统的设计作必须的基础准备。

课程大纲一、课程的性质与任务:本课程是软件工程专业的专业方向课程。

教学任务主要包括使学生了解EDA技术的工作流程,正确使用开发平台,掌握以VHDL为代表的硬件描述语言的基本知识、编程实用方法和工程设计方法,掌握原理图设计法、状态机设计法,能够正确使用IP Core和LPM等宏功能模块。

本课程是软件工程专业嵌入式专业方向的第一门专业方向课,是后续课程的必备基础,具有较重要的地位。

二、课程的目的与基本要求:本课程涉及到的学科基础知识面广,要求软硬件兼备,需要较好的学科基础。

通过本课程的学习,最终达到能够设计基于FPGA/CPLD的ASIC,并能进行EDA优化的目的。

三、面向专业:软件工程四、先修课程:《计算系统基础》五、本课程与其它课程的联系:本课程的先行课程是计算系统基础。

服务的主要后续课程包括基于FPGA的嵌入式软件开发、基于ARM的嵌入式软件开发等。

六、教学内容安排、要求、学时分配及作业:第一章概述(2学时)1.1 EDA技术及其发展(C)1.2 硬件描述语言硬件描述语言种类、自顶向下设计方法、EDA工程设计流程。

(A)1.3 面向FPGA/CPLD的开发流程设计输入、分析综合、布局布线、仿真、下载和硬件测试。

(A)1.4 IP Core 及EDA技术发展趋势。

(C)第二章 FPGA硬件特性与编程技术(8学时)2.1 PLD发展历程及其分类(c)2.2 低密度PLD工作原理PROM、PLA、PAL、GAL。

《VHDL语言程序设计》课程教学大纲

GDOU-B-11-213《VHDL语言程序设计》课程教学大纲课程简介课程简介:本课程为软件工程专业嵌入式专业方向的专业课,是开发基于FPGA/CPLD嵌入式系统的必备基础。

主要内容包括FPGA/CPLD目标器件的结构和工作原理、EDA技术和工作流程、VHDL基础知识、VHDL实用方法和设计深入、原理图输入法、LPM宏功能模块实用方法、状态机设计以及EDA优化设计。

目的是为后续课程的学习和嵌入式系统的设计作必须的基础准备。

课程大纲一、课程的性质与任务:本课程是软件工程专业的专业方向课程。

教学任务主要包括使学生了解EDA技术的工作流程,正确使用开发平台,掌握以VHDL为代表的硬件描述语言的基本知识、编程实用方法和工程设计方法,掌握原理图设计法、状态机设计法,能够正确使用IP Core和LPM等宏功能模块。

本课程是软件工程专业嵌入式专业方向的第一门专业方向课,是后续课程的必备基础,具有较重要的地位。

二、课程的目的与基本要求:本课程涉及到的学科基础知识面广,要求软硬件兼备,需要较好的学科基础。

通过本课程的学习,最终达到能够设计基于FPGA/CPLD的ASIC,并能进行EDA优化的目的。

三、面向专业:软件工程四、先修课程:《计算系统基础》五、本课程与其它课程的联系:本课程的先行课程是计算系统基础。

服务的主要后续课程包括基于FPGA的嵌入式软件开发、基于ARM的嵌入式软件开发等。

六、教学内容安排、要求、学时分配及作业:第一章概述(2学时)1.1 EDA技术及其发展(C)1.2 硬件描述语言硬件描述语言种类、自顶向下设计方法、EDA工程设计流程。

(A)1.3 面向FPGA/CPLD的开发流程设计输入、分析综合、布局布线、仿真、下载和硬件测试。

(A)1.4 IP Core 及EDA技术发展趋势。

(C)第二章 FPGA硬件特性与编程技术(8学时)2.1 PLD发展历程及其分类(c)2.2 低密度PLD工作原理PROM、PLA、PAL、GAL。

vhdl语法

在VHDL语言里,不同类型的数据信号之间不能互 相赋值。当需要不同类型数据之间传递信息时,就需 要类型转换函数将其中的一种类型数据转换为另一中 数据类型后,再进行信号的传递。

• 1999年,IEEE又将数字模拟混合VHDL的版本作为工业标准, 即IEEE1076.3;

一、VHDL概述

VHDL与电路图设计电路的方式不同:

和电路图设计方式相比: (1)易于修改;

(2)设计能力更强;

(3)VHDL语言很方便:独立于器件设计;相同的程

序代码可以用于不同厂家生产的器件。

一、VHDL概述

设计范例:2输入与门

a b

c

电路真值表

a 0 1 0 1

b 0 0 1 1

c 0 0 0 1

一、VHDL 概述 IEEE; LIBRARY

USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; Entity and2 is Port( a : in bit; 双减号--为VHDL程序的 b : in bit; 注释符,类似C语言中的 //注释符。 c : out bit); End and2; --实体定义结束。

端口名

端口模式

数据类型

一、VHDL概述

端口模式(MODE)有以下几种类型: IN ;OUT;INOUT ;BUFFER

端口模式可用下图说明:(黑框代表一个设计或模块)

IN

OUT

BUFFER

INOUT

(3)ARCHITECTURE定义区

实体的实现。即说明电路执行什么动作或实现功能。 定义格式: Architecture 结构体名 of 实体名 is

VHDL的时序电路描述

第5章 时序逻辑电路的分析和设计

电路时钟信号的VHDL描述

1. clk‟event and clk=„1‟; clk‟event and clk=„0‟; 2. rising_edge(clk); falling_edge(clk); --上升沿 --下降沿 --上升沿 --下降沿

第5章 时序逻辑电路的分析和设计

第5章 时序逻辑电路的分析和设计

状态机描述

MOORE 状态机 MEALY 状态机

第5章 时序逻辑电路的分析和设计

MOORE 状态机

0 S0/0 1 1 S1/1 0 0 S2/0 0 1 S3/0

1

第5章 时序逻辑电路的分析和设计

ቤተ መጻሕፍቲ ባይዱ

CH6_5_1.VHD

-- **************************************** LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; --********************************************* ENTITY Ch6_5_1 is PORT( CP : IN STD_LOGIC; -- CLOCK DIN : IN STD_LOGIC; -- I/P Signal OP : OUT STD_LOGIC -- O/P Signal ); END Ch6_5_1;

第5章 时序逻辑电路的分析和设计

architecture behave of count10 is begin tc<='1' when q=9 else '0'; --”1001” process(cp) begin if (rising_edge(cp)) then if q=9 then --”1001” q<=“0000”; --十进制 else q<=q+1; --自身赋值! end if; end if; end process; end behave;

时序电路VHDL讲解

前几节,我们讲解的都是组合逻辑电路。

通过这些组合逻辑电路,我们初步掌握了VHDL常用的语法结构。

从这节开始,我们要介绍时序电路了。

(其实我们没有刻意去分组合和时序,只是觉的前面组合讲的多点,后面可能会多讲些时序电路而已。

对小平爷爷曾经说过:不管黑猫,白猫,只要能捉到老鼠的猫就是好猫。

所以不论时序,组合,还是时序和组合的混合体,只要能实现功能的就是好程序!)说一下概念:异步和同步。

这是时序电路的两大类。

同步就是电路的触发器由同一个时钟信号驱动,在同一个时刻翻转;而异步就是不在同一个时刻翻转。

大多数编程器的的内部结构是同步时序逻辑电路。

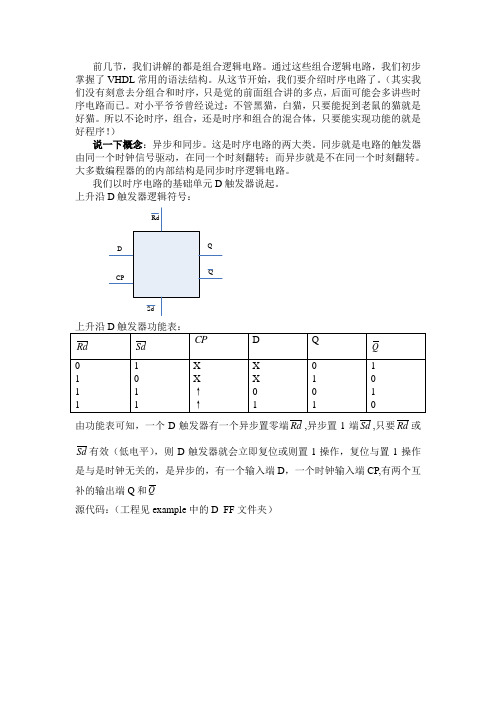

我们以时序电路的基础单元D触发器说起。

上升沿D触发器逻辑符号:由功能表可知,一个D触发器有一个异步置零端Rd,异步置1端Sd,只要Rd或Sd有效(低电平),则D触发器就会立即复位或则置1操作,复位与置1操作是与是时钟无关的,是异步的,有一个输入端D,一个时钟输入端CP,有两个互补的输出端Q和Q源代码:(工程见example中的D_FF文件夹)逐行解释:19~33:是一个有嵌套的IF结构。

这个IF结构就是按照功能表的顺序来写的。

25:是一条功能表没有的语句,在这种情况下,信号输出不确定,即用’X’来表示。

这儿要考虑到选择信号的完备性:Rd和Sd的组合会形成4种可能,若没有第25句的话,那么28~32可在Rd=’0’且Sd=’0’和Rd=’1’且Sd=’1’两种情况下运行。

这个是不符合功能要求的。

这里提醒大家一句:编写程序,不仅仅是VHDL程序,心一定要细。

29:用到了一个内置函数rising_edge(),即表示信号的上升沿,相对的就是falling_edge()。

该句等同于(if CP’event and CP=’1’),意思是CP上有事件发生,且事件发生后CP是高电平。

(事件无非就是上升和下降,若事件后是高电平,那就是上升沿发生了!)这两个函数在以后会经常用到的。

注意:因为是Sd,Rd是异步信号,即该信号不等待时钟的某一状态,而是直接起作用。

第六章 时序逻辑电路的VHDL语言描述解读

第 5章

时序逻辑电路的VHDL描述

6.2 时序电路的复位方法

时序电路的初态是由复位信号来触发而设置的, 所以复位是时序电路中的基本动作。 6.2.1 时序电路的同步复位方法 时序电路的同步复位是指:当电路的复位信号有 效并且时钟信号的边沿到来时,时序电路才进行复位。 在VHDL中描述时序电路的同步复位时,把时钟

clk’EVENT AND clk=‘0’ (下降沿)

第 5章

时序逻辑电路的VHDL描述

6.1.2 时钟作为敏感信号

在时序电路中,时钟信号是必不可少的,在VHDL 中都是用时钟信号作为进程的驱动来实现和时钟的同 步。 1.显式表示时钟敏感信号

如果将时钟信号放在进程的敏感信号表中,当时

钟变化时启动进程。 2. 隐式表示时钟敏感信号 时钟信号不放在进程的敏感信号表中,用WAIT语 句来控制进程的执行。

第 5章

时序逻辑电路的VHDL描述

第六章

时序电路

时序逻辑电路的输出不但和当前输入有关,还与系统的原 先状态有关,即时序电路的当前输出由输入变量与电路原先的 状态共同决定。 作为时序逻辑电路的基本特征,时序逻辑电路应具有“记 忆”功能。触发器是时序电路最常用的记忆元件。 任何时序逻辑电路都是以时钟信号为驱动信号的,时序电 路通常在时钟信号的边沿到来时才发生状态变化。因此,设计 时序逻辑电路时,必须要重视时钟信号。 本章将首先介绍常用触发器的设计方法,然后介绍常用的 时序电路:计数器、寄存器、移位寄存器等。

第 5章

时序逻辑电路的VHDL描述

时钟敏感信号设置时注意:

1. 无论是在进程还用WAIT中对时钟边沿说明时,一定 要说明是上升沿还是下降沿。 2.当时钟作为进程的敏感信号表时,在敏感信号表中不 能同时出现多个时钟信号,其它信号可以和时钟信

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第 5章

时序逻辑电路的VHDL描述

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ; ENTITY clock_inst IS END ENTITY clock_inst ; PROCESS BEGIN WAIT ON ( clock_signal ) UNTIL ( clock_signal = '0' ) ; -- 隐式表示 其他处理语句; END PROCESS ;

第 5章

时序逻辑电路的VHDL描述

yinshi : PROCESS -- 隐式表示 BEGIN WAIT ON ( clock_signal ) UNTIL ( clock_signal_condition ) ; IF (synchronization_reset_condition ) THEN signal_n <= reset_value_n ; temp_n := reset_value_temp ; ELSE 其他处理语句; END IF ; END PROCESS yinshi ;

第 5章

时序逻辑电路的VHDL描述

LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; ENTITY clock_inst IS END ENTITY clock_inst ; PROCESS ( clock_signal ) -- 显式表示 BEGIN IF ( clock_signal = '1' ) THEN 其他处理语句; END IF ; END PROCESS ;

END ARCHITECTURE behavioral ;

第 5章

时序逻辑电路的VHDL描述

第 5章

时序逻辑电路的VHDL描述

6.3.2 边沿触发同步复位、加载锁存器

此时复位和加载信号都和时序电路中的时钟信号同步。 LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; ENTITY synch_latch IS

第 5章

时序逻辑电路的VHDL描述

1. 时钟的上升沿描述

从图中可看出时钟信号的变化过程:0

变化 。

1。在

VHDL语言中可用信号的属性函数来描述这三个状态:

clk’LAST_VALUE=‘0’ , clk’EVENT , clk=‘1’ 由于上升沿是瞬时完成的,也就是说当这三个条件同时 满足时,说明时钟信号出现了上升沿。所以判断的条件为: Clk’LAST_VALUE=‘0’ AND clk’EVENT AND clk=‘1’

第 5章

时序逻辑电路的VHDL描述

6.1 时序电路的时钟信号

时钟信号在时序电路中有着重要的作用,它将驱动时

序逻辑电路的状态转移,根据时钟信号可以区别时序电路 的现态和次态。

6.1.1 时钟信号边沿的描述

时钟信号的边沿分上升沿和下降沿,有的时序逻辑电 路是用上升沿驱动,有的是用时钟信号的下降沿驱动。

ARCHITECTURE behave OF synch_latch IS BEGIN PROCESS ( clk ) BEGIN IF ( clk=‘1’ AND clk‘EVENT ) THEN -- 时钟上升沿 IF ( reset = ‘1’ ) THEN -- 复位信号 dataout <= '0' ; ELSIF ( lock = '1' ) THEN -- 锁存信号 dataout <= datain ; END IF ; END IF ; END PROCESS ; END ARCHITECTURE behave ;

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY single_latch IS PORT ( reset : IN STD_LOGIC ; datain : IN STD_LOGIC ; lock : IN STD_LOGIC ;

dataout : OUT STD_LOGIC ) ;

第 5章

时序逻辑电路的VHDL描述

第 5章

时序逻辑电路的VHDL描述

【例6-8】 异步锁存器

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ; ENTITY asynch_latch IS PORT ( reset, clk : IN STD_LOGIC ; datain : IN STD_LOGIC ; lock : IN STD_LOGIC ; dataout : OUT STD_LOGIC ) ;

第 5章

时序逻辑电路的VHDL描述

2. 时钟的下降沿描述

判断的条件为: Clk’LAST_VALUE=‘1’ AND clk’EVENT AND clk=‘0’ 由于实际工作中时钟信号是明确给出的,只有‘1’和 ‘0’,所以用判断条件也可为(maxplus中支持的格式): clk’EVENT AND clk=‘1’ (上升沿)

END ENTITY single_latch ;

第 5章

时序逻辑电路的VHDL描述

ARCHITECTURE rtl OF single_latch IS BEGIN PROCESS ( reset, datain, lock ) BEGIN IF ( reset = ‘1’ ) THEN -- 异步复位 dataout <= '0' ; ELSIF ( lock = ‘1’ ) THEN -- 锁存信号 dataout <= datain ; END IF ; END PROCESS ; END ARCHITECTURE rtl ;

第 5章

时序逻辑电路的VHDL描述

时钟敏感信号设置时注意:

1. 无论是在进程还用WAIT中对时钟边沿说明时,一定 要说明是上升沿还是下降沿。 2.当时钟作为进程的敏感信号表时,在敏感信号表中不 能同时出现多个时钟信号,其它信号可以和时钟信

号并列放在敏感信号表中。

3.采用WAIT时,由于其是进程的同步点,它要么放在 进程的最前面,要么放在进程的最后面。

第 5章

时序逻辑电路的VHDL描述

yinshi : PROCESS

BEGIN WAIT ON ( clock_signal, asynchronous_reset_signal )

UNTIL ( clock_signal_condition, ) ; -- 隐式表示

IF ( asynchronous_reset_condition ) THEN signal_n <= reset_value_n ;

第 5章

时序逻辑电路的VHDL描述

6.2 时序电路的复位方法

时序电路的初态是由复位信号来触发而设置的, 所以复位是时序电路中的基本动作。 6.2.1 时序电路的同步复位方法 时序电路的同步复位是指:当电路的复位信号有 效并且时钟信号的边沿到来时,时序电路才进行复位。 在VHDL中描述时序电路的同步复位时,把时钟

第 5章

时序逻辑电路的VHDL描述

第 5章

时序逻辑电路的VHDL描述

【例6-6】 多输入电平锁存器 LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; ENTITY multi_latch IS

PORT (

reset : IN STD_LOGIC ;

datain1, datain2, datain3 : IN STD_LOGIC ;

lock1, lock2, lock3 : IN STD_LOGIC ;

dataout : OUT STD_LOGIC ) ; END ENTITY multi_latch ;

第 5章

BEGIN

时序逻辑电路的VHDL描述

ARCHITECTURE behavioral OF multi_latch IS

第 5章

时序逻辑电路的VHDL描述

-- 显式表示

xianshi : PROCESS ( clock_signal, asynchronous_reset_signal ) BEGIN IF ( asynchronous_reset_condition ) THEN signal_n <= reset_value_n ; temp_n := reset_value_temp ; ELSIF ( clock_signal_condition ) THEN 其他处理语句; -- 复位条件不成立时执行时序电路的正常行为 ELSE 其他处理语句; END IF ; END PROCESS xians述

第六章

时序电路

时序逻辑电路的输出不但和当前输入有关,还与系统的原 先状态有关,即时序电路的当前输出由输入变量与电路原先的 状态共同决定。 作为时序逻辑电路的基本特征,时序逻辑电路应具有“记 忆”功能。触发器是时序电路最常用的记忆元件。 任何时序逻辑电路都是以时钟信号为驱动信号的,时序电 路通常在时钟信号的边沿到来时才发生状态变化。因此,设计 时序逻辑电路时,必须要重视时钟信号。 本章将首先介绍常用触发器的设计方法,然后介绍常用的 时序电路:计数器、寄存器、移位寄存器等。

PORT ( reset, clk : IN STD_LOGIC ;

datain : IN STD_LOGIC ; lock : IN STD_LOGIC ; dataout : OUT STD_LOGIC ) ; END ENTITY synch_latch ;