EDA课程设计参考题目

EDA课程设计选题

EDA课程设计选题1.2FSK信号发生器:目的:进一步熟悉maxplus II软件的使用,掌握EDA技术及CPLD/FPGA的开发流程,掌握自顶向下的设计思想,掌握DDS原理和2FSK的原理;要求:(1)理解2FSK的工作原理,基于DDS设计2FSK调制信号,能用maxplus II软件仿真;(2)能把设计文件下载到实验箱,能用示波器观察波形;2.2PSK信号发生器:目的:进一步熟悉maxplus II软件的使用,掌握EDA技术及CPLD/FPGA的开发流程,掌握自顶向下的设计思想,掌握DDS原理和2pSK的原理;要求:(1)理解2FSK的工作原理,基于DDS设计2FSK调制信号,能用maxplus II软件仿真;(2)能把设计文件下载到实验箱,能用示波器观察波形;3.电梯控制器设计目的:掌握EDA技术及CPLD/FPGA的开发流程,掌握自顶向下的设计思想,掌握DDS原理和2PSK的原理;要求:(1)设计一个三层楼房自动电梯控制器,用八个LED显示电梯行进过程,并有数码管显示电梯当前所在楼层位置;(2)每层电梯入口处设有请求按钮开关,请求按钮按下则相应楼层的LED 亮;(3)能把设计文件下载到实验箱正确实现功能。

4.多功能电子钟:目的:进一步熟悉maxplus II软件的使用,掌握EDA技术及CPLD/FPGA的开发流程,掌握自顶向下的设计思想,掌握实用电子钟的设计原理;要求:(1)用HDL设计一个多功能数字钟,包含以下主要功能:精确计时,时间可以24小时制或12小时制显示;(2)日历:显示年月日星期;(3)能把设计文件下载到实验箱正确实现功能5.任意波形发生器:目的:(1)进一步熟悉maxplus II软件的使用,掌握EDA技术及CPLD/FPGA的开发流程,掌握自顶向下的设计思想,掌握DAC的工作原理,并利用EDA技术产生任意波形;要求:(1)DAC的工作原理,可以产生正弦波、方波、三角波、锯齿波等波形;(2)能把设计文件下载到实验箱,并用示波器观察波形。

EDA课程设计题目

电子081班课程设计题目1. LED显示控制系统中的控制器设计2. 基于FPGA的十字路口交通灯控制器3. 基于FPGA的八路竞赛抢答器4. 基于VHDL的乐曲演奏电路5. 基于VHDL的键盘扫描电路分组名单见下表全勤“√”迟到“×”请假“⊙”早退“*”LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ToneTaba ISPORT(Index:IN STD_LOGIC_VECTOR(3 DOWNTO 0);CODE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);HIGH:OUT STD_LOGIC;Tone:OUT STD_LOGIC_VECTOR(10 DOWNTO 0));END;ARCHITECTURE one OF ToneTaba ISBEGINSearch:PROCESS(Index)BEGINCASE Index ISWHEN"0000"=>Tone<="11111111111";CODE<="0000";HIGH<='0'; WHEN"0001"=>Tone<="01100000101";CODE<="0001";HIGH<='0'; WHEN"0010"=>Tone<="01110010000";CODE<="0010";HIGH<='0';WHEN"0011"=>Tone<="10000001100";CODE<="0011";HIGH<='0';WHEN"0101"=>Tone<="10010101101";CODE<="0101";HIGH<='0';WHEN"0110"=>Tone<="10100001010";CODE<="0110";HIGH<='0';WHEN"0111"=>Tone<="10101011100";CODE<="0111";HIGH<='0';WHEN"1000"=>Tone<="10110000010";CODE<="0001";HIGH<='1';WHEN"1001"=>Tone<="10111001000";CODE<="0010";HIGH<='1';WHEN"1010"=>Tone<="11000000110";CODE<="0011";HIGH<='1';WHEN"1100"=>Tone<="11001010110";CODE<="0101";HIGH<='1';WHEN"1101"=>Tone<="11010000100";CODE<="0110";HIGH<='1';WHEN"1111"=>Tone<="11011000000";CODE<="0001";HIGH<='1';WHEN OTHERS => NULL;END CASE;END PROCESS;END;1引言EDA是英文"Electronics Design Automation(电子设计自动化)"的缩写。

EDA课程设计_7

乒乓球游戏电路设计一、乒乓球设计方案(1)我们设计的乒乓球游戏是以一排发光二极管交替发光指示乒乓球的行进路径, 其行进的速度可由输入的时钟信号控制。

乒乓球比赛是甲乙双方的比赛, 所以用两个按键模拟左右两个球拍;我们还要设计一个乒乓球控制模块, 即当发光二极管到最后一个的瞬间, 若检测到对应的表示球拍的键的信号, 立即使“球”反向运行, 如果此瞬间没有接到按键信号, 将给出失败鸣叫, 同时为对方记1分, 并将记分显示出来, 然后由对方重新发球以此类推;还要设计失球计数器的高低位计数模块;乒乓球行进方向控制模块, 主要由发球键控制;还要有一个失球提示发生模块。

(2)要知道乒乓球的游戏规则, 以多少分为一局, 谁先得到一定的分数谁就赢一局, 以此来判断输赢。

(3)用数码管显示双方的得分, 还要设计一个十进制计数器, 来显示分数。

(4)在乒乓球设计方案时还要考虑球速的问题。

二、乒乓球游戏电路的设计程序1.LIBRARY IEEE;--乒乓球游戏顶层文件use ieee.std_logic_1164.all;entity TENNIS isport(bain,bbin,clr,clk,souclk:in std_logic;ballout:out std_logic_vector(7 downto 0);countah,countal,countbh,countbl:out std_logic_vector(3 downto 0);lamp,speaker:out std_logic);end entity TENNIS;architecture ful of TENNIS iscomponent soundport(clk,sig,en:in std_logic;sout:out std_logic);end component;component ballctrlport(clr,bain,bbin,serclka,serclkb,clk:in std_logic; bdout,serve,serclk,ballclr,ballen:out std_logic);end component;component ballport(clk,clr,way,en:in std_logic;ballout:out std_logic_vector(7 downto 0));end component;component boardport(ball,net,bclk,serve:in std_logic;couclk,serclk:out std_logic);end component;component cou10port(clk,clr:in std_logic;cout:out std_logic;qout:out std_logic_vector(3 downto 0));end component;component cou4port(clk,clr:in std_logic;cout:out std_logic;qout:out std_logic_vector(3 downto 0));end component;component mwayport(servea,serveb:in std_logic;way:out std_logic);end component;signalnet,couclkah,couclkal,couclkbh,couclkbl,cah,cbh:std_logic; signalserve,serclka,serclkb,serclk,ballclr,bdout,way,ballen:std_lo gic;signal bbll:std_logic_vector(7 downto 0);beginnet<=bbll(4);ballout<=bbll;lamp<=clk;uah:cou4 port map(couclkah,clr,cah,countah);ual:cou10 port map(couclkal,clr,couclkah,countal);ubh:cou4 port map(couclkbh,clr,cbh,countbh);ubl:cou10 port map(couclkbl,clr,couclkbh,countbl); ubda:board port map(bbll(0),net,bain,serve,couclkal,serclka);ubdb:board port map(bbll(7),net,bbin,serve,couclkbl,serclkb);ucpu:ballctrlportmap(clr,bain,bbin,serclka,serclkb,clk,bdout,serve,serclk, ballclr,ballen);uway:mway port map(serclka,serclkb,way);uball:ball port map(clk,ballclr,way,ballen,bbll);usound:sound port map(souclk,ballen,bdout,speaker);end ful;2.library ieee;use ieee.std_logic_1164.all;entity sound isport(clk:in std_logic; --发声时钟sig:in std_logic; --正确接球信号en:in std_logic; --球拍接球脉冲sout:out std_logic); --提示声输出, 接小喇叭end entity sound;architecture ful of sound isbeginsout<=clk and (not sig) and en;--球拍接球, 没接到时, 发提示声end ful;3.library ieee; --总控制模块use ieee.std_logic_1164.all;entity ballctrlisport(clr:in std_logic; --系统复位bain:in std_logic; --左球拍bbin:in std_logic; --右球拍seclka:in std_logic; --左拍准确接球或发球serclkb:in std_logic; --右拍准确接球或发球clk:in std_logic; --乒乓球灯移动时钟bdout:out std_logic; --球拍接球脉冲serve:out std_logic; --发球状态信号serclk:out std_logic; --球拍正确接球信号ballclr:out std_logic; --乒乓球灯清零信号ballen:out std_logic); --乒乓球灯使能end entity ballctrl;architecture ful of ballctrl issignal bd:std_logic;signal ser:std_logic;beginbd<=bain or bbin;ser<=serclka or serclkb;serclk<=ser;--球拍正确接球信号bdout<=bd; --球拍接球脉冲process(clr,clk,bd)beginif(clr='1')then --系统复位serve<='1'; --系统处在职发球状态ballclr<='1'; --乒乓球灯清零elseif(bd='1')then --系统正常--球拍发球或接球时ballclr<='1'; --乒乓球灯清零if(ser='1')then --球拍发球或准确接球ballen<='1'; --乒乓球灯使能允许serve<='0'; --系统处在接球状态else ballen<='0';serve<='1'; --系统处在发球状态end if;else ballclr<='0';--没发球或接球时乒乓球灯不清零end if;end if;end process;end ful;4.--乒乓球灯模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity ball isport(clk:in std_logic; --乒乓球灯前进时钟clr:in std_logic; --乒乓球灯清零way:in std_logic; --乒乓球灯前进方向en:in std_logic; --乒乓球灯使能ballout:out std_logic_vector(7 downto 0));--乒乓球灯end entity ball;architecture ful of ball issignal lamp:std_logic_vector(9 downto 0);beginprocess(clk,clr,en)beginif(clr='1') then lamp<="1000000001";--清零elsif en='0' thenelsif (clk'event and clk='1')then--使能允许, 乒乓球灯前进时钟上升沿if(way='1') then lamp(9 downto 1)<=lamp(8 downto 0);lamp(0)<='0';--乒乓球灯右移else lamp(8 downto 0)<=lamp(9 downto 1); lamp(9)<='0';--乒乓球灯左移end if;end if;ballout<=lamp(8 downto 1);end process;end ful;5.--乒乓拍模块library ieee;use ieee.std_logic_1164.all;entity board isport(ball:in std_logic; --接球点, 也就是乒乓球灯的末端net:in std_logic; --乒乓球灯的中点, 乒乓球过中点时, counclk、serclk复位bclk:in std_logic; --球拍接球信号serve:in std_logic; --发球信号couclk:out std_logic;serclk:out std_logic);end entity board;architecture ful of board isbeginprocess(bclk,net)beginif(net='1')then serclk<='0';couclk<='0';--乒乓球过中点时, counclk、serclk复位elsif(bclk'event and bclk='1')then—球拍接球时if(serve='1')then serclk<='1';--系统处于发球状态时—发球成功else—系统处于接球状态if(ball='1')then serclk<='1';--乒乓球刚落在接球点上, 接球成功else serclk<='0';couclk<='1';end if;end if;end if;end process;end ful;6.--十进制计数器用来做失球低位计数library ieee;use ieee.std_logic_1164.all;entity mway isport(servea:in std_logic;serveb:in std_logic;way:out std_logic);end entity mway;architecture ful of mway isbeginprocess(servea,serveb)beginif(servea='1')then way<='1';elsif(serveb='1')then way<='0';end if;end process;end ful;7、--四进制计数器用来做失球高位计数library ieee;use ieee.std_logic_1164.all;entity mway isport(servea:in std_logic;serveb:in std_logic;way:out std_logic);end entity mway;architecture ful of mway isbeginprocess(servea,serveb)beginif(servea='1')then way<='1';elsif(serveb='1')then way<='0';end if;end process;end ful;8、--乒乓球前进方向产生模块library ieee;use ieee.std_logic_1164.all;entity mway isport(servea:in std_logic;--左选手发球信号serveb:in std_logic;--右选手发球信号way:out std_logic);--乒乓球灯前进方向信号end entity mway;architecture ful of mway isbeginprocess(servea,serveb)beginif(servea='1')then way<='1';--左选手发球方向向右elsif(serveb='1')then way<='0';--右选手发球方向向左end if;end process;end ful;三、乒乓球游戏程序的仿真波形仿真波形图四、硬件测试方法然后我们就要测试硬件, 下载文件。

EDA课程设计题目

EDA课程设计题目

题目一:正弦信号发生器设计,要求:

1、与D/A转换电路配合,产生一路频率范围为1KHz~20KHz的正弦信号,输出

频率、幅度可调;

2、频率、幅度的设定通过按键增减来实现,频率调整步长为1KHz,幅度调整步

长为500mV。

题目二:乐曲硬件演奏电路设计,要求:

1、FPGA配合按键、蜂鸣器演奏一段简单音乐;

2、当前演奏音调对应的阿拉伯数字用一位数码管显示;

3、用LED灯亮的个数指示当前演奏音调。

题目三:计时电路设计,要求:

1、具有小时、分钟、秒计时功能,并在数码管上实时显示,显示模式为12小时制和24小时制可选

2、可以对时钟进行设置

3、具有设置闹钟使能、设置功能,并能进行闹钟提醒。

题目四:串口通信电路设计

要求:

(1)设计一个全双工串口收发控制程序,速率为9600b/s,其中数据帧格式为:1位起始位+8位数据+1位奇偶校验位+1位停止位。

(2)通过连接两个实验箱,验证通信功能(如通过一个实验箱按键,另一个实验箱显示)。

题目五:数字频率计设计,要求:

1、所测频率的误差恒为百万分之一;

2、测频范围为0.1Hz~10MHz。

题目六:灯柱控制电路设计。

要求:

1、通过调节旋钮,在数码管上显示当前电压值

2、随着旋钮旋动时,LED 灯柱改变点亮的长度,蜂鸣器改变发出的音调。

EDA设计题目和内容

EDA设计题目和内容1智力竞赛抢答器的设计设计一个4人参加的智力竞赛抢答计时器。

电路具有回答问题时间控制功能。

要求回答问题时间小于等于100秒(显示为0~99),时间显示采用倒计时方式,当达到限定时间时,发出声响以示警告;设置一个主持人“复位”按钮,主持人复位后,开始抢答,进入倒计时,当有某一参赛者首先按下抢答开关时,相应指示灯亮并伴有2~3 秒声响,此时抢答器不再接受其他输入信号,使除第一抢答者外的按钮不起作用,倒计时也相应停止,主持人复位后,重新开始抢答。

其他要求:(1)数码管显示抢答得胜的选手号;(2)设置一个计分电路,每组开始预置100 分,由主持人记分,答对一次加10 分,答错一次减10 分。

2 数字电子钟的设计具有时,分,秒计数显示功能,以24小时循环计时;设置启动、停止开关,具有启动和停止计时操作的功能;显示格式为××-××-××,用8位数码管显示。

其他要求:(1)具有清零,调节小时、分钟、秒功能;(2)具有整点报时功能,整点报时的同时LED灯花样显示。

(3)具有闹钟功能,可任意设置时间点。

3 拔河游戏机的设计设计要求如下:(1)设计一个能进行拔河游戏的电路。

(2)电路使用7个发光二极管,开机后只有中间一个发亮,此即拔河的中心点。

(3)游戏双方各持一个按钮,迅速地、不断地按动,产生脉冲,谁按得快,亮点就向谁的方向移动,每按十次,亮点移动一次。

(4)亮点移到任一方终端二极管时,这一方就获胜,此时双方按钮均无作用,输出保持,只有复位后才使亮点恢复到中心。

(5)用数码管显示双方按键的次数。

4 数字频率计的设计设计一个8位十进制数字频率计,待测信号由50MHz时钟分频得到或外部输入,测频范围为1Hz~50MHz,频率通过8位数码管显示。

其他要求:(1)测频范围扩大到1Hz~100MHz。

(2)用1602液晶显示待测信号频率。

5 乒乓球比赛游戏机(1)设计一个由甲、乙双方参赛,有裁判的3人乒乓球游戏机。

EDA课程设计题目

1.数控分频器的设计2.8位16进制频率计设计3.数据采集电路和简易存储示波器设计利用FPGA直接控制0809对模拟信号进行采样,然后将转换好的8位二进制数据迅速存储到存储器中,在完成对模拟信号一个或数个周期的采样后,由外部电路系统(如单片机)将存储器中的采样数据读出处理。

4.8位移位相加硬件乘法器设计5.16阶数字滤波器的设计6.基于DSP Builder的FIR数字滤波器设计7.基于DSP Builder的IIR数字滤波器设计实验8. 基于FPGA的十字路口交通灯控制器9. 通用十进制加法器(动态扫描显示)设计一个双4 位的BCD码全加器,其框图如图1所示。

图中的“进位出”C即是本位的进位输出。

全加器的16个输入所对应的管脚同16位拨码开关相连,16个输入管脚是(被加数)A1(3..0)、(被加数)B1(3..0)和(被加数)A2(3..0)、(被加数)B2(3..0)。

相加的十进制结果经译码电路译为7段显示输出,和与进位的值。

要求显示器动态显示两位十进制相加的结果。

10、通用十进制减法器(动态扫描显示)设计一个双4 位的BCD码全减器,其框图如图2所示。

图中的“借位出”C即是本位的借位输出。

全减器的16个输入所对应的管脚同16位拨码开关相连,16个输入管脚是(被减数)A1(3..0)、(被减数)B1(3..0)和(减数)A2(3..0)、(减数)B2(3..0)。

相减的十进制差经译码电路译为7段显示输出,差与借位的值。

要求显示器动态显示两位十进制相减的结果。

11、六人抢答器抢答台数为6;具有抢答开始后20秒倒计时,20秒倒计时后六人抢答显示超时,并报警;能显示超前抢答台号并显示犯规报警;系统复位后进入抢答状态,当有一路抢答按键按下,该路抢答信号将其余各路抢答信号封锁,同时铃声响起,直至该路按键松开,显示牌显示该路抢答台号。

12、出租车计费器实现计费功能,计费标准为武汉起步3元,车行3公里后为1.4元/公里,当计费达到20元后,每公里加收50%的车费,车停止每3分钟增加0.7元。

(成都大学)EDA课程设计题目及解决方案(抢答器)

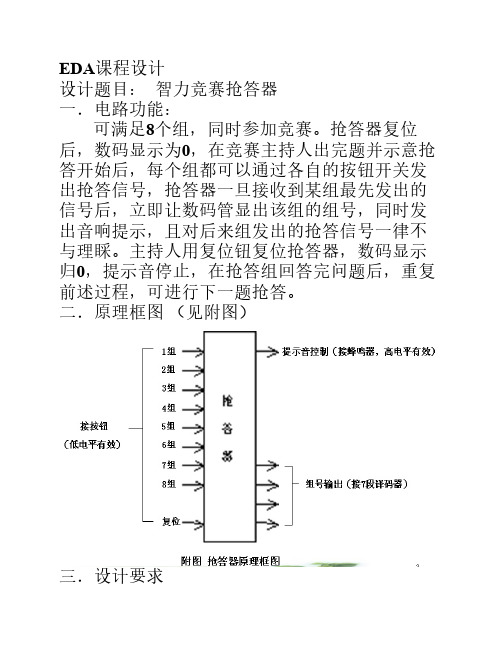

EDA课程设计设计题目:智力竞赛抢答器一.电路功能:可满足8个组,同时参加竞赛。

抢答器复位后,数码显示为0,在竞赛主持人出完题并示意抢答开始后,每个组都可以通过各自的按钮开关发出抢答信号,抢答器一旦接收到某组最先发出的信号后,立即让数码管显出该组的组号,同时发出音响提示,且对后来组发出的抢答信号一律不与理睬。

主持人用复位钮复位抢答器,数码显示归0,提示音停止,在抢答组回答完问题后,重复前述过程,可进行下一题抢答。

二.原理框图(见附图)三.设计要求用VHDL语言描述抢答器逻辑功能,经编译后仿真,仿真波形正确后,加上段码译码器编译通过后方可在实验箱上下载,做真实电路验证。

四. 撰写设计报告给出设计方案框图,包括模块的划分,信息的传递关系;给出各模块的VHDL程序;给出每个模块的仿真波形图,并附以文字说明;写出设计的心得体会和收获。

一.结构描述法1(先锁存后编码)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY scq_8 ISPORT (g: IN STD_LOGIC_VECTOR (8 DOWNTO 1); rst, en: IN STD_LOGIC;q: OUT STD_LOGIC_VECTOR (8 DOWNTO 1)); END scq_8;ARCHITECTURE one OF scq_8 ISBEGINPROCESS ( rst, en)BEGINIF rst='0' THENq<= "11111111";ELSIF en ='1' THENq<=g;END IF;END PROCESS;END one;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY bm8_4 ISPORT(d: IN STD_LOGIC_VECTOR(8 DOWNTO 1); sum: OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END bm8_4;ARCHITECTURE one OF bm8_4 ISBEGINPROCESS(d)BEGINCASE d ISWHEN "11111110" => sum<="0001";WHEN "11111101" => sum<="0010";WHEN "11111011" => sum<="0011";WHEN "11110111" => sum<="0100";WHEN "11101111" => sum<="0101";WHEN "11011111" => sum<="0110";WHEN "10111111" => sum<="0111";WHEN "01111111" => sum<="1000";WHEN OTHERS => sum<="0000";END CASE;END PROCESS;END one;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DECL7S ISPORT(A: IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S: OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END;ARCHITECTURE one OF DECL7S ISBEGINPROCESS(A)BEGINCASE A ISWHEN "0000" => LED7S <= "0111111";WHEN "0001" => LED7S <= "0000110";WHEN "0010" => LED7S <= "1011011";WHEN "0011" => LED7S <= "1001111";WHEN "0100" => LED7S <= "1100110";WHEN "0101" => LED7S <= "1101101";WHEN "0110" => LED7S <= "1111101";WHEN "0111" => LED7S <= "0000111";WHEN "1000" => LED7S <= "1111111";WHEN "1001" => LED7S <= "1101111";WHEN "1010" => LED7S <= "1110111";WHEN "1011" => LED7S <= "1111100";WHEN "1100" => LED7S <= "0111001";WHEN "1101" => LED7S <= "1011110";WHEN "1110" => LED7S <= "1111001";WHEN "1111" => LED7S <= "1110001";WHEN OTHERS => NULL;END CASE;END PROCESS;END;四.状态机描述法LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY qdq8_1 ISPORT(rst,clk: STD_LOGIC;g: IN STD_LOGIC_VECTOR(8 DOWNTO 1);q: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);sq: OUT STD_LOGIC );END qdq8_1;ARCHITECTURE one OF qdq8_1 ISTYPE s IS (s0,s1);SIGNAL crt_s: s;SIGNAL sum: STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINPROCESS(rst,clk,g)BEGINIF rst='0' THEN crt_s<=s0;ELSIF clk'event AND clk='1' THENCASE crt_s ISWHEN s0 => q<="0000";sq<='0';CASE g ISWHEN "11111110" => sum<="0001";crt_s<=s1;WHEN "11111101" => sum<="0010";crt_s<=s1;WHEN "11111011" => sum<="0011";crt_s<=s1;WHEN "11110111" => sum<="0100";crt_s<=s1; WHEN "11101111" => sum<="0101";crt_s<=s1; WHEN "11011111" => sum<="0110";crt_s<=s1; WHEN "10111111" => sum<="0111";crt_s<=s1; WHEN "01111111" => sum<="1000";crt_s<=s1; WHEN OTHERS => crt_s<=s0;END CASE;WHEN s1 => q<=sum; sq<='1';crt_s<=s1;END CASE;END IF;END PROCESS;END one;。

EDA课程设计题目_图文.(共5篇)

EDA课程设计题目_图文.(共5篇)第一篇:EDA课程设计题目_图文.课程设计题目设计一数字式竞赛抢答器1、设计一个可容纳6 组(或4 组参赛的数字式抢答器,每组设一个按钮,供抢答使用。

2、抢答器具有第一信号鉴别和锁存功能,使除第一抢答者外的按钮不起作用。

3、设置一个主持人“复位”按钮。

4、主持人复位后,开始抢答,第一信号鉴别锁存电路得到信号后,有指示灯显示抢答组别,扬声器发出2~3 秒的音响。

5、设置一个计分电路,每组开始预置100 分,由主持人记分,答对一次加10 分,答错一次减10 分。

教学提示:1、此设计问题的关键是准确判断出第一抢答者并将其锁存,实现的方法可使用触发器或锁存器,在得到第一信号后将输入封锁,使其它组的抢答信号无效。

2、形成第一抢答信号后,用编码、译码及数码显示电路显示第一抢答者的组别,用第一抢答信号推动扬声器发出音响。

3、计分电路采用十进制加/减计数器、数码管显示,由于每次都是加/减10 分,所以个位始终为零,只要十位、百位进行加/减运算即可。

设计二数字钟1、设计一个能显示1/10秒、秒、分、时的12小时数字钟。

2、熟练掌握各种计数器的使用。

3、能用计数器构成十进制、六十进制、十二进制等所需进制的计数器。

4、能用低位的进位输出构成高位的计数脉冲。

教学提示:1、时钟源使用频率为0.1Hz的连续脉冲。

2、设置两个按钮,一个供“开始”及“停止”用,一个供系统“复位”用。

3、时钟显示使用数码管显示。

4、“时显示”部分应注意12点后显示1点。

5、注意各部分的关系,由低位到高位逐级设计、调试。

设计三数字频率计1、设计一个能测量方波信号的频率的频率计。

2、测量的频率范围是0?999999Hz。

3、结果用十进制数显示。

教学提示:1、脉冲信号的频率就是在单位时间内所产生的脉冲个数,其表达式为,f为被测信号的频率,N为计数器所累计的脉冲个数,T为产生N个脉冲所需的时间。

所以,在1秒时间内计数器所记录的结果,就是被测信号的频率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

附录I EDA课程设计参考题目注:在以下设计中只可以用一个参考时钟一、设计数码管显示控制器要求:1.能自动一次显示出数字0、1、2、3、4、5、6、7、8、9(自然数列),1、3、5、7、9(奇数列),0、2、4、6、8(偶数列),0、1、2、3、4、5、6、7、0、1(音乐符号序列);然后再从头循环;2.打开电源自动复位,从自然数列开始显示。

二、设计乒乓球游戏机要求:1.用8个发光二极管表示球;用两个按钮分别表示甲乙两个球员的球拍;2.一方发球后,球以固定速度向另一方运动(发光二极管依次点亮),当球达到最后一个发光二极管时,对方击球(按下按钮)球将向相反方向运动,在其他时候击球视为犯规,给对方加1分;都犯规,各自加1分;3.甲、乙各有一数码管计分;4.裁判有一个按钮,是系统初始化,每次得分后,按下一次。

三、设计智力竞赛抢答器要求:1.五人参赛每人一个按钮,主持人一个按钮,按下就开始;2.每人一个发光二极管,抢中者灯亮;3.有人抢答时,喇叭响两秒钟;4.答题时限为10秒钟,从有人抢答开始,用数码管倒计时间,0、9、8…1、0;倒计时到0的时候,喇叭发出两秒声响。

四、设计数字钟要求:1.输入10HZ的时钟;(提示:对已有kHz频率时钟进行分频)2.能显示时、分、秒,24小时制;4.时和分有校正功能;5.整点报时,喇叭响两秒;6.可设定夜间某个时段不报时;注意:硬件资源的节约,否则器件内资源会枯竭。

五、设计交通灯控制器要求:1.东西方向为主干道,南北方向为副干道;2.主干道通行40秒后,若副干道无车,仍主干道通行,否则转换;4.换向时要有4秒的黄灯期;5.南北通行时间为20秒,到时间则转换,若未到时,但是南北方向已经无车,也要转换。

6.附加:用数码管显示计时。

六、设计双钮电子锁要求:1.有两个按钮A和B,开锁密码可自设,如(3、5、7、9);2.若按B钮,则门铃响;(滴、嗒…);3.开锁过程:按3下A,按一下B,则3579中的“3”即被输入;接着按5下A,按一下B,则输入“5”;依此类推,直到输入完“9”,按B,则锁被打开——用发光管KS表示;4.报警:在输入3、5、6、9过程后,如果输入与密码不同,则报警;用发光管BJ表示,同时发出“嘟、嘟……的报警声音;5.用一个开关表示关门(即闭锁)。

七、设计彩灯控制器二要求:1.有十只LED,L0……L92.显示方式①先奇数灯依次灭②再偶数灯依次灭③再由L0到L9依次灭3.显示间隔0.5S,1S可调。

八、设计速度表要求:1.显示汽车Km/h数;2.车轮每转一圈,有一传感脉冲;每个脉冲代表1m的距离;3.采样周期设为10S;4.要求显示到小数点后边两位;5.用数码管显示;6,最高时速小于300Km/h。

九、设计电话卡计费器要求:1.设计一个模拟电话卡计费的计数器模型。

该计费器在电话卡插入后能将卡中币值读出并显示出来。

在通话过程中,根据通话种类计费并将话费从卡中扣除,卡值每分钟更新一次;2.话费种类:市话:0.3元/分长途0.6元/分特话免费;3.当卡中余额不足时产生警告,警告时间达到一定长度切断通话。

十、设计出租车计价器要求:1.5 Km起计价,起始价5元,每公里1.2元;2.传感器输出脉冲为0.5m/个;3.每0.5km改变一次显示,且提前显示(只显示钱数)。

十一、设计八音电子琴要求:1.能发出1、2、3、4、5、6、7、1八个音;2.用按键作为键盘;十二、自设计动奏乐器一要求:1.开机能自动奏一个乐曲,可以反复演奏;2.速度可变。

1 1 5 5 6 6 5 –4 4 3 3 2 2 1 –5 5 4 4 3 3 2 –5 5 4 4 3 3 2 –3.附加:显示乐谱。

十三、设计自动奏乐器二要求:1.开机能自动奏一个乐曲,可以反复演奏;2.速度可变。

1 3 1 3 5 6 5 – 6 6 ∙1 6 5 –––6 6 ∙1 6 5 5 3 12 23 2 1 –––3.附加:显示乐谱。

十四、设计自动打铃器要求:1.有数字钟功能;(不包括校时等功能)2.可设置六个时间,定时打铃;3.响铃5秒钟。

十五、设计数字频率计要求:1.输入为矩形脉冲,频率范围0~99MHz;2.用五位数码管显示;只显示最后的结果,不要将计数过程显示出来;3.单位为Hz和KHz两档,自动切换。

十六、设计算术运算单元ALU的设计要求:1.进行两个四位二进制数的运算。

2.算术运算:A+B,A-B,A+1,A-13.逻辑运算:A and B,A or B,A not, A xor B注意:从整体考虑设计方案,优化资源的利用十七、设计游戏机,有三位数码管显示0—7之间的数码,按下按钮,三个数码管循环显示,抬起按钮,显示停止,当显示内容相同时,为赢要求:1.三个数码管循环显示的速度不同2.停止时的延迟时间也要不同3.如果赢了游戏时,要有数码管或LED的花样显示或声音提示。

十八、设计16路数显报警器要求:1.设计16路数显报警器,16路中某一路断开时(可用高低电平表示断开和接通),用十进制数显示该路编号,并发出声音信号;2.报警时间持续10秒钟;3.当多路报警时,要有优先级,并将低优先级的报警存储,处理完高优先级报警后,再处理之(附加)。

十九、设计电话按键显示器要求:1.设计一个具有4位显示的电话按键显示器,能准确反映按键数字;2.显示器显示从低位向高位前移,逐位显示,最低位为当前输入位;3.设置一个“重拨”键,按下此键,能显示最后一次输入的电话号码;4.摘下话机后才能拨号有效,挂机后熄灭显示。

二十、设计病房呼叫系统要求:1.用1~5个开关模拟5个病房的呼叫输入信号,1号优先级最高;1~5优先级依次降低;2.用一个数码管显示呼叫信号的号码;没信号呼叫时显示0;又多个信号呼叫时,显示优先级最高的呼叫号(其它呼叫号用指示灯显示);3.凡有呼叫发出5秒的呼叫声;4.对低优先级的呼叫进行存储,处理完高优先级的呼叫,再进行低优先级呼叫的处理(附加)。

二十一、设计自动电子钟要求:1.用24小时制进行时间显示;2.能够显示小时、分钟;3.每秒钟要有秒闪烁指示;4.上电后从“00:00”开始显示。

二十二、设计具有数字显示的洗衣机时控电路要求:1.洗衣机工作时间可在1~15分钟内任意设定(整分钟数);2.规定电动机运行规律为正转20s、停10s、反转20s、停10s、再正转20s,以后反复运行;3.要求能显示洗衣机剩余工作时间,每当电机运行一分钟,显示计数器自动减1,直到显示器为“0”时,电机停止运转;4.电机正转和反转要有指示灯(发光二极管)指示。

二十三、设计篮球比赛数字计分牌要求:1.分别记录两队得分情况;2.进球得分加2分,罚球进球得分加1分;3.计时电路,24秒计时,用一个键表示球碰篮板,之后清零重新计时;用到六个数码管。

二十四、设计电子日历要求:1.能显示年、月、日,星期;2.例如:“01.11.08 6”,星期日显示“8”;3.年月日,星期可调;4.不考虑闰年。

二十五、设计用电器电源自动控制电路要求:1.控制电路能使用电器的电源自动开启30s,然后自动关闭30s,如此周而复始的工作,要有工作状态指示;2.当电源接通时,可随时采用手动方式切断电源;当电源切断时,可随时采用手动方式接通电源;3.若手动接通,可由定时信号断开,然后进入自动运行状态,反之亦然;4.定时范围0分~60分,要有分秒的倒计时显示。

二十六、设计模拟中央人民广播电台报时电路要求:1.计时器运行到59分49秒开始报时,每鸣1s就停叫1s,共鸣6响;前5响为低音,频率为750Hz(用分频器);最后1响为高音,频率为1KHz(用分频器);2.至少要有分秒显示。

二十七、设计数字跑表要求:1.具有暂停/启动功能;2.具有重新开始功能;3.用6个数码管分别显示百分秒、秒和分钟。

二十八、设计拔河游戏机1.拔河游戏机需用9个发光二极管排列成一行,开机后只有中间一个点亮,以此作为拔河的中心线,游戏双方各持一个按键,迅速地、不断地按动产生脉冲,谁按得快,亮点向谁方向移动,每按一次,亮点移动一次。

移到任一方终端二极管点亮,这一方就得胜,此时双方按键均无作用,输出保持,只有经复位后才使亮点恢复到中心线;2.数码管显示胜者的盘数。

二十九、设计彩灯控制器三要求:1.8 个灯全亮;2.8 个灯全灭;3.从左边第一个开始每隔一个亮;4.从右边第一个开始每隔一个灭;5.左4个灭,右4个亮;6.左4个亮,右4个灭;三十、设计电子密码锁要求:1.实验任务根据设定好的密码,采用二个按键实现密码的输入功能;2.码输入正确之后,锁就打开,如果输入的三次的密码不正确,就锁定按键3秒钟,同时发出报警声,直到没有按键按下3秒后,才打开按键锁定功能;3.否则在3秒钟内仍有按键按下,就重新锁定按键3秒时间并报警。

三十一、设计倒计时器要求:1.显示1 位天,2 位时,2 位分;2.在0 分~9 天内,能任意设置倒计时长短;3.倒计时结束,能发出告警信号。

三十二、设计电梯控制器要求:1.利用四个位键作为用梯人的呼叫,上升或下降按键,第一个作为一楼呼叫按键,第二个作为二楼呼叫按键,第三个作为楼梯上升按键,第四个作为楼梯下降按键;2.4个键输入,用两个发光二极管表示上升和下降,再用两个数码管显示1和2层。

模拟电梯的工作过程,设计一个两层电梯控制器。

三十三、设计地铁售票系统要求:1.售票机有两个进币孔,一个是输入硬币,一个是输入纸币,硬币的识别范围是五角和一元的硬币,纸币的识别范围是一元、两元,五元,拾元;2.乘客可以连续多次投入钱币。

乘客可以选择的种类为2元和4元,乘客一次只能选择一个出站口;3.购买车票时,乘客先选择出站名,然后选择所需的票数,再进行投币,投入的钱币达到所需金额时,售票机自动出票,并找出余额,本次交易结束,等待下一次的交易;4.在投币期间,乘客可以按取消键取消本次操作,钱币自动退出。

三十四、设计微波炉控制器要求:1.微波炉控制器主要由四大模块来够成。

第一:时间控制模块要设计一个具有60分和60秒的倒计时控制器来控制。

第二:输入时间数据模块(置数部分)。

第三:操作和过程控制模块。

第四:动态显示的输出;2.电路里面要进行开关控制和复位控制及几种加热方式的档位控制以及档位灯光的显示控制。

用三个LED等来显示三档的加热方式,当工作的时候就亮着,停止工作的时候就熄灭。

开关控制主要控制脉冲的输入控制,就可以对加热的暂停和继续;3.为了减少控制电路的功率以至提高性能。

在显示时用动态显示电路来实现。

三十五、设计彩灯控制器一要求:1.有八只LED,L0……L72.显示顺序如下表3.显示间隔为0.25S,0.5S,1S,2S可调。