卷积码编译码课设 (2)

卷积码的编码及解码Viterbi解码Word版

卷积码的编码及解码(Viterbi 解码)一、实验目的1、了解卷积码的基本原理;2、掌握卷积码编码的电路设计方法;2、掌握卷积码 Viterbi 译码的基本方法和电路设计方法。

二、实验仪器1、移动通信实验箱一台;2、台式计算机一台;三、实验原理1.卷积码编码原理卷积码是一个有限记忆系统,它也将信息序列切割成长度 k的一个个分组,与分组码不同的是在某一分组编码时,不仅参看本时刻的分组而且参看本时刻以前的 L 个分组。

我们把 L+1 称为约束长度。

2.卷积码的译码算法(硬判决 Viterbi 译码)Viterbi译码算法是一种最大似然算法,它不是在网络图上依次比较所有可能的路径,而是接收一段,计算,比较一段,保留最有可能的路径,从而达到整个码序列是一个最大似然序列。

Viterbi解码算法的基本步骤如下:1、从某一时间单位j=m开始,对进入每一状态的所有长为j段分支的部分路径,计算部分路径度量。

对每一状态,挑选并存储一条有最大度量的部分路径及其部分度量,称此部分路径为留选(幸存)路径。

2、j增加1,把此时刻进入每一状态的所有分支度量,和同这些分支相连的前一时刻的留选路径的度量相加,得到了此时刻进入每一状态的留选路径,加以存储并删去其他所有的路径。

因此留选路径延长了一个分支。

3、若j<L+m,则重复以上步骤,否则停止,译码器得到了有最大路径度量的路径。

上面的过程可以简单的总结为“加、比、选”(也称ACS)。

四、实验步骤1、将实验箱和计算机通过串行口连接好,为实验箱上电。

2、将与实验箱相连的电脑上的学生平台程序打开。

在“实验选择”栏中选择“卷积码”实验,点击确认键。

从而进入此实验界面。

3、在实验界面上点“生成数据”,让系统生成待编码的随机比特。

也可在界面上直接双击所显示的 bit,修改其值。

4、在界面上点击下发“原始数据”,该数据将被送入单片机(或 CPLD)进行卷积编码然后经过编码的数据被送回学生平台并显示在“编码数据”栏。

实验二 卷积码编码及译码实验

实验二卷积码编码及译码实验一、实验目的通过本实验掌握卷积编码的特性、产生原理及方法,卷积码的译码方法,尤其是维特比译码的原理、过程、特性及其实现方法。

二、实验内容1、观察NRZ基带信号及其卷积编码信号。

2、观察帧同步信号的生成及巴克码的特性。

3、观察卷积编码信号打孔及码速率匹配方法。

4、观察接收端帧同步过程及帧同步信号。

5、观察译码结果并深入理解维特比译码的过程。

6、观察随机差错及突发差错对卷积译码的影响。

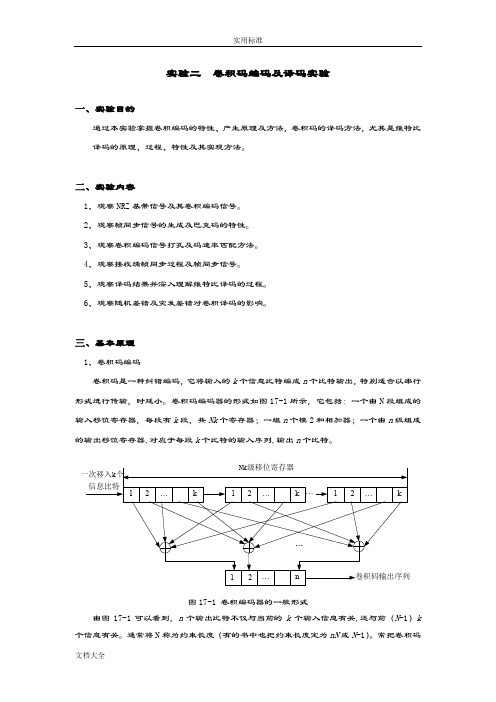

三、基本原理1、卷积码编码卷积码是一种纠错编码,它将输入的k个信息比特编成n个比特输出,特别适合以串行形式进行传输,时延小。

卷积码编码器的形式如图17-1所示,它包括:一个由N段组成的输入移位寄存器,每段有k段,共Nk个寄存器;一组n个模2和相加器;一个由n级组成的输出移位寄存器,对应于每段k个比特的输入序列,输出n个比特。

图17-1 卷积编码器的一般形式由图17-1可以看到,n个输出比特不仅与当前的k个输入信息有关,还与前(N-1)k 个信息有关。

通常将N称为约束长度(有的书中也把约束长度定为nN或N-1)。

常把卷积码记为:(n 、k 、N ),当k =1时,N -1就是寄存器的个数。

编码效率定义为:/c R k n =(17-1)卷积码的表示方法有图解表示法和解析表示法两种:解析法,它可以用数学公式直接表达,包括离散卷积法、生成矩阵法、码生成多项式法;图解表示法,包括树状图、网络图和状态图(最的图形表达形式)三种。

一般情况下,解析表示法比较适合于描述编码过程,而图形法比较适合于描述译码。

(1)图解表示法 (2)解析法下面以(2,1,3)卷积编码器为例详细讲述卷积码的产生原理和表示方法。

(2,1,3)卷积码的约束长度为3,编码速率为1/2,编码器的结构如图17-2所示。

jj图17-2 (2,1,3)卷积编码器这里我们主要介绍码多项式法。

我们可以用多项式来表示输入序列、输出序列、编码器中移位寄存器与模2和的连接关系。

卷积编码译码通信原理课程设计MATLAB

set(h,'color','y');

end

hold on

end

title('卷积编码译码');

legend('灾难编码器','1/2编码器','1/3编码器')

xlabel('信道信噪比');

ylabel('误码率');

六.实验结果及分析

编码器灾难性编码系统结果

对比三个仿真结果可知:灾难性编后果十分严重,在实际应用中必须编码,另外1/3编码器比1/2编码器性能要好。

d.网格图(研究卷积码最大似然译码维特比算法的工具)

纵坐标表状态,横坐标表时间。

从图中我们可看出编码过程中使用K-1个冲洗比特使得编码器恢复初始状态是有必要的。

三、卷积码的译码

Viterbi译码(最大似然译码)

先验概率条件下,后验概率最大者似然函数最大,最值MAP即最大似然(ML)译码。而最大对数似然函数即计算最小汉明距,如此,比较接受序列和发送序列汉明距,选出最小汉明距序列作为最佳译码即可。

如图:

状态表为:

ui

ui-1

si

0

0

a

1

0Байду номын сангаас

b

0

1

c

1

1

d

有如下状态图:

b.树图(将状态图按时间展开)

设初始状态s0=00为树根,对每个时刻的可能输入进行分支,分数级数L表示,L=0时,u0=0向上,u0=1向下,依次向后无限延伸,分支上数字表示相应输出,a,b,c,d表示状态。(优点:时序关系清晰)

四、卷积灾难性错误(Catastrophic error)

信道编码卷积码原理编码译码

(2)

m ' 0 0 1 1 0 0 . .. . . . 0 0 . .1 0 . .0 0 . .. .. . . . 0 0 . .1 0 . .0 0 . .. .. . . . m '( . . 1 ) m . .'( 2 . . )

000 000

.. ..

.... ....

000 000 000 000 000 000......

... ...

... ...

... ...

... ...

... ...

... ...

............

(11,011,100,000,139;''1 1

c(1,3) 10100.. ....

二. 卷积码-----有记忆的码-----有记忆编码电路

m(1)

c(1,1) 10000.. .... c(1)c(1,2)00000.. . .(.1.,0 01 0 ,00 ,0 01 0 ,00 0 ,.)0 ..,

(11, 11,11,11,...,)000 000 011 001 000 000 000 000 000 ......

000 000 000 101 000 001 000 000 000 ......

000 000 000 011 001 000 000 000 000 ......

000 000 001 000

000 000 000 000

000 000 000 000

000 000 000 000

000 000 000 000

000 000 000 000

实验九-(2-1-5)卷积码编码译码技术

实验九 (2,1,5)卷积码编码译码技术一、实验目的1、掌握(2,1,5)卷积码编码译码技术2、了解纠错编码原理。

二、实验内容1、(2,1,5)卷积码编码。

2、(2,1,5)卷积码译码。

三、预备知识1、纠错编码原理。

2、(2,1,5)卷积码的工作原理。

四、实验原理/卷积码是将发送的信息序列通过一个线性的,有限状态的移位寄存器而产生的编码。

通常卷积码的编码器由K级(每级K比特)的移位寄存器和n个线性代数函数发生器(这里是模2加法器)组成。

若以(n,k,m)来描述卷积码,其中k为每次输入到卷积编码器的bit数,n 为每个k元组码字对应的卷积码输出n元组码字,m为编码存储度,也就是卷积编码器的k元组的级数,称m+1= K为编码约束度m称为约束长度。

卷积码将k 元组输入码元编成n元组输出码元,但k和n通常很小,特别适合以串行形式进行传输,时延小。

与分组码不同,卷积码编码生成的n元组元不仅与当前输入的k元组有关,还与前面m-1个输入的k元组有关,编码过程中互相关联的码元个数为n*m。

卷积码的纠错性能随m的增加而增大,而差错率随N的增加而指数下降。

在编码器复杂性相同的情况下,卷积码的性能优于分组码。

编码器随着信息序列不断输入,编码器就不断从一个状态转移到另一个状态并同时输出相应的码序列,所以图3所示状态图可以简单直观的描述编码器的编码过程。

因此通过状态图很容易给出输入信息序列的编码结果,假定输入序列为110100,首先从零状态开始即图示a状态,由于输入信息为“1”,所以下一状态为b并输出“11”,继续输入信息“1”,由图知下一状态为d、输出“01”……其它输入信息依次类推,按照状态转移路径a->b->d->c->b->c->a输出其对应的编码结果“”。

译码方法⒈代数代数译码是将卷积码的一个编码约束长度的码段看作是[n0(m+1),k0(m+1)]线性分组码,每次根据(m+1)分支长接收数字,对相应的最早的那个分支上的信息数字进行估计,然后向前推进一个分支。

卷积码编译码课设 (2)

摘要卷积码是一种性能优越的信道编码。

它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。

随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。

本文对卷积码和卷积码的编译码有一个简单的介绍且给出了信道编码的发展历史及研究状况,然后详细讨论了(2,1,2)卷积码的编码过程和译码过程,通过状态转移方程和输出方程得出状态转移表和状态转移图,然后通过维特比译码器研究,总结出了维特比译码算法,最后通过Matlab软件进行设计与仿真,得到了编码程序和译码程序,其运行结果与理论分析一致。

关键字卷积码编码、信道编码、Viterbi译码、MATLAB仿真目录摘要........................................... 错误!未定义书签。

一、引言 (3)1.1发展历史及研究状况 (3)1.2设计目的和意义 (3)1.3设计方法 (4)二、卷积码编译码原理 (5)2.1 卷积码编码原理 (5)2.2编码器 (6)2.3 卷积码译码原理 (7)2.4 VITEBI 译码的关键步骤 (8)2.4.1 输入与同步单元 (8)2.4.2 支路量度计算 (8)2.4.3 路径量度的存储与更新 (8)2.4.4 信息序列的存储与更新 (8)2.4.5 判决与输出单元 (8)三、卷积码编码实现 (9)3.1 编码原理分析 (9)3.2 卷积码编码流程图 (10)四、卷积码译码实现 (11)4.1 译码编程思路 (11)4.2 卷积码译码流程图 (11)五、卷积码编译码程序的编译及仿真波形 (11)5.1 卷积码编码仿真 (12)5.2卷积码译码仿真 (13)5.3卷积码纠错码仿真 (14)六、总结 (15)七、参考文献 (16)附录 (17)一、引言1.1发展历史及研究状况1948年,Bell实验室的C.E.Shannon发表的《通信的数学理论》,是关于现代信息理论的奠基性论文,它的发表标志着信息与编码理论这一学科的创立。

卷积编译码

实验四:卷积编/译码一.实验目的1.学习卷积编码的方法与码字测量。

2.学习维特比译码方法及译码的测量。

3.观察卷积码的纠错能力。

二.实验仪器1.RZ8621D实验箱一台2.20MHZ双踪示波器一台三.实验电路连接及测量点说明图7-1 用单片机AT89C2051进行卷积编码电路图图7-2 用单片机AT89C2051进行维特比译码电路图差错控制编码的方法很多,卷积码是一种既能纠随机错,又能纠实发错的编码,在同样的传输速率和设备复杂的条件下,性能较优良的一种编码。

卷积码常采用维特比软判决译码,具有较好的纠错功能。

本实验为卷积码的编译码,它是由一片AT80C2051芯片用软件编程方法实现。

其编译码电路框图如下:图中各主要测量点说明如下:TP401—源码序列TP402—卷积码序列TP403—加错或不加错卷积码序列(模拟信道的传输)TP405—卷积码译码输出序列四.实验步骤及内容(一)卷积码编码1.拨线开关介绍。

用拨动开关SW401设置输入信息。

开关拨动至上面为1,下面为0。

拨动开关共9位,左起1-8位为信息位,第九位为状态位。

第九位为“1”表示无错误,第九位为“0”表示有错误。

2.信息码设置。

如上所述,信息码设置共8位,由SW401开关位置决定,例如设置信息为DCH则八位码为1101 1100。

3.信息码观察。

为了示波器上能看到周期性的信息码和编出的卷积码,本机规定在信息位第一位前加一个“1”,在末位加两个“0”。

因此信息码序列变成1 1101 110000,我们称它们为源码序列。

将示波器1通道探头接于TP401(DTAT3),便可看到该序列波形。

4.卷积编码序列手工编码。

根据源码序列和(2.1.3)卷积码编码规秩,写出卷积码编码序列。

上述源码序列的卷积码为1101 1001 0001 1001 110000。

5.无错卷积码编码序列观察。

将拨动开关第九位(状态位)置于“1”表示无错码。

示波器1通道探头接至TP402(DATA1),2通道探头接至TP403(DATA2),观察示波器上显示的波形,看看它是否与上述卷积编码的码型一致。

实验二--卷积码编码及译码实验

实验二--卷积码编码及译码实验实验二卷积码编码及译码实验一、实验目的通过本实验掌握卷积编码的特性、产生原理及方法,卷积码的译码方法,尤其是维特比译码的原理、过程、特性及其实现方法。

二、实验内容1、观察NRZ基带信号及其卷积编码信号。

2、观察帧同步信号的生成及巴克码的特性。

3、观察卷积编码信号打孔及码速率匹配方法。

4、观察接收端帧同步过程及帧同步信号。

5、观察译码结果并深入理解维特比译码的过程。

6、观察随机差错及突发差错对卷积译码的影响。

三、基本原理1、卷积码编码卷积码是一种纠错编码,它将输入的k个信息比特编成n个比特输出,特别适合以串行形式进行传输,时延小。

卷积码编码器的形式如图17-1所示,它包括:一个由N段组成的输入移位寄存器,每段有k 段,共Nk 个寄存器;一组n 个模2和相加器;一个由n 级组成的输出移位寄存器,对应于每段k 个比特的输入序列,输出n 个比特。

12…k 12…k …12…k12…n 卷积码输出序列信息比特一次移入k 个Nk 级移位寄存器…图17-1 卷积编码器的一般形式由图17-1可以看到,n 个输出比特不仅与当前的k 个输入信息有关,还与前(N -1)k 个信息有关。

通常将N 称为约束长度(有的书中也把约束长度定为nN 或N -1)。

常把卷积码记为:(n 、k 、N ),当k =1时,N -1就是寄存器的个数。

编码效率定义为:/c R k n (17-1)卷积码的表示方法有图解表示法和解析表示法两种:解析法,它可以用数学公式直接表达,包括离散卷积法、生成矩阵法、码生成多项式法;图解表示法,包括树状图、网络图和状态图(最的图形表达形式)三种。

一般情况下,解析表示法比较适合于描述编码过程,而图形法比较适合于描述译码。

(1)图解表示法(2)解析法下面以(2,1,3)卷积编码器为例详细讲述卷积码的产生原理和表示方法。

(2,1,3)卷积码的约束长度为3,编码速率为1/2,编码器的结构如图17-2所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要卷积码是一种性能优越的信道编码。

它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。

随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。

本文对卷积码和卷积码的编译码有一个简单的介绍且给出了信道编码的发展历史及研究状况,然后详细讨论了(2,1,2)卷积码的编码过程和译码过程,通过状态转移方程和输出方程得出状态转移表和状态转移图,然后通过维特比译码器研究,总结出了维特比译码算法,最后通过Matlab软件进行设计与仿真,得到了编码程序和译码程序,其运行结果与理论分析一致。

关键字卷积码编码、信道编码、Viterbi译码、MATLAB仿真目录摘要........................................... 错误!未定义书签。

一、引言 (3)1.1发展历史及研究状况 (3)1.2设计目的和意义 (3)1.3设计方法 (4)二、卷积码编译码原理 (5)2.1 卷积码编码原理 (5)2.2编码器 (6)2.3 卷积码译码原理 (7)2.4 VITEBI 译码的关键步骤 (8)2.4.1 输入与同步单元 (8)2.4.2 支路量度计算 (8)2.4.3 路径量度的存储与更新 (8)2.4.4 信息序列的存储与更新 (8)2.4.5 判决与输出单元 (8)三、卷积码编码实现 (9)3.1 编码原理分析 (9)3.2 卷积码编码流程图 (10)四、卷积码译码实现 (11)4.1 译码编程思路 (11)4.2 卷积码译码流程图 (11)五、卷积码编译码程序的编译及仿真波形 (11)5.1 卷积码编码仿真 (12)5.2卷积码译码仿真 (13)5.3卷积码纠错码仿真 (14)六、总结 (15)七、参考文献 (16)附录 (17)一、引言1.1发展历史及研究状况1948年,Bell实验室的C.E.Shannon发表的《通信的数学理论》,是关于现代信息理论的奠基性论文,它的发表标志着信息与编码理论这一学科的创立。

20世纪40年代,R.Hamming和M.Golay提出了第一个实用的差错控制编码方案,使编码理论这个应用数学分支的发展得到了极大的推动。

分组码所存在的固有缺点可以通过采用其他的编码方法来改善,这种编码方法就是卷积码。

卷积码是Elias等人在1955年提出的。

卷积码与分组码的不同在于:它充分利用了各个信息块之间的相关性。

通常卷积码记为(n,k,N)码。

卷积码的编码过程是连续进行的,依次连续将每k个信息元输入编码器,得到n个码元,得到的码元中的检验元不仅与本码的信息元有关,还与以前时刻输入到编码器的信息元(反映在编码寄存器的内容上)有关。

同样,在卷积码的译码过程中,不仅要从本码中提取译码信息,还要充分利用以前和以后时刻收到的码组.从这些码组中提取译码相关信息,而且译码也是可以连续进行的,这样可以保证卷积码的译码延时相对比较小。

通常,在系统条件相同的条件下,在达到相同译码性能时,卷积码的信息块长度和码字长度都要比分组码的信息块长度和码字长度小,相应译码复杂性也小一些。

由Wozencraft和Reiffen在1961年提出,Fano和Jelinek分别在1963年和1969年进行改进了的序贯译码算法。

该算法是基于码字树图结构的一种次最优概率译码算法。

由Massey在1963年提出的门限译码算法。

这个算法利用码字的代数结构进行代数译码。

由Viterbi在1967 年提出的Viterbi算法是基于码字格图结构的一种最大似然译码算法,是一种最优译码算法。

在Viterbi译码算法提出之后,卷积码在通信系统中得到了极为广泛的应用。

如GSM、3G、商业卫星通信系统等。

1.2设计目的和意义因为信道中信号不可避免会受到干扰而出错。

为实现可靠性通信,主要有两种途径:一种是增加发送信号的功率,提高接收端的信号噪声比;另一种是采用编码的方法对信道差错进行控制。

前者常常受条件限制,不是所有情况都能采用。

而编码理论可以解决这个问题,使得成本降低,实用性增强。

随着现代通信的发展,卷积码以其高速性和可靠性在实际应用中越来越广泛。

1967年Viterbi译码算法的提出,使卷积码成为信道编码中最重要的编码方式之一。

在卷积码中,因为Viterbi算法效率高,速度快,结构相对简单等特点,被广泛应用于各种数据传输系统。

特别是深空通信、卫星通信系统中。

因此采用Viterbi译码算法具有非常现实的意义。

1.3设计方法本文在分析卷积码编译码器原理的基础上,通过基于MATLAB对卷积编码,解码进行仿真。

通过仿真可以更清楚的认识到卷积码的编码,解码的各个环节,并对仿真结果进行了分析。

得出卷积码Viterbi译码的误比特性能和回溯长度,码率,约束长度的关系。

二、卷积码编译码原理2.1 卷积码编码原理2.1.1卷积码简介卷积码,又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。

卷积码编码的当前输出v(l)不仅与当前输入消息u(l)相关,还与此去前输入的m 个消息u(l-1),…,u(l-m) 相关,即v(l)=f(u(l),u(l-1),…,u(l-m)), l=0,1,2…卷积编码电路中移位寄存器初态可设定为全0,电路为按段工作方式,即对每段k 比特输出入,产生一段n 比特输出。

任意一输入段u(l-h)与输出v(l)的关系都是一个特殊的(n,k )线性分组码的编码关系,即存在k*n 的二元矩阵h G ,使得h G h l u l v ∙-=)()(, h=0,1,2,…,m因此对于消息段序列u=(u(0),u(1),…,u(m),u(m+1),…),相应的输出端序列为v=(v(0),v(1),…,v(m),v(m+1),…),并满足0)0()0(G u v =01)1()0()1(G u G u v +=011)()1()1()0()(G m u G m u G u G u m v m m +-+++=-011)1()()2()1()1(G m u G m u G u G u m v m m +++++=+-卷积编码电路在按段工作方式下只需存储或者记忆m 段的消息输入,电路中输入移位寄存器最多只有k m ∙个有效的寄存器单元,而输出移位寄存器仅起一个并串转换作用。

因此称参量m 为卷积码的记忆长度(段)。

二元(n ,k ,m )卷积码共有M 2个不同的状态,记为1210,,,-M S S S 当状态为)(l δ(或δ)时,输入段)(l u (或u )产生编码输出端)(l v (或v ) 并使该状态改变(或称为转移)到新的状态)1(+l δ(或'δ)。

δ到'δ的转移过程称为一个转移分支,记为(δ,'δ)或()(l δ,)1(+l δ)并标记转移过程为)(/)(l u l v 或v/u 。

以状态δ为结点,转移分支为有向边描述卷积码的所有不同状态转移的有向图,称为卷积码的状态转移图。

2.2编码器2.2.1编码器的一般结构卷积码的编码器一般都比较简单。

输入图2-1 卷积码编码器框图图2-1是一般情况下的卷积码编码器框图。

它包括NK 级的输入移位器,一组n 个模2和加法器和n 级的输出移位寄存器 [6]。

对应于每段k 比特的输入序列,输出n 个比特。

由图可知,n 个输出比特不但与当前的k 个输入比特有关,而且与以前的(N-1)k 个输入信息比特有关。

整个编码过程可以看成是输入信息序列与由移位寄存器和模2加法器的连接方式所决定的另一个序列的卷积,卷积码由此得名。

本文采用的是冲击响应描述法编码思想。

2.2.2编码器的参数⑴ 有k 个输入信息端,n 个输出端(k<n ),K-1节移位寄存器(共需k(K-1)个寄存器单元),称做(n,k,K )卷积码。

⑵ 通常称K 为约束长度(一般来说,约束长度越大,则码字纠错性能越好)。

⑶ 码的效率:k/n⑷ 编码前,k(K-1)个寄存器单元全部复位清零。

⑸ 由于一段消息不仅影响当前段的编码输出,还影响其后m 段的编码输出,所以称参量为卷积吗的约束比特长度为n K n A ∙=注意进入卷积编码器的最后m 段消息仍是要编码输出的消息,对这最后m 段消息的编码处理,称作卷积编码的结尾处理。

一种常见的结尾处理方法是额外输入m段无效的0数据比特,一方面将存储的m 段消息编码全部推出,另一方面保证编码器回到全0的初态。

2.3 卷积码译码原理维特比算法的基本思想是把接收到的矢量,和网格图上诸种可能的路径比较,删去距离大的路径,保留距离小的路径,以距离最小路径作为发码的估值。

它的原理是将接收到的信号序列和所有可能的发送信号序列作比较,选择其中汉明距离最小的序列作为现在的发送信号序列。

为简便起见,讨论(n,k,N)卷积码当k=1的情形,从全0状态起始点开始讨论。

由卷积码网格图的前N-1级中支路构成的路径互不相交,即最初的2N-r条路径各不相同;当到达第N级时,每条路径都有2N-1条支路延伸到第N级上;而第N级上的每2条支路又都汇聚在一个节点上。

第N级以后的网格图图形完全是重复第N级的图形。

在维特比算法中,把汇聚在每个节点上的2条路径的对数似然函数累加值进行比较;然后把具有较大对数似然函数累加值的路径保存下来,称此部分路径为幸存路径,而丢弃另一条路径;经挑选后,第N级只留下2N-r条幸存路径,选出的路径连同它们的对数似然函数累加值一起被存储起来。

因每个节点引出2N-1条支路,因此以后各级中路径的延伸都增大一倍;但比较它们的似然函数累加值后,丢弃一半,结果留存下来的路径总数保持常数(等于其状态数)。

由此可见,上述译码过程中的基本操作是“加→比→选”。

即每级求出对数似然函数累加值,然后两两比较并做出选择。

有时会出现2条路径的对数似然函数累加值相等的情形,此时可任意选择其中一条作为“幸存路径”。

每一级都有21-N条幸存路径,则当序列发送完毕后,为判断其最后结果,通常要在网格图的终结处加上一些结束信息。

通常结束信息为N-1个已知信息,当然结束信息大于N-1也可以。

在此信息到来时,因每一个状态只有与已知发送信息相符的那条支路被延伸,因而在每级比较后,幸存路径减少一半。

因此,在接收到N-1个已知信息后,整个网格图中只有惟一的一条幸存路径保留下来。

这就是译码所得到的路径,这条译码路径和发送序列是最相似的。

从上述卷积码的译码过程可以看出:约束长度为N时,需要存储和计算21-N条路径的参量。

由此可见,维特比算法的复杂度随约束长度N按指数形式增长2N。

故维特比算法适合约束长度较小(N≤10)的编码。

当编码约束度不太大(≤10)或者误码率要求不太高(>105 )时,它的设备比较简单,用硬件译码计算速度快。

Viterbi译码的缺点是随着约束长度的增加算法的复杂度增加很快。