【精品课件】数字电子技术第三章习题

数字电子技术题目第三章

数字电子技术题目第三章第三章组合逻辑电路一.填空题1.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A2A1A0=100时,输出Y7’Y6’Y5’Y4’Y3’Y2’Y1’Y0’应为。

2.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A2A1A0=101时,输出Y7’Y6’Y5’Y4’Y3’Y2’Y1’Y0’应为。

3.数字电路按照是否有记忆功能通常可分为两类:和。

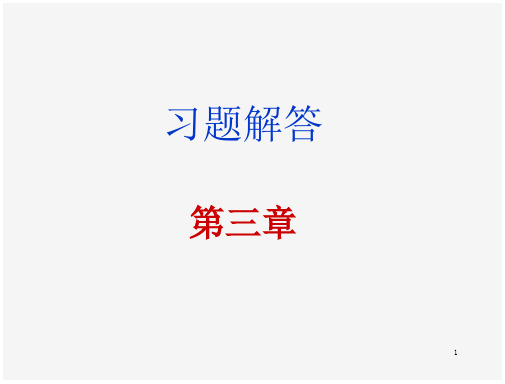

4.16选1数据选择器,其地址输入端有个5.8选1数据选择器有____________条地址控制线。

二.选择题1.在下列逻辑电路中,不是组合逻辑电路的是A.译码器B.编码器C.全加器D.寄存器2.三十二路数据选择器,其地址输入端有个A.16B.2C.5D.83.数据选择器是具有通道的器件A.多输入单输出B.多输入多输出C.单输入单输出D.单输入多输出4.欲对全班54个同学以二进制代码编码表示,最少需要二进制的位数是()A.5B.6C.10D.535.已知A、B为逻辑门的输入端,F为输出端,其输入、输出波形如图1所示。

试判断这是哪种逻辑门的波形。

图1A.与非门B.与门C.或非门D.或门三.分析与设计1.将逻辑函数F=A’B’+A’C’+ABC转化为与非-与非表达式,并画出只由与非门实现的逻辑电路图。

2.将逻辑函数Y=AB+BC+CA化为与非-与非形式,并画出只由与非门实现的逻辑电路图。

3.用8选1数据选择器74HC151实现函数F=A’C’+A’B’C+AB’C’+ABC。

74HC1514.用8选1数据选择器74HC151实现逻辑函数F=A’C’+A’B’+ABC。

74HC1515.用8选1数据选择器实现函数F=AC+A’BC’+A’B’C。

74HC1516.用译码器74HC138实现函数F=AC+A’BC’+A’B’C。

要求写出设计过程。

7.译码器74HC138的逻辑符号如图8所示。

用译码器74HC138实现逻辑函数F=AC+A’BC+A’B’。

数字电子技术基础 第三章(1)11-优质课件

图3.1.2 正逻辑与负逻辑

一些概念

1、片上系统(SoC) 2、双极型TTL电路 3、CMOS

1961年美国TI公司,第一片数字集成电路 (Integrated Circuits, IC)。

VLSI(Very Large Scale Integration)

3.2 半导体二极管门电路

3.2.1 半导体二极管 的开关特性

图3.2.1 二极管开关电路

可近似用PN结方程和下图所 示的伏安特性曲线来描述。

i Is ev/VT 1

其中:i为流过二极管的电流。 v为加到二极管两端的电压。

nkT VT q

图3.2.2 二极管的伏安特性

图3.2.3 二极管伏安特性的几种近似方法

三、电源的动态尖峰电流

图3.5.23 TTL反相器电源电流的计算 (a)vO=VOL 的情况 (b) vO=VOH的情况

图3.5.24 TTL反相器的电源动态尖峰电流

图3.5.25 TTL反相器电源尖峰电流的计算

图3.5.26 电源尖峰电流的近似波形

例3.5.4 计算f=5MHz下电源电流的平均值

图3.3.xx CMOS三态门电路结构之二 (a)用或非门控制 (b)用与非门控制

图3.3.xx CMOS三态门电路结构之三 可连接成总线结构。还能实现数据的双向传输。

3.3.6 CMOS电路的正确使用

一、输入电路的静电防护

1、在存储和运输CMOS器件时最好采用金属屏蔽层 作包装材料,避免产生静电。

tPHL:输出由高电平跳变为低电 平的传输延迟时间。

tPLH:输出由低电平跳变为高电 平的传输延迟时间。

tPD: 经常用平均传输延迟时间tPD

来表示tPHL和tPLH(通常相等)

数字电子技术基础第三版课后习题解答与第章

【题3-2】 解:),=(A田B) C=A⑥B+C}、=AB+(AB)C=AB+(AB+AB)C=AB+ABC+ABC=AB+BC+AC)=A B CY,=AB+(A B)C=AB+BC+AC两个电路功能相同,均为全加器。

14

(2) CDAB 00 01 11o0[ X0111 1 1 X10 1 1

A₃B₃…A₀B₀ 91A₃B₃…A₀B₀A<B.A>R低位 A=B74LS85Fg FxBF,A>B

A₂B₇…A₄B₄A=B74LS85FAn FxnF

【题3-9】 解:连线图如图3-26所示。

图3 - 26

27

【题3-10】 解:A=A₃A₂A₁A₀ 8421BCD 码 B=B₃B₂B₁B₀ 余3 BCD 码C=C₃C₂C₁C₀ 2421BCD 码 D=D₃D₂D₁D₀ 余 3 循环码(1)卡诺图如图3 - 27所示。B₃=A₃+A₂A₁+A₂A₀=A₂A₂A₁A₂A₀

2

A

B

A

Y'

2

0

0

0

1

0

0

1

1

0

0

1

0

0

0

1

1

1

0

1

)

3-2 解:(1)X=AB;Y=AB+AB=AB+AB;Z=AB。真值表如表3-10所示。表3-10

(2)实现1 位数值比较功能。

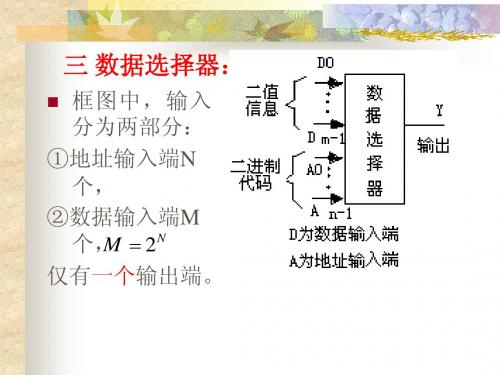

3

Y₀=X,④X 。 Y₀=Y₁X₀=X₂X₇X。若令 X₂=B₂ 、X₁=B₁ 、λ₀=B, 则当 K=1 时电路可正确地实现3位二进制码到3位循环码的转换,即有 Y₂=G₂ 、Y,=G₁ 、Y₀=G₀ 。 若 令X₂=G₂ 、X,=G₁、X₀=G₀, 则当 K=0 时,通过比较可明显看出,只要去掉一个反相器便可实现3位循环码到3位二进制码的转换,即有 Y₂=B₂ 、Y₁=B₁ 、Y₀=B₀。

数字电子技术第三章-2

根据全加器的逻辑功能可知 (CO)i=AiBi+(Ai+Bi)(CI)i 设:AiBi=Gi, Ai+Bi=Pi 得 (CO)i=Gi+Pi(CI)i =Gi+Pi[Gi-1+Pi-1(CI)i-1] = Gi+PiGi-1+ Pi Pi-1[Gi-2+Pi-2(CI)i-2] …… =Gi+PiGi-1+ Pi Pi-1Gi-2+……Pi Pi-1……P1G0 +Pi Pi-1……P0C0 因为CO=0,所以当A和B输入时即可计算出各位的CI, 使运算速度大大提高。

以三位为例

CO3 G3 P3 CI 3 G3 P3 (G2 P2CI 2 ) G3 P3 [G2 P2 (G1 P CI1 )] 1

MSI 四位超前进位加法器74LS283的逻辑 图见P167、逻辑框图如下

3.用加法器设计组合逻辑电路: 逻辑函数能化成变量相加的可用。

( A A ) D

1 0

4

( A1 A0 ) D5 ( A1 A0 ) D6 ( A1 A0 ) D7 A2

2. 用数据选择器设计组合逻辑电路:

数据选择器 ①只可实现单输出的逻辑函数; ②地址输入端的个数可等于逻辑函数的 变量数,也可比逻辑函数的变量数少1个 例:分别用四选一和八选一数据选择器 设计交通灯监视电路。

74LS153的逻辑结构 图如右图 S1 0 时

Y1 D10 A1 A0 D11 A1 A0

12 1 0 13 1 0 1

D A A D A A S

Y2的表达式类似。

数字电路 第三章习题答案课件

解: 根据题意,该控制电路有三个输入A,B,C; 三个输出G, Y,R。G代表绿灯,Y代表黄灯,R代表红灯。状态赋值如下:1 表示水在电极之上,0表示水在电极之下; 0表示灯亮,1表示灯灭。 按照题意列出的真值表如下。由真值表画出的卡诺图:

3-11

G A B AB

Y AB C ABC RC

3-11

试用六个与非门设计一个水箱控制电路。图为水箱示意图。A、B、C是三个电极。 当电极被水浸没时,会有信号输出。水面在A,B间为正常状态,点亮绿灯G;水面在 B、C间或在A以上为异常状态,点亮黄灯Y;水面在C以下为危险状态.点亮红灯R。

3-4 试分析题示逻辑图的功能。图中G1,G0为控制端,A,B为输入端。要求写

出G1,G0四种取值下F的表达式。

3-5 列出题示逻辑图的真值表。图中T331为输出低电平有效的8421码译码器。

T33l为8421码的四线一十·线译码器,由于A3=0, 便变成了三线一八线译码器。

Si Ai BiC Ai BiC Ai BiC Ai BiCi

S1S0 ( AB AB )

3-10

F S1 AB S0 AB S0 A B S0 AB S1S0 A B F F S1 AB S0 AB S0 AB S0 AB S1S0 AB

3-11

试用六个与非门设计一个水箱控制电路。图为水箱示意图。A、B、C是三个电极。 当电极被水浸没时,会有信号输出。水面在A,B间为正常状态,点亮绿灯G;水面在 B、C间或在A以上为异常状态,点亮黄灯Y;水面在C以下为危险状态.点亮红灯R。

X2X1X0 = Z2Z1Z0时,输出 F=0

X2X1X0 Z2Z1Z0时,输出 F=1

3-9 由八线一三线优先编码器74148和与非门构成的电路如下,试说明该电路的

数字电子技术第三章(组合逻辑电路)作业及答案

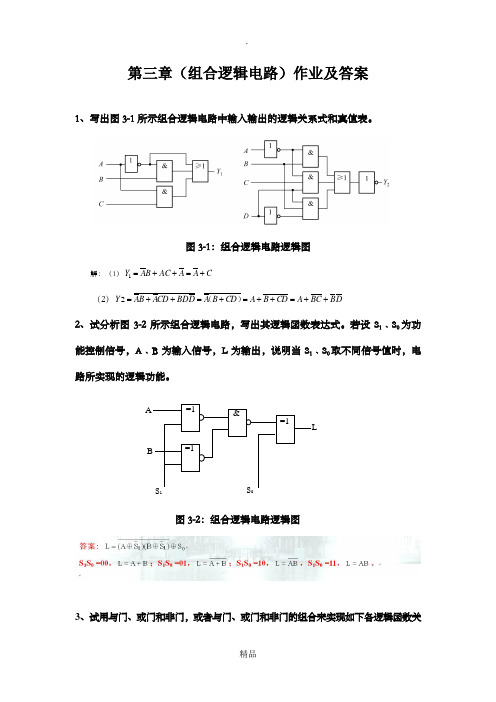

第三章(组合逻辑电路)作业及答案1、写出图3-1所示组合逻辑电路中输入输出的逻辑关系式和真值表。

图3-1:组合逻辑电路逻辑图解:(1)C A A AC B AY +=++=1(2)D B C B A CD B A CD B A D BD CD A B A Y ++=++=+=++=)(2 2、试分析图3-2所示组合逻辑电路,写出其逻辑函数表达式。

若设S 1﹑S 0为功能控制信号,A ﹑B 为输入信号,L 为输出,说明当S 1﹑S 0取不同信号值时,电路所实现的逻辑功能。

图3-2:组合逻辑电路逻辑图3、试用与门、或门和非门,或者与门、或门和非门的组合来实现如下各逻辑函数关ABS 1S=1=1&=1系,画出相应的逻辑电路图。

(1)1Y AB BC=+(2)2Y A C B=+()(3)3Y ABC B EF G=++()&&1≥Y1.1ABC.&1≥Y2.1ABC&1≥1≥&&1ABC.EFG.Y3...4、试用门电路设计4线-2线优先编码器,输入、输出信号都是高电平有效,要求任一按键按下时,G S为1,否则G S=0;还要求没有按键按下时,E O信号为1,否则为0。

5、试用逻辑门电路设计一个2选1数据选择器,输入信号为A、B,选择信号为S,输出信号为Y,要求写出真值表、逻辑函数表达式和画出逻辑电路图。

6、某公司3条装配线各需要100kW电力,采用两台发电动机供电,一台100kW,另外一台是200kW,3条装配线不同时开工,试设计一个发电动机控制电路,可以按照需求启动发电动机以达到节电的目的。

7、图3-3是由3线/8线译码器74LS138和与非门构成的组合逻辑电路,试写出P和P2的逻辑表达式,并列出真值表,说明其逻辑功能。

1BIN/OCT01201234567B AC 10074LS138P 1P 2图3-3 组合逻辑电路图8、试用3线-8线译码器74LS138和与非门实现以下多输出函数:1F AB C AB BC AC =++(,,) ∑=),,,(),,(75422m C B A F9、图3-4是由八选一数据选择器74LS151构成的组合逻辑电路,试写出当G 1G 0为各种不同取值时输出Y 与输入A 、B 的逻辑函数表达式。

数字电子技术基础-第3章课后习题答案

第3章集成逻辑门电路3-1 如图3-1a)~d)所示4个TTL门电路,A、B端输入的波形如图e)所示,试分别画出F1、F2、F3和F4的波形图。

A1A234a)b)c)d)F1F2F3F4BAe)图3-1 题3-1图解:从图3-1a)~d)可知,11F=,2F A B=+,3F A B=⊕,4F A B= ,输出波形图如图3-2所示。

F1F2F3F4AB图3-2题3-1输出波形图3-2 电路如图3-3a )所示,输入A 、B 的电压波形如图3-3b )所示,试画出各个门电路输出端的电压波形。

1A 23b)a)AB图3-3 题3-2图解:从图3-3a )可知,1F AB =,2F A B =+,3F A B =⊕,输出波形如图3-4所示。

F 1F 2F 3AB图3-4 题3-2输出波形3-3在图3-5a )所示的正逻辑与门和图b )所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明F 和A 、B 之间是什么逻辑关系。

b)a)图3-5 题3-3图解:(1)图3-5a )负逻辑真值表如表3-1所示。

表3-1 与门负逻辑真值表F 与A 、B 之间相当于正逻辑的“或”操作。

(2)图3-5b )负逻辑真值表如表3-2所示。

表3-2 或门负逻辑真值表F 与A 、B 之间相当于正逻辑的“与”操作。

3-4试说明能否将与非门、或非门和异或门当做反相器使用?如果可以,各输入端应如何连接?解:与非门、或非门和异或门经过处理以后均可以实现反相器功能。

1)与非门:将多余输入端接至高电平或与另一端并联; 2)或非门:将多余输入端接至低电平或与另一端并联;3) 异或门:将另一个输入端接高电平。

3-5为了实现图3-6所示的各TTL 门电路输出端所示的逻辑关系,请合理地将多余的输入端进行处理。

b)a)AB=A B=+A BC DABC D图3-6 题3-5图解:a )多余输入端可以悬空,但建议接高电平或与另两个输入端的一端相连;b )多余输入端接低电平或与另两个输入端的一端相连;c) 未用与门的两个输入端至少一端接低电平,另一端可以悬空、接高电平或接低电平;d )未用或门的两个输入端悬空或都接高电平。

数字电子技术第三章习题课

辽宁工业大学

电子与信息工程学院 电子信息工程教研室

第3章、门电路

一、本章内容: 逻辑门电路是各种数字电路及数字系统的基本逻辑单元。本章首先介

绍了半导体二极管和三极管的开关特性,同时介绍了TTL和CMOS两类集成 门电路的特性,即它们的逻辑功能和外部电气特性(包括电压传输特性、 输入特性、输出特性和动态特性等)。为便于合理选择和正确使用数字 集成器件,必须熟悉它们的主要参数,逻辑门使用中的接口问题以及其 他一些实际问题。

写出真值表。

DM

1

表题2.18

△ △ △

S1 S0

≥1

DN

EN 1

EN

输入

输

S1

S0

Y

0

0

0

1

1

DP

1

1

0

EN

&

图3.6

1

1

, 解: 在输入S1、S0各种取值下的输出Y见下表。

输入

S1

S0

输出 Y

0

0

Y DN

0

1

Y DP

信息工程学院 电子教研室

1

9

Y DM

第3章、门电路

解:Y1为低电平;Y2为高电平;Y3为高电平;Y4为低电平;Y5为低电平;Y6 为高阻态;Y7为高电平;Y8为低电平。

电子与信息工程学院

19

电子教研室

第3章、门电路

题3.15 说明图3.15中各门电路的输出时高电平还是低电平。已知他们 都是74HC系列的CMOS电路。

解:Y1为高电平;Y2为高电平;Y3为低电平;Y4为低电平。

解 (a) Y1 ABCDE (c) Y3 ABC DEF

数电电子技术第三章习题参考答案

3.16 TTL与非门,计算可驱动多少同样的门 与非门, 与非门 VOH ≥ 3.2V,VOL≤0.4V;IIL≤-1.6mA,IIH≤40uA; , ; , ; IOL(max)=16mA,IOH(max)=-0.4mA。 。 (书P121,P133) , )

VOL≤0.4V:N1 ≤IOL(max)/|IIL(max)|=10 : VOH ≥3.2V: N2 ≤ |IOH(max)|/pIIH(max)=5

3.8 画出输出电压波形

Y1=(AB)’(CD)’

D=1 Y2=ABC D=0 Y2为高阻态

《数字电子技术基础》第五版 数字电子技术基础》

3.9 (书P95~96)OD门, ) 门 IOH(max)=5uA,IOL(max)=5.2mA,VOL(max)=0.33V; IIH(max)=1uA,IIL(max)=-1uA;VDD=5V,求RL 求

《数字电子技术基础》第五版 数字电子技术基础》

3.18 万用表测得的电压,万用表内阻为 万用表测得的电压, 5V量程(与非门为 量程( 电路) 量程 与非门为TTL电路) 电路 (1) vI1悬空; ) 悬空; vI1 (2) vI1接低电平(0.2V); ) 接低电平( ); vI2 (3) vI1接高电平(3.2V); ) 接高电平( ); V 电阻接地; (4) vI1经51 电阻接地; ) 电阻接地。 (5) vI1经10k 电阻接地。 ) (1)vI2≈1.4V ) (2) vI2≈0.2V ) (3) vI2≈1.4V ) (4) vI2≈0V ) (5) vI2≈1.4V )

Y=AB

Y=A+B

《数字电子技术基础》第五版 数字电子技术基础》

A 0 0 1 1

B 0 1 0 1

《数字电子技术 》课件第3章 (8)

第3章 触发器

3.3 边沿触发器

3.3.1 边沿JK

为了提高触发器的可靠性,增强抗干扰能力,我们希望 触发器的次态仅仅取决于CP信号下降沿(或上升沿)到达 时刻输入信号的状态,而在此之前和之后输入状态的变化对 触发器的次态没有影响。负边沿JK触发器即可满足这一要 求,它克服了空翻现象,提高了触发器的工作可靠性和抗干 扰能力。

第3章 触发器

3.2.2 同步JK

1. 为了克服R=S=1时触发器的状态输出错误,人们在电 路结构上作了进一步改进,把触发器的输出端连接到输入 端,这样G3 、G4的输出不会同时出现0,从而避免了不定 状态的出现,电路如图3.6(a)所示,图3.6(b)所示为其逻 辑符号。J和K为信号输入端。

第3章 触发器

第3章 触发器

1. 负边沿JK触发器的逻辑电路和逻辑符号如图3.9所示。 这个电路包含一个由与或非门G1、G2组成的基本RS触发器 和两个输入控制门G3、G4,而且与非门G3、G4的平均延迟 时间tpd1比与或非门构成的基本触发器的平均延迟时间tpd2

第3章 触发器

图3.9 (a) 逻辑电路;

JK (b) 逻辑符号

(1) 当 RD =0, S D =1时,触发器置0。因 RD =0,与

非门2输出 Q =1,这时与非门1的输入都为高电平1,输出 Q=0,触发器被置0。使触发器输出0状态的输入端 RD 称为 置0

第3章 触发器

(2) 当 RD =1, S D =0时,触发器置1。因 S D =0,与非

门1输出Q=1,这时与非门2的输入都为高电平1,输出 Q=0,

第3章 触发器

(4) 当 RD =0, S D =0时,触发器输出状态Q= Q =1,输出状态错误。而且在 RD 和 S D 同时由0变为1时,由

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

所以此种输入的接法也属于逻辑0。

i

E1

+ T1

R

Vi

图3.1 输入端通过 电阻接地的情况

第3章、门电路

例3.2为什么说TTL与非门的输入端在以下4种接法下,都属于逻辑1: (1)输入端悬空;(2)输入端接高于2V的电源; (3)输入端接同类与非门的输出高电压3.6V; (4)输入端接10kΩ的电阻到地。

解: TTL电路输出低电平 VOL0.4V,输入低电平 VIL0.8V ,所以前三种情况输入都在低电平范围内,属于逻辑0。 i B 1 当输入端通过200W的电阻接地时,见图3.1。 由电路分析得:

+ VC C

R b1 4K

R

Vi RRb

(VCC0.7)

1

0.2 (50.7)0.2V 0.24

可见,输入电压小于关门电平,

解:TTL电路输出高电平 VOH2.4V,输入高电平 VIH 2V 。

对于(2)和(3),输入电压都高于2V,属于逻辑1。当输入悬空时,

输入PN结截止,与输入高电平使PN结截止一样,因此为逻辑1;

当输入端接10kW的电阻到地时,见图3.2。

+ VC C

Vi RRRb

(VCC0.7)

1

10 (50.7)3.1V 104

VD D

VD D

A B

(a)

L1

A

B

C

图3.5

L (b)

解:图3.5所示为CMOS逻辑电路。 其表达式:

L1ABAB

L2 ABC

第3章、门电路

△ △ △

例3.6 分析图3.6所示电路,求输入S1、S0各种取值下的输出Y,

写出真值表。

DM

1

表题2.18

S1 S0

≥1

DN

EN 1

EN

输入

S1

S0

Y

0

iB 1

R b1

4K

可见,输入电压大于2V,所以此种输入的接法也属于逻辑1。 但要注意的是,在这种输入的作用下,会使T1的集电结正偏导 通、T2、T3管饱和导通,VB1=2.1V。而R的存在致使T1的发射 结也是导通的, 所以输入电压Vi最终被钳制在1.4V上。

i

E1

+ T1

R

Viቤተ መጻሕፍቲ ባይዱ

图3.2 输入端通过 电阻接地的情况

等于A。再经过输出端反相器以后得到

(d)此电路有两个输入端,可以分几种情况讨论其工作过程: 当输入A、B均为低电平时,T1、T2都截止,L4以下部分的支路不通,输出高电平; 当输入A、B一高一低时,T1、T2中有个饱和导通,L4以下部分的支路导通,输出低电 平; 当输入A、B均为高电平时,T1、T2都饱和导通,L4以下部分的支路导通,输出低电平 。 根据以上分析可得表达式: L4ABAB

第3章、门电路

例3.4 在图3.4中,所有的门电路都为TTL门,设输入A、B、C的波形

如图3.4 (d)所示,试定量画出各输出的波形图。

VCC

A

≥1

=1

B

(a)

C

A

&

L1

B

≥1 L2

(b)

A B C

解

G1 &

EN

△

(c)

A B C

L1 L2 L3

A

B

&

L3

C

图3.4

(d)

第3章、门电路

例3.5写出图3.5 所示电路的逻辑表达式。

《数字电子技术基础》习题课 教学课件

第3章、门电路

一、本章内容: 逻辑门电路是各种数字电路及数字系统的基本逻辑单元。本章首先介

绍了半导体二极管和三极管的开关特性,同时介绍了TTL和CMOS两类集成 门电路的特性,即它们的逻辑功能和外部电气特性(包括电压传输特性、 输入特性、输出特性和动态特性等)。为便于合理选择和正确使用数字 集成器件,必须熟悉它们的主要参数,逻辑门使用中的接口问题以及其 他一些实际问题。

第3章、门电路

例3.8试分析图3.8电路的逻辑功能。

图3.8

第3章、门电路

解: 这个CMOS电路可以划分成四个反相器和一个传输门共五个功能模

块。传输门的工作状态由B和

控制,当B=0时传输门导通,输

出等于输入的 ;当B=1时传输门截止。电路图中间的一个反相

状态的控制,当B=0时( =1) 和 同时导通,反相器工作,输出

二、本章要求:

1.熟练掌握各种门电路的逻辑功能、符号和参数。 2.正确理解以下基本概念:推拉式输出、线与、高阻态。 3.熟悉各门电路的结构、工作原理、主要参数及应用中注意的问题。 4.会应用各种门电路。

第3章、门电路

三、典型例题:

例3.1 为什么说TTL与非门的输入端在以下4种接法下都属于逻辑0: (1)输入端接地;(2)输入端接低于0.8V的电源; (3)输入端接同类与非门的输出低电压0.3V; (4)输入端通过200Ω的电阻接地。

第3章、门电路

例3.3 电路如图3.3所示,写出输出L的表达式。设电路中各元件参数满

足使三极管处于饱和及截止的条件。

A B

A B

D1

D2 C

R

D3 D4

R

+ VC C (a ) + VC C

RC

Rb

3

L3

1

T

2

1

Rb

3

1

T

2

2

L1 A

R1

1

2

3

T1

D

1

(b )

+ VC C

RC

3

L2

2T 2

+ VC C

RC

L4

Rb

33

Rb

A

1

T 21 2T2

1

B

(c )

(d )

图3.3电路图

第3章、门电路

解:(a)此电路由两级逻辑门构成,第一级是与门,输出为AB;第二级是或门, 输出为: L1=AB+C

(b)此电路是只有一个输入端的逻辑电路。当输入端A为低电平时,T1发射结导 通,VB1<2.1V,D、T2截止,L2输出高电平;当输入端A为高电平时,T1发射结不通,+VCC 足以使D、T2导通,L2输出低电平。由以上分析可见:L2 A

0

0

1

输

1

DP

1

EN

&

图3.6

1

0

1

1

, 解: 在输入S1、S0各种取值下的输出Y见下表。

输入

S1

S0

输出 Y

0

0

Y DN

0

1

Y DP

1

0

Y DM

1

1

Y DM

第3章、门电路

例3.7试分析如下图所示TTL门电路的逻辑功能。

解: 首先将电路划分为虚线框内的六个基本功能模块:最左边的三个 “与”结构模块、中间的两个“或非”结构模块和最右边的“推拉式 输出”模块,然后自左而右地逐个写出每个模块的逻辑关系式(如图 中所示),最后得到