电子科技大学CMOS模拟集成设计Hspice仿真

CMOS译码器设计与HSPICE仿真

《集成电路设计》课程设计报告基于HSPICE的晶体管级电路设计与仿真题目:CMOS2-4译码器设计与HSPICE仿真学院专业班级学生姓名指导教师提交日期目录一、设计目的 (1)二、设计要求和设计指标 (1)三、设计内容 (1)CMOS2-4译码器原理及电路设计 (1)门级设计 (1)门的CMOS实现 (2)仿真结果与分析 (5)四、总结 (7)五、主要参考文献 (10)一、设计目的熟悉《数字集成电路设计》课程,学习Hspice软件的使用,以及.sp文件的编写,进一步理解掌握CMOS设计组合逻辑电路与时序逻辑电路的基本知识,继而熟练地运用半导体集成电路知识。

二、设计要求和设计指标(1)了解C2MOS 主从正沿触发寄存器的电路结构、电路原理;(2)了解电路具体参数,包含的晶体管数目、晶体管尺寸、连线情况等;(3)利用HSPICE软件,编写.sp 文件;(4)仿真该sp 文件,得出描述电路性能的函数图线、波形等参数;(5)在具体的软硬件实验环境中,进行设计模拟、仿真和调试,解决设计调试中的具体问题;得出结论,并完成设计。

三、设计内容CMOS2-4译码器原理及电路设计门级设计译码器是组合逻辑电路的一个重要器件,把代码状态的特定含义“翻译”出来的过程叫做译码,实现译码操作的电路称为译码器。

译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。

而CMOS2-4译码,是将其输入的两位二进制代码“00”“01”“10”“11”进行翻译,从而控制电路的输出线路,实现四路译码的过程。

其真值表如图表1所示:A B Y0Y1Y2Y3000111011011101101111110图表1由图表1可以得到CMOS2-4译码器的布尔表达式为:Y0=Y1=Y2=Y3=从而可以得到CMOS2-4译码器门级设计的电路图,如图表2:123U1A 12U5A123U6A123U2A 12U4A123图表2这样,通过两个非门和四个与非门就可以实现如图表1中的真值表所示的逻辑功能。

电子科技大学 集成电路原理实验模拟集成电路版图设计与验证 王向展

实验报告课程名称:集成电路原理实验名称:模拟集成电路版图设计与验证小组成员:实验地点:科技实验大楼606实验时间:2017年6月19日2017年6月19日微电子与固体电子学院一、实验名称:模拟集成电路版图设计与验证二、实验学时:4三、实验原理1、电路设计与仿真实验2内容,根据电路的指标和工作条件,然后通过模拟计算,决定电路中各器件的参数(包括电参数、几何参数等),EDA软件进行模拟仿真。

2、工艺设计根据电路特点结合所给的工艺,再按电路中各器件的参数要求,确定满足这些参数的工艺参数、工艺流程和工艺条件。

3、版图设计按电路设计和确定的工艺流程,把电路中有源器件、阻容元件及互连以一定的规则布置在Candence下的版图编辑器内。

并优化版图结构。

四、实验目的本实验是基于微电子技术应用背景和《集成电路原理》课程设置及其特点而设置,为IC设计性实验。

其目的在于:1、根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路版图设计,掌握基本的IC版图布局布线技巧。

2、学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的的设计与验证。

通过该实验,使学生掌握CMOS模拟IC版图设计的流程,加深对课程知识的感性认识,增强学生的设计与综合分析能力。

五、实验内容1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、根据实验2所得参数,自主完成版图设计,并掌握布局布线的基本技巧。

3、整理版图生成文件,总结、撰写并提交实验报告。

六、实验仪器设备(1)工作站或微机终端一台(2)EDA仿真软件1套七、实验步骤1、根据实验指导书掌握Cadence EDA仿真环境的调用。

熟悉版图编辑器Layout Editor的使用。

了解基本的布局布线方法及元器件的画法。

2、根据实验2所计算验证的两级共源CMOS运放的元器件参数如表1所示,在版图设计器里画出相应的元器件,对V+、V-、V out、V DD、GND的压焊点位置合理化放置,通过金属画线将各个元器件按实验2的电路图合理连接,避免跳线。

第3讲 Hspice电路仿真

随着新型电子器件和材料的不 断涌现,Hspice电路仿真将不 断更新和完善元件模型库,提 供更加全面和精确的仿真支持 。

THANKS

[ 感谢观看 ]

数字电路设计与分析

Hspice支持数字电路的逻辑仿真、 时序分析和功耗分析等。

混合信号电路设计与分析

Hspice可用于混合信号电路的设计 、仿真和验证,包括模数转换器和数 模转换器等。

通信系统设计与分析

Hspice可用于通信系统的信号处理 、调制解调、信道编码和误码率分析 等。

CHAPTER 02

CHAPTER 04

Hspice在模拟电路仿真中的应用

直流工作点分析

1 2

确定电路的静态工作点

通过Hspice仿真,可以获取电路中各个节点的直 流电压和电流,从而确定电路的静态工作点。

分析电路性能

根据静态工作点的数据,可以分析电路的性能指 标,如放大倍数、输入/输出电阻等。

3

优化电路设计

通过比较不同设计方案下的静态工作点,可以优 化电路设计,提高电路性能。

CHAPTER 07

总结与展望

Hspice电路仿真优势与局限性

高效性

Hspice电路仿真可以快速进行电路分 析和设计验证,大大缩短了产品开发 周期。

精确性

Hspice采用了先进的电路仿真算法, 能够精确地模拟电路的实际行为,提 高了设计的可靠性。

Hspice电路仿真优势与局限性

Hspice电路仿真优势与局限性

Monte Carlo统计分析

随机性建模

考虑元器件参数的随机性,通过Monte Carlo方法对电路性能进行统计分析。

概率分布函数

支持多种概率分布函数,如正态分布、均匀分布等 ,以模拟实际元器件参数的分布情况。

HSPICE仿真课件

2013-11-04

13

输入输出文件

2013-11-04

14

数量级的工程符号

2013-11-04

15

输入文件的例子

2013-11-04

16

输入文件的例子

2013-11-04

17

HSPICE的输入 输入行格式

• 文件名、语句、等式的长度不能超过256字符; • 上标和下标将被忽略; • 对英文字符大小写不敏感 • 用加号(+)表示续行,此时加号应该是新续之行的 第一个非空格字符; • 星号(*)和美圆符号($)可以引出注释行,但*必 须是每行第一个字母,而$一般跟在一个语句后,并 与语句有至少一个空格。

2013-11-04

23

HSPICE的语句 使用子电路

2013-11-04

24

HSPICE的语句 .model引导模型说明语句

• .MODEL 模型名 元器件类型 • 例如:nmos模型 • .model mod1 nmos VTO=1.0 KP=4.5E-5 +LAMBDA=0 GAMMA=0.4 TOX=1.0E-7 +NSUB=4.0E+15 LD=0.06U CJ=2.0E-4 MJ=0.5 +CJSW=2.0E-10 MJSW=0.4 CGSO=1E-10 +CGDO=1E-10 CGBO=2E-9 元器件参数

En

数字集成电路理论与设计

刘 涛

E-mail: ttlyz@

2013-11-04 1

声明

本课件所引用任何素材,包括但不限于文 字图片等,其版权均归原作者所有,这里 不一一列出,一并致谢!

2013-11-04

2

第四章 SPICE与MOS管模型

电子科技大学集成电路实验报告——模拟集成电路

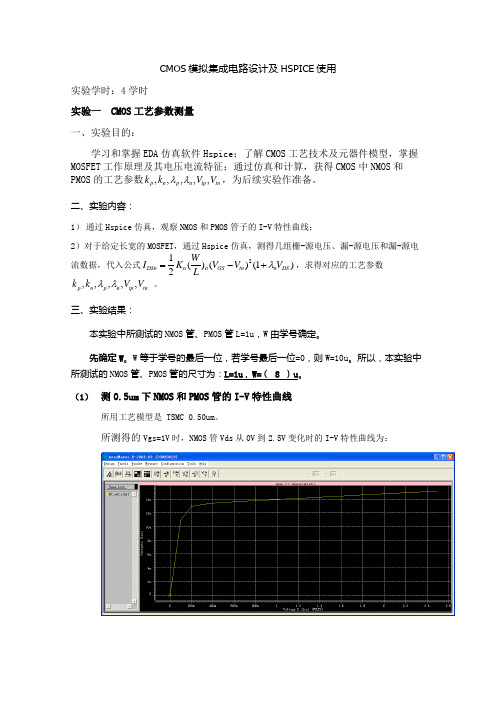

CMOS 模拟集成电路设计及HSPICE 使用实验学时:4学时实验一 CMOS 工艺参数测量 一、实验目的:学习和掌握EDA 仿真软件Hspice ;了解CMOS 工艺技术及元器件模型,掌握MOSFET 工作原理及其电压电流特征;通过仿真和计算,获得CMOS 中NMOS 和PMOS 的工艺参数,,,,,p n p n tp tn k k V V λλ,为后续实验作准备。

二、实验内容:1) 通过Hspice 仿真,观察NMOS 和PMOS 管子的I-V 特性曲线;2)对于给定长宽的MOSFET ,通过Hspice 仿真,测得几组栅-源电压、漏-源电压和漏-源电流数据,代入公式21()()(1)2DSn n n GS tn n DS WI K V V V Lλ=-+,求得对应的工艺参数,,,,,p n p n tp tn k k V V λλ 。

三、实验结果:本实验中所测试的NMOS 管、PMOS 管L=1u ,W 由学号确定。

先确定W 。

W 等于学号的最后一位,若学号最后一位=0,则W=10u 。

所以,本实验中所测试的NMOS 管、PMOS 管的尺寸为:L=1u ,W=( 8 )u 。

(1) 测0.5um 下NMOS 和PMOS 管的I-V 特性曲线所用工艺模型是 TSMC 0.50um 。

所测得的Vgs=1V 时,NMOS 管Vds 从0V 到2.5V 变化时的I-V 特性曲线为:所测得的Vds=1.2V时,NMOS管Vgs从0V到2.5V变化时的I-V特性曲线为:所测得的Vsg=1V时,PMOS管Vsd从0V到2.5V变化时的I-V特性曲线为:所测得的Vsd=1.2V时,PMOS管Vsg从0V到2.5V变化时的I-V特性曲线为:(2)计算TSMC 0.50um工艺库下mos管对应的工艺参数测试NMOS管相关参数,Hspice中仿真用源文件(.sp文件)为:NOMS I-V CharacteristicM1 OUT IN 0 0 CMOSn L=1U W=8UVIN IN 0 1VOUT OUT 0 1.2.OPTIONS LIST NODE POST*.DC VOUT 0 2.5 0.1.DC VIN 0 2.5 0.1*.DC VOUT 0 2.5 0.1 VIN 0.8 1.0 0.2.PRINT DC I(M1).LIB "C:\synopsys\project\tsmc_050um_model.lib" CMOS_MODELS .END所测得的NMOS 管电流曲线为:所测的数据如下表:Ids Vds1V 1.5V Vgs 1V65.4uA 66.5 1.2V14.014.4根据公式21()()(1)2DSn n n GS tn n DS I K V V V Lλ=-+,计算,,n n tn k V λ,分别为: -611910,0.028, 1.37n n tn k V λ≈⨯≈≈测试PMOS 管相关参数,Hspice 中仿真用源文件(.sp 文件)为: POMS I-V CharacteristicM1 OUT IN Vdd Vdd CMOSP L=1U W=8UVIN Vdd IN 1 VOUT Vdd OUT 1.2.OPTIONS LIST NODE POST *.DC VOUT 0 2.5 0.1 .DC VIN 0 2.5 0.1*.DC VOUT 0 2.5 0.1 VIN 0.8 1.0 0.2.PRINT DC I(M2).LIB "C:\synopsys\project\tsmc_050um_model.lib" CMOS_MODELS .END所测得的PMOS 管电流曲线为:所测的数据如下表:Isd Vsd1V 1.5VVsg 1V 1.17 1.181.2V 4.87 5.15计算TSMC 0.50um 工艺中 pmos 参数p p tp ,分别为:-654.8910,0.017,0.927p p tp K V λ≈⨯≈≈综上所述,可得:TSMC 0.50um 工艺参数=n λ0.028=p λ0.017=tn V 0.37V=tp V 0.927V2/119V A K n μ=2/89.54V A K p μ=四、思考题2) 不同工艺,,p n λλ不同。

电子科技大学CMOS模拟集成设计Hspice仿真

以下用实例说明 Hspice 的输入电路程序。 的输入电路程序。

1

NMOS II-V Characteristic 测试电路: 测试电路:

图 1-1 NMOS I-V 特性测试电路 ------------------------------------------------------------------------------------------------------------------

图 1-8 Hspice InstallShield Wizard

2. 选择安装目录。Click“Next”选择 default 目录,如图 1-9 所示。 C:\synopsys\Hspice_A-2008.03-SPI 是 default 的目录。

7

图 1-9 InstallShield Wizard 选择安装目录

饱和状态下 NMOS 电压电流关系公式[1-1]中的参数Kn, VT 和 λn是 CMOS 工艺参数,理想状态下是常数。 针对一具体 CMOS 工艺技术, 通过仿真求取以上工艺参数是模拟电路设计的第 一步。

4. 实验步骤: 实验步骤: 练习一: 练习一: 下载/安装/ 安装/设置 Hspice 仿真软件 步骤一:在本机的桌面建一子目录 2008Hspice。 步骤一 步骤二:从指定的机器和目录中,下载图 1-5 中 23 个压缩文件到本机的子目录 步骤二 2008Hspice 下。 文件 _Hspice.pቤተ መጻሕፍቲ ባይዱrt01 到 _Hspice.part22 是 Hspice 的 setup 文件的压缩, _Hspice.2008-03 是 Hspice 2008 版的 license 文件的压缩。

实验目录

实验一: 实验一:EDA 仿真软件 Hspice 及 CMOS 工艺技术参数 实验二: 实验二:CMOS Differential Amplifier Design 差分放大器设计 实验三: 实验三:CMOS Operational Amplifier Design 运算放大器设计 实验四: 实验四:CMOS AnalogAnalog-toto-Digital Converter 模数转换器( 模数转换器(ADC) ADC)设计

ASIC课程设计——MOS输出级电路设计与Hspice仿真

ASIC课程设计——MOS输出级电路设计与Hspice仿真————————————————————————————————作者:————————————————————————————————日期:目录一.背景介绍 (1)二.设计要求与任务 (2)三.电路原理及设计方法 (2)1.电阻负载共源级放大器电路原理分析 (3)2.有源负载共源放大器设计方法 (5)四.HSpice软件环境概述 (7)1.简介 (7)2.特点 (8)3.界面预览 (8)五.设计过程 (10)六.结果和讨论 (11)七.设计心得 (12)八.库文件程序附录 (13)一.背景介绍ASIC是Application Specific Integrated Circuit的英文缩写,在集成电路界被认为是一种为专门目的而设计的集成电路。

ASIC的设计方法和手段经历了几十年的发展演变,从最初的全手工设计已经发展到现在先进的可以全自动实现的过程。

在集成电路界ASIC被认为是一种为专门目的而设计的集成电路。

是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

ASIC的特点是面向特定用户的需求,ASIC在批量生产时与通用集成电路相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

ASIC分为全定制和半定制。

全定制设计需要设计者完成所有电路的设计,因此需要大量人力物力,灵活性好但开发效率低下。

如果设计较为理想,全定制能够比半定制的ASIC芯片运行速度更快。

半定制使用库里的标准逻辑单元(Standard Cell),设计时可以从标准逻辑单元库中选择SSI(门电路)、MSI(如加法器、比较器等)、数据通路(如ALU、存储器、总线等)、存储器甚至系统级模块(如乘法器、微控制器等)和IP核,这些逻辑单元已经布局完毕,而且设计得较为可靠,设计者可以较方便地完成系统设计。

现代ASIC常包含整个32-bit处理器,类似ROM、RAM、EEPROM、Flash的存储单元和其他模块. 这样的ASIC常被称为SoC(片上系统)。

电子科技大学-集成电路原理实验-CMOS模拟集成电路设计与仿真

实验报告课程名称:集成电路原理实验名称:CMOS模拟集成电路设计与仿真一、实验名称:CMOS模拟集成电路设计与仿真二、实验学时:4三、实验原理1、转换速率(SR):也称压摆率,单位是V/μs。

运放接成闭环条件下,将一个阶跃信号输入到运放的输入端,从运放的输出端测得运放的输出上升速率。

2、开环增益:当放大器中没有加入负反馈电路时的放大增益称为开环增益。

3、增益带宽积:放大器带宽和带宽增益的乘积,即运放增益下降为1时所对应的频率。

4、相位裕度:使得增益降为1时对应的频率点的相位与-180相位的差值。

5、输入共模范围:在差分放大电路中,二个输入端所加的是大小相等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范围。

6、输出电压摆幅:一般指输出电压最大值和最小值的差。

图1两级共源CMOS运放电路图实验所用原理图如图1所示。

图中有多个电流镜结构,M1、M2构成源耦合对,做差分输入;M3、M4构成电流镜做M1、M2的有源负载;M5、M8构成电流镜提供恒流源;M8、M9为偏置电路提供偏置。

M6、M7为二级放大电路,Cc为引入的米勒补偿电容。

其中主要技术指标与电路的电气参数及几何尺寸的关系:转换速率:SR=I5I I第一级增益:I I1=−I I2I II2+I II4=−2I I1I5(I2+I3)第二级增益:I I2=−I I6I II6+I II7=−2I I6I6(I6+I7)单位增益带宽:GB=I I2I I输出级极点:I2=−I I6I I零点:I1=I I6I I正CMR:I II,III=I II−√I5I3−|I Iℎ3|(III)+I Iℎ1,III负CMR:I II,III=√I5I1+III5,饱和+I Iℎ1,III+I II饱和电压:I II,饱和=√2I III功耗:I IIII=(I8+I5+I7)(I II+I II)四、实验目的本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。

电子科技大学-集成电路原理实验-CMOS模拟集成电路设计与仿真

实验报告课程名称:集成电路原理实验名称: CMOS模拟集成电路设计与仿真一、实验名称:CMOS模拟集成电路设计与仿真二、实验学时:4三、实验原理1、转换速率(SR):也称压摆率,单位是V/μs。

运放接成闭环条件下,将一个阶跃信号输入到运放的输入端,从运放的输出端测得运放的输出上升速率。

2、开环增益:当放大器中没有加入负反馈电路时的放大增益称为开环增益。

3、增益带宽积:放大器带宽和带宽增益的乘积,即运放增益下降为1时所对应的频率。

4、相位裕度:使得增益降为1时对应的频率点的相位与-180相位的差值。

5、输入共模范围:在差分放大电路中,二个输入端所加的是大小相等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范围。

6、输出电压摆幅:一般指输出电压最大值和最小值的差。

图1两级共源CMOS运放电路图实验所用原理图如图1所示。

图中有多个电流镜结构,M1、M2构成源耦合对,做差分输入;M3、M4构成电流镜做M1、M2的有源负载;M5、M8构成电流镜提供恒流源;M8、M9为偏置电路提供偏置。

M6、M7为二级放大电路,Cc为引入的米勒补偿电容。

其中主要技术指标与电路的电气参数及几何尺寸的关系:转换速率:第一级增益:第二级增益:单位增益带宽:输出级极点:零点:正CMR:负CMR:饱和电压:功耗:四、实验目的本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。

其目的在于:∙根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。

∙学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。

五、实验内容1、根据设计指标要求,针对CMOS两级共源运放结构,分析计算各器件尺寸。

2、电路的仿真与分析,重点进行直流工作点、交流AC和瞬态Trans分析,能熟练掌握各种分析的参数设置方法与仿真结果的查看方法。

3、电路性能的优化与器件参数调试,要求达到预定的技术指标。

CMOS器件模型

精选课件ppt

5

(a)单线和U-型电阻结构 (b)它们的等效电路

精选课件ppt

• 阻值计算 • 最小宽度

6

栅、漏短接并工作在饱和区的MOS有源电阻

IDS I

I

VGS V VTP

DI

O

S

+

G+

V G-

V-

O

I

S

D

VTN V VGS

IDS

(a)

(b)

栅漏短接的MOS有源电阻及其I-V曲线

Ron VGSV I 2ntooxxW L(VV VTN )2 直流电阻 Ron>交流电阻 rds

+

TARG v(out) val=‘3.3/2'

FALL=1

.meas Tdelay param='(Tr+T精f)选/课2件'ppt

47

Hspice激励介绍(直流电压/电流源)

n1

3.3V

Vdc n1 n2 3.3 n2

20mA

n3 Idc n3 n4 20m

n4

tpw v2

v1 tr td

tf tper

Level 1 Level 2 Level 3 BSIM 1 BSIM 2 BSIM 3 Level=6 Level=50 Level=11

简单MOSFET模型 2m 器件模拟分析 0.9m 器件数字分析 0.8m 器件数字分析 0.3m 器件模拟与数字分析 0.5m 器件模拟分析与0.1m 器件数字分析 亚微米离子注入器件 小尺寸器件模拟电路分析 SOI器件

直流电阻 Ron<交流电阻 rds

精选课件ppt

8

对于理想情况,Oˊ点的交流电阻应为无穷大,实际上因为 沟道长度调制效应,交流电阻为一个有限值,但远大于在该 工作点上的直流电阻。在这个工作区域,当漏源电压变化时, 只要器件仍工作在饱和区,它所表现出来的交流电阻几乎不 变,直流电阻则将随着漏源电压变大而变大。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

饱和区 0 < VGS – VTHn < VDS

I DSn =

且 [1-1]

1 W K n ( ) n (VGS − VT ) 2 (1 + λ nV DS ) 2 L

其中 Kn

是跨导参数,VT 是NMOS阀值电压,W和L是NMOS的宽

和长度,λn是沟道长度调制系数。

3.2.3 模拟电路中 CMOS 工作在饱和状态区 CMOS 工艺中 NMOS 和 PMOS 用于模拟电路设计时必须工作在饱和区。这一现象 由 MOSFET 的小信号模型的线性特征所决定。 gm = ∆ids W ≅ K n ( ) n (VGS − VT ) ∆v gs L

Hspice 的输入电路程序典型格式如下: *标题描述 电 路 主 体 电路描述 (资料叙述) 资料叙述) 分析形态 (控制叙述) 控制叙述) (输出叙述) 输出叙述) .END (结束叙述) (*引导的注解叙述可安插入其内任一行) 引导的注解叙述可安插入其内任一行)

Байду номын сангаас

---------------------------------------------------------------------------------------------------------------------

9

图 1-13 Hspice Installing

6.

Click “OK”以忽略安装中的 Warnings 如图 1-14。

图 1-14 安装中 Warnings

7. 如图 1-15,Click “OK”以确论 license 文件的路径变量设置的要求信 息。HSPICE2008 安装完成后,再设置系统环境变量。

3

从而和源(S) 、漏(D)两端 p 形成 p 沟道。当 D 和 S 之间有压差,PMOS 就会 导通,形成源漏电流 ISDp。

+

3.2.2 NMOS 晶体管 I-V 工作特性 NMOS 晶体管 I-V 工作特性可用其简单的大信号模型来表示。图 1-3 显示 NMOS 晶体管电流电压方向。图 1-4 显示 NMOS 工作区。

8

图 1-11 Window Program 中的名字

5. Click “Next”确定所有 Hspice Setup 选项, 如图 1-12 所示。 如图 1-13 所示,InstallShield Wizard 开始 Hspice 2008 的安装。

图 1-12 列表所有 Hspice Setup 选项

nmos.sp *NMOS I-V Characteristic .OPTIONS LIST NODE POST .LIB "tsmc_025um_model.lib" CMOS_MODELS M1 2 1 0 0 CMOSN L=0.24U W=1u VGS 1 0 0.8 VDS 2 0 1 .DC VGS 0.6 1.8 0.1 .DC VDS 0 2.5 0.1 .PRINT DC I(M1)

10

图 1-15 环境变量修改信息

8. Click 图 1-16 中 “Finish”以完成安装。

图 1-16 Installation Completed

步骤六 步骤六:设置 Hspice2008 的 license 文件路径变量。 1. 从桌面目录 2008Hspice\_Hspice_2008-03\中,复制 hp_2008-03.lic 文件到目录 C:\synopsys\中。 2. 在桌面 desktop 上,在 “我的电脑”或“Computer”上,右击鼠标;选

3. Click “Next”选择“Typical Setup”, 如图 1-10 所示。

图 1-10 InstallShield Wizard 选择 Setup 的类型

4. Click “Next”选择“HSPICE A-2008.03-SPI”作为 Window Program 中 的名字, 如图 1-11 所示。

实验一、 实验一、Hspice 基础及 基础及 CMOS 工艺技术参数

1. 实验目的: 实验目的: 学习和掌握 EDA 仿真软件 Hspice;了解 CMOS 工艺技术及元器件模型,掌握 MOSFET 工作原理及其电压电流特征;通过仿真和计算, 获得 CMOS 中 NMOS 和 PMOS 的工艺参数,为后续实验作准备

图 1-3 NMOS 晶体管电流电压方向

图 1-4 NMOS 工作区

NMOS 有三个工作区, 截止区, 线性区, 和饱和区。 其端点电压及漏源电流 I-V 特性在不同工作区分别如下:

4

截止区 VGS < VT 且 ID = 0 线性区 0 < VDS < VGS – VTHn 且

I DSn = K n ( W ) n [2(VGS − VT ) − V DS ]V DS L

5

图 1-5 Hspice 2008 的压缩文件

步骤三 步骤三:双击文件 _Hspice.part01,解压缩 Hspice Setup 文件到目录 2008Hspice\_Hspice\Hspice\中,如图 1-6 所示。

图 1-6 Hspice Setup 文件

以下用实例说明 Hspice 的输入电路程序。 的输入电路程序。

1

NMOS II-V Characteristic 测试电路: 测试电路:

图 1-1 NMOS I-V 特性测试电路 ------------------------------------------------------------------------------------------------------------------

2.

实验内容: 实验内容: 1) 安装和设置 Hspice 2) 仿真获得 PMOS 和 NMOS 的工艺参数 K p , K n , Vtp , Vtn , λ p , λn 3) 设计反相器使其开关阀值电压为 0.25Vdd, 0.5Vdd,或 0.75Vdd

3. 预备知识: 预备知识: 3.1 Hspice 输入程序结构 输入程序结构

*标题描述

.END ------------------------------------------------------------

2

3.2 NMOS 和 PMOS 的 I-V 工作特性

半导体集成电路设计最常采用的两种工艺是 Bipolar 工艺和 MOS 工艺。近年 来,由于 MOS 工艺可设计出高密度的电路,用户对高密度数字电路(如存储器和 微处理器)的需求推动了 MOS 工艺在数字电路应用中的巨大发展。模拟和数字电 路兼容在同一芯片上又催化 MOS 模拟电路设计的发展。当前,MOS 工艺中 CMOS 工艺占主导地位,许多新的 VLSI 集成电路设计采用 CMOS 工艺。 本实验阐述 CMOS 工艺中元器件 NMOS 和 PMOS 用于模拟电路设计时的 I-V 工 作特性。

步骤四 步骤四:双击文件 _Hspice_2008-03,解压缩 Hspice License 文件到 目录 2008Hspice\_Hspice_2008-03\中,如图 1-7 所示。

6

图 1-7 Hspice License 文件

步骤五 步骤五:安装 Hspice2008 1. 双击目录 2008Hspice\_Hspice\Hspice\中的文件 hspice_vA-2008.03-SPI_Win_Setup, 开始 Hspice2008 的安装 Wizard, 如图 1-8 所示。

,且当此电 在 NMOS 的多晶硅(G)是加一正电位(对轻掺杂的 p- 阱--接地) 压差大于一定电压(Vthn) ,氧化层下的轻掺杂的 p- 阱转化成 n-type,从而和源 (S) 、漏(D)两端 n+ 形成 n 沟道。当 D 和 S 之间有压差,NMOS 就会导通,形 成漏源电流 IDSn。 PMOS 的工作相反,多晶硅(G)是加一负电位(对轻掺杂的 n- 衬底--接 VDD) , 且当此电压差大于一定电压(Vthp) ,氧化层下的轻掺杂的 n- 阱转化成 p-type,

实验目录

实验一: 实验一:EDA 仿真软件 Hspice 及 CMOS 工艺技术参数 实验二: 实验二:CMOS Differential Amplifier Design 差分放大器设计 实验三: 实验三:CMOS Operational Amplifier Design 运算放大器设计 实验四: 实验四:CMOS AnalogAnalog-toto-Digital Converter 模数转换器( 模数转换器(ADC) ADC)设计

CMOS 模拟集成电路设计与 Hspice 仿真

实验教学手册

王明珍 张俊 编 电工学院 电子科技大学

电子信息工程专业建设

CMOS 模拟集成电路设计 与 Hspice 仿真

实验教学手册

王明珍 张俊 编 电工学院 电子科技大学 2011-12

前

言

集成电路设计和应用是多学科交叉高技术密集的学科,是现代电子信息科技 的核心技术,是国家综合实力的重要标志。目前我国对集成电路设计人才需求旺 盛,模拟集成电路设计人才尤其缺乏。 本实验教学手册是面向本科生的 CMOS 模拟集成电路设计的自学软件平台。 通过应用 EDA 仿真软件 Hspice,学生了解和掌握 CMOS 模拟集成电路设计技术及 基本理论。实验手册的目的是使学生了解集成电路设计的 EDA 工具,掌握 CMOS 模拟集成电路设计的基础知识和基本技能,并熟悉其应用领域相关的系统知识。 《CMOS 模拟集成电路设计》 是一门电路基本理论与现代新型元器件相结合且 具有较强的实践性的专业课程。其实验教学可以 1) 使学生巩固所学的电路理论知识,培养学生实践动手能力,解决问题能 力以及创新能力; 2) 使电子信息专业的本科生充分的了解 CMOS 模拟集成电路设计技术及其 相关知识,培养学生学习 CMOS 模拟集成电路设计技术的兴趣和积极性; 3) 激发学生从事集成电路设计和集成系统的研究、开发和应用,以满足我 国集成电路设计领域及相关行业人才需求。 从自学软件平台, 学生可以 download 仿真软件 Hspice 和项目实验学习指导 书。在学生用来学习的计算机上,安装和设置 Hspice,根据实验学习指导书完 成实验内容。 此实验教学手册可作为用作独立的学习指导书,也可作为《CMOS 模拟集成电 路设计》的课程实验手册。对应的参考教材是 P. E. Allen 和 D. R. Holberg 的 《CMOS Analog Circuit Design》 。