闭环锁相环控制框图及分析

锁相ppt

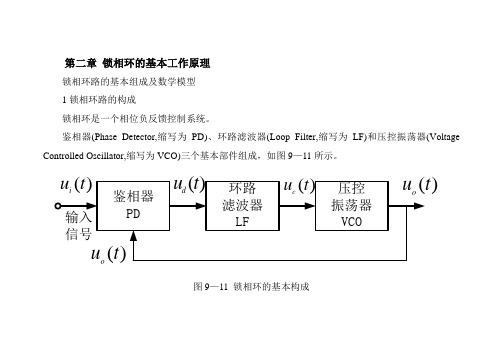

第二章锁相环的基本工作原理锁相环路的基本组成及数学模型1锁相环路的构成锁相环是一个相位负反馈控制系统。

鉴相器(Phase Detector,缩写为PD)、环路滤波器(Loop Filter,缩写为LF)和压控振荡器(Voltage Controlled Oscillator,缩写为VCO)三个基本部件组成,如图9—11所示。

)工作机理:PLL 环路利用输入与输出信号的相位误差()e t θ产生误差电压,通过环路滤波器滤除其中的高频成分与噪声,得到控制电压()c u t 去控制压控振荡器,使()e t θ朝缩小固有频差的方向变化,最终()e t θ稳定在某一很小的常数(称剩余相差),输入、输出信号频率相等i V ωω=,则环路被锁定了,即()e e t θθ∞=。

说明:图9—11为简图,省略了分频器。

PLL 电路中几个重要的频率。

鉴相器的两个输入信号;其一,晶体振荡器提供的参考输入信号 ()sin()i im i i u t V t ωθ=+; 其二,VCO 的输出电压信号。

开环时VCO 的自由振荡频率o ω,其输出电压为 ()cos()o om o o u t V t ωθ=+。

闭环时VCO 的频率受()c u t 控制,瞬时频率从oV ωω→,相应的输出()cos()o om V o u t V t ωθ=+。

为了研究的方便(请看课本P2),通常假设i u 和o u 的初始相位为零,i u 和o u 的相位均以o t ω作为参考,则1()sin[()]sin[()]i im o i o im o u t V t t V t t ωωωωθ=+-=+ (9.4.1)2()cos[()]cos[()]o om o V o om o u t V t t V t t ωωωωθ=+-=+ (9.4.2)式中,1()()i o t t θωω=-,为输入相位。

环路的固有频差 1()o i o d t dt θωωω∆=-=,其值等于输入参考信号频率与VCO 自由振荡频率之差。

锁相环PLL

光耦合器

2.电流传输比 光耦合器的重要参数,通常用直流电流传 输比来表示,当输出电压保持恒定时,它等 于直流输出电流IC与直流输入电流IF的百分 比。有公式 CTR=IC/IF *100%。

光耦合器

六、选用原则

1.光耦合器的电流传输比(CTR)的允许范围为 50%-200%。 这时因为当CTR<50%时,光耦合器中的LED就需 要较大的工作电流(IF>50mA),才能正常控制占 空比,这会增大光耦合器的功耗。如果当 CTR<200%,在启动电路或者当负载发生突变时, 有可能造成误触发,影响正常输出。

其中,1.通用型属于中速光耦合器,其电流传输比 为25%-300%。达林顿型光耦合器的速度较低,其 电流传输比可达到100%-5000%。 2.高速型光耦合器具有速度快、输出线性好等优点。 由光集成电路构成的光耦合器属于高速光耦,电流 传输比较大。

光耦合器

3.光纤型光耦合器能够耐压高,其绝缘电压 值超过100kV。 4.光敏晶闸管型光耦合器属于大功率输出的 光耦典型产品有4N39(内含单向晶闸管), IS607(内含双向晶闸管)。光敏场效应管型 光耦合器的特点是速度快,交、直流两用。

隔离变压器

三、图形符号(见P56 图5-17)

隔离变压器

四、作用

隔离变压器是交流电源转换的一种重要的静止型电 磁感应器件,广泛应用于电器、控制、船舶及测试 等行业。 1.绝缘耐压特性 2.电源滤波作用

隔离变压器

五、应用

图一 常见的晶闸管触发电路

图二 典型的直接耦合式GTO驱动电路

光耦合器

一、概念 光耦合器(Optical Coupler)也称光电耦合 光耦合器 器或隔离器,简称光耦 光耦。 光耦

PLL锁相环详解-经典收藏

PLL的概念我们所说的PLL。

其实就是锁相环路,简称为锁相环。

许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

目前锁相环主要有模拟锁相环,数字锁相环以及有记忆能力(微机控制的)锁相环。

PLL的组成锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

压控振荡器(VCO)的基本概念调节可变电阻或可变电容可以改变波形发生电路的振荡频率,一般是通过人的手来调节的。

而在自动控制等场合往往要求能自动地调节振荡频率。

常见的情况是给出一个控制电压(例如计算机通过接口电路输出的控制电压),要求波形发生电路的振荡频率与控制电压成正比。

这种电路称为压控振荡器,又称为VCO或u-f转换电路。

压控振荡器是锁相环中关键部件,在实际应用中有很多种结构。

压控振荡器(VCO)电路的举例和原理利用集成运放就可以构成精度高、线性好的压控振荡器。

我们知道积分电路输出电压变化的速率与输入电压的大小成正比,如果积分电容充电使输出电压达到一定程度后,设法使它迅速放电,然后输入电压再给它充电,如此周而复始,产生振荡,其振荡频率与输入电压成正比。

即压控振荡器。

4046锁相环

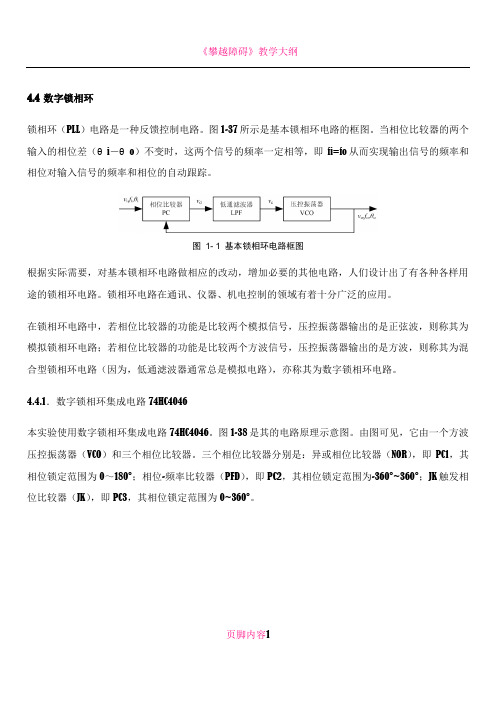

4.4 数字锁相环锁相环(PLL)电路是一种反馈控制电路。

图1-37所示是基本锁相环电路的框图。

当相位比较器的两个输入的相位差(θi-θo)不变时,这两个信号的频率一定相等,即fi=fo从而实现输出信号的频率和相位对输入信号的频率和相位的自动跟踪。

图1- 1 基本锁相环电路框图根据实际需要,对基本锁相环电路做相应的改动,增加必要的其他电路,人们设计出了有各种各样用途的锁相环电路。

锁相环电路在通讯、仪器、机电控制的领域有着十分广泛的应用。

在锁相环电路中,若相位比较器的功能是比较两个模拟信号,压控振荡器输出的是正弦波,则称其为模拟锁相环电路;若相位比较器的功能是比较两个方波信号,压控振荡器输出的是方波,则称其为混合型锁相环电路(因为,低通滤波器通常总是模拟电路),亦称其为数字锁相环电路。

4.4.1.数字锁相环集成电路74HC4046本实验使用数字锁相环集成电路74HC4046。

图1-38是其的电路原理示意图。

由图可见,它由一个方波压控振荡器(VCO)和三个相位比较器。

三个相位比较器分别是:异或相位比较器(NOR),即PC1,其相位锁定范围为0~180°;相位-频率比较器(PFD),即PC2,其相位锁定范围为-360°~360°;JK触发相位比较器(JK),即PC3,其相位锁定范围为0~360°。

页脚内容1页脚内容2图 1- 2 74HC4046的电路原理示意图在使用相位比较器的选择方面,PC1是比较容易锁定的,但要求输入的信号是50%占空比,或者是一个波形较好的小信号正弦波。

如果有条件达到这个要求,尽可能使用PC1。

不对称的大信号如能得到一个比要求输出倍频的基准,用一个触发器分频就可以得到很严格的50%占空比。

如果没有条件得到50%占空比,就要考虑用PC2以得到稳定的锁相。

对照图1-37可知,图1-38所示电路的框图就是图1-37。

其使用的相位比较器是PC2,R3、R4、C2组成低通滤波器,其传递函数K f (s )与K p 、K o /s 、K n 将确定环路的动态特性,R1、C1将确定锁相输出的频带范围,R2、C1将确定输出的频率偏移。

锁相环理论讲解

锁相环的理论锁相环作为一个系统,主要包含三个基本模块:鉴相器(Phase Detector :PD)、低通滤波器(LowPass Filter :LPF),亦即环路滤波器(L00P Filter :LF ),和压控振荡器(V oltage Controlled Oscillator :VCO )。

这三个基本模块组成的锁相环为基本锁相环,亦即线形锁相环(LPLL),如图2.1所示。

图2.1锁相环原理图当锁相环开始工作时,输入参考信号的频率1f 与压控振荡器的固有振荡频率o f 总是不相同的,即1o f f f ∆=-,这一固有频率差1o f f f ∆=-必然引起它们之间的相位差不断变化,并不断跨越2π角。

由于鉴相器特性是以相位差2π为周期的,因此鉴相器输出的误差电压总是在某一范围内摆动。

这个误差电压通过环路滤波器变成控制电压加到压控振荡器上,使压控振荡器的频率o f 趋向于参考信号的频率i f ,直到压控振荡器的频率变化到与输入参考信号的频率相等,并满足一定条件,环路就在这个频率上稳定下来。

两个频率之间的相位差不随时间变化而是一个恒定的常数,这时环路就进入“锁定”状态。

当环路已处于锁定状态时,如果输入参考信号的频率和相位发生变化,通过环路的控制作用,压控振荡器的频率和相位能不断跟踪输入参考信号频率的变化而变化,使环路重新进入锁定状态,这种动态过程称为环路的“跟踪”过程。

而环路不处于锁定和跟踪状态,这个动态过程称为“失锁”过程。

从上述分析可知,鉴相器有两个主要功能:一个是频率牵引,另一个是相位锁定。

实际中使用的锁相环系统还包括放大器、分频器、混频器等模块,但是这些附加的模块不会影响锁相环的基本工作原理,可以忽略。

2.1 锁相环的工作原理锁相环作为一个系统,主要包含三个基本模块:鉴相器【4】、低通滤波器,亦即环路滤波器,和压控振荡器。

在本节首先分析鉴相器、环路滤波器和压控振荡器.2.1.1 鉴相器锁相环中的鉴相器(PD )通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图示:()O U t ()i U t ()D U t图2.2 模拟鉴相器电路 鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:()sin[()]i m i i u t U t ωθ=+ (2.1)()sin[()]o om o o u t U t ωθ=+ (2.2)式中的O ω为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

锁相环基本原理及其应用

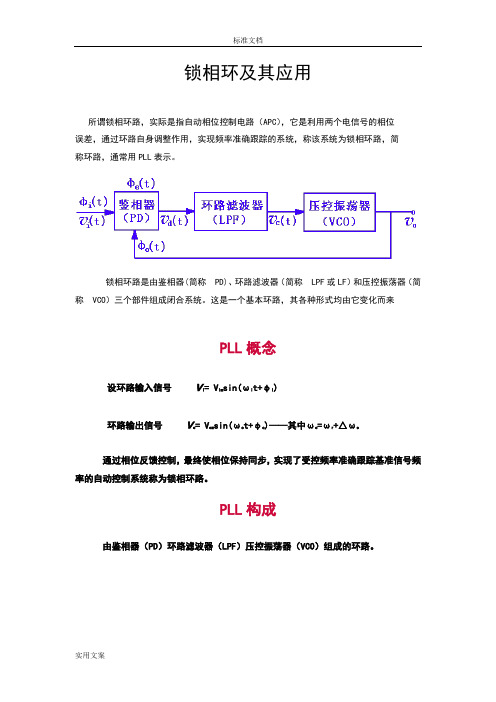

锁相环及其应用所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL表示。

锁相环路是由鉴相器(简称PD)、环路滤波器(简称LPF或LF)和压控振荡器(简称VCO)三个部件组成闭合系统。

这是一个基本环路,其各种形式均由它变化而来PLL概念设环路输入信号v i= V im sin(ωi t+φi)环路输出信号v o= V om sin(ωo t+φo)——其中ωo=ωr+△ωo通过相位反馈控制,最终使相位保持同步,实现了受控频率准确跟踪基准信号频率的自动控制系统称为锁相环路。

PLL构成由鉴相器(PD)环路滤波器(LPF)压控振荡器(VCO)组成的环路。

PLL原理从捕捉过程→锁定A.捕捉过程(是失锁的)a.φi┈φi均是随时间变化的,经相位比较产生误差相位φe=φi-φo,也是变化的。

b.φe(t)由鉴相器产生误差电压v d(t)=f(φe)完成相位误差—电压的变换作用。

v d(t)为交流电压。

c. vd(t)经环路滤波,滤除高频分量和干扰噪声得到纯净控制电压,由VCO产生控制角频差△ω0,使ω0随ωi变化。

B.锁定(即相位稳定)a.一旦锁定φe(t)=φe∞(很小常数)v d(t)= V d(直流电压)b.ω0≡ωi输出频率恒等于输入频率(无角频差,同时控制角频差为最大△ω0max, 即ω0=ωr+△ω0max。

ωr为VCO固有振荡角频率。

)锁相基本组成和基本方程(时域)各基本组成部件鉴相器(PD)数学模式v d(t)=A D sinφe(t)相位模式环路滤波器(LPF)数学模式v c(t)=A F(P)v d(t)相位模式压控振荡器(VCO)数学模式相位模式环路模型相位模式:指锁相环(PLL)输入相位和输出相位的反馈调节关系。

相位模型:把鉴相器,环路滤波器和压控振荡器三个部件的相位模型依次级联起来就构成锁相相位模型。

锁相环路基本工作原理.

锁相环路基本工作原理一、框图与各部分作用·框图·各部分的作用▲ PD——产生误差电压▲LF——产生控制电压▲VCO——产生瞬时输出频率二、环路工作原理1.原理与环路锁定的充分必要条件·原理PLPLL环路在某一因素作用下,利用输入与输出信号的相位差产生误差电压,并滤除其中非线性成分与噪声后的纯净控制信号控制压控振荡器,使朝着缩小固有角频差方向变化,一旦趋向很小常数(称为剩余相位差)时,则锁相环路被锁定了,即·充分必要条件充分2.举例说明 (以一阶锁相环为例)锁定未锁定锁定锁定锁定锁锁定可可见,环路锁定过程中是从0~2π周期的变化,若干周期后使,则环路被锁定。

三、环路相位模式和环路方程1.相位模式①求环路中各部件的数学表示式与数学模式A.鉴相器(PD)乘积型积型叠加型加型其中:若上述经PD输出的误差电压可表示为则数学模型为B.环路滤波器(LF)环C.压控振荡器(VCO)②环路的相位模型2.环路方程及其物理意义①方程②物理意义a)各项的物理意义b)方程的物理意义: 在任何时候环路开环输入固有角频率永远恒等于环路闭环瞬时角频差和环路控制角频差之和。

在锁定过程瞬时角频差逐渐减小,控制角频差逐渐增大,它们之和永远恒等于开环时输入固有角频差。

3.结论①只有环路锁定时,瞬时角频差为0,才实现了了频率准确跟踪。

②环路进入锁定的条件为显然愈大愈小,环路稳定性愈好。

③环路锁定过程是变化的,所以是交变变的电压;一旦锁定为直流电压。

④环路方程是非线性微分方程,其中非线性取决于鉴相器,而微分方程阶数取决于环路滤波器多项式F(P)的阶数。

四、环路滤波器常用的环路滤波器有:1.RC积分滤波器波器电压传输系数为:器,若作为环路滤波器其中中, F(s)为一个极点而无零点的多项式2.无源RC比例积分滤波器电压传输系数为:电压若作为环路滤波器:其中,F(s)为一个极点一个零点的多项式3.有源RC比例积分(或RC 理想积分)滤波器电压传输系数为:其中, ,F(S)为一个极点一个零点的多项式因为极点在原点,所以是理想的积分环节。

锁相环原理及应用

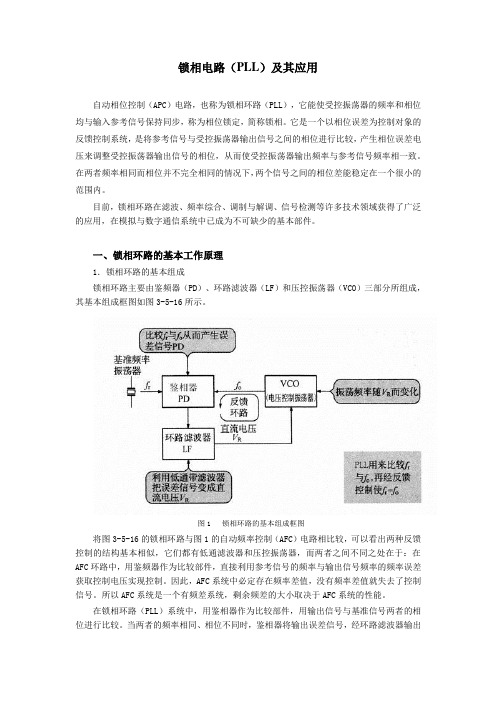

锁相电路(PLL)及其应用自动相位控制(APC)电路,也称为锁相环路(PLL),它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

它是一个以相位误差为控制对象的反馈控制系统,是将参考信号与受控振荡器输出信号之间的相位进行比较,产生相位误差电压来调整受控振荡器输出信号的相位,从而使受控振荡器输出频率与参考信号频率相一致。

在两者频率相同而相位并不完全相同的情况下,两个信号之间的相位差能稳定在一个很小的范围内。

目前,锁相环路在滤波、频率综合、调制与解调、信号检测等许多技术领域获得了广泛的应用,在模拟与数字通信系统中已成为不可缺少的基本部件。

一、锁相环路的基本工作原理1.锁相环路的基本组成锁相环路主要由鉴频器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分所组成,其基本组成框图如图3-5-16所示。

图1 锁相环路的基本组成框图将图3-5-16的锁相环路与图1的自动频率控制(AFC)电路相比较,可以看出两种反馈控制的结构基本相似,它们都有低通滤波器和压控振荡器,而两者之间不同之处在于:在AFC环路中,用鉴频器作为比较部件,直接利用参考信号的频率与输出信号频率的频率误差获取控制电压实现控制。

因此,AFC系统中必定存在频率差值,没有频率差值就失去了控制信号。

所以AFC系统是一个有频差系统,剩余频差的大小取决于AFC系统的性能。

在锁相环路(PLL)系统中,用鉴相器作为比较部件,用输出信号与基准信号两者的相位进行比较。

当两者的频率相同、相位不同时,鉴相器将输出误差信号,经环路滤波器输出控制信号去控制VCO ,使其输出信号的频率与参考信号一致,而相位则相差一个预定值。

因此,锁相环路是一个无频差系统,能使VCO 的频率与基准频率完全相等,但二者间存在恒定相位差(稳态相位差),此稳态相位差经鉴相器转变为直流误差信号,通过低通滤波器去控制VCO ,使0f 与r f 同步。

2.锁相环路的捕捉与跟踪过程当锁相环路刚开始工作时,其起始时一般都处于失锁状态,由于输入到鉴相器的二路信号之间存在着相位差,鉴相器将输出误差电压来改变压控振荡器的振荡频率,使之与基准信号相一致。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

闭环锁相环闭环控制框图推导过程

对于并网发电系统的进网电流品质,相关国际标准做了严格规定和限制,进网电流的频率和相位必须与电网电压同步。

对此,首先要保证的是进网电流参考信号能够精确、快速跟踪电网电压的相位和频率。

若所获取的电网电压相位不准确,则会对并网发电系统的控制造成干扰。

日前电力电子系统中广泛采用的电网相位跟踪方法是利用硬件电路检测电网电压过零点,然后根据基波信号频率来估测并获取电网电压相位。

这种相位获取方式不存在相差自动调节系统,可以称为是“开环’,的,因而无法抑制电网电压的畸变和干扰。

Dian/T 锁相环采用闭环控制系统,其控制框图如图所示,通过该控制可以得到电网的相位角,作为电流相位的给定。

v αv β(2⋅

根据系统控制框图可以得到以下关系:

d grid q grid v =v cos θv =-v sin θ

⎧⋅⎪⎪⎨

⎪⋅⎪⎩ 将电网电压代入上式,φ为电网相位角,可以得到:

grid grid v =V sin φ⋅d grid q grid v =V sin cos θv =-V sin sin θ

φφ⎧⋅⋅⎪⎪⎨⎪⋅⋅⎪⎩ 利用三角函数积化和差公式可以得到:

()()()(22grid d

grid q V v =sin sin V v =cos cos φθφθφθφθ⎧⎪⎪)⎡⎤⋅−++⎪⎣⎦⎪⎪⎨⎪⎪⎡⎤⎪⋅+−−⎣⎦⎪⎪⎩

对进行求偏导,近似认为θ的角速度为工频角速度q v ff ω,可以得到:

()()()()22q grid ff q grid ff dv V d =sin sin d dt dv V d =sin sin d dt

φφθφθωφθφθφθωθ⎧⎪⎪⎡⎤⋅⋅−−+⋅⎪⎣⎦⎪⎪⎨⎪⎪⎡⎤⎪⋅⋅−−−+⎪⎣⎦⎪⎩⋅ 从而得到对时间的微分方程如下:

q v

()(2)2

q

q q grid ff dv dv dv V d d =+=sin dt d dt d dt φθφθωφθ⎡⎤⋅⋅⋅−+⋅⋅⎣⎦ 式中ff 2314.159ff f ωπ==err ωω为工频角速度,。

从而能得到的表达式如下:

()1

2q

err d grid ff

dv v V sin dt ωφθω=

⋅

+=⋅−⋅err ωφerr ωerr ωq v q s v ⋅

作为工频角速度误差进行调节,后面的调节过程与三相以及常用的dq 锁相方法一

致,不做具体分析。

即:当θ超前电网相位时,为负值,经过PI 进行调节减小调节出来的工频角速度,相反,当θ超前电网相位φ时,为正值,经过PI 进行调节增加调节出来的工频角速度,从而得到跟电网一致的工频角速度。

程序中进行了离散,离散与时间常数Ts 相关,Ts=1/fs=1/20000。

上面分析的传递关系中,与时间常数相关的部分为对进行微分部分。

用S 域表示可以写成,其中后项差分可以表示为

1

z s Tz

−=

可以得到

11111q q q s q s q s s z s v v Z v f v f v Z Tz T T −−⎛⎞−⎟⎜⎟⋅=⋅=−⋅=⋅−⋅⋅⎜⎟

⎟⎜⎝⎠

进一步可以得到

()()1111

222s q s q s q q q ff ff ff

f s v f v f v Z v v Z ωωω−−⋅⋅=⋅⋅−⋅⋅=⋅−⋅⋅⋅⋅ 式中的

2s f ff ω⋅为程序中的系数,20000

31.832314.159

s ff f ω==× 程序中进行了加权平均,故对

1

2q ff

s v ω⋅⋅⋅离散写成了如下表达式: 0.4 * v q _k + 0.6 * 31.83 * (v q _k ‐ vq_k ‐1)

式中v q _k 为当前值,vq_k ‐1为上周期的值。