展讯方案PCB layout指导

分享 PCB Layout设计规范

268条PCB Layout设计规范等等1PCB布线与布局PCB布线与布局隔离准则:强弱电流隔离、大小电压隔离,高低频率隔离、输入输出隔离、数字模拟隔离、输入输出隔离,分界标准为相差一个数量级。

隔离方法包括:空间远离、地线隔开。

2PCB布线与布局晶振要尽量靠近IC,且布线要较粗3PCB布线与布局晶振外壳接地4PCB布线与布局时钟布线经连接器输出时,连接器上的插针要在时钟线插针周围布满接地插针5PCB布线与布局让模拟和数字电路分别拥有自己的电源和地线通路,在可能的情况下,应尽量加宽这两部分电路的电源与地线或采用分开的电源层与接地层,以便减小电源与地线回路的阻抗,减小任何可能在电源与地线回路中的干扰电压6PCB布线与布局单独工作的PCB的模拟地和数字地可在系统接地点附近单点汇接,如电源电压一致,模拟和数字电路的电源在电源入口单点汇接,如电源电压不一致,在两电源较近处并一1~2nf的电容,给两电源间的信号返回电流提供通路7PCB布线与布局如果PCB是插在母板上的,则母板的模拟和数字电路的电源和地也要分开,模拟地和数字地在母板的接地处接地,电源在系统接地点附近单点汇接,如电源电压一致,模拟和数字电路的电源在电源入口单点汇接,如电源电压不一致,在两电源较近处并一1~2nf的电容,给两电源间的信号返回电流提供通路8PCB布线与布局当高速、中速和低速数字电路混用时,在印制板上要给它们分配不同的布局区域9PCB布线与布局对低电平模拟电路和数字逻辑电路要尽可能地分离10PCB布线与布局多层印制板设计时电源平面应靠近接地平面,并且安排在接地平面之下。

11PCB布线与布局多层印制板设计时布线层应安排与整块金属平面相邻12PCB布线与布局多层印制板设计时把数字电路和模拟电路分开,有条件时将数字电路和模拟电路安排在不同层内。

如果一定要安排在同层,可采用开沟、加接地线条、分隔等方法补救。

模拟的和数字的地、电源都要分开,不能混用13PCB布线与布局时钟电路和高频电路是主要的干扰和辐射源,一定要单独安排、远离敏感电路14PCB布线与布局注意长线传输过程中的波形畸变15PCB布线与布局减小干扰源和敏感电路的环路面积,最好的办法是使用双绞线和屏蔽线,让信号线与接地线(或载流回路)扭绞在一起,以便使信号与接地线(或载流回路)之间的距离最近16PCB布线与布局增大线间的距离,使得干扰源与受感应的线路之间的互感尽可能地小17PCB布线与布局如有可能,使得干扰源的线路与受感应的线路呈直角(或接近直角)布线,这样可大大降低两线路间的耦合18PCB布线与布局增大线路间的距离是减小电容耦合的最好办法19PCB布线与布局在正式布线之前,首要的一点是将线路分类。

PCBLayout中的走线策略

PCBLayout的常见问题和解决方法

走线策略基础

02

在PCB设计中,走线是指将电路板上的元件引脚或端子连接起来的导线。走线的主要作用是传输信号、电源和接地等,是电路板设计中的重要环节。

走线的定义

走线应尽量短、直,避免走回头路和交叉路,减少信号的传输延迟和信号之间的干扰。同时,走线应考虑到电路板的生产和加工工艺,以及后续维护和检修的方便性。

板材特性

根据PCB板材的介电常数、耐热性、耐腐蚀性等特性,选择合适的走线材料和厚度,以满足电路性能和加工工艺的要求。

加工工艺

考虑PCB板的加工工艺,如钻孔、镀铜、多层板制作等,优化走线策略以避免对加工工艺造成不良影响。

根据PCB板材和加工工艺优化走线策略

元件布局

01

分析电路板上的元件分布、排列和连接方式,优化走线策略以减少信号交叉和干扰,提高电路性能。

PCBLayout中的走线策略

目录

contents

PCBLayout概述走线策略基础走线策略的细化和优化高速电路的走线策略PCBLayout中的电磁兼容性走线策略的实例和应用

PCBLayout概述

01

PCBLayout是将电子线路图转化为实际电路板的过程,包括元件的布局和走线的规划。

PCBLayout是电子设计过程中的关键环节,直接影响到电路板的功能、性能、可维护性和可靠性。

走线的基本原则

走线的定义和基本原则

按照传输信号类型分类

走线可以分为信号线、电源线和地线等。信号线又可以分为高频信号线和低频信号线,高频信号线的走线要求更加严格,需要考虑信号的特性阻抗、传播速度等因素。

按照走线的形状分类

走线可以分为直线、蛇形线、圆形等。直线走线最简单、最短,但可能受到电路板上其他元件的干扰;蛇形线和圆形走线可以增加信号传输的可靠性,但会增加走线的长度和复杂度。

PCB Layout 高阶篇

PCB Layout 高阶篇概述PCB布局(PCB Layout)是电子产品开发过程中的重要环节之一。

合理的PCB布局可以确保电路性能的稳定和可靠。

本文将介绍一些高阶的PCB布局技巧,帮助您设计出更优秀的PCB板。

1. 确定板尺寸和层数在进行PCB布局之前,首先需要确定PCB板的尺寸和层数。

尺寸的选择应该根据具体的项目需求、外部约束条件和组装工艺来确定。

层数的选择主要考虑到电路复杂度和成本因素。

2. 分析电路需求在进行PCB布局之前,需要对电路进行全面的需求分析。

了解电路的信号传输速度、功率需求、EMC要求等特性,以便在布局过程中做出合适的决策。

3. 分区规划将电路划分为不同的功能单元,然后将每个功能单元划分到合适的区域进行布局。

布局时应注意减少信号干扰和电源噪声。

4. 信号完整性在PCB布局中,保持信号完整性是非常重要的。

信号完整性包括信号传输线的匹配阻抗、减小信号回线的长度、降低串扰等。

布局时应注意信号线的走向和布线规则。

5. 电源和地线布局电源和地线的布局对于整个电路的性能和稳定性至关重要。

应尽量减少电源噪声和地线回流路径的长度和阻抗。

布局时应将电源和地线从最近的电容或负载引脚引出,并采用大面积铺铜的方式来进行连接。

6. 热管理对于功耗较大的电路,热管理是非常重要的。

在布局中应合理安排散热元件(如散热片、散热孔),以确保电路在工作时能够稳定运行。

7. 元件布局元件布局应考虑到元件之间的距离、方向和相互之间的影响。

布局时应注意元件之间的电气和机械相互作用,并遵循最佳布局实践。

8. 剖析布局在完成初步布局后,应进行布局剖析,查看布局中存在的问题和潜在的风险。

通过剖析布局,可以及早发现问题并进行修正。

9. PCB层间布局对于多层PCB板,层间布局非常重要。

应尽量将高速信号和低速信号分开布局,避免信号串扰。

布局时应合理安排地面和电源层。

10. 地域布局和特殊要求根据不同地区的法规和认证要求,以及特殊环境(如高温、高湿度)下的工作条件,进行布局时应遵守相应的规定并考虑特殊需求。

pcb layout指导书

pcb layout指导书pcb layout指导书一、概述⑴目的本pcb layout指导书的目的是为了提供一个详细的指南,帮助设计人员进行pcb布局。

⑵背景pcb布局是电路设计的重要环节之一,它涉及到电路板上元件的布置、连线的规划以及电磁兼容性等问题。

合理的pcb布局可以提高电路性能和可靠性。

二、设计准备⑴系统规格在进行pcb布局之前,需要明确系统规格,包括电路功能、性能要求以及信号传输速率等。

⑵系统拓扑根据系统规格,确定电路板的拓扑结构,包括电路板的层数和板型。

⑶元件选型根据系统规格选定合适的元件,并注意元件的尺寸和布局形式。

⑷连接件选型选定合适的连接件,包括电路板与外部接口的连接器、接线端子等。

三、布局规划⑴元件布置根据系统规格和元件尺寸,选择合适的元件布置方式,确保元件之间的间距和连接线长度符合设计要求。

⑵电源和地线布置合理布置电源和地线,确保电路板上各个元件的供电和地线连接畅通。

⑶敏感信号布置敏感信号的布置需要与其他信号相隔一定距离,并采取屏蔽措施,以减少对敏感信号的干扰。

⑷时钟信号布置时钟信号的布置需要考虑时钟传输的稳定性和抗干扰能力。

⑸热管理合理布置散热器、散热孔和风扇等,确保电路板的温度控制在可接受范围内。

四、连线规划⑴信号层定义根据系统规格和布局需求,将电路板划分为不同的信号层,包括功耗层、地层、电源层和信号层等。

⑵信号线宽度和间距根据信号传输速率和电流要求,确定信号线的宽度和层间间距。

⑶信号线走向根据电路功能和信号传输路径,规划信号线的走向,尽量缩短信号线长度。

⑷差分信号布局差分信号需要保持相等长度,并与其他信号相隔一定距离,以减少互相之间的干扰。

五、电磁兼容性措施⑴地线分割根据电路板的信号层划分和布局需求,采取地线分割策略,减少地线回路的面积。

⑵绕线方式对于高频信号和敏感信号,采用绕线方式减少辐射和串扰。

六、文档附件本指导书相关附件包括:附件1:系统规格说明书附件2:pcb布局图附件3:连线规划图七、法律名词及注释⒈电路板:也称印刷线路板(Printed Circuit Board,PCB),是用于连接和支持电子元件的载体。

Layout(集成电路版图)注意事项及技巧总结

Layout主要工作注意事项●画之前的准备工作●与电路设计者的沟通●Layout 的金属线尤其是电源线、地线●保护环●衬底噪声●管子的匹配精度一、l ayout 之前的准备工作1、先估算芯片面积先分别计算各个电路模块的面积,然后再加上模块之间走线以及端口引出等的面积,即得到芯片总的面积。

2、Top-Down 设计流程先根据电路规模对版图进行整体布局,整体布局包括:主要单元的大小形状以及位置安排;电源和地线的布局;输入输出引脚的放置等;统计整个芯片的引脚个数,包括测试点也要确定好,严格确定每个模块的引脚属性,位置。

3、模块的方向应该与信号的流向一致每个模块一定按照确定好的引脚位置引出之间的连线4、保证主信号通道简单流畅,连线尽量短,少拐弯等。

5、不同模块的电源,地线分开,以防干扰,电源线的寄生电阻尽可能较小,避免各模块的电源电压不一致。

6、尽可能把电容电阻和大管子放在侧旁,利于提高电路的抗干扰能力。

二、与电路设计者的沟通搞清楚电路的结构和工作原理明确电路设计中对版图有特殊要求的地方包含内容:(1)确保金属线的宽度和引线孔的数目能够满足要求(各通路在典型情况和最坏情况的大小)尤其是电源线盒地线。

(2)差分对管,有源负载,电流镜,电容阵列等要求匹配良好的子模块。

(3)电路中MOS管,电阻电容对精度的要求。

(4)易受干扰的电压传输线,高频信号传输线。

三、layout 的金属线尤其是电源线,地线1、根据电路在最坏情况下的电流值来确定金属线的宽度以及接触孔的排列方式和数目,以避免电迁移。

电迁移效应:是指当传输电流过大时,电子碰撞金属原子,导致原子移位而使金属断线。

在接触孔周围,电流比较集中,电迁移更容易产生。

2、避免天线效应长金属(面积较大的金属)在刻蚀的时候,会吸引大量的电荷,这时如果该金属与管子栅相连,可能会在栅极形成高压,影响栅养化层质量,降低电路的可靠性和寿命。

解决方案:(1)插一个金属跳线来消除(在低层金属上的天线效应可以通过在顶层金属层插入短的跳线来消除)。

PCB Layout指南

1. 一般規則1.1 PCB板上預劃分數位、類比、DAA信號佈線區域。

1.2 數位、類比元器件及相應走線儘量分開並放置於各自的佈線區域內。

1.3 高速數位信號走線儘量短。

1.4 敏感類比信號走線儘量短。

1.5 合理分配電源和地。

1.6 DGND、AGND、實地分開。

1.7 電源及臨界信號走線使用寬線。

1.8 數位電路放置於平行匯流排/串列DTE介面附近,DAA電路放置於電話線介面附近。

2. 元器件放置2.1 在系統電路原理圖中:a) 劃分數位、類比、DAA電路及其相關電路;b) 在各個電路中劃分數位、類比、混合數位/類比元器件;c) 注意各IC晶片電源和信號引腳的定位。

2.2 初步劃分數位、類比、DAA電路在PCB板上的佈線區域(一般比例2/1/1),數位、類比元器件及其相應走線儘量遠離並限定在各自的佈線區域內。

Note:當DAA電路占較大比重時,會有較多控制/狀態信號走線穿越其佈線區域,可根據當地規則限定做調整,如元器件間距、高壓抑制、電流限制等。

2.3 初步劃分完畢後,從Connector和Jack開始放置元器件:a) Connector和Jack周圍留出外掛程式的位置;b) 元器件周圍留出電源和地走線的空間;c) Socket周圍留出相應外掛程式的位置。

2.4 首先放置混合型元器件(如Modem器件、A/D、D/A轉換晶片等):a) 確定元器件放置方向,儘量使數位信號及類比信號引腳朝向各自佈線區域;b) 將元器件放置在數位和類比信號佈線區域的交界處。

2.5 放置所有的模擬器件:a) 放置類比電路元器件,包括DAA電路;b) 模擬器件相互靠近且放置在PCB上包含TXA1、TXA2、RIN、VC、VREF信號走線的一面;c) TXA1、TXA2、RIN、VC、VREF信號走線周圍避免放置高雜訊元器件;d) 對於串列DTE模組,DTE EIA/TIA-232-E系列介面信號的接收/驅動器儘量靠近Connector並遠離高頻時鐘信號走線,以減少/避免每條線上增加的雜訊抑制器件,如阻流圈和電容等。

谈谈平板电脑类产品PCB设计的流程及Layout设计注意事项

谈谈平板电脑类产品PCB设计的流程及Layout设计注意事项写在之前

此系列文章以联发科MTK主控为例,谈谈平板电脑类产品PCB设计的流程及Layout设计注意事项;希望对刚接触Layout设计的朋友起到小小的辅助作用,以及和同行相互交流、相互提高的目的。

▼导入结构图▼

基本要素说明:

1、CPU Pitch:0.4mm;

2、设计平台:Cadence Allegro16.6

3、产品案例:平板电脑类产品

1、新建好PCB文件后,接下来需要导入结构工程师提供的结构图文件,一般为dxf格式,用于作PCB的Outline(板框);

2、菜单File-Import-DXF,如下图:

界面Ⅰ

3、界面如下,需要设置正确的单位及Subclass:

界面Ⅱ

说明:

1、一般DXF文件名不要有中文字符;

2、格式单位(DXF units)一栏一般选择“MM”;结构工程师用公制单位居多;

3、导入DXF file后,Layer conversion file栏会自动填上相关信息;

4、单击“Edit/View layers”选项,界面如下:

界面Ⅲ

说明:。

Layout讲解

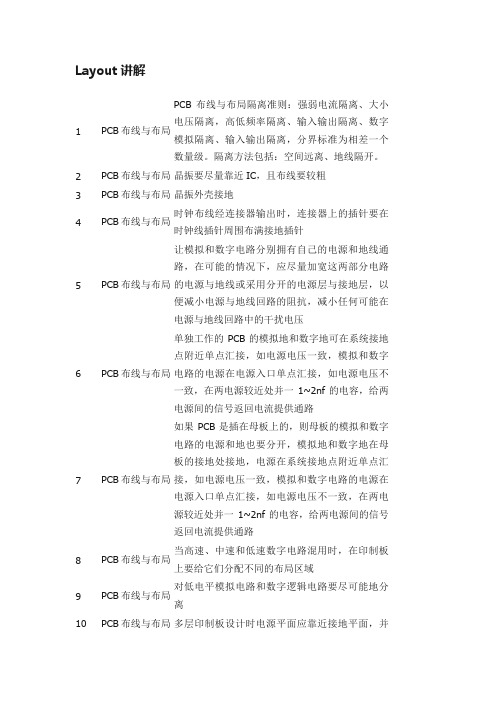

Layout讲解1PCB布线与布局PCB布线与布局隔离准则:强弱电流隔离、大小电压隔离,高低频率隔离、输入输出隔离、数字模拟隔离、输入输出隔离,分界标准为相差一个数量级。

隔离方法包括:空间远离、地线隔开。

2PCB布线与布局晶振要尽量靠近IC,且布线要较粗3PCB布线与布局晶振外壳接地4PCB布线与布局时钟布线经连接器输出时,连接器上的插针要在时钟线插针周围布满接地插针5PCB布线与布局让模拟和数字电路分别拥有自己的电源和地线通路,在可能的情况下,应尽量加宽这两部分电路的电源与地线或采用分开的电源层与接地层,以便减小电源与地线回路的阻抗,减小任何可能在电源与地线回路中的干扰电压6PCB布线与布局单独工作的PCB的模拟地和数字地可在系统接地点附近单点汇接,如电源电压一致,模拟和数字电路的电源在电源入口单点汇接,如电源电压不一致,在两电源较近处并一1~2nf的电容,给两电源间的信号返回电流提供通路7PCB布线与布局如果PCB是插在母板上的,则母板的模拟和数字电路的电源和地也要分开,模拟地和数字地在母板的接地处接地,电源在系统接地点附近单点汇接,如电源电压一致,模拟和数字电路的电源在电源入口单点汇接,如电源电压不一致,在两电源较近处并一1~2nf的电容,给两电源间的信号返回电流提供通路8PCB布线与布局当高速、中速和低速数字电路混用时,在印制板上要给它们分配不同的布局区域9PCB布线与布局对低电平模拟电路和数字逻辑电路要尽可能地分离10PCB布线与布局多层印制板设计时电源平面应靠近接地平面,并且安排在接地平面之下。

11PCB布线与布局多层印制板设计时布线层应安排与整块金属平面相邻12PCB布线与布局多层印制板设计时把数字电路和模拟电路分开,有条件时将数字电路和模拟电路安排在不同层内。

如果一定要安排在同层,可采用开沟、加接地线条、分隔等方法补救。

模拟的和数字的地、电源都要分开,不能混用13PCB布线与布局时钟电路和高频电路是主要的干扰和辐射源,一定要单独安排、远离敏感电路14PCB布线与布局注意长线传输过程中的波形畸变15PCB布线与布局减小干扰源和敏感电路的环路面积,最好的办法是使用双绞线和屏蔽线,让信号线与接地线(或载流回路)扭绞在一起,以便使信号与接地线(或载流回路)之间的距离最近16PCB布线与布局增大线间的距离,使得干扰源与受感应的线路之间的互感尽可能地小17PCB布线与布局如有可能,使得干扰源的线路与受感应的线路呈直角(或接近直角)布线,这样可大大降低两线路间的耦合18PCB布线与布局增大线路间的距离是减小电容耦合的最好办法19PCB布线与布局在正式布线之前,首要的一点是将线路分类。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2010年1月20日

Proprietary and Confidential Information

4

PCB STACK

一个典型的8层板结构(H=1mm)

File Name sm001.pho art001.pho Description Top Solder M ask Plating Layer1 Dielectric Plating Layer2 Dielectric Layer3 Dielectric CORE Layer4 Dielectric Layer5 Dielectric CORE Layer6 Dielectric Layer7 Plating Dielectric Layer8 Plating Bottom Solder M ask Total M aterial Resist Ink Cu 0.075/Cu RCC Copper 0.075/Cu RCC Resin Cu 1/2OZ Cu FR-4 1/2OZ Cu FR-4 1/2OZ Cu FR-4 1/2OZ Cu FR-4 1/2OZ Cu FR-4 1/2OZ Cu Cu 0.075/Cu RCC Resin 0.075/Cu RCC Copper Cu Resist Ink Thickness 15 22 12 65 20 17 130 17 100 17 185 17 100 17 130 17 20 65 12 22 15 1015 Er

14

Layout: VBAT处理

星型走线:不同的分支到PA ,到BBchip ,到Audio PA 等; 根据流经的电流大小来控制 不同分支的宽度和打孔数量 ; VBAT线需要避开其他线,特 别是audio线; BB内部的LDO分别给RF, digital, analogy供电;相应 的VBAT也要用不同分支来供 电;

2010年1月20日

Proprietary and Confidential Information

6

PCB STACK: Impedance Control

RF 阻抗控制

Reference Ground Layer1 Layer5 Layer4 Layer4 & Layer6 Type Microstrip Stripline Width 21mil 4mil Characteristic Impedance 50Ω 50Ω Tolerance +/-5Ω +/-5Ω

Placement 原则: 器件集中/隔离 原则 保持不同部分 信号的回路的 通畅和相对独 立

Bat

2010年1月20日

t e Proprietary and Confidential Information r

8

Placement:规则

1 RF部分: 布局保证RF走线尽量短,而且不要有交叉;大功率线(PA输出和从开关到 天线的连线)优先级更高; 2 总线考虑 flash(MCP)同BB,以及其他总线设备的相对位置尽量按推荐的,保证BB 到flash(MCP)的走线最顺畅; 3 电源(LDO)考虑 电源和LDO输出线上的电容尽量靠近相应的管腿; 4 EMI/ESD FPC的EMI尽量靠近connector; ESD器件要就近摆放 5 BB 周围器件(特别是模拟部分)要严格按照参考设计

2010年1月20日

Proprietary and Confidential Information

10

Layout:原则

Layout 基本原则: 同样性质的线尽量压缩; 不同性质的线之间尽量用GND+VIA隔开; 保证信号回路的相对独立; 保证地的完整性,每个GND PIN需要可靠连接到主GND平面(L4); 敏感线的包GND和隔离处理; EMI/ESD考虑;

art008.pho sm008.pho

Note: 1OZ=1.4mil=35μm

2010年1月20日

Proprietary and Confidential Information

5

PCB STACK:规则

走线WIDTH/SPACE 为4mil/4mil Copper与Trace、Via、Pad、Board Line等的距离应大于8mil以上 同一NET上的两个VIA的距离为0,不允许出现外环重叠的情况,最 坏情况为边缘相切。 过 孔 的 类 型 有 1-2 、 2-7 、 7-8 、 1-8 四 种 , 其 中 1-2 、 7-8 的 标 准 为 12/4mil , 2-7 的 为 19/8mil , 1-8 的 VIA 根 据 需 要 确 定 , 一 般 为 20/10mil,根据板厂的能力设置。

PCB Layout Guide

Created by : Cowin Wei

目录 Spreadtrum solution的特点 PCB STACK Placement Layout

2010年1月20日

Proprietary and Confidential Information

2

Spreadtrum solution

布线规划

L1: Component; L2/L3/: trace; L4: GND; L5: RF/Audio trace; L6: power; L7: keypad trace; L8: Keypad;

2010年1月20日

Proprietary and Confidential Information

7

PLACEMENT

一个典型Placement: RF 同BB相对隔 开; Digital同analogy隔 开 Audio同RF/ Digital 隔开 PA电流通路 电源布局 相同性质/电路相关 部分相对集中

Antenn a PA

tranc audio e i v e Fla r BB s h Analogy BB

2010年1月20日

Proprietary and Confidential Information

11

Layout:RF Part

可靠的接地,PA电流可靠的回 流路径; 充足的GND VIA,特别是PA和 switchplexer下面; 注意阻抗控制线,铺GND时用 12mil clearance; 避免PA的输入和输出之间,开 关的输入和输出之间的耦合; Transceiver下面在表层不要有 线; 为减小寄生电容,挖GND处理 :天线的PAD下面全部挖空,表 层RF线和PAD下面,以L4为参 考GND; Vramp/AFC/IQ线/clk线避免被 其他信号干扰或干扰别人;

3.3±0.2 @1GHz

art002.pho art003.pho art004.pho art005.pho art006.pho art007.pho

4.1±0.3 @1GHz 4.2±0.2 @1GHz 4.3±0.3 @1GHz 4.2±0.2 @1GHz 4.1±0.3 @1GHz

3.3±0.2 @1GHz

2010年1月20日

Proprietary and Confidential Information

12

Layout: BB处理

模拟部分外围走线要紧凑,避免交叉和干扰(特别注意VRBG, AVDDAUX,AVDDBB,AVDDVB,AVDDVBO); 保证模拟部分有一个相对干净的GND(L3);不同模拟GND要单点接地处理; 避免数字部分的线对模拟的干扰;

2010年1月20日

Proprietary and Confidential Information

9

Placement:更多的详细规则

元器件与元器件外框边缘的距离大于10mil,一般最少为12mil,元器件距板 边的距离至少12mil以上,结构定位器件除外 芯 片 电 源 的 滤 波 电 容 必 须 放 在 芯 片 PIN 旁 边 , 比 如 AVDDVBO 、 AVDDVB 、 AVDDBB 、 AVDDAUX 、 AVDD36 、 VBAT 、 VDRAM 、 VDDIO、VMEM、DVDD3V、VDD、VLCD等等。 RF部分的器件摆放请参考提供的参考设计。尤其注意滤波器、开关、隔离 器等器件的位置。将收发电路功能块电路分开,并采用屏蔽盖屏蔽。 晶振必须放在离芯片最近的地方,但不要放在靠近板边的地方,包括 13M、32.768K。 基带处理芯片及外部MEMORY尽量靠近,并采用屏蔽盖屏蔽。 屏蔽盖的焊接线的宽度视屏蔽盖厚度而定,但至少25mil,元器件距离屏蔽 盖的焊接线距离至少12mil,同时要考虑器件的高度是否超出屏蔽盖。 升压电路,音频电路、FPC远离天线 充电电路远离RF、Audio以及其它敏感电路。 AUDIO部分滤波电路的输入输出级应该相互隔离,不能有耦合

1 4 7 *

2 5 8 0

3 6 9 #

GEA

Keypad Timer PWM DAI A/D D/A System Timing VDDPLL AVDD VDDCORE VDDIO Power/ Charger Management

MICP MICN AUXMICP AUXMICN EARP EARN AUXSPP AUXSPN SSCLK SSDR SSDX SSRST SSMD0 SSMD1 VBAT Vdrv LDO1 LDO2 Charge

MCP

Ext. Mem Interface

RF Part

RAM UART 0 Interrupt Control UART 1 DMA UART 2 SI

TX/RX IP TX/RX IN TX/RX QP TX/RX QN

Channel Codec

Viterbi Equalizer Voice Band Codec

Test/Debug Interface ARM7TDMI Ext. Mem Interface MTDO MTDI MTCK MTMS MTRST_N EMA [24:0] EMD [15:0] EMBL_N EMBH_N EMOE_N EMWE_N EMCS_N [7:0] RST_N PBINT XTLEN Prog RAM JTAG X/Y RAM P-Port X-Port and Y-Port TeakLite Z-Port X ROM Clock & PLL System Control Shared RAM RF Control SIMCLK SIMDA SIMPE SIMRST SIM card U0TXD U0RXD U0DTRN U0RTSN U0DSRN U0CTSN U1TXD U1RXD Download & Tuning U2TXD U2RXD SDA SCL KEYOUT [5:0] KEYIN [4:0] PWMA PWMB ADCI [4:0] DAC 32k crystal CLK32I CLK32O SIM Interface ROM Interrupt Control PA Control Encryption Enagine Baseband Codec MCLKI AFCOUT RFSDA RFSCK RFSEN RFCTL [15:0] PAGSM Prog ROM