全国大学生电子设计竞赛

第十五届全国大学生电子设计大赛报名开始

第十五届全国大学生电子设计大赛报名开始这是一个令全国大学生翘首以待的消息,第十五届全国大学生电子设计大赛正式开始报名啦!作为国内最具影响力和知名度的电子设计比赛之一,本届大赛旨在鼓励和推动大学生在电子科学与技术领域的创新与实践,为培养高素质的电子工程人才做出巨大贡献。

本文将为大家介绍此次比赛的具体信息、报名要求和参赛流程。

一、比赛概述第十五届全国大学生电子设计大赛是由中国电子学会主办的一项全国性大学生科学技术竞赛。

自2005年首次举办以来,已经成功举办了14届,广受大学生和电子行业的喜爱和认可。

大赛面向全国普通本科院校在校大学生,旨在激发学生对电子科学与技术的兴趣,培养他们的实践创新能力和团队协作精神。

二、报名要求1.参赛资格比赛面向全国普通本科院校在校大学生,不限专业和年级。

学生可自愿组队参赛,每队成员不超过5人。

同一学校可以有多支参赛队伍。

2.报名时间本次比赛的报名时间为XX年XX月XX日至XX年XX月XX 日。

逾期将不再接受报名申请。

3.报名方式参赛队伍需登录大赛官方网站进行在线报名,填写相关信息并上传报名材料。

三、参赛流程1.报名阶段参赛队伍需按照要求在规定时间内完成在线报名,并上传相关材料,包括队伍介绍、指导教师信息和项目简介等。

2.初赛阶段初赛采用电子资料提交的方式,参赛队伍需提交一份完整的设计报告和演示视频。

评审专家将根据设计报告和演示视频的内容对作品进行评审和筛选,选拔出进入决赛的优秀作品。

3.决赛阶段决赛采用现场演示和答辩的形式,参赛队伍需准备完整的作品和展示材料,并在比赛现场进行展示和答辩。

评委将综合考察作品的设计创新性、技术难度、实用性和团队合作能力等方面进行评分,最终评选出一、二、三等奖和优秀组织奖、优秀创新奖等。

四、比赛收益1.学术交流参赛队伍将有机会与来自全国各地的电子科技爱好者进行面对面的交流和学术研讨,共同分享电子设计领域的最新研究成果和技术进展。

2.奖项荣誉获奖队伍将获得来自中国电子学会颁发的荣誉证书和奖金,并有机会参加国内外的科技创新交流活动,提升个人和团队的知名度和竞争力。

全国大学生电子设计竞赛报告要求及格式

全国大学生电子设计竞赛设计报告要求及格式设计报告内容:一、封面:单独1页见样件二、摘要:中文200~300字,单独1页三、设计报告正文:1 前言:简述本设计要解决的主要问题或要达到的目标即设计题目给定的设计要求的主要内容,对应采用的实现方法及手段这点与摘要相似;一般这部分不宜太长,300字左右;2 系统方案设计:包括方案比较、方案论证、方案选择;以方框图的形式给出各方案,至少针对2个及以上方案进行;方案比较、论证要充分,方案选择要合理、正确;3 理论分析与计算根据设计要求达到的性能指标及实现的功能,必须进行理论分析及必要的计算,说明如何保证;4 系统电路设计:①说明各单元模块的功能,同时进行电路设计要有对应的单元电路图;②电路参数的计算及元器件的选择;③特殊器件的简介;④各单元模块的联接即接口问题;5 系统软件设计:①说明软件设计原理及设计所用工具;②画出软件设计结构图、说明其功能;③画出主要软件设计流程框图;6 系统测试:包括系统指标参数及功能的测试,说明测试方法与测试内容;1列出主要的测试仪器、仪表;2系统测试:①说明测试方法;②要求有完整的测试参数记录表及测试数据;③系统功能测试:测试或说明系统能实现的功能;3测试结果分析:对测试的系统指标参数及实现的功能分析与设计要求对比进行,指出指标参数及实现的功能的整体完成情况,重点分析指标及功能达不到要求的原因或功能、指标较优是如何实现的;7 结束语结论:②对设计制作进行小结,总结得失及收获体会;②对设计制作的不理想及不完善处提出进一步改进的设想;四、附录:①相关设计图必须包含一张系统总图;②相关设计程序主程序、部分子程序;设计报告格式:设计报告统一用A4纸打印,设计报告正文大标题用小三号宋体、小标题用四号宋体、内容用小四号宋体,报告正文为单倍行距;报告从正文开始统一编页码,报告每页上方必须留出3cm空白,空白内不得有任何文字,以便顶端密封装订;设计报告要求6页;特别注意:设计报告封面及内容中不能出现参赛队的任何信息包括学校名称、学生姓名等,否则,视为违规。

全国大学生电子设计大赛应该怎么准备

全国大学生电子设计大赛应该怎么准备?全国大学生电子设计大赛是高校“四大赛”之一,每两年一次(逢单数年举办),竞赛大约于九月初举办,历时四天三晚。

大赛参赛者主要是高校本科学生(也有一部分高职学生),三人组成一组(大赛以组为参赛的基本单位)。

竞赛期间参赛者与外界相对隔离,但可查阅资料、可使用PC上网(不得与非组成员交流)。

大赛分理论和实践两部分,其中前者占50分,后者占100分。

实际部分包括从问题出发设计电路到制成产品并撰写相关论文报告整个过程,时限为四天三晚。

竞赛场地一般由高校提供。

知识要求:竞赛对参赛者最基础的知识要求包括:电路、模拟电子技术、数字电子技术、微机原理与接口技术、C语言编程(面向硬件)。

当然,仅仅由这些知识支撑还是不够的,竞赛还需要参赛者有较扎实的专业背景知识。

下面分类列出:信息通讯:高频电子技术、数字信号原理、通讯原理、信号与系统。

电子仪器:电子测量技术、电子仪器技术、虚拟仪器技术。

机电控制:传感器与检测、自动控制原理、计算机控制、控制电机。

电力电子:变流技术、电力电子技术。

以上并不是都需要掌握,而是根据自己的专业或兴趣,选择性地“精通”一到两项。

对于自动化专业的同学来说,主要适合于后两项。

基本技能要求:竞赛十分重视参赛者的动手能力,故对技能的要求是非常实在的东西,并非空谈。

主要技能有:1、资料收集整理的能力。

由于竞赛期间可以查阅资料,故赛前对资料的收集整理十分重要,甚至关键。

2、自学能力。

竞赛题目大多都包含一些新知识新思想,平时一般都未接触过,甚至指导老师也不一定听说过。

所以在短时间内自学新知识并转化到实践中去的能力必不可少。

3、英语资料阅读能力。

由于竞赛的前沿性及技术的全球性,决定了我们不可避免地需要查阅英文资料,故此能力非常重要。

4、文档组织与撰写能力。

竞赛包括撰写论文报告这一环节,且时间很紧,故这一能力也应具备。

5、PCB制版能力。

设计好的电路怎样制版?怎样制版才能方便组装焊接,且减少相互干扰?采用怎样的工艺才能提高电路的精度等等问题都是最终成败的关键,而这就基于PCB制版能力。

全国大学生电子设计竞赛简介

2005年全国大学生电子设计竞赛

全国共有525所高等学校、4662个代表队的

13986名同学参赛

评出了全国一等奖173个队,全国二等奖264

个队

2005年全国大学生电子设计竞赛

全国一等奖获奖队数量173个, 北京12名,上海5名,天津4名,重庆7名,

湖北28名,河北5名,河南6名,江苏22名 (含SONY杯3名队员),四川14名,辽宁9 名,浙江9名,吉林3名,福建1名,山东8名, 黑龙江4名,广东8名,广西3名,湖南8名, 山西2名,江西3名,安徽1名,陕西15名, 甘肃1名,新疆1名。

评奖工作

各赛区组委会聘请专家组成赛区评委会,

评选本赛区的一、二等奖,获奖比例一 般不超过总参赛队数的三分之一。此外, 对参赛成功者,赛区可酌情颁发“成功 参赛证书”。 按教育部、信息产业部的指示精神,全 国一、二等奖颁发全国统一的获奖证书, 竞赛成绩记入学生档案,对成绩优秀的 参赛学生,各校根据实际情况在评选优 秀学生、奖学金及推荐免试研究生时予 以适当考虑。

团队精神的培养

电子设计竞赛要求三人组队参赛,集体计算成绩,这就 使得三个人必须互相信任、互相配合、分工合作。在顺境时 要相互提醒保持冷静,逆境时要相互鼓励共度难关,出现问 题时不能相互埋怨,这与课堂教学强调独立性是有明显区别 的。在实际的工作中,一般都要与人合作,需要团队精神, 而这一点在常规的教学得到的锻炼是有限的。

内容全开放: 学生自定课题、自拟方案、独立自 主的完成课题的设计、组装与调试。

本次招生计划

经过训练,参加2007年9月的第八届全国

大学生电子设计竞赛。

科技学院十二人(三年级)

三峡大学2005年全国大学生电子设计竞赛教练员名单

2023年全国大学生电子设计竞赛作品

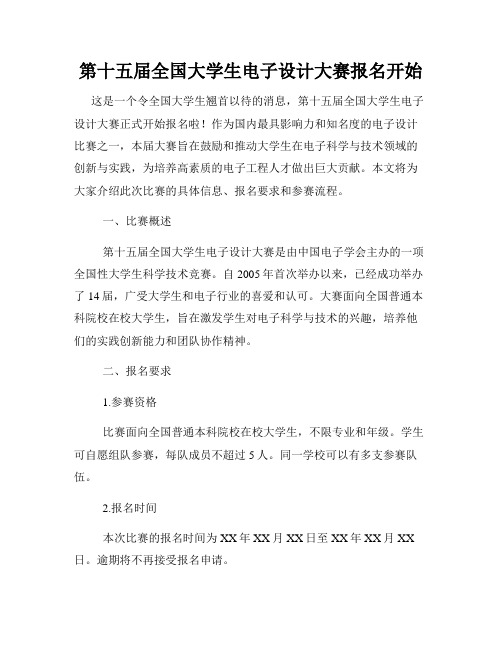

本系统电路连接及硬件资源分派见图4.1所示。

采用AT89S51单片机作为核心器件, 多圈电位器为悬挂物体位置采集器件, 通过ADC0832转换位数字信号送入单片机解决, L298作为直流电机的驱动模块, 以MAX7219驱动的LED显示和4×4键盘作为人机接口。

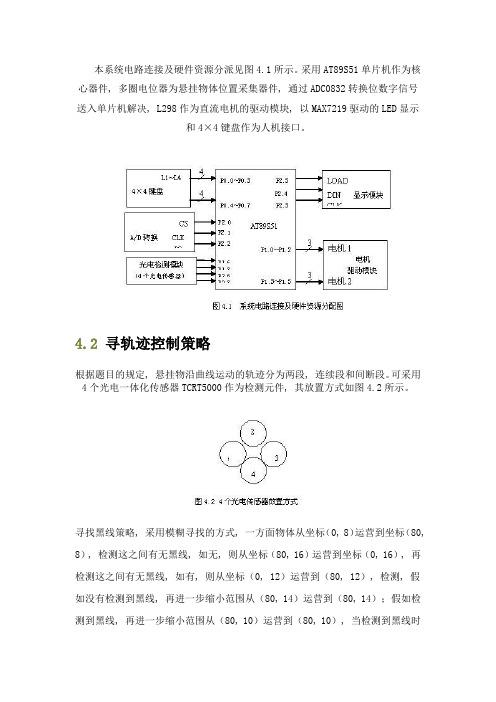

4.2 寻轨迹控制策略根据题目的规定, 悬挂物沿曲线运动的轨迹分为两段, 连续段和间断段。

可采用4个光电一体化传感器TCRT5000作为检测元件, 其放置方式如图4.2所示。

寻找黑线策略, 采用模糊寻找的方式, 一方面物体从坐标(0, 8)运营到坐标(80, 8), 检测这之间有无黑线, 如无, 则从坐标(80, 16)运营到坐标(0, 16), 再检测这之间有无黑线, 如有, 则从坐标(0, 12)运营到(80, 12), 检测, 假如没有检测到黑线, 再进一步缩小范围从(80, 14)运营到(80, 14);假如检测到黑线, 再进一步缩小范围从(80, 10)运营到(80, 10), 当检测到黑线时就停下, 此处将是黑线起点;假如没有检测到黑线则返回从(80, 12)运营到(0, 12)检测到的黑线即为黑线起点。

以同样的运营检测方式即可寻找出黑线的起点。

在连续段寻迹时, 通过判断四个传感器的16种组合状态, 使电机作出相应的伸缩动作。

当轨迹为间断线时, 电机拉动传感器在大角度方向内位移, 直到在某一方向检测到新的黑线为止。

然后再调用连续段的寻迹程序。

4.3 系统各模块单元电路设计4.3.1 电源部分电路设计本系统中使用了直流12V电机, 其额定工作电压为12V, 而单片机额定工作电压为5V, 所以电路中采用了7805和7812作为稳压模块, 其最大输出电流为1.5A, 满足系统电机驱动电流的规定, 其电路如图4.3.1所示。

4.3.2 电机控制模块设计物体运动的轨迹由电机的转速和转向决定, 电机的转速和转向的控制是通过多圈电位器对滑轮所转的圈速进行检测, 同时通过另一个计数器对时间进行测量, 结合两个计数器的值, 由单片机计算出电机的速度, 而物体运动的轨迹的里程由滑轮的周长和所转的圈数来计算。

电子设计竞赛简介

电子设计竞赛简介全国大学生电子设计竞赛是面向大学生的群众性科技活动,目的在于按照紧密结合教学实际,着重基础、注重前沿的原则,促进电子信息类专业和课程的建设,引导高等学校在教学中注重培养大学生的创新能力、协作精神;加强学生动手能力的培养和工程实践的训练,提高学生针对实际问题进行电子设计、制作的综合能力;吸引、鼓励广大学生踊跃参加课外科技活动,为优秀人才脱颖而出创造条件。

电子设计竞赛题目包括“理论设计”和“实际制作”两部分,以电子电路(含模拟和数字电路)设计应用为基础,可以涉及模-数混合电路、单片机、可编程器件、EDA软件的应用。

电子设计竞赛要求学生组队参加,组内成员协作利用课堂所学的专业课知识,结合学生课余自学的可编程器件知识及PCB制板软件等,将电子设计的题目按要求制成实物。

因此,这对于学习电子类相关专业的学生及喜爱电子的学生来说,都是一次很好的巩固专业知识,提高动手实践能力和团队协作能力,实现自己梦想的机会。

我校电子设计竞赛自1996年开始,每年一届,今年已是我校电子设计竞赛的第14届。

校电子设计竞赛是为全国大学生电子设计竞赛培养人才的主要途径。

回望过去,每一届校赛都吸引了全校各院的大批电子设计爱好者。

通过我校举办这个活动,提供这个锻炼动手能力与实现梦想的平台,爱好者们个个都颇有收获。

他们不仅学习了更多的课本和课堂无法获取的知识,提高了自己编程、制板、设计调试电路、分析解决问题的能力,增强了团队协作意识,更重要的是,在这个大舞台上,很多爱好者初次体会到了自己动手去实现梦想的快乐与成功的喜悦。

两年一届的全国大学生电子设计竞赛即将开始,截至2009年,我校共参与全国大学生电子设计竞赛10届,其中获得了“索尼杯”(全国赛中最高奖项,每届仅此一组)一组,一等奖18组,二等奖15组,赛区一等奖34组。

回顾以往的竞赛历程,这些在国赛中成绩优异的参赛队都经历了从“兴趣→电子科技苑和校赛→全国赛”的过程。

过程是艰难的,成绩是辉煌的,只要你有兴趣,只要你有恒心,踏上这个舞台你就一定能演绎自己的辉煌。

全国大学生电子设计竞赛

3、推荐参考书与网站

技术资料

4、芯片选择

查找前人的设计 尽量选用常用、便于购买的芯片 关键芯片(如单片机)要备用

4、芯片选择

常用处理器

单片机:PIC系列、AVR系列、STC系列…… ARM:STM32F103、ARM7 CPLD:EPM1270、EPM7128 FPGA:EP2C5T144C8、EP2C8T144C8、EP2C8Q2 08C8

全国大学生电子竞赛

主要内容

1 全国电子竞赛简介 2 历届考题分类 3 推荐参考书与网站 4 芯片的选择 5 竞赛前的准备工作 6 竞赛题目解析 7 竞赛注意事项 8 竞赛时间安排

1、 全国电子竞赛简介

➢ 组织机构:教育部高等教育司和信息部人事司 ➢ 举办时间:9月份,赛期为4天3夜。 ➢ 一般时间为9月4日8:00~9月7日20:00。 ➢ 竞赛流程 ➢ 竞赛分为国家奖和省奖 ➢ 一般为6个题,题目以电子技术应用设计为主要内容,

3、推荐参考书与网站

2 全国大学生电子设计竞赛作品选编

3、推荐参考书与网站

3 准备内容 电路、模电、数电 C语言、单片机接口技术 高频电子、PLC 微弱信号检测 电力电子技术 数字信号处理 传感器与检测技术 Mutisim软件仿真、Proteus软件仿真 常用模块电路、常用仪器仪表等

3、推荐参考书与网站

建议采用16位的单片机(AD、PWM、捕获),

5、竞赛前的准备工作

4 仪器仪表类及数电类

程控增益、各种运放电路、模拟滤波器、锁相环电 路、乘法器电路、滞回比较器、液晶波形描绘、AD、D A、信号发生器、verilog(VHDL)语言等。

FFT、数字滤波、PID,各种仪器原理。 此类题建议使用32位处理器,芯片选择很关键。

(完整版)全国大学生电子设计竞赛

全国大学生电子设计竞赛一、竞赛时间和竞赛周期全国大学生电子设计竞赛从1997年开始每二年举办一届,竞赛时间定于竞赛举办年度的9月份,赛期四天。

全国大学生电子设计竞赛每逢单数年的9月份举办,赛期四天三夜(具体日期届时通知)。

在双数的非竞赛年份,根据实际需要由全国竞赛组委会和有关赛区组织开展全国的专题性竞赛,同时积极鼓励各赛区和学校根据自身条件适时组织开展赛区和学校一级的大学生电子设计竞赛。

二、竞赛方式竞赛采用全国统一命题、分赛区组织的方式,竞赛采用“半封闭、相对集中”的组织方式进行。

竞赛期间学生可以查阅有关纸介或网络技术资料,队内学生可以集体商讨设计思想,确定设计方案,分工负责、团结协作,以队为基本单位独立完成竞赛任务;竞赛期间不允许任何教师或其他人员进行任何形式的指导或引导;竞赛期间参赛队员不得与队外任何人员讨论商量。

参赛学校应将参赛学生相对集中在实验室内进行竞赛,便于组织人员巡查。

为保证竞赛工作,竞赛所需设备、元器件等均由各参赛学校负责提供。

三、评奖工作(1)评奖工作采用“校为基础、一次竞赛、二级评奖”的方式进行,即竞赛建立在学校广泛开展课外科技活动的基础上,积极组织学生参加全国大学生电子设计竞赛活动,每次全国竞赛后,经赛区评奖(第一级评奖)后再推荐出赛区优秀参赛队参加全国评奖(第二级评奖)。

(2)各赛区组委会聘请专家组成赛区评委会,评选本赛区的一、二、三等奖,获奖比例一般不超过总参赛队数的三分之一。

此外,对参赛成功者,赛区也可酌情颁发“成功参赛奖”或“成功参赛证书”。

(3)由于各赛区采用的是全国统一制定的竞赛命题和测试评分规则,赛区颁发的获奖证书、奖杯等冠名原则上为“XXXX年XXX杯全国大学生电子设计竞赛XX赛区(本科生组或高职高专学生组)”。

(4)全国分组设立一、二等奖。

本科生组和高职高专学生组获奖队数量分别不超过当年实际参赛队的8%,其中一等奖和二等奖的比例原则上为3:7。

竞赛颁发全国统一的获奖证书。

全国大学生电子设计竞赛获奖名单

全国大学生电子设计竞赛获奖名单

一、本科组获奖名单

一等奖:

1.山东大学:

项目:智能LED照明系统

团队成员:徐海飞、李文君、王宇洁、郭芳、罗乐晗、雷迪2.武汉大学:

项目:用于汽车安全驾驶控制的环境抗干扰传感器

团队成员:赵威轶、宋玉玲、马芷茹、梁政达

二等奖:

1.华中科技大学:

项目:基于无线传感器网的工厂安全检测系统

团队成员:李思亮、朱贝贝、金晓婷、陈妍妍

2.华南农业大学:

项目:无线地表水质监控系统

团队成员:王汉明、陈友毅、林文钰、何元昊

三等奖:

1.广西大学:

项目:基于无线传感器网的植物实验参数监测系统

团队成员:文昊、赵安宇、黄晓英2.重庆大学:

项目:智能家居控制系统

团队成员:潘晓君、袁建伟、钱奔。

全国大学生电子设计竞赛

全国大学生电子设计竞赛全国大学生电子设计竞赛是一个旨在激发和培养大学生创新能力和实践能力的电子设计比赛。

每年都有来自全国各个高校的优秀学子参赛,他们通过比拼创意、技术和团队合作能力,展示出了丰富的想象力和才能。

电子设计竞赛分为个人赛和团队赛两个部分,允许参赛选手自由选择设计项目。

参赛者可以基于单片机、嵌入式系统、无线通信等进行设计创新。

无论是设计的创意性还是技术实施方面,都要求参赛选手具备独立思考和解决问题的能力。

参赛作品评比主要考虑创新性、工程性以及可行性等方面,对整个设计过程的完整性和合理性进行评估。

这项竞赛为大学生提供了施展才华、展现成果的舞台。

通过参加竞赛,学生们可以贯彻理论知识和实践技能,提高解决问题的能力和综合素质。

同时,竞赛也加强了学生们的合作意识和团队精神,鞭策他们不断追求技术进步和创新。

参赛学生在准备过程中面临着各种挑战和困难。

他们需要深入学习相关知识,掌握电子设计的基本理论与技术。

同时,他们还需要进行大量的实际操作和实践,来熟悉电子元器件的使用和电路的设计。

在团队赛中,学生们需要密切合作,充分发挥各自的优势,共同完成一个复杂的设计任务。

这些挑战和困难充分考验了学生们的学习能力和智慧。

然而,参与全国大学生电子设计竞赛也带来了很多机会和收获。

学生们可以通过竞赛来拓宽自己的视野,了解电子工程领域的最新技术和发展趋势。

他们也可以与其他高校的学生进行交流和互动,增加了解其他学校的机会,拓展了人脉。

同时,优秀的参赛者还有机会获得奖金和奖学金等,这对于学生的学习和生活都是一种肯定和激励。

综上所述,全国大学生电子设计竞赛是一项重要的学生实践和创新活动。

通过竞赛,学生们可以充分发挥自己的才华和创造力,同时也促进了学生们的知识学习和团队协作能力的提高。

参与竞赛不仅为学生提供了展示自我的机会,也为他们的未来发展打下了坚实的基础。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

全国大学生电子设计竞赛Revised as of 23 November 20202017年全国大学生电子设计竞赛远程幅频特性测试装置(H题)2017年8月12日摘要本远程幅频特性测试装置是由信号源、放大器、幅频特性装置、电源模块等组成。

本设置中信号源的输出频率范围为:1MHz~40MHz且具有自动扫描功能,步进: 1MHz;放大器的输出电压的峰值为1V,且波形无明显失真;远程幅频特性测试装置可用示波器显示放大器输出信号的幅频特性。

放大器的输出信号信息与笔记本电脑连接起来时,笔记本电脑就可完成放大器输出信号的幅频特性测试,并能以曲线的方式显现出来。

用设计利DDS原理由FPGA经D/A转换产生扫频信号,再经待测网络实现峰值检测和相位检测,从而完成了待测网络幅频和相频特性曲线的测量和显示。

经过调试,示波器显示待测网络频率范围1MHz~40 MHz的幅频和相频特性曲线,该系统工作稳定,操作方便。

关键词:频率特性测试仪、幅频特性、相频特性、FPGA1.方案设计与论证单片机的选择方案一:普通的AT89S51从内部的硬件到软件有一套完整的按位操作系统,称作位处理器,处理对象不是字或字节而是位。

不但能对片内某些特殊功能寄存器的某位进行处理,如传送、置位、清零、测试等,还能进行位的逻辑运算,其功能十分完备,使用起来得心应手。

但是运算速度过慢,保护能力很差,AD、EEPROM等功能需要靠扩展,增加了硬件和软件负担方案二:STM32系列基于专为要求高性能、低成本、低功耗的嵌入式应用专门设计的ARM Cortex-M3内核。

还支持以太网、USB OTG和外设接口同时工作,因此,开发人员只需一颗芯片就能设计整合所有这些外设接口的网关设备。

运算速度大约是51单片机的几十倍方案三:采用以增强型80C51内核的STC系列单片机。

AT89S51具有完整的输入输出、控制端口、以及内部程序存储空间。

与我们通常意义上的类似,可以通过外接A/D,D/A转换电路及运放芯片实现对传感器传送信息的采集,且能够提供以点阵或LCD液晶及外接按键实现人机交互,能对内部众多连接对进行精确操控,具有强大的工控能力。

其语法结构与我们常用的计算机C语言基本相同方案选择:方案2运算速度较快,开发容易与相关设备兼容性高整体方案设计方案一:FFT法。

这种频谱分析采用数字方法直接由模拟/数字转换器(ADC)对输入信号取样,再经FFT处理后获得频谱分布图。

它的频率范围受到ADC采集速率和FFT运算速度的限制。

为获得良好的仪器线性度和高分辨率,ADC的取样率最少等于输入信号最高频率的两倍。

FFT运算时间与取样点数成对数关系,频谱分析需要高频率、高分辨率和高速运算时,要选用高速的FFT硬件,或者相应的数字信号处理器(DSP)芯片。

可见这种方法的优点是硬件电路简单,主要依靠软件运算,可以提高分辨率。

其缺点是频率越高,对ADC和DSP芯片的速度要求越高,相应价格也越昂贵。

方案二:分段FFT。

这种方法将输入信号分段,逐段进行FFT的处理,这样分段取样降低了对ADC和FFT硬件的速度要求,又可以在相对窄的频段内得到更高的频谱分辨率。

但是这种方法在软件和硬件的设计和测试上显然要复杂很多。

方案三:扫频法。

这种频谱分析采用外差原理,由振荡器产生一定步进频率的信号与输入信号相乘,然后由适当的滤波器将差频分量滤出以代表相应频点的幅度。

振荡信号可以达到很宽的频率,与外部混频器配合,可扩展到很高频率。

这种方法的突出优点是扫频范围大,硬件成本低廉,但这种方法对硬件电路要求较高,各模块性能都需要精心设计,且连接在一起整体调试时有一定难度。

而且它只适于测量稳态信号的频率幅度,但获得测量结果要花费较长的时间。

根据实际条件和成本以及题意上的考虑,在满足题目要求的前提下,我们选择方案三来实现频谱分析的总体设计。

控制系统的论证与选择方案一:采用在面包板上搭建简易单片机系统在面包板上搭建单片机系统可以方便的对硬件做随时修改,也易于搭建,但是系统连线较多,不仅相互干扰,使电路杂乱无章,而且系统可靠性低,不适合本系统使用。

方案二:自制单片机印刷电路板自制印刷电路实现较为困难,实现周期长,此外也会花费较多的时间,影响整体设计进程。

不宜采用该方案。

方案三:采用单片机最小系统。

单片机最小系统包含了显示、矩阵键盘、A/D、D/A等模块,能明显减少外围电路的设计,降低系统设计的难度,非常适合本系统的设计。

综合以上三种方案,选择方案三。

2.系统理论分析与计算扫频测试法理论依据设频率响应为H(j ω)的实系数线性时,不变系统在信号x(n)_Acos(ω0n+f)激励下的稳态输出为y(n)。

利用三角恒等式,可将输入表示为2个复指数函数之和:()()*()x n g n g n =+式子中01()2jw n j f g n Ae e =对于输入为0jw n e 线性时,不变系统稳态输出为00()jw jw n H e e 。

根据线性性质可知,输入()g n 的响应()v n 为001()()2jw jw n jf v n Ae H e e ⎡⎤=⎣⎦ 同理,输入*()g n 的输出*()v n 是()v n 的复共轭。

于是得到输出结果的表达式为()()()[]0011()cos 22jf jw jwn jf jw jwn jw y n Ae H e e Ae H e e A H e w n qw f ---=+=++ 因此,输出信号和输入信号是频率相同的正弦波,仅有两点不同:第一,振幅被|H(ej ω)|加权,即网络系统在ω=ω0的幅度函数值;第二,输出信号相对于输入信号有一个数量为q(ω0)的相位时延,即网络系统在ω=ω0的相位值。

DDS 信号源根据DDFS 原理所产生的波形频率为:式中fclk 为基准频率,M 为相位增量因子,N 为累加器的位数。

M 取22,N 取24。

为得到100kHz 的信号,而且在每个周期希望取到32个以上点,则累加器输出后级D /A 转换需要至少3.2MHz 的速度,于是选取建立时间为30ns 、10位的DAC900,不仅满足了对D /A 转换速度的要求,而且具有10位数据线,减少了D /A 转换中固有的量化误差。

fclk 取40MHz ,频率的最小步进:相位差测量设INl和IN2为两路具有相位差经整形后得到的方波信号,Gate2为INl和IN2经过异或后得到的脉冲信号,Fo为FPGA内部的标准高频脉冲信号,取40MHz。

将IN2八分频,结合单片机控制,可得到一个动态门控信号Gatel。

动态门控与脉冲信号相“与”,可得到门限内的有限个脉冲信号Gate2。

Gate1中含有IN2的4个周期,Gate2含有8个异或脉冲。

其中分别对clk进行计数,分别得到计值M和N。

根据公式精确地测得相位差绝对值。

其时序如图所示。

由于对高频脉冲计数可能存在±1的误差:在F=100kHz时,Mmin≈1600,则δmax(△ψ)≈°?FPGA内部生成一个D触发器,以INl为触发器的数据输入,IN2为触发器的时钟输入,若触发器输出端为高电平,则△ψ>O°;若输出端为低电平,则△ψ<0°。

特性曲线显示分析频率范围1M-40MHz,步进100kHz,则有390个点。

我们采用320*240分辨率的彩屏来显示幅频与相位。

整个显示图像根据测量结果转化为对应的点从+90°到-90°变化显示。

具体参数包括模式、频率、幅度、相位、中心频率、带宽会在图像侧边显示。

参数具体计算是根据幅频响应与相频响模拟分析转换为数学分析通过单片机计算得到并在屏幕上进行显示。

3.电路的设计.放大器为了减少级数,系统采用数据手册参考设计值在输入50欧匹配的情况下,对于增益为20db的同相接法中,RF取174欧,RG取9欧。

TLV3501比较器的设计TLV3501主要是挽输出比较器,主要是405ns传播延时好人操作++,由于超出摆幅输入共模范围,使其更合适低电压应用的理想选择同时可对TTL逻辑在10MHZ情况下的输出波形系统总体框图电源EP3C16Q240C8 器件内核工作电压 VCCINT 为,锁相环(PLL)所需的数字电压为,锁相环电压调节器所需的模拟电压为。

该器件将所有I/O 端口分为 8个 I/O 块—BANK1-BANK8,这样每个 I/O 块可以用,、、和幅频特性自动测试系统的设计与实现18等 I/O 端口电压供电,满足不同 I/O 电平标准。

为了简化电路,本设计用电平统一为 8 个 I/O 块端口供电。

图电源电路图电源电路如图所示,数字电源+5V 分别经过,和稳压器件降压为、和,供 I/O 口、PLL 电压调节器和内核使用。

PLL 数字电压 VCCD_PLL 是由内核电压VCCINT 经过 LC 滤波电路后的电压。

由于该器件有 4 个 PLL,需要了分别为其供电,因此在供电管脚之间加上去耦电容。

与 PLL供电情况类似,所有 I/O 块的内核电源管脚和 I/O 端口电源管脚之间也需要加上去耦电容来避免互相间的耦合干扰。

滤波电路本设计 DDS 的采样频率通过锁相环倍频可达到 100MHz,根据奈奎斯特采样定理输出信号的最高频率为其一半,即 50MHz,但是在实际情况中,信号的输出频率只能达到采样频率的 40%,即 40MHz。

因此根据需要,设计一个通带截至频率为 40 MHz,通带允许的最大衰减为 dB,阻带频率为 50MHz,阻带最小衰减为 50 dB,特性阻抗为 200 的低通滤波器。

常用的滤波器按设计分为:Butterworth 滤波器、Chebyshev 滤波器和椭圆滤波器等。

图是三种低通滤波器频率特性响图。

从图中可以看出,Butterworth 滤波器的通带和阻带比较平坦,其过渡带比较平缓;Chebyshev 滤波器的通带是等波纹抖动的,过渡带也比较平缓;椭圆滤波器的通带和阻带都是抖动的,过渡带是比较陡峭的。

综合比较选择椭圆滤波器进行设计。

图低通滤波器频率响应对比图4.测试方案及测试结果测试仪器:数字万用表DT9205,直流稳压源QJ-3003S、频率特性测试仪(1MHz~150MHz)、500MHz 数字示波器、100MHz 双通道数字示波器。

测试方案:1mVrms或更低,将信号通过射频宽带放大器,且外接50Ω负载,确认放大倍数为60dB时,再用示波器观察,记录无明显失真时的带宽和平坦度。

在测量噪声时,在射频宽带放大器放大60dB的情况下,将输入端短入到地,外接50Ω负载下,再用示波器观察其输出有效值。

在测量增益控制精度时,通过示波器观察程序控制的增益值与实际增益值的误差大小。

在测量增益控制范围时,如果测0dB或其他较低的增益时,示波器无法读出信号大小,则应该加大输入信号,直到示波器可以有效辨别为止。