锁相环及压控振荡器电路实验

模拟锁相环

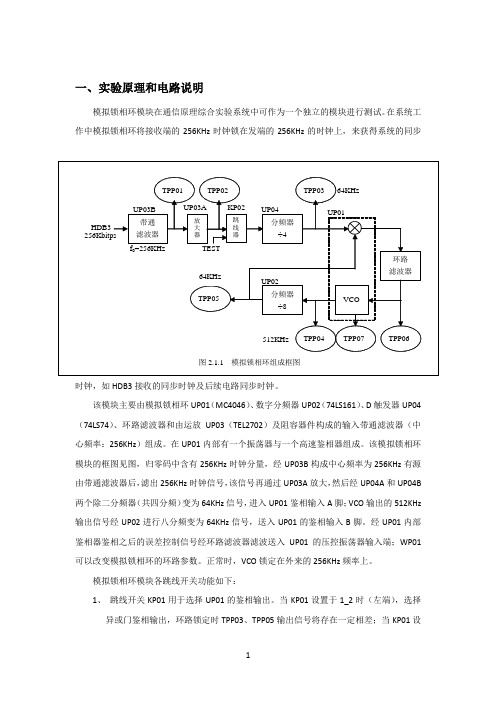

一、实验原理和电路说明模拟锁相环模块在通信原理综合实验系统中可作为一个独立的模块进行测试。

在系统工作中模拟锁相环将接收端的256KHz时钟锁在发端的256KHz的时钟上,来获得系统的同步时钟,如HDB3接收的同步时钟及后续电路同步时钟。

该模块主要由模拟锁相环UP01(MC4046)、数字分频器UP02(74LS161)、D触发器UP04(74LS74)、环路滤波器和由运放UP03(TEL2702)及阻容器件构成的输入带通滤波器(中心频率:256KHz)组成。

在UP01内部有一个振荡器与一个高速鉴相器组成。

该模拟锁相环模块的框图见图,归零码中含有256KHz时钟分量,经UP03B构成中心频率为256KHz有源由带通滤波器后,滤出256KHz时钟信号,该信号再通过UP03A放大,然后经UP04A和UP04B 两个除二分频器(共四分频)变为64KHz信号,进入UP01鉴相输入A脚;VCO输出的512KHz 输出信号经UP02进行八分频变为64KHz信号,送入UP01的鉴相输入B脚。

经UP01内部鉴相器鉴相之后的误差控制信号经环路滤波器滤波送入UP01的压控振荡器输入端;WP01可以改变模拟锁相环的环路参数。

正常时,VCO锁定在外来的256KHz频率上。

模拟锁相环模块各跳线开关功能如下:1、跳线开关KP01用于选择UP01的鉴相输出。

当KP01设置于1_2时(左端),选择异或门鉴相输出,环路锁定时TPP03、TPP05输出信号将存在一定相差;当KP01设置于2_3时(右端),选择三态门鉴相输出,环路锁定时TPP03、TPP05输出信号将不存在相差,详情请参见4046器件性能资料。

调整电位器WP01可以改变模拟锁相环的环路参数。

2、跳线开关KP02是用于选择输入锁相信号:当KP02置于1_2时(HDB3:左端),输入信号来自HDB3编码模块的HDB3码信号;当KP02置于2_3时(TEST:右端)选择外部的测试信号(J007输入),此信号用于测量该模拟锁相环模块的性能。

浅谈压控振荡器在锁相环电路中的应用

它 为环路 中的固有积分环节 。式 ( —1) 1 7 就是压控振荡器 相位

控制特性 的数学模型 , 若对式 ( —1) 1 7 进行拉 氏变换 , 可得 到在 复频域 的表示式 为

0 (): k 2s d ( —1) 1 8

3有 源比例积 分滤波器 [ ) J 有源 比例积分滤波 器 由运算 放 大器组 成 , 电路 如 图 5所

l — 一 = 0 l — m

“

:

(_ ) l ) 1 5 一 ,

此时 , 出信 号的频率 已偏离 了原来 的 自由振荡 频率 o 输 ( 控制 电压 u () 0时 的频率 )其 偏移量 由式( —4 和 ( —5 ct= , 1 ) 1 )

得 到为

d ot 0()

了

() a时域模型

() b频域模型

图 3 环路滤 波器的模型

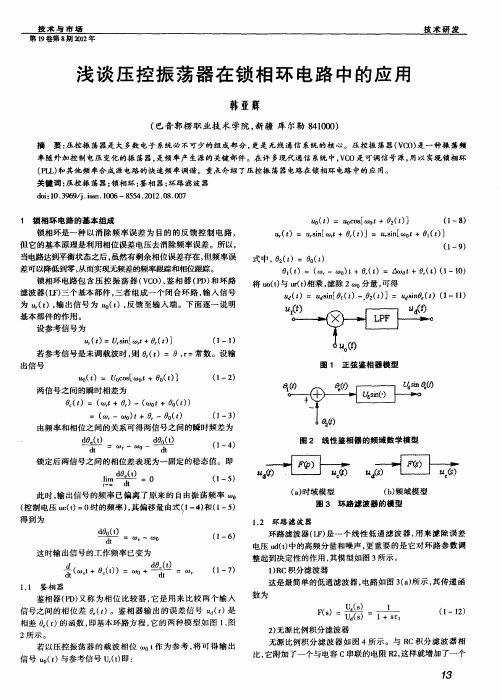

1 2 环 路 滤 波 器 .

:t 一 0 . O r

(— ) 卜 。 1 6 ,

环路 滤波器( F 是 一个 线性低 通滤 波器 , L) 用来 滤 除误差

电压 u () d t中的高频分量和噪声 , 更重要 的是它对 环路参数 调 整起 到决定性的作用 , 其模 型如 图 3所示 。

示 。当运算放大器开环 电压 增益 A为有 限值 时 , 它的传递 函

( 一  ̄ ) + 一 0 () 0 t 0 o

( —3 1 )

由频率和相位之 间的关系可得两信号之 间的瞬时频差为

T

: 一 一T ot d ( 0 ) C 一T O一 r

( 1

-

4 )

图 2 线性鉴相器 的频域 数学模 型

锁定后 两信号之 间的相位差表现为一 固定 的稳态 值。即

两种高频CMOS压控振荡器的设计与研究

两种高频CMOS压控振荡器的设计与研究锁相环在通讯技术中具有重要的地位,在调制、解调、时钟恢复、频率合成中都扮演着不可替代的角色。

可控振荡器是锁相环的核心部分。

最近,鉴于对集成电路低功耗和高集成度的追求,越来越多的研究人员投人到基于CMOS工艺的压控振荡器的设计。

环形压控振荡器因为具有宽的调谐范围和小的芯片面积,在电路的精心设计下也可以具有不错的相位噪声性能,从而在数字通信系统中得到广泛的应用。

而随着CMOS工艺特征尺寸的不断减小,根据CMOS工艺按比例缩小理论,电源电压也要同比例降低。

与采用1.8 V电源电压的0.18 μm CMOS工艺相比,传统全差分延时单元结构的输出信号的摆幅被限制在非常小的区域内,不但降低了输出信号的信噪比(SNR),而且必须经过放大等一系列处理后才能送给下一级电路。

文中分析了影响压控振荡器性能的重要参数,同时设计实现了两种多谐压控振荡器,给出了相应的实验结果。

1 VCO的工作原理与性能指标VCO是一个电压/频率转换电路,在环路中作为被控振荡器,它的输出频率应随控制电压线性地变化。

一个理想的VCO其输出频率和输入频率的关系ωout=ω0+KVCOVcont (1)式中,ω0是控制电压Vcont为零时的振荡器的固定频率,KVCO为VCO的增益或灵敏度(单位为rad/s·V-1)。

由式(1)可以推导出VCO的传输函数由式(2)可以得出,当VCO被放在锁相环中时,其输出经分频器后接到鉴相器的输入,对鉴相器输出起作用的不是其频率,而是相位。

所以在锁相环中VCO通常被看作输入为控制电压,输出为相位的系统。

所以VCO在锁相环系统中就像一个理想的积分器,其传输函数可以表示为在实际应用中,VCO的线性范围有限,超出这个范围之后,环路的参数就会变化较大,不利于环路设计。

通常,评价VCO的好坏主要有以下特征:(1)低抖动或低相位噪声:由于电路结构、电源噪声、地噪声等因素的影响,VCO的输出信号并不是理想的方波或正弦波,其输出信号存在一定的抖动,转换成频域后可看出信号中心频率附近也会有较大的能量分布,即相位噪声。

电荷泵锁相环的模型研究和电路设计

结论

本次演示对电荷泵锁相环的模型研究和电路设计进行了详细探讨。通过建立 数学模型并简化分析,我们发现电荷泵锁相环的性能主要受到电荷泵增益、环路 滤波器时间常数以及输入信号频率的影响。在此基础上,我们设计了一款电荷泵 锁相环电路,并对关键元件进行了选择和优化。然而,该电路仍存在一些不足之 处,需要进一步改进。

2、低功耗:该设计方案采用了先进的工艺和电路设计,使得芯片的功耗较 低,延长了设备的使用寿命。

3、高集成度:所设计的锁相环集成电路芯片具有高集成度,减小了设备的 体积和重量,方便了实际应用。

结论:

本次演示通过对高速锁相环集成电路芯片的深入研究和实验验证,提出了一 种针对高速条件下的高效设计方案。实验结果表明,所设计的芯片在高速条件下 具有良好的性能和可靠性。但是,我们也意识到该设计方案仍存在一些不足之处, 例如在复杂电磁环境下的稳定性等问题。

近年来,随着太阳能技术的快速发展,光伏并网逆变器在太阳能发电系统中 得到了广泛应用。三相锁相环设计在光伏并网逆变器控制中具有重要意义,是实 现并网稳定运行的关键技术之一。本次演示将阐述三相锁相环设计及光伏并网逆 变器控制的研究内容和方法。

在光伏并网逆变器控制领域,文献综述表明,现有的研究主要集中在逆变器 拓扑结构、控制策略和并网保护等方面。其中,三相锁相环设计是逆变器控制策 略中的重要组成部分。已有的三相锁相环设计方法主要包括基于PI调节器和基于 同步检测器的设计方法。然而,这些方法在实时性、准确性和稳定性方面仍存在 一定的问题,特别是在复杂环境和恶劣条件下。

模型研究

1、电荷泵锁相环的原理和内部 机制

电荷泵锁相环主要由电荷泵、环路滤波器(Loop Filter)和电压控制振荡 器(VCO)三个主要部分组成。其工作原理是,通过电荷泵将输入信号的相位差 转化为电压,再经环路滤波器滤除高频成分,得到控制VCO的直流电压,最终实 现输出信号与输入信号的相位和频率同步。

锁相环电路中压控振荡器的分析与设计

关键词 : 压控 振荡器 ; 相位噪声 ; D ;二次谐波滤波技 术 AS

中 图分 类 号 : P 7 T 3 文 献标 识 码 : A 文 章 编 号 :17 — 2 6 2 1 )4 0 7 -4 6 4 6 3 (0 12 - 17 0

De i n nd a a y i fVCo n PLL r t t sg a n l ssO i Cie i l

c n e e u n yo MHzc n r a h- 4 .2 d cHz e tr q e c f r f 1 a c 1 88 5 B / . e

Ke r s:VC y wo d O;p a e n ie; h s os AD S;f tai n o e s c n a o i e h iu i r t f h e o d h r n ct c n q e l o t m

t e s u t r fc n e t n lL h t cu eo o v n i a C VCO, l ai n o e s c n a mo i e h i u a n l d d t e u e t ep a e n ie r o a f t t ft e o d h r n c t c n q e W i c u e r d c h h s o s i r o h s o a d t e c ru tsmu a in i c mp ee y t e s f a e o i n ’ n ic i i lt S o l td b h o t r fAgl t SADS T e smua in r s l h w t a s L o tg — h o w e . h i lt e u t s o h tmi C v l e o s a c n rl d o c l tra h e e o a wi ey tr h e u n y a d t e r n e i 1 — 2 1 o tol s i ao c iv d t d l u n t e f q e c n h a g s . e l r 9 .GHz h h s o s wa r m h .T e p a e n ie a y f o.9 1 1

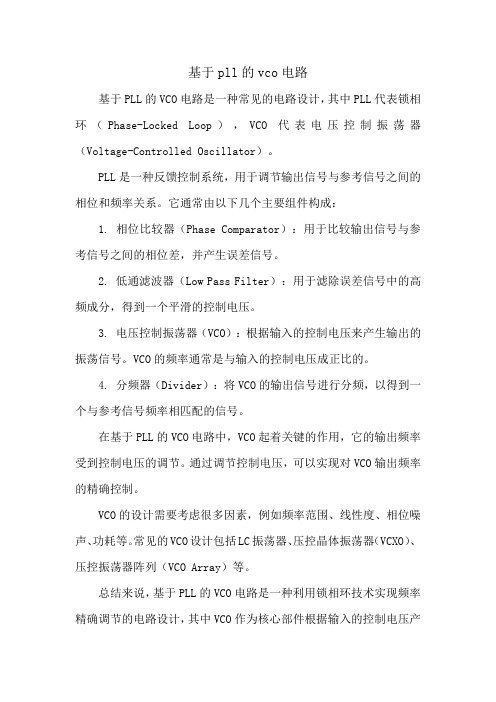

基于pll的vco电路

基于pll的vco电路

基于PLL的VCO电路是一种常见的电路设计,其中PLL代表锁相环(Phase-Locked Loop),VCO代表电压控制振荡器(Voltage-Controlled Oscillator)。

PLL是一种反馈控制系统,用于调节输出信号与参考信号之间的相位和频率关系。

它通常由以下几个主要组件构成:

1. 相位比较器(Phase Comparator):用于比较输出信号与参考信号之间的相位差,并产生误差信号。

2. 低通滤波器(Low Pass Filter):用于滤除误差信号中的高频成分,得到一个平滑的控制电压。

3. 电压控制振荡器(VCO):根据输入的控制电压来产生输出的振荡信号。

VCO的频率通常是与输入的控制电压成正比的。

4. 分频器(Divider):将VCO的输出信号进行分频,以得到一个与参考信号频率相匹配的信号。

在基于PLL的VCO电路中,VCO起着关键的作用,它的输出频率受到控制电压的调节。

通过调节控制电压,可以实现对VCO输出频率的精确控制。

VCO的设计需要考虑很多因素,例如频率范围、线性度、相位噪声、功耗等。

常见的VCO设计包括LC振荡器、压控晶体振荡器(VCXO)、压控振荡器阵列(VCO Array)等。

总结来说,基于PLL的VCO电路是一种利用锁相环技术实现频率精确调节的电路设计,其中VCO作为核心部件根据输入的控制电压产

生输出的振荡信号。

它在许多应用中被广泛使用,例如通信系统、时钟生成电路、频率合成等领域。

锁相环及实验

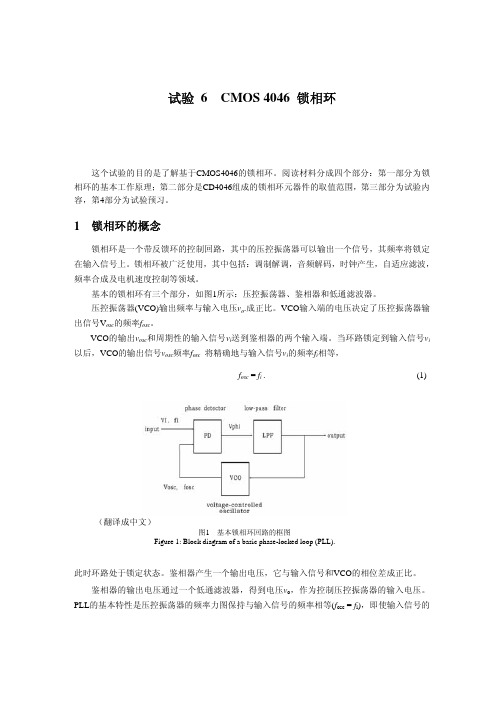

试验 6 CMOS 4046 锁相环这个试验的目的是了解基于CMOS4046的锁相环。

阅读材料分成四个部分:第一部分为锁相环的基本工作原理;第二部分是CD4046组成的锁相环元器件的取值范围,第三部分为试验内容,第4部分为试验预习。

1 锁相环的概念锁相环是一个带反馈环的控制回路,其中的压控振荡器可以输出一个信号,其频率将锁定在输入信号上。

锁相环被广泛使用,其中包括:调制解调,音频解码,时钟产生,自适应滤波,频率合成及电机速度控制等领域。

基本的锁相环有三个部分,如图1所示:压控振荡器、鉴相器和低通滤波器。

压控振荡器(VCO)输出频率与输入电压v o .成正比。

VCO 输入端的电压决定了压控振荡器输出信号V osc 的频率f osc 。

VCO 的输出v osc 和周期性的输入信号v i 送到鉴相器的两个输入端。

当环路锁定到输入信号v i 以后,VCO 的输出信号v osc 频率f osc 将精确地与输入信号v i 的频率f i 相等,f osc = f i . (1)此时环路处于锁定状态。

鉴相器产生一个输出电压,它与输入信号和VCO 的相位差成正比。

鉴相器的输出电压通过一个低通滤波器,得到电压v o ,作为控制压控振荡器的输入电压。

PLL 的基本特性是压控振荡器的频率力图保持与输入信号的频率相等(f osc = f i ),即使输入信号的(翻译成中文)图1 基本锁相环回路的框图Figure 1: Block diagram of a basic phase-locked loop (PLL).频率在做变化。

假设锁相环处于锁定状态,输入信号的频率f i增大一点,则VCO的输出与输入信号的相位差将变大。

结果,滤波器的输出电压V0将增大,压控振荡器的输出频率f osc增加,直到与fi一致,这样就保持了PLL在锁定状态。

输入信号频率的最大可能的变化范围被称为锁相环的锁定范围。

如果开始的时候锁相环处于锁定状态,输入信号的频率变得比允许的最小频率还要小的时候,或者变得比最大允许的频率还要大的时候,锁相环将不再能够保持振荡器的输出频率与输入频率一致,这时就称为失锁。

模拟锁相环实验实验报告

实验十四模拟锁相环实验一、实验目的1、了解用锁相环构成的调频波解调原理。

2、学习用集成锁相环构成的锁相解调电路。

二、实验内容1、掌握锁相环锁相原理。

2、掌握同步带和捕捉带的测量。

三、实验仪器1、1号模块 1块2、6号模块 1块3、5号模块 1块4、双踪示波器 1台四、锁相环的构成及工作原理1、锁相环路的基本组成锁相环由三部分组成,如图14-1所示,它由相位比较器PD、低通滤波器LF、压控振荡器VCO三个部分组成一个闭合环路,输入信号为V i(t),输出信号为V0(t),反馈至输入端。

下面逐一说明基本部件的作用。

鉴相器PD 环路滤波器LF压控振荡器VCO)(t V i)(tVD)(tVC)(tV 图14-1 锁相环组成框图一、压控振荡器(VCO)VCO是本控制系统的控制对象,被控参数通常是其振荡频率,控制信号为加在VCO上的电压,故称为压控振荡器,也就是一个电压-频率变换器,实际上还有一种电流-频率变换器,但习惯上仍称为压控振荡器。

二、鉴相器(PD )PD 是一个相位比较装置,用来检测输出信号V 0(t)与输入信号V i (t)之间的相位差θe (t),并把θe (t)转化为电压V d (t)输出,V d (t)称为误差电压,通常V d (t)作为一直流分量或一低频交流量。

三、环路滤波器(LF )LF 作为一低通滤波电路,其作用是滤除因PD 的非线性而在V d (t)中产生的无用的组合频率分量及干扰,产生一个只反映θe (t)大小的控制信号V e (t)。

按照反馈控制原理,如果由于某种原因使VCO 的频率发生变化使得与输入频率不相等,这必将使V 0(t)与V i (t)的相位差θe (t)发生变化,该相位差经过PD 转换成误差电压V d (t),此误差电压经LF 滤波后得到V c (t),由V c (t)去改变VCO 的振荡频率使趋近于输入信号的频率,最后达到相等。

环路达到最后的这种状态就称为锁定状态,当然由于控制信号正比于相位差,即)()(t t V e d θ∝因此在锁定状态,θe (t)不可能为零,换言之在锁定状态V 0(t)与V i (t)仍存在相位差。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

自动相位控制方框图

θR(t)

鉴相器

Ud(t) 环路滤波器 Uc(t) 压控振荡器 θV(t)

θV

原理图

4046管脚分布

VDD Vz IN1 OUT22 R2 R1 Vd VCO1

16 15 14 13 12 11 10 9

CD4046

12345678

OUT21 OUT1 IN2 VCO0 INH Ct Ct Vss

锁相环及压控振荡器电路实验

电子实验室

实验目的

? 1. 通过实验深入了解锁相环的工作原理 和特点;

? 2. 了解锁相环环路的锁定状态、失锁状 态、同步带、捕捉带等基本概念。

? 3. 掌握锁相环主要参数的测试方法。

实验内容

? 1. 观察模拟锁相环的锁定状态、失锁状 态及捕捉过程。

? 2. 观察测量环路的捕捉带和同步带。

? 2、电源电压对固有振荡频率有何影响?

捕捉带与同步带

3 4

2 1

f

fi3 fi4

fv

捕捉带

同步带

fi2 fi1

捕捉带 ? fV= fi2-fi4 同步带 ? fL= fi1- fi3

ΔfP =K0ΔV2/2

ΔfH =K0ΔV1/2 K0=18 HZ/V

Hale Waihona Puke 思考题? 1、VCO的固有振荡频率fv由哪些参数决 定?当改变时,锁相环的捕捉带与同步 带是否改变?