DSP汇编指令总结

DSP汇编指令总结

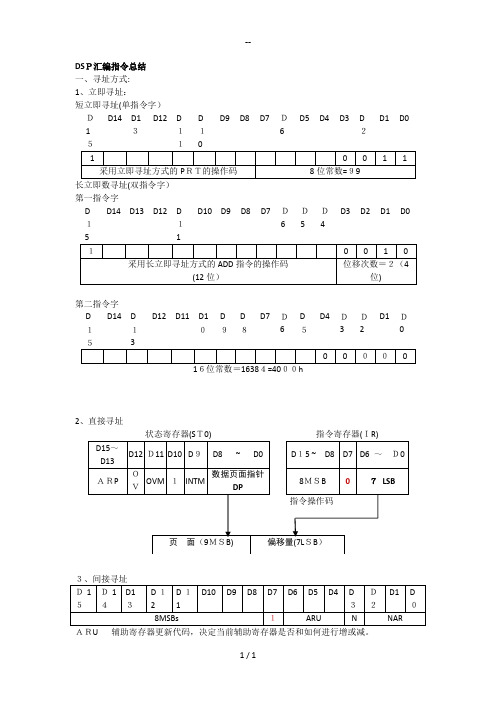

DS P汇编指令总结 一、寻址方式: 1、立即寻址:短立即寻址(单指令字) D1D14 D13 D12 D 1D 1D9 D8 D7 D6 D5 D4 D3 D2D1 D0长立即数寻址(双指令字) 第一指令字 D 1D14 D13 D12 D 1D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0第二指令字 D 1D14 D 1D12 D11 D10 D 9 D 8 D7 D6 D 5 D4 D3 D2 D1 D0 16位常数=16384=4000h2、直接寻址ARU 辅助寄存器更新代码,决定当前辅助寄存器是否和如何进行增或减。

N规定是否改变ARP值,(N=0,不变)4.3.1、算术逻辑指令(28条)4.3.1.1、加法指令(4条);4.3.1.2、减法指令(5条);4.3.1.3、乘法指令(2条);4.3.1.4、乘加与乘减指令(6条);4.3.1.5、其它算数指令(3条);4.3.1.6、移位和循环移位指令(4条);4.3.1.7、逻辑运算指令(4条);4.3.2、寄存器操作指令(35条)4.3.2.1、累加器操作指令(6条)4.3.2.2、临时寄存器指令(5条) 4.3.2.3、乘积寄存器指令(6条) 4.3.2.4、辅助寄存器指令(5条)4.3.2.5、状态寄存器指令(9条)4.3.2.6、堆栈操作指令(4条)4.3.3、存储器与I/O操作指令(8条) 4.3.3.1、数据移动指令( 4条)4.3.3.2、程序存储器读写指令(2条) 4.3.3.3、I/O操作指令(2条)4.3.4、程序控制指令(15条)4.3.4.1、程序分支或调用指令(7条) 4.3.4.2、中断指令(3条)4.3.4.3、返回指令(2条)4.3.4.4、其它控制指令(3条)4.3.1、算术逻辑指令(28条)4.3.1.1、加法指令(4条);▲ADD▲ADDC(带进位加法指令)▲ADDS(抑制符号扩展加法指令)▲ADDT(移位次数由TREG指定的加法指令)4.3.1.2、减法指令(5条);★SUB(带移位的减法指令)★SUBB(带借位的减法指令)★SUBC(条件减法指令)★SUBS(减法指令)★SUBT(带移位的减法指令,TREG决定移位次数)4.3.1.3、乘法指令(2条);★MPY(带符号乘法指令)★MPYU(无符号乘法指令)4.3.1.4、乘加与乘减指令(6条);★MAC(累加前次积并乘)(字数2,周期3)★MAC(累加前次积并乘)★MPYA(累加-乘指令)★MPYS(减-乘指令)★SQRA(累加平方值指令)★SQRS(累减并平方指令)4.3.1.5、其它算数指令(3条);★ABS(累加器取绝对值指令)★NEG(累加器取补码指令)★NORM(累加器规格化指令)返回4.3.1.6、移位和循环移位指令(4条);▲SFL(累加器内容左移指令)▲ SFR(累加器内容右移指令)▲ROL(累加器内容循环左移指令)▲ROR(累加器内容循环右移指令)返回4.3.1.7、逻辑运算指令(4条);▲ AND(逻辑与指令)▲ OR(逻辑或指令)▲ XOR(逻辑异或指令)▲ CMPL(累加器取反指令)返回4.3.2、寄存器操作指令(35条)4.3.2.1、累加器操作指令(6条)▲LACC(装载累加器指令)▲ LACT(装载累加器)*按TREG低4位指定的次数移位▲ LACL(装载累加器低16位指令)▲ ZALR(装载累加器指令)▲ SACL(移位并存储累加器低半部)▲SACH(移位并存储累加器高半部)返回4.3.2.2、临时寄存器指令(5条)▲ LT(装载TREG指令)▲ LTA(装载TREG并累加上次乘积指令)▲LTS(装载TREG并减去上次乘积指令)▲LTD(装载TREG并累加上次乘积及数据移动指令)▲LTP(装载TREG和累加器指令)返回4.3.2.3、乘积寄存器指令(6条)▲ PAC (乘积寄存器内容载入累加器)▲ APAC(PREG与累加器相加)▲ SPAC(累加器和乘积寄存器相减)▲ LPH(装载PREG高16位指令)▲ SPL(存储PREG低16位指令)▲ SPH(存储PREG高16位指令)返回4.3.2.4、辅助寄存器指令(5条)★LAR(装载当前辅助寄存器AR)★SAR(存储辅助寄存器指令)★MAR(修改当前辅助寄存器)★SBRK(从当前辅助寄存器减去短立即数)返回4.3.2.5、状态寄存器指令(9条)★LST(装载状态寄存器)★SST(存储状态寄存器)★SETC(控制位置“1”指令)★SETC(控制位置“1”指令)★LDP(装载数据指针DP指令)★BIT(位测试指令)★BITT(测试由TREG指定bit code指令)★CMPR(比较当前辅助寄存器AR和AR0)返回4.3.2.6、堆栈操作指令(4条)★PUSH(累加器低16位进栈指令)★POP(栈顶内容弹出至累加器低16位指令)★POP(栈顶内容弹出至累加器低16位指令)★POPD(弹栈至数据存储器指令)返回4.3.3、存储器与I/O操作指令(8条)4.3.3.1、数据移动指令( 4条)▲DMOV(数据存储器内部数据移动指令)▲SPLK(存储长立即数至数据存储器指令)▲BLDD(数据存储器内部的数据块移动)▲ BLPD(从程序存储器到数据存储器的数据块传送) 4.3.3.2、程序存储器读写指令(2条)★TBLR(读程序存储器数据到数据存储器)★TBLW(写程序存储器)4.3.3.3、I/O操作指令(2条)★IN(数据输入指令)★OUT(数据输出指令)4.3.4、程序控制指令(15条)4.3.4.1、程序分支或调用指令(7条)★B(无条件转移指令)★BANZ(辅助寄存器内容不等于零转移)★CALL(无条件子程序调用指令)★BACC(按累加器内容转移指令)★CALA(由累加器指定地址的子程序调用指令)★CC(条件调用指令)4.3.4.2、中断指令(3条)★INTR(软中断指令)★TRAP(软件陷阱中断)★NMI(非屏蔽中断)4.3.4.3、返回指令(2条)★RET(无条件从子程序或中断返回)★RETC(条件返回指令)4.3.4.4、其它控制指令(3条)★RPT(重复执行下条指令)★NOP(空操作)★IDEL(暂停)返回。

DSP汇编指令学习笔记

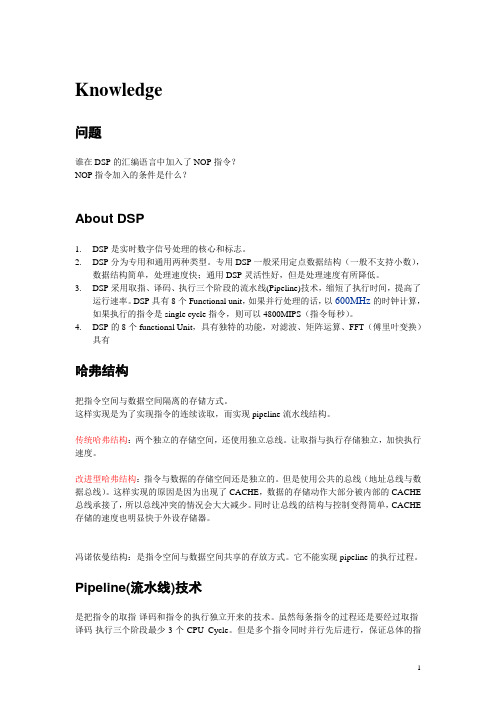

Knowledge问题谁在DSP的汇编语言中加入了NOP指令?NOP指令加入的条件是什么?About DSP1.DSP是实时数字信号处理的核心和标志。

2.DSP分为专用和通用两种类型。

专用DSP一般采用定点数据结构(一般不支持小数),数据结构简单,处理速度快;通用DSP灵活性好,但是处理速度有所降低。

3.DSP采用取指、译码、执行三个阶段的流水线(Pipeline)技术,缩短了执行时间,提高了运行速率。

DSP具有8个Functional unit,如果并行处理的话,以600MHz的时钟计算,如果执行的指令是single cycle指令,则可以4800MIPS(指令每秒)。

4.DSP的8个functional Unit,具有独特的功能,对滤波、矩阵运算、FFT(傅里叶变换)具有哈弗结构把指令空间与数据空间隔离的存储方式。

这样实现是为了实现指令的连续读取,而实现pipeline流水线结构。

传统哈弗结构:两个独立的存储空间,还使用独立总线。

让取指与执行存储独立,加快执行速度。

改进型哈弗结构:指令与数据的存储空间还是独立的。

但是使用公共的总线(地址总线与数据总线)。

这样实现的原因是因为出现了CACHE,数据的存储动作大部分被内部的CACHE 总线承接了,所以总线冲突的情况会大大减少。

同时让总线的结构与控制变得简单,CACHE 存储的速度也明显快于外设存储器。

冯诺依曼结构:是指令空间与数据空间共享的存放方式。

它不能实现pipeline的执行过程。

Pipeline(流水线)技术是把指令的取指-译码和指令的执行独立开来的技术。

虽然每条指令的过程还是要经过取指-译码-执行三个阶段最少3个CPU Cycle。

但是多个指令同时并行先后进行,保证总体的指令吞吐速率理想情况下可以保证在每个指令只要一个CPU CYCLE。

Pipeline技术必须要有哈弗结构支持,即必须把指令空间与数据空间隔离存放。

流水线阻断流水线中阻断现象也十分普遍,下面就各种阻断情况下的流水线性能进行详细分析。

第五章 DSP的汇编指令..

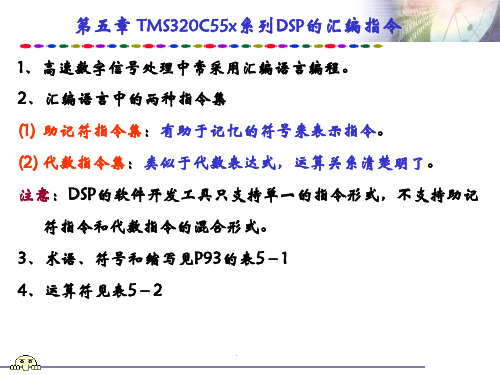

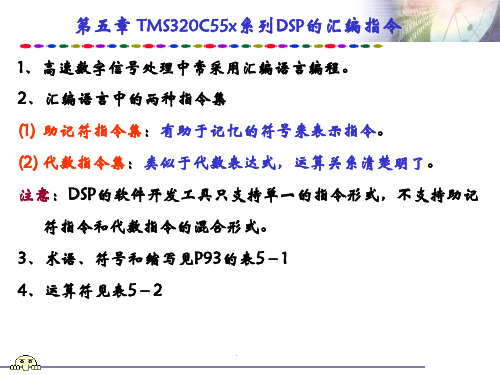

第五章 TMS320C55x系列DSP的汇编指令

(2) 用户自定义的双指令的并行

这两条指令的并行是通过用户或C编译器定义的。两条指令 同时执行两个操作,用并行符“||”区分并行执行的两条指令。 例:

MPYM *AR1+, *CDP, AC1 ;D单元的一个MAC来完成

||XOR AR2,T1

;A单元的ALU来完成

第五章 TMS320C55x系列DSP的汇编指令

1、高速数字信号处理中常采用汇编语言编程。 2、汇编语言中的两种指令集 (1) 助记符指令集:有助于记忆的符号来表示指令。 (2) 代数指令集:类似于代数表达式,运算关系清楚明了。 注意:DSP的软件开发工具只支持单一的指令形式,不支持助记

符指令和代数指令的混合形式。 3、术语、符号和缩写见P93的表5-1 4、运算符见表5-2

令执行的条件:

TCx(测试/控制标志为1) !TCx(测试/控制标志为0)

TC1&TC2 TC1&!TC2 TC1|TC2 TC1|!TC2 TC1^TC2 TC1^!TC2

!TC1&TC2 !TC1&!TC2 !TC1|TC2 !TC1|!TC2 !TC1^TC2 !TC1^!TC2

第五章 TMS320C55x系列DSP的汇编指令

4、双16比特算术指令: [(1)语法、(2)操作数、(3)状态位] 在D单元中利用其ALU的双16比特模式,同时执行(并行)两个16

比特算术运算,包括加-减、减-加、两个加和两个减运算。

例:

说明: NO:不能并行执行 3:指令的长度为3字节 1:周期为1 X:在X(执行)流水线阶段处理

D – ALU:在D单元ALU执行。 执行结果:AC0=(*AR3)+CARRY+AC1 状态位: Affected by CARRY,C54CM,M40等

dsp汇编指令系统介绍(精)

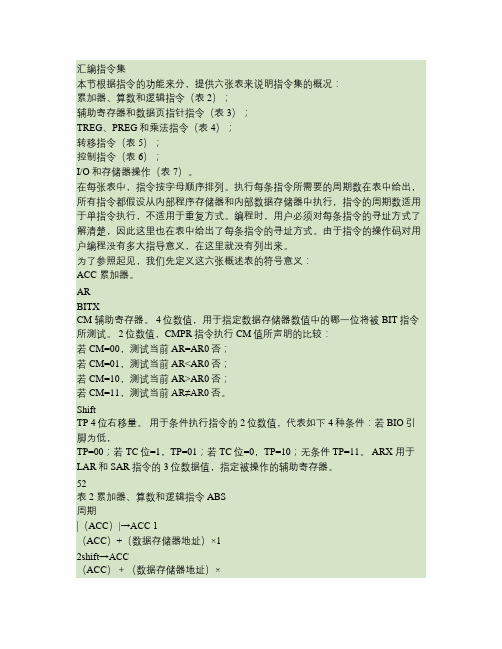

汇编指令集本节根据指令的功能来分,提供六张表来说明指令集的概况:累加器、算数和逻辑指令(表2);辅助寄存器和数据页指针指令(表3);TREG、PREG和乘法指令(表4);转移指令(表5);控制指令(表6);I/O和存储器操作(表7)。

在每张表中,指令按字母顺序排列。

执行每条指令所需要的周期数在表中给出,所有指令都假设从内部程序存储器和内部数据存储器中执行,指令的周期数适用于单指令执行,不适用于重复方式。

编程时,用户必须对每条指令的寻址方式了解清楚,因此这里也在表中给出了每条指令的寻址方式。

由于指令的操作码对用户编程没有多大指导意义,在这里就没有列出来。

为了参照起见,我们先定义这六张概述表的符号意义:ACC 累加器。

ARBITXCM 辅助寄存器。

4位数值,用于指定数据存储器数值中的哪一位将被BIT指令所测试。

2位数值,CMPR指令执行CM值所声明的比较:若CM=00,测试当前AR=AR0否;若CM=01,测试当前AR<AR0否;若CM=10,测试当前AR>AR0否;若CM=11,测试当前AR≠AR0否。

ShiftTP 4位右移量。

用于条件执行指令的2位数值,代表如下4种条件:若BIO引脚为低,TP=00;若TC位=1,TP=01;若TC位=0,TP=10;无条件TP=11。

ARX 用于LAR和SAR指令的3位数据值,指定被操作的辅助寄存器。

52表2 累加器、算数和逻辑指令 ABS周期|(ACC)|→ACC 1(ACC)+(数据存储器地址)×12shift→ACC(ACC)+(数据存储器地址)×216→ACC 1(ACC)+k→ACC 1shift(ACC)+lk×2→ACC 2指令功能(ACC)+(数据存储器地址)+(C)→ACC寻址方式直接/间接直接/间接短立即数长立即数指令说明ACC取绝对值移位时低位填0,若SXM=1,高位用符号扩展;若SXM=0,高位填0;结果存在ACC中,该指令使C=0。

第五章 DSP的汇编指令..

令执行的条件:

TCx(测试/控制标志为1) !TCx(测试/控制标志为0)

TC1&TC2 TC1&!TC2 TC1|TC2 TC1|!TC2 TC1^TC2 TC1^!TC2

!TC1&TC2 !TC1&!TC2 !TC1|TC2 !TC1|!TC2 !TC1^TC2 !TC1^!TC2

第五章 TMS320C55x系列DSP的汇编指令

4、双16比特算术指令: [(1)语法、(2)操作数、(3)状态位] 在D单元中利用其ALU的双16比特模式,同时执行(并行)两个16

比特算术运算,包括加-减、减-加、两个加和两个减运算。

例:

▪ M40=0时,D单元按32位运算模式,因此累加器溢出、进位、符号扩

展和移位操作都以第31比特为准。

▪ M40=1时,D单元按40位运算模式,因此累加器溢出,进位,符号扩

展和移位操作都以第39比特为准。

BCLR M40 ; Clear M40

BSET M40 ; Set M40

第五章 TMS320C55x系列DSP的汇编指令

第五章 TMS320C55x系列DSP的汇编指令

一、算术运算指令 用于完成加减乘除等运算,按照功能可分成以下几类:

▪ 加法指令 ▪ 减法指令:减法,条件减法,条件加/减 ▪ 乘法指令:乘法,乘加,乘减,双乘加/减 ▪ 双16比特算术指令 ▪ 比较运算指令:比较并求极值,最大/最小值,存储单元比较,寄存器比较 ▪ 移位指令:条件移位、带符号的移位。 ▪ 寄存器修改:辅助寄存器修改、堆栈指针SP修改 ▪ 隐含的并行指令 ▪ 专用指令:绝对值、归一化、有限冲激响应滤波FIR、最小均方LMS等

✓ M40=0时: 溢出位在第31位检测

dsp汇编指令

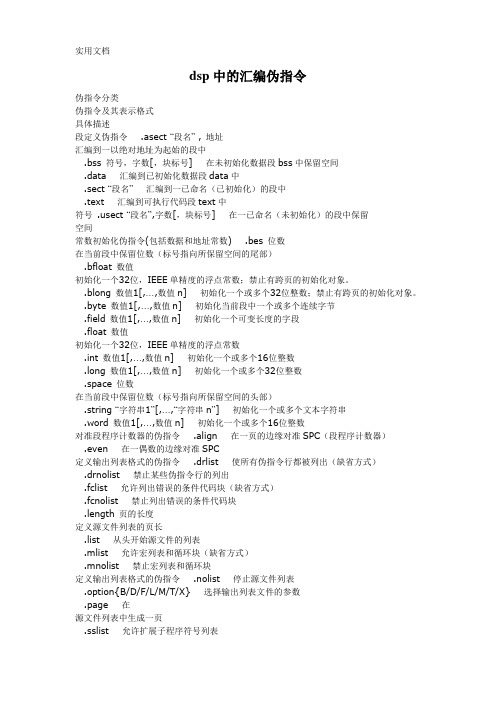

dsp中的汇编伪指令伪指令分类伪指令及其表示格式具体描述段定义伪指令 .asect “段名” , 地址汇编到一以绝对地址为起始的段中.bss 符号,字数[,块标号] 在未初始化数据段bss中保留空间.data 汇编到已初始化数据段data中.sect “段名”汇编到一已命名(已初始化)的段中.text 汇编到可执行代码段text中符号 .usect “段名”,字数[,块标号] 在一已命名(未初始化)的段中保留空间常数初始化伪指令(包括数据和地址常数) .bes 位数在当前段中保留位数(标号指向所保留空间的尾部).bfloat 数值初始化一个32位,IEEE单精度的浮点常数;禁止有跨页的初始化对象。

.blong 数值1[,…,数值n] 初始化一个或多个32位整数;禁止有跨页的初始化对象。

.byte 数值1[,…,数值n] 初始化当前段中一个或多个连续字节.field 数值1[,…,数值n] 初始化一个可变长度的字段.float 数值初始化一个32位,IEEE单精度的浮点常数.int 数值1[,…,数值n] 初始化一个或多个16位整数.long 数值1[,…,数值n] 初始化一个或多个32位整数.space 位数在当前段中保留位数(标号指向所保留空间的头部).string “字符串1”[,…,“字符串n”] 初始化一个或多个文本字符串.word 数值1[,…,数值n] 初始化一个或多个16位整数对准段程序计数器的伪指令 .align 在一页的边缘对准SPC(段程序计数器).even 在一偶数的边缘对准SPC定义输出列表格式的伪指令 .drlist 使所有伪指令行都被列出(缺省方式).drnolist 禁止某些伪指令行的列出.fclist 允许列出错误的条件代码块(缺省方式).fcnolist 禁止列出错误的条件代码块.length 页的长度定义源文件列表的页长.list 从头开始源文件的列表.mlist 允许宏列表和循环块(缺省方式).mnolist 禁止宏列表和循环块定义输出列表格式的伪指令 .nolist 停止源文件列表.option{B/D/F/L/M/T/X} 选择输出列表文件的参数.page 在源文件列表中生成一页.sslist 允许扩展子程序符号列表.ssnolist 禁止扩展子程序符号列表(缺省方式).tab 大小设置表的大小.title “字符串”在列表页头显示一个标题.width 页宽设置源文件列表的页宽外部文件定位的指伪令 .copy [“]文件名[”] 包含其他文件中的源语句.def 符号1[,…,符号n] 标明一个或多个在当前模块中定义而在其他模块中要用到的符号.global 符号1[,…,符号n] 标明一个或多个全局(外部)符号.include [“]文件名[”] 包含其他文件中的源语句.mlib [“]文件名[”] 定义宏定义库.ref符号1[,…,符号n] 标明一个或多个在另一模块中定义而在当前模块中要用到的符号条件汇编伪指令.break [确切定义的表达式] 如果条件满足,就结束.loop汇编。

DSP常用汇编语言指令简介

5. 控制指令举例

Example1:BIT0h,15 ;(DP = 6)把内存地址=300h 单元内容的最低位(BIT0)送给TC。 Example2:LDP #0h;使用立即数方式装载 数据页,也可以采用直接寻址和间接寻址方式装 载。 Example3:PUSH ;把累加器的低16位压入堆 栈。 Example4:SETC C;置进位C=1,也可以设置 以下的控制位为1或者为0,例如:CNF、INTM、 OVM、SXM、TC和XF。类似的指令还有: CLRC。

2. 工作寄存器等指令举例

Example4:ADRK #80h ;把当前工作寄存器内容 加一个立即数80h(注意立即数范围:00~FFh)。类 似的指令还有SBRK。 Example5:BANZ指令使用举例。例: MAR *, AR0 ;当前ARP=AR0 LAR AR1, #03h ;AR1内容赋值为03h LAR AR0, #60h ;AR0内容赋值为60h ZAC ; 累加器ACC清零 loop: ADD *+, AR1 ;把当前工作寄存器AR0指向 的内存单元数值加到ACC,然后AR0内容加1,当前工 作寄存器指针指向AR1 BANZ loop, *-AR0 ;判断AR0是否为0,否则程序 转到loop,同时AR0的内容减1。 南航自动化学院DSP技术应用实验 返回到第10页 室

南航自动化学院DSP技术应用实验 室

1. 累加器等指令举例

Example 1:ADD 1,1;(假设DP = 6),把 第6个数据页的第一个内存单元内容左移一 位加到累加器 Example 2:LACC *,4; (与SXM有关) Example 3:ROL;把累加器内容循环左移 Example 4:SACL *,0,AR7 ;把当前工作寄 存器指示内容左移0位送入累加器的低8位 Example 5:RPT #15 SUBC * ;累加器减去当前寄存 器指的内容,连续减16次,结果存累加器

DSP指令一览表

DSP指令一览表附录6 TMS320C54x 指令系统一览表按指令功能排列

一、算术运算指令

1. 加法指令

2. 减法指令

3. 乘法指令

4. 乘法累加/减指令

5. 双精度32位操作数指令

6. 专用指令

二、逻辑运算指令

1. 与逻辑运算指令

2. 或逻辑运算指令

3. 异或逻辑运算指令

4. 移位指令

5. 测试指令

三、程序控制指令

1. 分支转换指令

2. 调用指令

注:条件“真”,§条件“假”,※延迟指令;

3. 中断指令

4. 返回指令

注:条件“真”,§条件“假”,※延迟指令;

5. 重复指令

注:条件“真”,§条件“假”,※延迟指令;

6. 堆栈管理指令

7. 其他程序控制指令

注:条件“真”,§条件“假”,※延迟指令;

四、加载和存储指令

1. 加载指令

2. 存储指令

3. 条件存储指令

4. 并行加载和存储指令

5. 并行加载和乘法指令

6. 并行存储和加 / 减法指令

7. 并行存储和乘法指令

8. 其他加载和存储指令。

dsp汇编指令

dsp中的汇编伪指令伪指令分类伪指令及其表示格式具体描述段定义伪指令 .asect “段名” , 地址汇编到一以绝对地址为起始的段中.bss 符号,字数[,块标号] 在未初始化数据段bss中保留空间.data 汇编到已初始化数据段data中.sect “段名”汇编到一已命名(已初始化)的段中.text 汇编到可执行代码段text中符号 .usect “段名”,字数[,块标号] 在一已命名(未初始化)的段中保留空间常数初始化伪指令(包括数据和地址常数) .bes 位数在当前段中保留位数(标号指向所保留空间的尾部).bfloat 数值初始化一个32位,IEEE单精度的浮点常数;禁止有跨页的初始化对象。

.blong 数值1[,…,数值n] 初始化一个或多个32位整数;禁止有跨页的初始化对象。

.byte 数值1[,…,数值n] 初始化当前段中一个或多个连续字节.field 数值1[,…,数值n] 初始化一个可变长度的字段.float 数值初始化一个32位,IEEE单精度的浮点常数.int 数值1[,…,数值n] 初始化一个或多个16位整数.long 数值1[,…,数值n] 初始化一个或多个32位整数.space 位数在当前段中保留位数(标号指向所保留空间的头部).string “字符串1”[,…,“字符串n”] 初始化一个或多个文本字符串.word 数值1[,…,数值n] 初始化一个或多个16位整数对准段程序计数器的伪指令 .align 在一页的边缘对准SPC(段程序计数器).even 在一偶数的边缘对准SPC定义输出列表格式的伪指令 .drlist 使所有伪指令行都被列出(缺省方式).drnolist 禁止某些伪指令行的列出.fclist 允许列出错误的条件代码块(缺省方式).fcnolist 禁止列出错误的条件代码块.length 页的长度定义源文件列表的页长.list 从头开始源文件的列表.mlist 允许宏列表和循环块(缺省方式).mnolist 禁止宏列表和循环块定义输出列表格式的伪指令 .nolist 停止源文件列表.option{B/D/F/L/M/T/X} 选择输出列表文件的参数.page 在源文件列表中生成一页.sslist 允许扩展子程序符号列表.ssnolist 禁止扩展子程序符号列表(缺省方式).tab 大小设置表的大小.title “字符串”在列表页头显示一个标题.width 页宽设置源文件列表的页宽外部文件定位的指伪令 .copy [“]文件名[”] 包含其他文件中的源语句.def 符号1[,…,符号n] 标明一个或多个在当前模块中定义而在其他模块中要用到的符号.global 符号1[,…,符号n] 标明一个或多个全局(外部)符号.include [“]文件名[”] 包含其他文件中的源语句.mlib [“]文件名[”] 定义宏定义库.ref符号1[,…,符号n] 标明一个或多个在另一模块中定义而在当前模块中要用到的符号条件汇编伪指令 .break [确切定义的表达式] 如果条件满足,就结束.loop汇编。

第三章DSP汇编指令

if 0≤ index+step < BK: index = index + step

else if index + step ≥ BK: index = index + step - BK

else if index + step< 0 index = index + step + BK

只有8条指令能使用存储器映射寄存器寻址:

LDM MMR, dst MVDM dmad, MMR MVMD MMR, dmad MVMM MMRx, MMRy POPM MMR PSHM MMR STLM src, MMR STM #lk, MMR

7. 堆栈寻址

系统堆栈用来在中断和子程序期间自动存放程序计数器。 它也能用来存放额外的数据项或传递数据值。处理器使用一 个16-bit的存储器映射寄存器—堆栈指针来对堆栈寻址,它 总是指向存放在堆栈中的最后一个元素。

2、调用与中断指令

3、返回指令

4、重复指令和堆栈操作指令

四、装入和存储指令

装入和存储指令包括:

一般的装入和存储指令 条件存储指令 并行装入和存储指令 并行装入和乘法指令 并行存储和加件乘指令 混合装入和存储指令

1、一般的装入指令

2、存贮指令

3 并行装入和存储指令 4、条件存储指令

共有四条使用堆栈寻址方பைடு நூலகம்访问堆栈的指令:

PSHD 把一个数据存储器的值压入堆栈。 PSHM 把 一 个 存 储 器 映 射 寄 存 器 的 值 压 入 堆 栈 。 POPD 把一个数据存储器的值弹出堆栈。 POPM 把一个存储器映射寄存器的值弹出堆栈。

§3-2 特殊寻址方式说明

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DSP汇编指令总结

一、寻址方式:

1、立即寻址:

短立即寻址(单指令字)

长立即数寻址(双指令字)

第一指令字

第二指令字

16位常数=16384=4000h

2、直接寻址

ARU 辅助寄存器更新代码,决定当前辅助寄存器是否和如何进行增或减。

N规定是否改变ARP值,(N=0,不变)

4.3.1、算术逻辑指令(28条)

4.3.1.1、加法指令(4条);

4.3.1.2、减法指令(5条);

4.3.1.3、乘法指令(2条);

4.3.1.4、乘加与乘减指令(6条);

4.3.1.5、其它算数指令(3条);

4.3.1.6、移位和循环移位指令(4条);

4.3.1.7、逻辑运算指令(4条);

4.3.2、寄存器操作指令(35条)

4.3.2.1、累加器操作指令(6条)

4.3.2.2、临时寄存器指令(5条)

4.3.2.3、乘积寄存器指令(6条)

4.3.2.4、辅助寄存器指令(5条)

4.3.2.5、状态寄存器指令(9条)

4.3.2.6、堆栈操作指令(4条)

4.3.3、存储器与I/O操作指令(8条)4.3.3.1、数据移动指令(4条)

4.3.3.2、程序存储器读写指令(2条)

4.3.3.3、I/O操作指令(2条)

4.3.4、程序控制指令(15条)

4.3.4.1、程序分支或调用指令(7条)

4.3.4.2、中断指令(3条)

4.3.4.3、返回指令(2条)

4.3.4.4、其它控制指令(3条)

4.3.1、算术逻辑指令(28条)

4.3.1.1、加法指令(4条);

▲ADD

▲ADDC(带进位加法指令)

▲ADDS(抑制符号扩展加法指令)

▲ADDT(移位次数由TREG指定的加法指令)

4.3.1.2、减法指令(5条);

★SUB(带移位的减法指令)

★SUBB(带借位的减法指令)

★SUBC(条件减法指令)

★SUBS(减法指令)

★SUBT(带移位的减法指令,TREG决定移位次数)4.3.1.3、乘法指令(2条);

★MPY(带符号乘法指令)

★MPYU(无符号乘法指令)

4.3.1.4、乘加与乘减指令(6条);

★MAC(累加前次积并乘)(字数2,周期3)

★MAC(累加前次积并乘)

★MPYA(累加-乘指令)

★MPYS(减-乘指令)

★SQRA(累加平方值指令)

★SQRS(累减并平方指令)

4.3.1.5、其它算数指令(3条);

★ABS(累加器取绝对值指令)

★NEG(累加器取补码指令)

★NORM(累加器规格化指令)

返回

4.3.1.6、移位和循环移位指令(4条);

▲ SFL(累加器内容左移指令)

▲ SFR(累加器内容右移指令)

▲ROL(累加器内容循环左移指令)

▲ROR(累加器内容循环右移指令)

返回

4.3.1.7、逻辑运算指令(4条);

▲ AND(逻辑与指令)

▲ OR(逻辑或指令)

▲ XOR(逻辑异或指令)

▲ CMPL(累加器取反指令)

返回

4.3.2、寄存器操作指令(35条)

4.3.2.1、累加器操作指令(6条)

▲ LACC(装载累加器指令)

▲ LACT(装载累加器)*按TREG低4位指定的次数移位▲ LACL(装载累加器低16位指令)

▲ ZALR(装载累加器指令)

▲ SACL(移位并存储累加器低半部)

▲ SACH(移位并存储累加器高半部)

返回

4.3.2.2、临时寄存器指令(5条)

▲ LT(装载TREG指令)

▲ LTA(装载TREG并累加上次乘积指令)

▲ LTS (装载TREG并减去上次乘积指令)

▲ L TD(装载TREG并累加上次乘积及数据移动指令)▲LTP(装载TREG和累加器指令)

返回

4.3.2.3、乘积寄存器指令(6条)

▲ PAC (乘积寄存器内容载入累加器)

▲ APAC (PREG与累加器相加)

▲ SPAC(累加器和乘积寄存器相减)

▲ LPH(装载PREG高16位指令)

▲ SPL(存储PREG低16位指令)

▲ SPH(存储PREG高16位指令)

返回

4.3.2.4、辅助寄存器指令(5条)

★LAR(装载当前辅助寄存器AR)

★SAR(存储辅助寄存器指令)

★MAR(修改当前辅助寄存器)

★SBRK(从当前辅助寄存器减去短立即数)

返回

4.3.2.5、状态寄存器指令(9条)

★LST(装载状态寄存器)

★SST(存储状态寄存器)

★SETC(控制位置“1”指令)

★SETC(控制位置“1”指令)

★LDP(装载数据指针DP指令)

★BIT(位测试指令)

★BITT(测试由TREG指定bit code指令)

★CMPR(比较当前辅助寄存器AR和AR0)

返回

4.3.2.6、堆栈操作指令(4条)

★PUSH(累加器低16位进栈指令)

★POP(栈顶内容弹出至累加器低16位指令)

★POP(栈顶内容弹出至累加器低16位指令)

★POPD(弹栈至数据存储器指令)

返回

4.3.3、存储器与I/O操作指令(8条)

4.3.3.1、数据移动指令(4条)

▲DMOV(数据存储器内部数据移动指令)

▲SPLK(存储长立即数至数据存储器指令)

▲BLDD(数据存储器内部的数据块移动)

▲ BLPD(从程序存储器到数据存储器的数据块传送)4.3.3.2、程序存储器读写指令(2条)

★TBLR(读程序存储器数据到数据存储器)

★TBLW(写程序存储器)

4.3.3.3、I/O操作指令(2条)

★IN(数据输入指令)

★OUT(数据输出指令)

4.3.4、程序控制指令(15条)

4.3.4.1、程序分支或调用指令(7条)

★B(无条件转移指令)

★BANZ(辅助寄存器内容不等于零转移)

★CALL(无条件子程序调用指令)

★BACC(按累加器内容转移指令)

★CALA(由累加器指定地址的子程序调用指令)

★CC(条件调用指令)

4.3.4.2、中断指令(3条)

★INTR(软中断指令)

★TRAP(软件陷阱中断)

★NMI(非屏蔽中断)

4.3.4.3、返回指令(2条)

★RET(无条件从子程序或中断返回)

★RETC(条件返回指令)

4.3.4.4、其它控制指令(3条)

★RPT(重复执行下条指令)

★NOP(空操作)

★IDEL(暂停)

返回。