19 IR_IRMCK F171-灵活易用的电机控制芯片

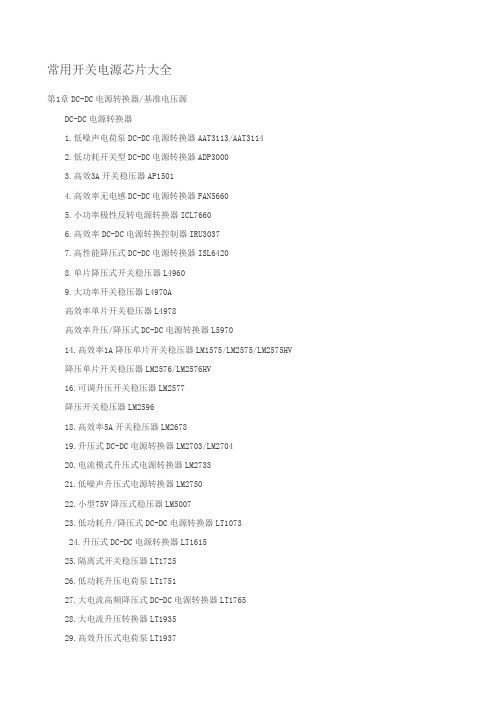

常用开关电源芯片大全

常用开关电源芯片大全第1章DC-DC电源转换器/基准电压源DC-DC电源转换器1.低噪声电荷泵DC-DC电源转换器AAT3113/AAT31142.低功耗开关型DC-DC电源转换器ADP30003.高效3A开关稳压器AP15014.高效率无电感DC-DC电源转换器FAN56605.小功率极性反转电源转换器ICL76606.高效率DC-DC电源转换控制器IRU30377.高性能降压式DC-DC电源转换器ISL64208.单片降压式开关稳压器L49609.大功率开关稳压器L4970A高效率单片开关稳压器L4978高效率升压/降压式DC-DC电源转换器L597014.高效率1A降压单片开关稳压器LM1575/LM2575/LM2575HV降压单片开关稳压器LM2576/LM2576HV16.可调升压开关稳压器LM2577降压开关稳压器LM259618.高效率5A开关稳压器LM267819.升压式DC-DC电源转换器LM2703/LM270420.电流模式升压式电源转换器LM273321.低噪声升压式电源转换器LM275022.小型75V降压式稳压器LM500723.低功耗升/降压式DC-DC电源转换器LT107324.升压式DC-DC电源转换器LT161525.隔离式开关稳压器LT172526.低功耗升压电荷泵LT175127.大电流高频降压式DC-DC电源转换器LT176528.大电流升压转换器LT193529.高效升压式电荷泵LT193730.高压输入降压式电源转换器LT195632.高压升/降压式电源转换器LT343333.单片3A升压式DC-DC电源转换器LT343634.通用升压式DC-DC电源转换器LT346035.高效率低功耗升压式电源转换器LT346437.大电流高效率升压式DC-DC电源转换器LT378238.微型低功耗电源转换器LTC175440.低噪声高效率降压式电荷泵LTC191141.低噪声电荷泵LTC3200/LTC3200-542.无电感的降压式DC-DC电源转换器LTC325143.双输出/低噪声/降压式电荷泵LTC325244.同步整流/升压式DC-DC电源转换器LTC340145.低功耗同步整流升压式DC-DC电源转换器LTC340246.同步整流降压式DC-DC电源转换器LTC340547.双路同步降压式DC-DC电源转换器LTC340748.高效率同步降压式DC-DC电源转换器LTC341649.微型2A升压式DC-DC电源转换器LTC3426两相电流升压式DC-DC电源转换器LTC342851.单电感升/降压式DC-DC电源转换器LTC344052.大电流升/降压式DC-DC电源转换器LTC344254.直流同步降压式DC-DC电源转换器LTC370355.双输出降压式同步DC-DC电源转换控制器LTC373656.降压式同步DC-DC电源转换控制器LTC377057.双2相DC-DC电源同步控制器LTC380258.高性能升压式DC-DC电源转换器MAX1513/MAX151459.精简型升压式DC-DC电源转换器MAX1522/MAX1523/MAX152460.高效率40V升压式DC-DC电源转换器MAX1553/MAX155461.高效率升压式LED电压调节器MAX1561/MAX159962.高效率5路输出DC-DC电源转换器MAX156563.双输出升压式DC-DC电源转换器MAX1582/MAX1582Y64.驱动白光LED的升压式DC-DC电源转换器MAX158365.高效率升压式DC-DC电源转换器MAX1642/MAX1643降压式开关稳压器MAX164467.高效率升压式DC-DC电源转换器MAX1674/MAX1675/MAX167668.高效率双输出DC-DC电源转换器MAX167769.低噪声1A降压式DC-DC电源转换器MAX1684/MAX168570.高效率升压式DC-DC电源转换器MAX169871.高效率双输出降压式DC-DC电源转换器MAX171572.小体积升压式DC-DC电源转换器MAX1722/MAX1723/MAX172473.输出电流为50mA的降压式电荷泵MAX173074.升/降压式电荷泵MAX175975.高效率多路输出DC-DC电源转换器MAX1800同步整流降压式稳压型MAX1830/MAX183177.双输出开关式LCD电源控制器MAX187878.电流模式升压式DC-DC电源转换器MAX189679.具有复位功能的升压式DC-DC电源转换器MAX194780.高效率PWM降压式稳压器MAX1992/MAX199381.大电流输出升压式DC-DC电源转换器MAX61882.低功耗升压或降压式DC-DC电源转换器MAX629升压式DC-DC电源转换器MAX668/MAX66984.大电流PWM降压式开关稳压器MAX724/MAX72685.高效率升压式DC-DC电源转换器MAX756/MAX75786.高效率大电流DC-DC电源转换器MAX761/MAX76287.隔离式DC-DC电源转换器MAX8515/MAX8515A88.高性能24V升压式DC-DC电源转换器MAX872789.升/降压式DC-DC电源转换器MC33063A/MC34063A升压/降压/反向DC-DC电源转换器MC33167/MC3416791.低噪声无电感电荷泵MCP1252/MCP125392.高频脉宽调制降压稳压器MIC220393.大功率DC-DC升压电源转换器MIC229594.单片微型高压开关稳压器NCP1030/NCP103195.低功耗升压式DC-DC电源转换器NCP1400A96.高压DC-DC电源转换器NCP140397.单片微功率高频升压式DC-DC电源转换器NCP141098.同步整流PFM步进式DC-DC电源转换器NCP142199.高效率大电流开关电压调整器NCP1442/NCP1443/NCP1444/NCP1445 100.新型双模式开关稳压器NCP1501101.高效率大电流输出DC-DC电源转换器NCP1550102.同步降压式DC-DC电源转换器NCP1570103.高效率升压式DC-DC电源转换器NCP5008/NCP5009104.大电流高速稳压器RT9173/RT9173A105.高效率升压式DC-DC电源转换器RT9262/RT9262A106.升压式DC-DC电源转换器SP6644/SP6645107.低功耗升压式DC-DC电源转换器SP6691108.新型高效率DC-DC电源转换器TPS54350109.无电感降压式电荷泵TPS6050x110.高效率升压式电源转换器TPS6101x恒流白色LED驱动器TPS61042112.具有LDO输出的升压式DC-DC电源转换器TPS6112x113.低噪声同步降压式DC-DC电源转换器TPS6200x114.三路高效率大功率DC-DC电源转换器TPS75003115.高效率DC-DC电源转换器UCC39421/UCC39422控制升压式DC-DC电源转换器XC6371117.白光LED驱动专用DC-DC电源转换器XC9116同步整流降压式DC-DC电源转换器XC9215/XC9216/XC9217119.稳压输出电荷泵XC9801/XC9802120.高效率升压式电源转换器ZXLB1600线性/低压差稳压器121.具有可关断功能的多端稳压器BAXXX122.高压线性稳压器HIP5600123.多路输出稳压器KA7630/KA7631124.三端低压差稳压器LM2937125.可调输出低压差稳压器LM2991126.三端可调稳压器LM117/LM317127.低压降CMOS500mA线性稳压器LP38691/LP38693128.输入电压从12V到450V的可调线性稳压器LR8 非常低压降稳压器(VLDO)LTC3025130.大电流低压差线性稳压器LX8610负输出低压差线性稳压器MAX1735低压差线性稳压器MAX8875133.带开关控制的低压差稳压器MC33375134.带有线性调节器的稳压器MC33998136.低静态电流低压差稳压器NCP562/NCP563137.具有使能控制功能的多端稳压器PQxx138.五端可调稳压器SI-3025B/SI-3157B低压差线性稳压器SPX2975140.五端线性稳压器STR20xx141.五端线性稳压器STR90xx142.具有复位信号输出的双路输出稳压器TDA8133143.具有复位信号输出的双路输出稳压器TDA8138/TDA8138A 144.带线性稳压器的升压式电源转换器TPS6110x145.低功耗50mA低压降线性稳压器TPS760xx146.高输入电压低压差线性稳压器XC6202147.高速低压差线性稳压器XC6204148.高速低压差线性稳压器XC6209F149.双路高速低压差线性稳压器XC6401基准电压源150.新型XFET基准电压源ADR290/ADR291/ADR292/ADR293 151.低功耗低压差大输出电流基准电压源MAX610x152.低功耗基准电压源MAX6120155.低功耗精密低压降基准电压源REF30xx/REF31xx156.精密基准电压源TL431/KA431/TLV431A第2章AC-DC转换器及控制器1.厚膜开关电源控制器DP104C2.厚膜开关电源控制器DP308P系列高电压功率转换控制器DPA423/DPA424/DPA425/DPA4264.电流型开关电源控制器FA13842/FA13843/FA13844/FA138455.开关电源控制器FA5310/FA5311开关电源控制器FAN75567.绿色环保的PWM开关电源控制器FAN7601型开关电源控制器FS6M07652R9.开关电源功率转换器FS6Sxx10.降压型单片AC-DC转换器HV-2405E11.新型反激准谐振变换控制器ICE1QS01电源功率转换器KA1M088013.开关电源功率转换器KA2S0680/KA2S088014.电流型开关电源控制器KA38xx型开关电源功率转换器KA5H0165R型开关电源功率转换器KA5Qxx型开关电源功率转换器KA5Sxx18.电流型高速PWM控制器L499019.具有待机功能的PWM初级控制器L599120.低功耗离线式开关电源控制器L6590SWITCH TN系列电源功率转换器LNK304/LNK305/LNK306SWITCH系列电源功率转换器LNK500/LNK501/LNK52023.离线式开关电源控制器M51995A电源控制器M62281P/M62281FP25.高频率电流模式PWM控制器MAX5021/MAX502226.新型PWM开关电源控制器MC4460427.电流模式开关电源控制器MC4460528.低功耗开关电源控制器MC4460829.具有PFC功能的PWM电源控制器ML482430.液晶显示器背光灯电源控制器ML487631.离线式电流模式控制器NCP120032.电流模式脉宽调制控制器NCP120533.准谐振式PWM控制器NCP120734.低成本离线式开关电源控制电路NCP121535.低待机能耗开关电源PWM控制器NCP1230系列自动电压切换控制开关STR8xxxx37.大功率厚膜开关电源功率转换器STR-F665438.大功率厚膜开关电源功率转换器STR-G865639.开关电源功率转换器STR-M6511/STR-M652940.离线式开关电源功率转换器STR-S5703/STR-S5707/STR-S570841.离线式开关电源功率转换器STR-S6401/STR-S6401F/STR-S6411/STR-S6411F 442.开关电源功率转换器STR-S651343.离线式开关电源功率转换器TC33369~TC3337444.高性能PFC与PWM组合控制集成电路TDA16846/TDA1684745.新型开关电源控制器TDA1685046.“绿色”电源控制器TEA150447.第二代“绿色”电源控制器TEA150748.新型低功耗“绿色”电源控制器TEA153349.开关电源控制器TL494/KA7500/MB3759SwitchⅠ系列功率转换器TNY253、TNY254、TNY255SwitchⅡ系列功率转换器TNY264P~TNY268GSwitch(Ⅱ)系列离线式功率转换器TOP209~TOP227Switch-FX系列功率转换器TOP232/TOP233/TOP234Switch-GX系列功率转换器TOP242~TOP25055.开关电源控制器UCX84X56.离线式开关电源功率转换器VIPer12AS/VIPer12ADIP57.新一代高度集成离线式开关电源功率转换器VIPer53第3章功率因数校正控制/节能灯电源控制器1.电子镇流器专用驱动电路BL83012.零电压开关功率因数控制器FAN48223.功率因数校正控制器FAN75274.高电压型EL背光驱动器HV826场致发光背光驱动器IMP525/IMP5606.高电压型EL背光驱动器/反相器IMP8037.电子镇流器自振荡半桥驱动器IR21568.单片荧光灯镇流器IR21579.调光电子镇流器自振荡半桥驱动器IR215910.卤素灯电子变压器智能控制电路IR216111.具有功率因数校正电路的镇流器电路IR216612.单片荧光灯镇流器IR216713.自适应电子镇流器控制器IR252014.电子镇流器专用控制器KA754115.功率因数校正控制器L656116.过渡模式功率因数校正控制器L656217.集成背景光控制器MAX8709/MAX8709A18.功率因数校正控制器MC33262/MC3426219.固定频率电流模式功率因数校正控制器NCP1653场致发光灯高压驱动器SP440321.功率因数校正控制器TDA4862/TDA486322.有源功率因数校正控制器UC385423.高频自振荡节能灯驱动器电路VK05CFL24.大功率高频自振荡节能灯驱动器电路VK06TL第4章充电控制器1.多功能锂电池线性充电控制器AAT36802.可编程快速电池充电控制器BQ20003.可进行充电速率补偿的锂电池充电管理器BQ20574.锂电池充电管理电路BQ2400x5.单片锂电池线性充电控制器BQ2401x接口单节锂电池充电控制器BQ2402x同步开关模式锂电池充电控制器BQ241008.集成PWM开关控制器的快速充电管理器BQ29549.具有电池电量计量功能的充电控制器DS277010.锂电池充电控制器FAN7563/FAN7564线性锂/锂聚合物电池充电控制器ISL629212.锂电池充电控制器LA5621M/LA5621V恒流/恒压电池充电控制器LT176915.线性锂电池充电控制器LTC173216.带热调节功能的1A线性锂电池充电控制器LTC173317.线性锂电池充电控制器LTC173418.新型开关电源充电控制器LTC198019.开关模式锂电池充电控制器LTC4002锂电池充电器LTC400621.多用途恒压/恒流充电控制器LTC400823.可由USB端口供电的锂电池充电控制器LTC405324.小型150mA锂电池充电控制器LTC405425.线性锂电池充电控制器LTC405826.单节锂电池线性充电控制器LTC405927.独立线性锂电池充电控制器LTC406128.镍镉/镍氢电池充电控制器M62256FP29.大电流锂/镍镉/镍氢电池充电控制器MAX150130.锂电池线性充电控制器MAX150731.双输入单节锂电池充电控制器MAX1551/MAX155532.单节锂电池充电控制器MAX167933.小体积锂电池充电控制器MAX1736接口单节锂电池充电控制器MAX181135.多节锂电池充电控制器MAX187336.双路输入锂电池充电控制器MAX187437.单节锂电池线性充电控制器MAX189838.低成本/多种电池充电控制器MAX190839.开关模式单节锂电池充电控制器MAX1925/MAX192640.快速镍镉/镍氢充电控制器MAX2003A/MAX200341.可编程快速充电控制器MAX712/MAX71342.开关式锂电池充电控制器MAX74543.多功能低成本充电控制器MAX846A44.具有温度调节功能的单节锂电池充电控制器MAX8600/MAX860145.锂电池充电控制器MCP73826/MCP73827/MCP7382846.高精度恒压/恒流充电器控制器MCP73841/MCP73842/MCP73843/MCP73844 647.锂电池充电控制器MCP73861/MCP7386248.单节锂电池充电控制器MIC7905049.单节锂电池充电控制器NCP180050.高精度线性锂电池充电控制器VM7205。

IRMCK171

PD-60361IRMCK171 High Performance Sensorless Motor Control ICFeaturesMCE TM (Flexible Motion Control Engine) - Dedicated computation engine for high efficiency sinusoidal sensorless motor controlBuilt-in hardware peripheral for single or two shunt current feedback reconstruction and analog circuitsSupports induction machine and both interior and surface permanent magnet motor sensorlesscontrolLoss minimization Space Vector PWMTwo-channel analog output (PWM)Embedded 8-bit high speed microcontroller (8051) for flexible I/O and man-machine controlJTAG programming port for emulation/debugger Serial communication interface (UART)I2C/SPI serial interfaceThree general purpose timers/countersTwo special timers: analog watchdog timer, periodic timer, capture timerInternal 32Kbyte OTP ROM5V tolerant I/O3.3V single supply Product SummaryMaximum clock input (f crystal) 60MHzMaximum Internal clock (SYSCLK) 128MHzMaximum 8051 clock (8051CLK) 32MHzSensorless control computation time (max.) 48 μsecMCE TM computation data range 16 bit signed8051 OTP Program ROM (min.) 20KB805/MCE Data RAM 2KBMCE Program RAM12KBPWM carrier frequency 20 bits/ SYSCLKA/D input channels 7A/D converter resolution 12 bitsA/D converter conversion speed 2 μsecAnalog output (PWM) resolution 8 bitsUART baud rate (typ) 57.6K bpsNumber of I/O (max) 10Package QFP48 Maximum 3.3V operating current60mADescriptionIRMCK171 is a high performance One Time Programmable ROM based motion control IC designed primarily for appliance applications. IRMCK171 is designed to achieve low cost yet high performance control solutions for advanced inverterized appliance motor control. IRMCK171 contains two computation engines. One is the Flexible Motion Control Engine (MCE TM) for sensorless control of permanent magnet motors or induction motors; the other is an 8-bit high-speed microcontroller (8051). Both computation engines are integrated into one monolithic chip. The MCE TM contains a collection of control elements implemented in a dedicated computation engine such as Vector rotator, Arc-Tangent, Multiply/Divide, Low loss SVPWM and Motor current sensing. The user can program a motion control algorithm by connecting Control elements using a graphic compiler. Key components of the complex sensorless control algorithms, such as the Angle Estimator, are provided as complete pre-defined control blocks. A unique analog/digital circuit and algorithm to fully support single shunt current reconstruction is also provided. The 8051 microcontroller performs 2-cycle instruction execution (16.5MIPS at 33MHz 8051CLK). The MCE and 8051 microcontroller communicate via dual port RAM for signal monitoring and command input. An advanced graphic compiler for the MCE TM is seamlessly integrated into the MATLAB/Simulink environment, while third party JTAG-based emulator tools are supported for 8051 software development including an OTP programmer. IRMCK171 comes in a 48 pin QFP package.1 Overview (5)2 Pinout (6)3 IRMCK171 Block Diagram and Main Functions (7)connection and Pin function (9)4 ApplicationInterface Group (10)Peripheral4.1 8051Peripheral Interface Group (11)4.2 MotionInterface Group (11)4.3 AnalogInterface Group (11)4.4 Power4.5 TestInterface Group (11)5 DCCharacteristics (12)Maximum Ratings (12)5.1 Absolute5.2 System Clock Frequency and Power Consumption (12)5.3 Digital I/O DC Characteristics (13)5.4 PLL and Oscillator DC characteristics (14)5.5 Analog I/O (IFB+,IFB-,IFBO, AIN5+,AIN5-,AIN5O) DC Characteristics (14)5.6 Under Voltage Lockout DC characteristics (15)DC characteristics (15)comparator5.7 Itrip5.8 CMEXT and AREF Characteristics (15)Characteristics (16)6 AC6.1 Digital PLL AC Characteristics (16)6.2 Analog to Digital Converter AC Characteristics (17)6.3 Op amp AC Characteristics (18)6.4 SYNC to SVPWM and A/D Conversion AC Timing (19)6.5 GATEKILLSVPWM AC Timing (20)to6.6 ItripAC Timing (20)6.7 InterruptAC Timing (21)6.8 I2C AC Timing (21)6.9 SPIAC Timing (22)AC Timing (24)6.10 UARTInput AC Timing (25)6.11 CAPTUREProgramming Timing (26)6.12 OTPAC Timing (27)6.13 JTAGStructure (28)7 I/OList (31)8 PinDimensions (33)9 PackageInformation (34)Marking10 PartTable 1 Absolute Maximum Ratings (12)Table 2 System Clock Frequency (12)Table 3 Digital I/O DC Characteristics (13)Table 4 PLL DC Characteristics (14)Table 5 Analog I/O DC Characteristics (14)Table 6 UVcc DC Characteristics (15)Table 7 Itrip DC Characteristics (15)Table 8 CMEXT and AREF DC Characteristics (15)Table 9 PLL AC Characteristics (16)Table 10 A/D Converter AC Characteristics (17)Table 11 Current Sensing OP Amp AC Characteristics (18)Table 12 SYNC AC Characteristics (19)Table 13 GATEKILL to SVPWM AC Timing (20)Table 14 Itrip AC Timing (20)Table 15 Interrupt AC Timing (21)Table 16 I2C AC Timing (21)Table 17 SPI Write AC Timing (22)Table 18 SPI Read AC Timing (23)Table 19 UART AC Timing (24)Table 20 CAPTURE AC Timing (25)Table 21 OTP Programming Timing (26)Table 22 JTAG AC Timing (27)Table 23 Pin List (32)Figure 1 Typical Application Block Diagram Using IRMCK171 (5)Figure 2 Pinout of IRMCK171 (6)Figure 3 Crystal circuit example (16)Figure 4 Voltage droop and S/H hold time (17)Figure 5 A capacitor of 47pF is recommended at the output pin of all op amps (18)Figure 6 SYNC timing (19)Figure 7 Gatekill timing (20)Figure 8 ITRIP timing (20)Figure 9 Interrupt timing (21)Figure 10 I2C Timing (21)Figure 11 SPI write timing (22)Figure 12 SPI read timing (23)Figure 13 UART timing (24)Figure 14 CAPTURE timing (25)Figure 15 OTP programming timing (26)Figure 16 JTAG timing (27)Figure 17 PWMUL/PWMUH/PWMVL/PWMVH/PWMWL/PWMWH output (28)Figure 18 All digital I/O except motor PWM output (28)Figure 19 RESET, GATEKILL I/O (29)Figure 20 Analog input (29)Figure 21 Analog operational amplifier output and AREF I/O structure (29)Figure 22 VPP programming pin I/O structure (30)Figure 23 VSS and AVSS pin structure (30)Figure 24 VDD1 and VDDCAP pin structure (30)Figure 25 XTAL0/XTAL1 pins structure (30)1 OverviewIRMCK171 is a new generation International Rectifier integrated circuit device primarily designed as a one-chip solution for complete inverter controlled appliance motor control applications. Unlike a traditional microcontroller or DSP, the IRMCK171 provides a built-in closed loop sensorless control algorithm using the unique flexible Motion Control Engine (MCE TM) for permanent magnet motors as well as induction motors. The MCE TM consists of a collection of control elements, motion peripherals, a dedicated motion control sequencer and dual port RAM to map internal signal nodes. IRMCK171 also employs a unique single shunt current reconstruction circuit in addition to two leg shunt current sensing circuit to eliminate additional analog/digital circuitry and enables a direct shunt resistor interface to the IC. Motion control programming is achieved using a dedicated graphical compiler integrated into the MATLAB/Simulink TM development environment. Sequencing, user interface, host communication, and upper layer control tasks can be implemented in the 8051 high-speed 8-bit microcontroller. The 8051 microcontroller is equipped with a JTAG port to facilitate emulation and debugging tools. Figure 1 shows a typical application schematic using the IRMCK171.IRMCK171 contains 32K bytes of OTP program ROM, The IRMCF171 contains 64K bytes of Flash RAM and intended for development purposes only while the IRMCK171 is intended for volume production. Both the development and ROM versions come in a 48-pin QFP package with identical pin configuration tofacilitate PC board layout and transition to mass production.Figure 1 Typical Application Block Diagram Using IRMCK1712 PinoutPin out shown is based on QFP48 pin package.XTAL0XTAL1P 1.1/R X DP 1.2/T X DVDD1VSS VDDCAP P1.3/SYNC/SCKP1.4/CAPP3.2/INT0VSS VDDCAP AVSS A R E FP 2.7/A O P W M 1P W M U H PWMVH PWMWH PWMUL PWMVL PWMWL G A T E K I L LI F B OI F B +I F B -R E S E TV P P /P 1.5T C KT D I /P 5.1T D O /P 5.3T M S /P 5.2SDA/CS0SCL/SO-SI A I N 2C M E X TP2.0/NMI P1.0/T2P 3.0/C S 1A I N 3A I N 4VDD1A I N 1A I N 0AIN5+A I N 5-AIN5O P 3.3/I N T 1P3.1/AOPWM2Figure 2 Pinout of IRMCK1713 IRMCK171 Block Diagram and Main FunctionsIRMCK171 block diagram is shown in Figure 3.analoginputFigure 3 IRMCK171 Block DiagramIRMCK171 contains the following functions for sensorless AC motor control applications:•Motion Control Engine (MCE TM)o Sensorless FOC (complete sensorless field oriented control)o Proportional plus Integral blocko Low pass filtero Differentiator and lag (high pass filter)o Rampo Limito Angle estimate (sensorless control)o Inverse Clark transformationo Vector rotatoro Bit latcho Peak detecto Transitiono Multiply-divide (signed and unsigned)IRMCK171 Array o Divide (signed and unsigned)o Addero Subtractoro Comparatoro Countero Accumulatoro Switcho Shifto ATAN (arc tangent)o Function block (any curve fitting, nonlinear function)o16 bit wide Logic operations (AND, OR, XOR, NOT, NEGATE)o MCE TM program memory and dual port RAM (max 12K+2k byte)o MCE TM control sequencer• 8051 microcontrollero Two 16 bit timer/counterso One 16 bit periodic timero One 16 bit watchdog timero One 16 bit capture timero Up to 24 discrete I/Oso Six-channel 12 bit A/DBuffered (current sensing) one channel (0 – 1.2V input)Unbuffered seven channels (0 – 1.2V input)o JTAG port (4 pins)o Up to three channels of analog output (8 bit PWM)o UARTo I2C/SPI porto32K byte OTP program ROMo2K byte data RAMIRMCK171 4 Application connection and Pin functionSystemClockFigure 4 IRMCK171 Connection DiagramIRMCK171 Array4.1 8051 Peripheral Interface GroupUART InterfaceP1.2/TXD Output,Transmit data from IRMCK171P1.1/RXD Input, Receive data to IRMCK171Discrete I/O InterfaceP1.0/T2 Input/output port 1.0, can be configured as Timer/Counter 2 inputP1.1/RXD Input/output port 1.1, can be configured as RXD inputP1.2/TXD Input/output port 1.2, can be configured as TXD outputP1.3/SYNC/SCK Input/output port 1.3, can be configured as SYNC output or SPI clock output,needs to be pulled up to VDD1 in order to boot from I2C EEPROM P1.4/CAP Input/output port 1.4, can be configured as Capture Timer inputP1.5/VPP Input/output port 1.5, or OTP programming voltageP2.0/NMI Input/output port 2.0, can be configured as non-maskable interrupt inputP3.2/INT0 Input/output port 3.2, can be configured as INT0 inputP2.7/AOPWM1 Input/output port 2.7, can be configured as AOPWM1 outputP3.0/INT2/CS1 Input/output port 3.0, can be configured as INT2 input or SPI chip select 1P3.1/AOPWM2 Input/output port 3.1, can be configured as AOPWM2 outputP3.3/INT1 Input/output port 3.3, can be configured as INT1 inputP5.1/TDI Input port 5.1, configured as JTAG port by defaultP5.2/TMS Input port 5.2, configured as JTAG port by defaultAnalog Output InterfaceP2.7/AOPWM1 Input/output, can be configured as 8-bit PWM output 1 with programmablecarrier frequencyP3.1/AOPWM2 Input/output, can be configured as 8-bit PWM output 2 with programmablecarrier frequencyCrystal InterfaceXTAL0 Input, connected to crystalXTAL1 Output, connected to crystalReset InterfaceRESET Input and Output, system reset, doesn’t require external RC time constantI2C InterfaceI2C clock output, or SPI dataSCL/SO-SI Output,I2C Data line or SPI chip select 0SDA/CS0 Input/output,I2C/SPI InterfaceSCL/SO-SI Output,I2C clock output, or SPI dataSDA/CS0 Input/output,I2C data line or SPI chip select 0P1.3/SYNC/SCK Input/output port 1.3, can be configured as SYNC output or SPI clock output,needs to be pulled up to VDD1 in order to boot from I2C EEPROMP3.0/INT2/CS1 Input/output port 3.0, can be configured as INT2 input or SPI chip select 14.2 Motion Peripheral Interface GroupPWMPWMUH Output, PWM phase U high side gate signal, internally pulled down by 58kΩPWMUL Output, PWM phase U low side gate signal, internally pulled down by 58kΩPWMVH Output, PWM phase V high side gate signal, internally pulled down by 58kΩPWMVL Output, PWM phase V low side gate signal, internally pulled down by 58kΩPWMWH Output, PWM phase W high side gate signal, internally pulled down by 58kΩPWMWL Output, PWM phase W low side gate signal, internally pulled down by 58kΩFaultGATEKILL Input, upon assertion, this negates all six PWM signals, active low, internallypulled up by 70kΩ4.3 Analog Interface GroupAVSS Analog power return, (analog internal 1.8V power is shared with VDDCAP) AREF 0.6V buffered outputCMEXT Unbuffered 0.6V, input to the AREF buffer, capacitor needs to be connected.IFB+ Input, Operational amplifier positive input for shunt resistor current sensing IFB- Input, Operational amplifier negative input for shunt resistor current sensing IFBO Output, Operational amplifier output for shunt resistor current sensingAIN0 Input, Analog input channel 0 (0 – 1.2V), typically configured for DC bus voltage inputAIN1 Input, Analog input channel 1 (0 – 1.2V), needs to be pulled down to AVSS ifunusedAIN2 Input, Analog input channel 2 (0 – 1.2V), needs to be pulled down to AVSS ifunusedAIN3 Input, Analog input channel 3 (0 – 1.2V), needs to be pulled down to AVSS ifunusedAIN4 Input, Analog input channel 4 (0 – 1.2V), needs to be pulled down to AVSS ifunusedAIN5+ Input, Operational amplifier positive input for shunt resistor current sensing AIN5- Input, Operational amplifier negative input for shunt resistor current sensing AIN5O Output, Operational amplifier output for AIN5 output, there is a singlesample/hold circuit on the output4.4 Power Interface GroupVDD1 Digital power (3.3V)VDDCAP Internal 1.8V output, requires capacitors to the pin. Shared with analog powerpad internallycommonVSS Digital4.5 Test Interface GroupP5.2/TMS JTAG test mode input or input/output digital portTDO JTAG data outputP5.1/TDI JTAG data input, or input/output digital portTCK JTAG test clock5 DC Characteristics5.1 Absolute Maximum RatingsSymbol Parameter Min TypMax Condition V DD1Supply Voltage -0.3 V - 3.6 V Respect to VSSV IA Analog Input Voltage -0.3 V - 1.98 V Respect to AVSSV ID Digital Input Voltage -0.3 V - 6.0 V Respect to VSS-0.3V - 7.0V Respect to VSSProgrammingV PP OTPvoltage˚C˚C - 85Temperature -40T A Ambient˚C˚C - 150Temperature -65T S StorageTable 1 Absolute Maximum RatingsCaution: Stresses beyond those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only and function of the device at these or any other conditions beyond those indicated in the operational sections of the specifications are not implied.5.2 System Clock Frequency and Power ConsumptionC AREF= 1nF, C MEXT= 100nF. VDD1=3.3V, Unless specified, Ta = 25˚C.Max UnitTypSymbol Parameter MinClock 32 - 128 MHzSYSCLK Systemconsumption 1601) 200 mW P D PowerTable 2 System Clock FrequencyNote 1) The value is based on the condition of MCE clock=126MHz, 8051 clock 31.5MHz with a actualmotor running by a typical MCE application program and 8051 code.5.3 Digital I/O DC CharacteristicsSymbol Parameter Min Typ Max Condition V DD1 Supply Voltage 3.0 V 3.3 V 3.6 V Recommended V PP OTP Programming voltage6.70V 6.75V 6.80V RecommendedV IL Input Low Voltage -0.3 V - 0.8 V Recommended V IH Input High Voltage 2.0 V 3.6 V RecommendedC IN Input capacitance - 3.6 pF - (1)I L Input leakage current ±10 nA ±1 μA V O = 3.3 V or 0 V I OL1(2) Low level output current 8.9 mA 13.2 mA 15.2 mA V OL = 0.4 V(1)I OH1(2) High level output current 12.4 mA 24.8 mA 38 mA V OH = 2.4 V(1)I OL2(3) Low level output current 17.9 mA 26.3 mA 33.4 mA V OL = 0.4 V(1)I OH2(3) High level output current 24.6 mA 49.5 mA 81 mA V OH = 2.4 V(1)Table 3 Digital I/O DC CharacteristicsNote:(1) Data guaranteed by design.(2) Applied to SCL/SO-SI, SDA/CS0 pins.(3) Applied to all digital I/O pins except SCL/SO-SI and SDA/CS0 pins.5.4 PLL and Oscillator DC characteristicsC AREF = 1nF, C MEXT = 100nF. VDD1=3.3V, Unless specified, Ta = 25˚C. Symbol Parameter Min Typ Max Condition V IL OSC Oscillator (XTAL0,1) Input Low Voltage 0 - 0.2* V DDCAP V DDCAP = voltage atVDDCAP pinV IH OSC Oscillator (XTAL0,1) Input High Voltage 0.8* V DDCAP - V DDCAP V DDCAP = voltage atVDDCAP pinTable 4 PLL DC Characteristics5.5 Analog I/O (IFB+,IFB-,IFBO, AIN5+,AIN5-,AIN5O) DC CharacteristicsC AREF = 1nF, C MEXT = 100nF. VDD1=3.3V, Unless specified, Ta = 25˚C.Symbol Parameter Min Typ Max Condition V OFFSET Input Offset Voltage - - 26 mV V I Input Voltage Range 0 V 1.2 V Recommended V OUTSW OP amp output operating range 50 mV (1)- 1.2 VC IN Input capacitance - 3.6 pF - (1)R FDBK OP amp feedback resistor 5 k Ω - 20 k ΩRequested between IFBO andIFB- OP GAINCL Operating Close loop Gain80 db - - (1)CMRR Common Mode Rejection Ratio- 80 db - (1)I SRC Op amp output source current - 1 mA - V OUT = 0.6 V(1)I SNK Op amp output sink current - 100 μA - V OUT = 0.6 V(1)Table 5 Analog I/O DC CharacteristicsNote:(1) Data guaranteed by design.5.6 Under Voltage Lockout DC characteristicsUnless specified, Ta = 25˚C.Symbol Parameter Min Typ Max ConditionUV CC+ UVcc positive going Threshold2.78 V3.04 V 3.23 V (1)UV CC- UVcc negative going Threshold2.78 V 2.97 V3.23 VUV CC H UVcc Hysteresys - 73 mV - (1)Table 6 UVcc DC CharacteristicsNote:(1) Data guaranteed by design.5.7 Itrip comparator DC characteristicsUnless specified, VDD1=3.3V, Ta = 25˚C.Symbol Parameter Min Typ Max Condition Itrip + Itrip positive going Threshold- 1.22V -Itrip - Itrip negative going Threshold- 1.10V -ItripH Itrip Hysteresys - 120mV -Table 7 Itrip DC Characteristics5.8 CMEXT and AREF CharacteristicsC AREF = 1nF, C MEXT = 100nF. Unless specified, Ta = 25˚C. Symbol Parameter Min Typ Max Condition V CM CMEXT voltage 495 mV 600 mV 700 mV VDD1 = 3.3 V (1) V AREF Buffer Output Voltage 495 mV 600 mV 700 mV VDD1 = 3.3 VΔV oLoad regulation (V DC -0.6) - 1 mV - (1)PSRR Power Supply Rejection Ratio- 75 db - (1)Table 8 CMEXT and AREF DC CharacteristicsNote:(1) Data guaranteed by design.6 AC Characteristics6.1 Digital PLL AC CharacteristicsSymbol Parameter Min Typ MaxConditionF CLKIN Crystalinputfrequency 3.2 MHz 4 MHz 60 MHz (1)(see figure below)F PLL Internalclockfrequency32 MHz 50 MHz 128 MHz (1)F LWPW Sleep mode outputfrequencyF CLKIN ÷ 256 - - (1) J S Short time jitter - 200 psec - (1) D Dutycycle - 50% - (1) T LOCK PLL lock time - - 500 μsec (1)Table 9 PLL AC CharacteristicsNote:(1) Data guaranteed by design.R2C1Figure 3 Crystal circuit example6.2 Analog to Digital Converter AC CharacteristicsUnless specified, Ta = 25˚C.Symbol Parameter Min Typ Max ConditionT CONV Conversion time - - 2.05 μsec (1)T HOLD Sample/Hold maximum hold time - - 10 μsec Voltage droop ≤ 15LSB(see figure below)Table 10 A/D Converter AC CharacteristicsNote:(1) Data guaranteed by design.T HOLDFigure 4 Voltage droop and S/H hold time6.3 Op amp AC CharacteristicsUnless specified, Ta = 25˚C.Symbol Parameter Min Typ MaxCondition OP SR OP amp slew rate - 10 V/μsec - VDD1 = 3.3 V, CL =33 pF (1) OP IMP OP input impedance - 108 Ω - (1) (2)T SET Settling time - 400 ns - VDD1 = 3.3 V, CL =33 pF (1)Table 11 Current Sensing OP Amp AC CharacteristicsNote:(1) Data guaranteed by design.(2) To guarantee stability of the operational amplifier, it is recommended to load the output pin by a capacitor of 47pF, see Figure 5. Here only the single shunt current amplifier is show but all op amp outputs should be loaded with this capacitor.Figure 5 A capacitor of 47pF is recommended at the output pin of all op amps.6.4 SYNC to SVPWM and A/D Conversion AC TimingSYNCIU,IV,IWAINxFigure 6 SYNC timingUnless specified, Ta = 25˚C.Symbol Parameter Min Typ Max Unitt wSYNC SYNC pulse width - 32 - SYSCLKt dSYNC1SYNC to currentfeedback conversiontime- - 100 SYSCLKt dSYNC2SYNC to AIN0-5 analoginput conversion time - - 200 SYSCLK(1)t dSYNC3SYNC to PWM outputdelay time- - 2 SYSCLKTable 12 SYNC AC CharacteristicsNote:(1) AIN1 through AIN5 channels are converted once every 6 SYNC events6.5 GATEKILL to SVPWM AC TimingUnless specified, Ta = 25˚C.Symbol Parameter Min Typ Max Unitt wGK GATEKILL pulse width 32 - - SYSCLK- - 100 SYSCLK t dGK GATEKILL to PWMoutput delayTable 13 GATEKILL to SVPWM AC Timing6.6 Itrip AC TimingUnless specified, Ta = 25˚C.Symbol Parameter Min Typ Max Unit t ITRIP Itrip propagation delay - - 100(sysclk)+1.0usec SYSCLK+usecTable 14 Itrip AC TimingIRMCK1716.7 Interrupt AC TimingFigure 9 Interrupt timingUnless specified, Ta = 25˚C. Symbol Parameter Min Typ Max Unitt wINT INT0, INT1 InterruptAssertion Time4 - - SYSCLK t dINT INT0, INT1 latency--4SYSCLKTable 15 Interrupt AC Timing6.8 I 2C AC TimingFigure 10 I C TimingUnless specified, Ta = 25˚C.Symbol Parameter Min Typ Max UnitT I2CLK I 2C clock period 10 - 8192 SYSCLKt I2ST1 I 2C SDA start time 0.25 - - T I2CLKt I2ST2 I 2C SCL start time 0.25 - - T I2CLKt I2WSETUP I 2C write setup time 0.25 - - T I2CLKt I2WHOLD I 2C write hold time 0.25 - - T I2CLKt I2RSETUP I 2C read setup time I 2C filter time (1)- - SYSCLKt I2RHOLD I 2C read hold time 1 - - SYSCLKTable 16 I 2C AC TimingNote:(1) I 2C read setup time is determined by the programmable filter time applied to I 2C communication.6.9 SPI AC TimingSPI Write AC timingFigure 11 SPI write timingUnless specified, Ta = 25˚C.Symbol Parameter Min Typ Max Unit T SPICLK SPI clock period 4 - - SYSCLK t SPICLKHT SPI clock high time - 1/2 - T SPICLKt SPICLKLT SPI clock low time - 1/2 - T SPICLK t CSDELAY CS to data delay time - - 10 nsec t WRDELAY CLK falling edge to data delay time- - 10 nsect CSHIGH CS high time between two consecutive byte transfer1 - - T SPICLKt CSHOLD CS hold time - 1 - T SPICLKTable 17 SPI Write AC TimingSPI Read AC TimingFigure 12 SPI read timingUnless specified, Ta = 25˚C.Symbol Parameter Min Typ Max Unit T SPICLK SPI clock period 4 - - SYSCLK t SPICLKHT SPI clock high time - 1/2 - T SPICLK t SPICLKLT SPI clock low time - 1/2 - T SPICLK t CSRD CS to data delay time - - 10 nsect RDSU SPI read data setup time 10 - - nsec t RDHOLD SPI read data hold time 10 - - nsec t CSHIGH CS high time between two consecutive byte transfer1 - - T SPICLKt CSHOLD CS hold time - 1 - T SPICLKTable 18 SPI Read AC Timing6.10 UART AC TimingUnless specified, Ta = 25˚C.Symbol Parameter Min Typ Max Unit T BAUD Baud Rate Period - 57600 - bit/sec- 1/16 - T BAUDT UARTFIL UART sampling filterperiod (1)Table 19 UART AC TimingNote:(1) Each bit including start and stop bit is sampled three times at center of a bit at an interval of 1/16T BAUD. If three sampled values do not agree, then UART noise error is generated.6.11 CAPTURE Input AC TimingFigure 14 CAPTURE timingUnless specified, Ta = 25˚C.Symbol Parameter Min Typ Max Unit T CAPCLK CAPTURE input period 8 - - SYSCLKt CAPHIGH CAPTURE input high time4 - - SYSCLKt CAPLOW CAPTURE input low time 4 - - SYSCLK t CRDELAY CAPTURE falling edge tocapture register latch time - - 4 SYSCLKt CLDELAY CAPTURE rising edge to capture register latch time - - 4 SYSCLKt INTDELAYCAPTURE input interrupt latency time- - 4 SYSCLKTable 20 CAPTURE AC Timing6.12 OTP Programming TimingTCKVPPFigure 15 OTP programming timingUnless specified, Ta = 25˚C.Symbol Parameter MinTypMaxUnit T VPS VPP Setup Time 10 - - nsecT VPH VPP Hold Time 15 - - nsecTable 21 OTP Programming Timing6.13 JTAG AC TimingUnless specified, Ta = 25˚C.Symbol Parameter MinUnitMaxTypT JCLK TCKPeriod - - 50 MHzt JHIGH TCK High Period 10 - - nsect JLOW TCK Low Period 10 - - nsec0 - 5 nsect CO TCK to TDO propagation delaytimet JSETUP TDI/TMS setup time 4 - - nsect JHOLD TDI/TMS hold time 0 - - nsecTable 22 JTAG AC Timing7 I/O StructureThe following figure shows the motor PWM output (PWMUH/PWMUL/PWMVH/PWMVL/PWMWH/PWMWL)Figure 17 PWMUL/PWMUH/PWMVL/PWMVH/PWMWL/PWMWH outputThe following figure shows the digital I/O structure except the motor PWM output6.0V6.0VInternal digital circuit VSSFigure 18 All digital I/O except motor PWM outputIRMCK171The following figure shows RESET and GATEKILL I/O structure.Figure 19 RESET, GATEKILL I/OThe following figure shows the analog input structure.Figure 20 Analog inputThe following figure shows all analog operational amplifier output pins and AREF pin I/O structure.Figure 21 Analog operational amplifier output and AREF I/O structureIRMCK171The following figure shows the VPP pin structurePINVSS270Figure 22 VPP programming pin I/O structureFigure 23 VSS and AVSS pin structureThe following figure shows the VDD1 and VDDCAP pin structurePINVSSFigure 24 VDD1 and VDDCAP pin structureFigure 25 XTAL0/XTAL1 pins structure8 Pin ListPinNumber Pin Name Internal Pull-up /Pull-downPinType Description1 XTAL0 I Crystalinput2 XTAL1 O Crystaloutput3 P1.0/T2 I/O Discrete programmable I/O or Timer/Counter 2 input4 SCL/SO-SI I/O I2C clock output (open drain, need pull up) or SPI data5 SDA/CS0 I/O I2C data (open drain, need pull up) or SPI Chip Select6 P1.3/SYNC/SCK I/O Discrete programmable I/O or SYNC output or SPIclock output, needs to be pulled up to VDD1 in order toboot from I2C EEPROM7 P1.4/CAP I/O Discrete programmable I/O or Capture timer input8 VDD1 P 3.3V digital power9 VSS P Digitalcommon10 VDDCAP P Internal 1.8V output, Capacitor(s) to be connected11 P2.0/NMI I/O Discreteprogrammable I/O or Non-maskable Interruptinput12 P3.2/INT0 I/O Discrete programmable I/O or Interrupt 0 input13 P2.7/AOPWM1 I/O Discrete programmable I/O or PWM 1 digital output14 AIN0 I Analog input channel 0, 0-1.2V range, needs to bepulled down to AVSS if unused15 AIN1 I Analog input channel 1, 0-1.2V range, needs to bepulled down to AVSS if unused16 AIN2 I Analog input channel 2, 0-1.2V range, needs to bepulled down to AVSS if unused17 AIN3 I Analog input channel 3, 0-1.2V range, needs to bepulled down to AVSS if unused18 AIN4 I Analog input channel 4, 0-1.2V range, needs to bepulled down to AVSS if unused19 IFB- I Single shunt current sensing OP amp input (-)20 IFB+ I Single shunt current sensing OP amp input (+)21 IFBO O Single shunt current sensing OP amp output22 CMEXT O Unbuffered 0.6V output. Capacitor needs to beconnected.23 AREF O Analog reference voltage output (0.6V)24 AIN5- I Analog input channel 5, 0-1.2V range, needs to bepulled down to AVSS if unused25 AIN5+ I Analog input channel 5, 0-1.2V range, needs to bepulled down to AVSS if unused26 AIN5O O Analog output 5, 0-1.2V range,27 AVSS P Analogcommon28 VDDCAP P Internal 1.8V output, Capacitor(s) to be connected29 VDD1 P 3.3V digital power30 VSS P Digitalcommon31 P3.1/AOPWM2 I/O Discrete programmable I/O or PWM 2 digital output32 PWMWL 58kΩ Pulldown O PWM gate drive for phase W low side, configurableeither high or low true.。

DSC-CN5711

最大结温…………………...150℃ 存储温度…………………....-65℃ to 150℃ 焊接温度…………………...260℃

超出以上所列的极限参数可能造成器件的永久损坏。以上给出的仅仅是极限范围,在这样的极限条件下 工作,器件的技术指标将得不到保证,长期在这种条件下还会影响器件的可靠性。

输入电源

3

4

8

VCC VCC

CE

5 LED LED 6

CN5711

可调 电阻

RISET2

RISET1

1 ISET

GND 2

图5 用可变电阻调整发光二极管的亮度

6

REV 1.1

如韵电子 CONSONANCE

稳定性

通常情况下,在ISET管脚没有外加电容时,在此管脚可以接一个阻值最大为30K的电阻。如果在ISET管 脚有外接的电容,则在此管脚允许外接的电阻值会减小。为了保证电流回路的稳定性,ISET管脚外接电 阻,电容所形成的极点应高于300KHz。假设ISET管脚外接电容C,用下面的公式可以计算ISET管脚允许 外接的最大电阻值:

REV 1.1

如韵电子 CONSONANCE

典型应用电路:

图 1 典型应用电路

订购信息:

器件型号 CN5711

封装形式 SOP8

包装 盘装,每盘 2500 只

工作环境温度 -40℃ 到 85℃

功能框图:

CE ISET

Sc hmitt

VCC

+

电压基准源

电流镜

GND

图 2 功能框图

2

LED

REV 1.1

如韵电子 CONSONANCE

管脚描述:

序号.

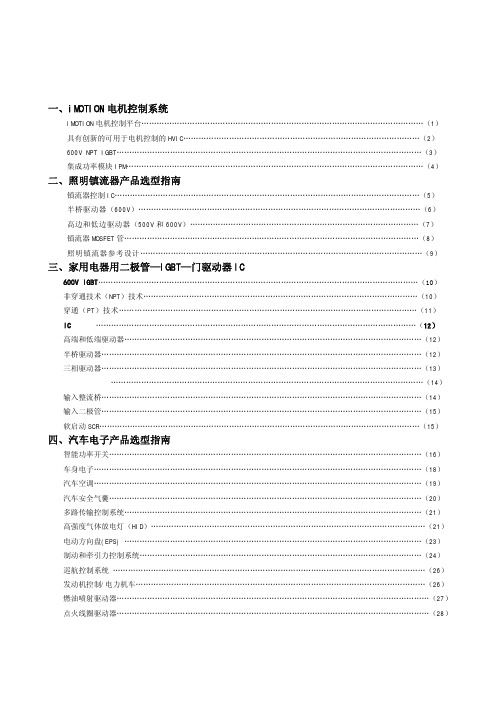

IR选型指南

600V 应用系统,输出推/拉电流为 200/420mA

型号

电路

VCC 范围

IR2130 3-Phase Bridge Driver IR2131 3HI/3LO MOS Driver IR2132 3-Phase Bridge Driver 10-25V with UVLO IR2133 3-Phase Bridge Driver IR2135 3-Phase Bridge Driver

Ton/Toff

VIH/VIL

Vitrip+ UVCC/BS+/CCBS-

IR2136

IR21362

12-25V with UVLO

IR21363

IR21365

IR21366 IR21367

12-20V with UVLO

IR21368

10V/20V

___ __ 400ns/380ns 2.7V/1.7V 0.46V

电路

IC@25°C IC@100°C VCE(on)@25°C

Co-Pack 12A

6.8A

2.1V

Co-Pack 12A

6.8A

2.1V

Co-Pack 13A

7A

1.8V

Co-Pack 17A

9A

1.8V

Co-Pack 22A

12A

1.8V

Co-Pack 31A

15A

1.8V

Isolated TO-220 Full-Pak

Co-Pack 9A

6A

1.8V

Isolated TO-220 Full-Pak

Co-Pack 12A

Hale Waihona Puke 8A1.8VIsolated TO-220 Full-Pak

芯片pn551a参数

芯片pn551a参数全文共四篇示例,供读者参考第一篇示例:芯片PN551A是一款高性能、多功能的芯片,在电子产品中广泛应用。

它具有很多强大的参数和功能,下面我们来详细介绍一下它的各项参数。

芯片PN551A的尺寸为5mm x 5mm x 1mm,非常小巧,适合安装在各种小型电子产品中。

它采用了先进的工艺技术,具有高度集成的芯片结构,同时具备了高性能的处理能力和低功耗的特点。

芯片PN551A支持多种接口协议,包括I2C、SPI和UART等,使得它能够与不同类型的主控芯片进行通信,实现更加灵活的应用场景。

它还支持多种传输速率,可以满足不同产品的通信需求。

芯片PN551A具有丰富的功能模块,包括蓝牙、射频、NFC、USB等,涵盖了多种无线通信方式,能够实现蓝牙音频传输、数据传输、支付功能等多种应用场景。

它还具有强大的数据处理能力,能够实现实时的数据传输和处理,使产品性能更加优越。

芯片PN551A还具有丰富的安全功能,包括身份认证、加密解密、随机数生成等多种安全机制,可以保护产品的数据安全。

它还支持多种电源管理模式,能够实现低功耗的工作状态,延长产品的使用时间。

芯片PN551A是一款具有多项强大参数和功能的芯片,适用于各种小型电子产品中,能够满足不同需求的设计要求。

它具有高性能、低功耗、丰富的功能模块、多种通信接口、强大的数据处理能力和安全功能等特点,是一款非常值得推荐的芯片。

第二篇示例:芯片PN551A采用的是32位ARM Cortex-M4内核,运行主频可达到100MHz。

这样的高性能处理器可以保证芯片在进行复杂计算和数据处理时能够快速高效地完成任务。

低功耗设计也是芯片PN551A 的特点之一,可以在保证性能的同时延长电池续航时间,提高产品的使用体验。

芯片PN551A内置了多种接口和外设模块,例如USB接口、SPI 接口、I2C接口等,可以方便地与外部设备进行通信和数据交换。

芯片还内置了丰富的模拟和数字引脚,可以满足各种外部传感器和器件的连接需求。

介绍几种电机驱动芯片

介绍几种电机驱动芯片[作者:佚名转贴自:本站原创点击数:1493 更新时间:2005-4-22 文章录入:白桦]减小字体增大字体在自制机器人的时候,选择一个合适的驱动电路也是非常重要的,本文详细介绍了几种常用的机器人驱动芯片。

介绍几种机器人驱动芯片(注:本文已经投稿至《电子制作》)在自制机器人的时候,选择一个合适的驱动电路也是非常重要的。

最初,通常选用的驱动电路是由晶体管控制继电器来改变电机的转向和进退,这种方法目前仍然适用于大功率电机的驱动,但是对于中小功率的电机则极不经济,因为每个继电器要消耗20~100mA的电力。

当然,我们也可以使用组合三极管的方法,但是这种方法制作起来比较麻烦,电路比较复杂,因此,我在此向大家推荐的是采用集成电路的驱动方法:马达专用控制芯片LG9110芯片特点:低静态工作电流;宽电源电压范围:2.5V-12V ;每通道具有800mA 连续电流输出能力;较低的饱和压降;TTL/CMOS 输出电平兼容,可直接连CPU ;输出内置钳位二极管,适用于感性负载;控制和驱动集成于单片IC 之中;具备管脚高压保护功能;工作温度:0 ℃-80 ℃。

描述:LG9110 是为控制和驱动电机设计的两通道推挽式功率放大专用集成电路器件,将分立电路集成在单片IC 之中,使外围器件成本降低,整机可靠性提高。

该芯片有两个TTL/CMOS 兼容电平的输入,具有良好的抗干扰性;两个输出端能直接驱动电机的正反向运动,它具有较大的电流驱动能力,每通道能通过750 ~800mA 的持续电流,峰值电流能力可达1.5 ~2.0A ;同时它具有较低的输出饱和压降;内置的钳位二极管能释放感性负载的反向冲击电流,使它在驱动继电器、直流电机、步进电机或开关功率管的使用上安全可靠。

LG9110 被广泛应用于玩具汽车电机驱动、步进电机驱动和开关功率管等电路上。

管脚定义:1 A 路输出管脚、2和3 电源电压、4 B 路输出管脚、5和8 地线、6 A 路输入管脚、7 B 路输入管脚2、恒压恒流桥式1A驱动芯片L293图2是其内部逻辑框图图3是其与51单片机连接的电路原理图L293是著名的SGS公司的产品,内部包含4通道逻辑驱动电路。

IRMCK201高性能数字运动控制芯片IRMCK201功能及其应用

Data Sheet No. PD60224 Rev.BIRMCK201High Performance Configurable Digital ACServo Control ICFeatures∙ Complete closed loop current control(Synchronously Rotating Frame Field Orientation ∙ Versatile Space Vector PWM ∙ Direct interface to IR2175 current sensing high voltage IC∙ Direct Encoder interface with multiplexed/non- multiplexed Hall A/B/C signals ∙ Direct interface to IR213x 3-phase gate driver IC ∙ Closed loop velocity control ∙ Configurable architecture o Supports AC PM motor or Induction motoro Closed loop or open loop control ∙ Asynchronous serial communication interface (RS232C, RS422 ∙ Fast SPI interface∙ 4 channel 12-bit A/D interface with simultaneous sample/hold∙ 8-bit parallel bus interface for microcontrollerexpansion (supports most 8-bit microprocessors ∙ Integrated brake IGBT control ∙ServoDesignerTM(Configuration Tool availableProduct SummaryMax. Clock Input (Sysclk33.3 MHz Max. PLL clock for current feedback133.3 MHzClosed loop current control computation time 6 µsec max Closed loop current loop bandwidth (-3 dB5.5 kHzClosed loop velocity loop update rate 5 / 10kHz PWM carrier frequency83.3 kHz max PWM counter resolution12bit Current feedback temp drift/offset calibrated Max SPI clock8 MHz Package: QFP100DescriptionIRMCK201 is a complete AC servo motor control IC. It contains closed loop current control for sinusoidal AC current, and closed loop velocity control based on encoder position feedback interface. A standard communication port is provided for RS232C or RS422, in addition to a fast SPI communication interface. Unlike a traditional DSP or a microcontroller, the IRMCK201 does not require any programming effort to complete the complex control algorithm. It allows users to configurethe algorithm for specific application needs. Permanent magnet motor or AC induction motor are supported. IRMCK201 facilitates high performance servo design together with the IR2175 current sensing IC and IR213x high voltage 3-phase gate driver IC, which simplifies the hardware design while minimizing cost. For multi-axis applications, IRMCK201 can be usedOverviewIRMCK201IRMCK201 is a new International Rectifier integrated circuit device designed as a one-chip solution for completeclosed loop current control and velocity control for a high performance servo drive system. Unlike a traditional microcontroller or DSP, IRMCK201 does not require any programming to complete complex AC servo algorithm development. Combined with International Rectifier's high voltage gate drive and current sensing IC, the user can implement a complete AC servo control with minimum component count and virtually no design effort. Although IRMCK201 contains dedicated logic to perform closed loop control of AC current and velocity, it has a wide range of application coverage through its flexible configuration ability. The drive can be easily configured for induction machine closed loop vector control or permanent magnet motor servo drive. Rich motion peripherals, analog and digital I/O can also be configured. Host communication logic contains an asynchronous RS232C or RS422 communication interface, a fast slave SPIinterface and an 8-bit-wide Host Parallel Interface. All communication ports have the same access capability to the host register set. The user can write to and read from the predefined registers to configure and monitor the drive through these communication ports.IRMCK201 Main Features∙Complete closed loop current control based on Synchronously Rotating Frame Field Orientation∙Configurable update rate with PWM carrier frequency∙Configurable parameters (all PI controller gains, PI output limit range, current feedback scaling, encoder feedback scaling∙Configurable control structure for Induction machine or AC Permanent Magnet machine (Disable/enable slip gain∙Closed loop velocity control with configurable update rate∙Enable/disable velocity loop∙Selectable reference input for torque and speed input∙Analog reference input∙RS232C/RS422 reference input∙Dynamic braking control for excess DC bus voltage∙Cycle-by-cycle on/off Control for Brake IGBT∙DC bus voltage feedback∙Standard Encoder interface with Hall ABC support∙A/B quadrature signal input up to 1 MHz∙Choice of separate or multiplexed Hall A/B/C signal input∙Auto-initialization with Hall A/B/C plus Z pulse input∙Adaptable for any line count encoder from 200 PPR to 10,000 PPR∙1/T counter (1 MHz for low speed performance improvement∙Space Vector PWM with deadtime insertion∙IR2175 current sensing IC interface∙IR213x high voltage gate driver IC interface∙Low cost serial 12 bit A/D interface with multiplexer and sample/hold circuit∙4 channel analog output by PWM0-3.3 V, 120 kHz output∙EEPROM for startup initialization of internal data/parameters through host register interfaceAT24C01A, 128 x 8IRMCK201 ∙Versatile host communication interfaceRS232C or RS422 host interfaceFast SPI slave host interface with multi-drop capability Parallel Host interface (total 12 pins∙Multiplexed data/address busAddress EnableRD/WR∙Discrete I/OStart (InputStop (InputIFBCAL (InputFault Clear (InputFault (OutputSYNC (OutputPWM Active (Output∙LEDTwo-bit bi-colorIRMCK201Table of ContentsOverview ....................................................................................................................... ................................................... 2 IRMCK201 MainFeatures ............................................................................................................................................ 2 IRMCK201 BlockDiagrams ............................................................................................................................... .. (7)Basic BlockDiagram ................................................................................................................................. ................... 7 Detailed Block Diagram.................................................................................................................................. .. (8)Input/Output ofIRMCK201 ........................................................................................................................... ............... 9 Typical ApplicationConnections . ......................................................................................................................... . (13)IC Crystal ClockCircuitry ................................................................................................................................ .......... 14 Low Pass Filter....................................................................................................................................... ..................... 15 Implementing the Low Pass FilterShield ............................................................................................................... 16 Cp Rp and Cs Component Values (16)PLL Reset....................................................................................................................................... ............................. 16 DC Electrical Characteristics and OperatingConditions (17)Absolute Maximum Ratings................................................................................................................................... ..... 17 Recommended OperatingConditions ......................................................................................................................... 17 DCCharacteristics ....................................................................................................................... ............................... 18 Common Quiescent and LeakageCurrent .................................................................................................................. 18 Input Characteristics ñ Non Schmitt TriggerInputs ................................................................................................... 18 Input Characteristics ñ Schmitt TriggerInputs ........................................................................................................... 18 Output Characteristics . ..................................................................................................................... ........................... 18 Output CharacteristicsOSC2CLK ..............................................................................................................................19 Pin and I/O CharacteristicTable .................................................................................................................................20 PowerConsumption ......................................................................................................................... ........................... 22 AC Electrical Characteristics and OperatingConditions ......................................................................................... 23 System Level AC Characteristics........................................................................................................................ ........ 23 Sync Pulse to Sync Pulse Timing. (23)FAULT and REDLED Response toGATEKILL ................................................................................................... 24 Host Interface AC Characteristics............................................................................................................................... 25 SPITiming ................................................................................................................................... ........................... 25 Host ParallelTiming ................................................................................................................................... . (26)IRMCK201Host Parallel Read Cycle...................................................................................................................................... ... 26 Host Parallel Write Cycle...................................................................................................................................... .. 27 Discrete I/O ElectricalCharacteristics ........................................................................................................................28 Motion Peripheral Electrical Characteristics (29)PWM ElectricalCharacteristics ....................................................................................................................... ....... 29 IR2175Interface ................................................................................................................................ ..................... 29 Encoder Electrical Characteristics........................................................................................................................ (30)Analog To Digital Interface ElectricalCharacteristics ............................................................................................... 31 ADC Timing.................................................................................................................................... ........................ 31 PLL Interface ElectricalCharacteristics......................................................................................................................33Appendix A Host RegisterMap (34)Host Parallel Access.................................................................................................................................... ............ 34 SPI RegisterAccess ................................................................................................................................... ............. 34 RS-232 RegisterAccess . ................................................................................................................................. .. (34)Write RegisterDefinitions ............................................................................................................................. ............. 40 QuadratureDecode Register Group (Write Registers............................................................................................. 40 PwmConfig Register Group (WriteRegisters (41)CurrentFeedbackConfig Register Group (WriteRegisters .................................................................................... 42 SystemControl Register Group (WriteRegisters . (43)CurrentLoopConfig Register Group (WriteRegisters ........................................................................................... 44 VelocityControl Register Group (WriteRegisters . ................................................................................................ 45 FaultControl Register Group (WriteRegisters (47)SVPWMScaler Register Group (WriteRegisters (47)DiagnosticPwmControl Register Group (WriteRegisters ..................................................................................... 48 SystemConfig Register Group (WriteRegisters . (49)DirectHostVoltageControl Register Group (WriteRegisters ................................................................................ 49 32bitQuadDecode Register Group (Write Registers.............................................................................................. 50 EepromControl Registers (Write Registers (51)HallSensorEncoderInit (Write Registers ñ EEPROMonly ................................................................................... 52 Read RegisterDefinitions ............................................................................................................................. .............. 53 QuadratureDecodeStatus Register Group (Read Registers.................................................................................... 53 SystemStatus Register Group (Read Registers ......................................................................................................53 DcBusVoltage Register Group (ReadRegisters (54)FocDiagnosticData Register Group (ReadRegisters . ............................................................................................ 54 FaultStatus Register Group (Read Registers. (56)VelocityStatus Register Group (ReadRegisters (56)CurrentFeedbackOffset Register Group (ReadRegisters (57)32bitQuadDecodeStatus Register Group (ReadRegisters . .................................................................................... 57 EepromStatus Registers (ReadRegisters . (58)FOCDiagnosticDataSupplement Register Group (ReadRegisters ........................................................................ 59 Appendix BPackage ................................................................................................................................. ................ 60 Appendix CErrata . ................................................................................................................................... . (62)IRMCK201List of FiguresFigure 1. Basic Block Diagram ofIRMCK201 . (7)Figure 2. Detailed Block Diagram ofIRMCK201 ........................................................................................................ 8 Figure 3. Input/Output ofIRMCK201 ..........................................................................................................................9 Figure 4. Typical Connection ofIRMCK201 (13)Figure 5. Oscillator Circuit.................................................................................................................................... ...... 14 Figure 6. PLL Low Pass FilterShielding (15)Figure 7. System Level SYNC-to-SYNCTiming ....................................................................................................... 23 Figure 8. FAULT and REDLED Response toGATEKILL ........................................................................................ 24 Figure 9. SPI Timing ................................................................................................................................... ................ 25 Figure 10. Host Parallel Read Cycle Timing............................................................................................................... 26 Figure 11. Host Parallel Write Cycle Timing.............................................................................................................. 27 Figure 12. Discrete I/OTiming ...................................................................................................................................28 Figure 13. PWMTiming ................................................................................................................................... .......... 29 Figure 14. IR2175Interface ................................................................................................................................ ........ 29 Figure 15. EncoderTiming ................................................................................................................................... ...... 30 Figure 16. Top Level ADCTiming . (31)Figure 17. ADC SpecificTiming ................................................................................................................................32 List of TablesTable 1: Typical Values for the ClockCircuit ................................................................................................................ 14 Table 2: PLL Test Pin Assignments........................................................................................................................... ..... 15 Table 3: PLL Low Pass FilterValues (16)Table 4: Absolute MaximumRatings (17)Table 5: Recommended OperatingConditions (17)Table 6: DCCharacteristics ....................................................................................................................... ..................... 18 Table 7: Non Schmitt Trigger InputCharacteristics ....................................................................................................... 18 Table 8: Schmitt Trigger InputCharacteristics (18)Table 9: Output Characteristics........................................................................................................................ ............... 18 Table 10: Output CharacteristicsOSC2CLK (19)Table11 ........................................................................................................................................... ............................... 20 Table 12: Pin and I/OCharacteristics ....................................................................................................................... ...... 22 Table 13: IRMCK201 Power Consumption.. (22)Table 14: System Level SYNC-to-SYNCTiming .......................................................................................................... 24 Table 15: FAULT and REDLED Response toGATEKILL ........................................................................................... 24 Table 16: SPI Timing ................................................................................................................................... ................... 25 Table 17: Host Parallel Read Cycle Timing.................................................................................................................... 26 Table 18: Host Parallel Write CycleTiming . .................................................................................................................. 27 Table19: Discrete I/OTiming ................................................................................................................................... ..... 28 Table 20: PWMTiming ................................................................................................................................... ............... 29 Table 21: IR2175Interface ................................................................................................................................ ............. 29 Table 22: EncoderTiming ................................................................................................................................... ........... 30 Table 23: Top Level ADCTiming . .................................................................................................................................31 Table 24: ADC SpecificTiming ................................................................................................................................... .. 32 Table 25: PLL Electrical Characteristics.........................................................................................................................33 Table 26: QFP100Package . ............................................................................................................................... ............. 60 Table 27: QFP100Dimensions ........................................................................................................................... (61)IRMCK201IRMCK201 Block DiagramsBasic Block DiagramFigure 1 shows the basic block diagram of the IRMCK201 surrounded by various Accelerator ICs. Host communications are provided over SPI, RS-232C or Host parallelports. Two current sensing ICs (IR2175 and a three phase high voltage gate drive typically implement the high voltage / current interface between the IRMCK201 IC and motor.The IRMCK201 can operate in a ìst and-al oneîmode without the host controller. A serial EEPROM could beutilized to load motor-specific parameters into the IC.AC PowerFigure 1. Basic Block Diagram of IRMCK201IRMCK201Detailed Block DiagramFigure 2 shows a detailed block diagram or the IRMCK201. All logic and algorithms are pre-programmed, and the user does not need to make any effort to develop code, alleviating the tedious design process. If needed, the user can configure the drive to tailor the control per specific needs to meet the required specification. This configuration is easily done by accessing the host register set through the communication interface.Figure 2. Detailed Block Diagram of IRMCK201IRMCK201Input/Output of IRMCK201Figure 3 shows the interface signals divided into sub-groups. For detailed pin assignment, please refer to Table 12 in this data sheet.SYSCLK PWMUH PLL &System ClockRESETN XPDOSC1CLKOSC2CLKPLLTESTCHGO LPVSSPWMUL PWMVH PWMVL PWMWH PWMWL BRAKEGATEKILLPWM gate signalInterfaceHostCommunicationInterfaceSCLK MISO MOSI CSNHP_nOE HP_nWE HP_D[0-7]HP_A IFB0 IFB1ENA ENB ENZ HALLAHALLB HALLCIR2175 InterfaceEncoder InterfaceHP_nCS Discrete I/OTX RX BAUDSEL SYNCFAULT ADCLK ADOUT ADCOVST ADMUX0ADMUX1REDLEDA/D InterfaceLEDSerial EEPROMSCA SCLPID[0-1] POWER IDFigure 3. Input/Output of IRMCK201 IRMCK201IRMCK201IRMCK201IRMCK201Typical Application ConnectionsTypical application connection is shown in Figure 4. In order to complete a high performance servo drive control, all necessary components are shown in connection to IRMCK201.Optional Current sensingOptional Current sensingFigure 4. Typical Connection of IRMCK201IRMCK201IC Crystal Clock CircuitryThe clock input to the IC is a 33.33 MHz crystal oscillator. Two shunt capacitors and possibly a series resistor is required to terminate the crystal to the IC.The values of the R/C will vary based on actual PCB attributes, and some empirical analysis may be required to get the PLL to start oscillating. Once oscillating, verify that the signal waveforms at the OSC1CLK and OSC2CLK pins are sinusoidal rather than trapezoidal. Refer to Table 1 for suggested R/C values. Most low-cost crystals can be used in this application. An example is a Citizen Part number CM309B33.333MABJT available from Digi-Key under part number 300-4160-1-ND.Figure 5. Oscillator CircuitTable 1: Typical Values for the Clock CircuitPLL Clock CircuitryIRMCK201The IRMCK201 contains a PLL that creates a 2X and 4X clock from the input 33.33 MHz input clock pin. There are a number of pins on the IC allocated for factory testing purposes, which need to be left unconnected. Table 2 shows required PCB signal connections for these pins. Note that N/C is for factory use only.Low Pass FilterThe low pass filter for this PLL resides between the CHGO and LPVSS pins. Three passive components arerequired to implement this filter: Cp, Rp and Cs. Figure 6 shows how to place these components around the IC. A shield should be placed below Rp, Cp and Cs made out of copper etch.Shielded by LPVSSIRMCK201I m p l e m e n t i n g t h e L o w P a s s F i l t e r S h i e l dMake all connections between CHGO, Rp, Cp, Cs and LPVSS as short as possible. Create the underlining shield by ìcopper fillingî a larger area in the signal plane of the PCB. Connect this shield to the LPVSS pin of the IC. Do not connect this shield to signal ground (VSS.C p R p a n d C s C o m p o n e n t V a l u e sFor a typical FR4 PCB, the values of the passive components are shown in Table 3.PLL ResetTable 3: PLL Low Pass Filter ValuesThere are two reset pins on the IC, XPD and RESETN both low true. XPD holds the PLL circuitry in reset when low. Upon XPD going high, the PLL circuitry begins to lock onto the 33.33 MHz clock input. The PLL circuit may take up to 1 ms to become stable. RESETN asserted low holds the internal DSP logic in reset. Upon RESETN going high, the IC digital logic becomes active.RESETN should be held low during and at least 1 ms after XPD goes high false to hold the internal DSP logic in reset while the PLL becomes stable.IRMCK201DC Electrical Characteristics and Operating ConditionsAbsolute Maximum RatingsNote: VSS = 0 VoltPARAMETER SYMBOL LIMITSUNIT S NOTEPower SupplyVoltage VDDVSS-0.3 to 4.0 VVSS-0.3 to VDD+0.5V Non 5 VoltInput Voltage VITolerant Pins VSS-0.3 to 7V Only on 5 Volt Tolerant PinsOutput Voltage VO VSS-0.3 to VDD+0.5 V Output Currentper Pin IOUT +/- 30 mATemperatureTstg-65 to 150°CTable 4: Absolute Maximum RatingsRecommended Operating ConditionsNote: VSS = 0 Volt PARAMETER SYMBOL MIN TYP MAX UNITS NOTE Power SupplyVoltage VDD 3.0 3.3 3.6 V VDD V Non 5 Volt Tolerant Pins Input Voltage VI VSS - 5.5 V Pins Ambient TemperatureTa-40-85°CNote 1Table 5: Recommended Operating ConditionsNotes:1. The ambient temperature range is recommended for Tj = -40 to 125 °CDC CharacteristicsIRMCK201Common Quiescent and Leakage CurrentPARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS VI=VDD or VSSQuiescentCurrentIDDSInput Leakage Current ILIVDD=MAXIOH=IOL=0Ta=Tj=85°CVDD=MAXVIH=VDDVIL=VSS- - 0.35 uA -1 - 1 uA Table 6: DC CharacteristicsInput Characteristics – Non Schmitt Trigger InputsPARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS High LevelInput VoltageVIH1 VDD=MAX 2.0 - - V Input VoltageVIL1 VDD=MIN - - 0.8 V Table 7: Non Schmitt Trigger Input CharacteristicsInput Characteristics – Schmitt Trigger InputsPARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS Input VoltageVT1+ VDD=MAX 1.1 - 2.4 V Input VoltageVT1- VDD=MIN 0.6 - 1.8 V VoltageVH1 VDD=MIN 0.1 - - V Table 8: Schmitt Trigger Input Characteristics Output CharacteristicsPARAMETER SYMBOL CONDITIONS MIN TYP MAX UNIT SHigh LevelOutput VoltageVOH3Low Level Output Voltage VOL3VDD=MINIOH=-12mAVDD - 0.4 - - V VDD=MINIOH = 12mA- - VSS + 0.4 V Table 9: Output CharacteristicsIRMCK201Output Characteristics OSC2CLK。

机器人常用芯片

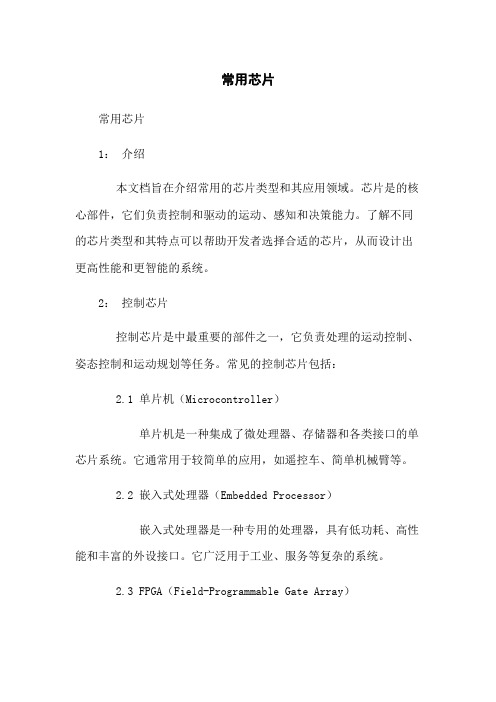

常用芯片常用芯片1:介绍本文档旨在介绍常用的芯片类型和其应用领域。

芯片是的核心部件,它们负责控制和驱动的运动、感知和决策能力。

了解不同的芯片类型和其特点可以帮助开发者选择合适的芯片,从而设计出更高性能和更智能的系统。

2:控制芯片控制芯片是中最重要的部件之一,它负责处理的运动控制、姿态控制和运动规划等任务。

常见的控制芯片包括:2.1 单片机(Microcontroller)单片机是一种集成了微处理器、存储器和各类接口的单芯片系统。

它通常用于较简单的应用,如遥控车、简单机械臂等。

2.2 嵌入式处理器(Embedded Processor)嵌入式处理器是一种专用的处理器,具有低功耗、高性能和丰富的外设接口。

它广泛用于工业、服务等复杂的系统。

2.3 FPGA(Field-Programmable Gate Array)FPGA是一种可编程逻辑器件,具有高度灵活性和可重构性。

它可以实现定制化的控制逻辑,常用于需要高实时性和并行计算能力的应用。

3:感知芯片感知芯片是实现环境感知和人机交互的关键组件,它可以接收、处理和分析传感器信号,以获取周围环境的信息。

常见的感知芯片包括:3.1 视觉处理器(Vision Processor)视觉处理器是一种专用的处理器,用于实时图像处理和分析。

它可以提取图像特征并实现目标识别、跟踪和三维重建等功能。

3.2 深度学习芯片(Deep Learning Chip)深度学习芯片是一种专用的芯片,用于实现深度学习算法。

它具有高并行计算能力和低功耗特点,可以用于图像识别、语音识别和自然语言处理等任务。

3.3 传感器接口芯片(Sensor Interface Chip)传感器接口芯片是一种与传感器连接的接口芯片,它可以将传感器信号转化为数字信号,并提供给控制芯片进行处理和分析。

4:决策芯片决策芯片是实现自主决策和规划能力的关键组件,它可以处理感知数据并相应的动作。

常见的决策芯片包括:4.1 高级控制单元(High-level Control Unit)高级控制单元是一种专用的芯片,用于实现的高级决策和规划算法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IRMCK/F171-灵活易用的电机控制芯片 IRMCK/F171 灵活易用的电机控制芯片

国际整流器公司 2012-1-11

内容

• 概述 概 • 传统方案存在的问题 • IR的解决方案:简单易用的电机控制 芯片IRMCF171 • 方案辅助工具和测试结果 • 结论

概述

• 全球能源短缺导致越来越严格的政府节能规章出 台 • 在中国 能效标签制度的实施以及能效标准的不 在中国,能效标签制度的实施以及能效标准的不 断提高使很多电器转向变频控制 • 变频空调已经完全确立了市场的主导地位 • 家电的变频化趋势也越来越明确,电机调速市场 竞争将更加激烈,产品更新的周期越来越短。

随 之而来的新产品研发风险也越来越大 之而来的新产品研发 险也越来越大 • 节能热点:

– – – – 高效率永磁电机 无位置传感正弦波控制 宽的调速范围 低的振动和噪声

传统方案存在的问题

• • • • 大容量存储单元的高速DSP或32位单片机 软件算法复杂,控制器计算任务繁重 软件算法复杂 控制器计算任务繁重 对于传统的软件编程控制方案,完成电机控制算法已经很复杂, 对于系统设计人员的要求很高

1. 2. 3. 熟悉实时的FOC控制算法,熟悉相关的外设; 熟悉DSP或32位RISC的C或汇编语言编程; 熟悉各种数模混合电路,高压电路和功率开关电路.

•

•

开发周期长,开发成本和开发风险都很高

后续的软件维护成本高

电机控制系统框图

IR电机控制IC-IRMCF171

电机控制器: IRMCK/F171

模数控制器IC

• MCU (微控制器) - 60MIPS 8bit 微处理器 • MCE (运动控制引擎) – 可配置的控制模块集 • ASE (模拟信号引擎) – 信号调理和A/D转换

IRMCK/F171内部功能框图

MCE™ (Motion Control Engine)

•不需要写代码 不需要写代码 •图形化模块编辑 •硬件实现算法

无传感FOC控制

速度环和弱磁控制环路

运动控制引擎TM

– MCE 作为单片机的一个外部设备,控制架 构,参数设置由共享RAM里的数据决定. 决 – 独立于单片机快速执行电机控制算法 – 特点:

• • • • • • • • 不需要编程 专用控制模块 小的运动控制序列控制器 丰富的运动控制外设 (低损耗PWM, 负母线或桥臂 电阻电流重构) 双端口RAM与应用层交换信息 多种保护功能 内嵌过流保护比较器 硬件关断脚 (GATEKILL)

Dual Port ua o t RAM

Motion Control Bus

MCE 内部框图

6

To Motor 1 gate drive GATEKILL

Low Loss SVPWM

Motion Control Modules M d l

PFC PWM

To PFC gate drive PFC GATEKILL

Single shunt current reconst

IFB (Motor 1)

MCE Program g RAM

A/D MUX S/H

IFB (PFC) DC bus AC input Analog Ref

Motion Control Sequencer

ASE (模拟信号引擎)

IRMCF171特点

特点

()

•运动控制引擎(MCE TM) 独立完成复杂的电机控制算法–可靠的底层控制模块

•FOC 模块

–磁通估算器和角度锁相环

–(直轴和交轴) 电流调节器

电流调节

–Catching spin功能

–制动、弱磁

•低损耗空间矢量PWM

–开放的速度环方便用户灵活设计

–模拟信号引擎提供功率电路和控制器之间完整的接口•直流负母线电流反馈,电机相电流重构

•辅助的模拟信号通道

•嵌入8051单片机方便用户实现单芯片系统控制–与MCE共享4KBRAM

–多路数字I/O口

–JTAG口调试8051软件.

自检功能符合标准

–自检功能----符合IEC标准

•IRMCK171为对应的OTP版

驱动参数计算工具•MCEWizard

•IR 提供MCE控制电机所需配置寄

存器的计算工具

•您只需输入简单的电机参数和应用

参数,MCEWizard会自动为您导出

所内部寄存器值。

.

•所需参数可以从电机厂家获得,IR

也给出用户自己手工测量的方法。

驱动调试工具

MCEDesigner

•使用该工具测试调整你的电

机驱动参数。

•允许用户自己定义运行过程

或速度曲线等。

•在电机运行过程中随时调整

参数。

参数

•使用示波器功能,可以实时

观察系统各个控制节点的变

化情况,为高效率的优化控

制参数提供便利。

重构的电机相电流

总结

•无需编程

•直流负母线电阻或桥臂电阻采样

•低损耗SVPWM

•Catching spin

•弱磁控制和零矢量制动

•过调制限制

•齐全的保护功能------过欠压,过流,缺相等

•方便直观的调试工具

•有对应的OTP版,并具有自测功能,符合IEC 60335-1 Edition 4.2 –Class B。