译码器实现逻辑电路

74LS153译码器组合逻辑电路设计案例分析

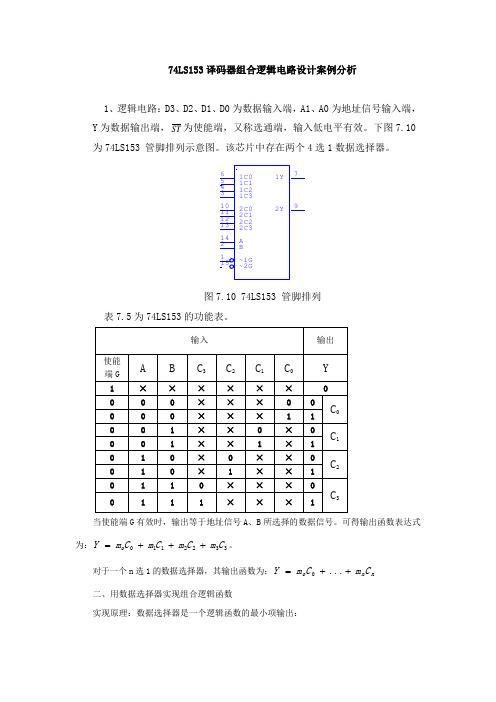

74LS153译码器组合逻辑电路设计案例分析1、逻辑电路:D3、D2、D1、D0为数据输入端,A1、A0为地址信号输入端,Y 为数据输出端,ST 为使能端,又称选通端,输入低电平有效。

下图7.10为74LS153 管脚排列示意图。

该芯片中存在两个4选1数据选择器。

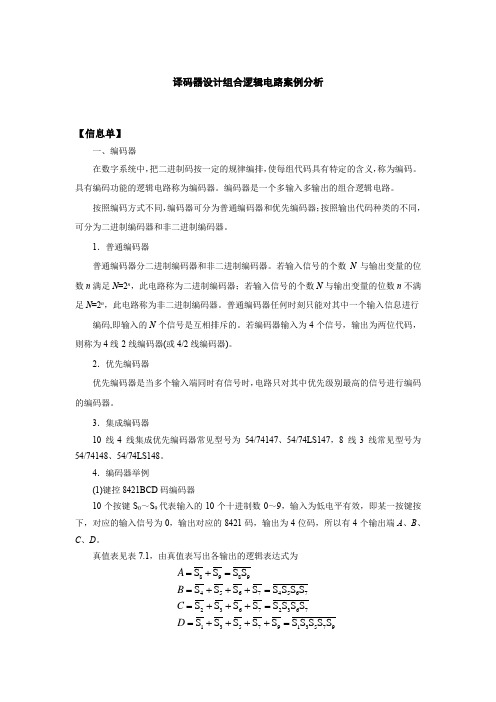

2Y92C0102C1112C2122C313A 14B 2~1G 11Y71C061C151C241C33~2G15图7.10 74LS153 管脚排列表7.5为74LS153的功能表。

当使能端G 有效时,输出等于地址信号A 、B 所选择的数据信号。

可得输出函数表达式为:3322110C m C m C m C m Y o +++=。

对于一个n 选1的数据选择器,其输出函数为:n n o C m C m Y ++=...0 二、用数据选择器实现组合逻辑函数实现原理:数据选择器是一个逻辑函数的最小项输出:∑-===++=1200...n i ii n n o c m C m C m Y 而任何一个n 位变量的逻辑函数都可变换为最小项之和的标准式。

对照函数表达式和相应的数据选择器输出函数表达式,可以实现用数据选择器来表示逻辑函数。

实现步骤:(1)根据函数变量选择合适的数据选择器,一般变量个数n 个,选择2n 选1的数据选择器。

(2)将被表示的函数转换成标准与或表达式。

(3)写出选择的数据选择器的输出函数。

(4)对比两函数,使数据选择器的地址端和函数变量一一对应(高位对高位),表达式中出现的最小项相应的输入数据C 为1,否则为0。

(5)画逻辑电路图。

例:用数据选择器和门电路实现AC AB Y +=的组合逻辑电路。

(1) 选择数据选择器:选8选1数据选择器74LS151。

(2) 标准与或表达式756m m m ABC C B A C AB AC AB Y '+'+'=++=+=' (3)写出数据选择器输出函数776655443322110C m C m C m C m C m C m C m C m Y o +++++++=(4)对照上述两表达式,令A=A2,B=A1,C=A0,则n n m m '=,所以,C 0=C 1=C 2=C 3=C 4=0;C 5=C 6=C 7=1。

4.3常用组合逻辑电路(3线—8线译码器 138)

用二极管与门阵列组成的3 线-8线译码器

Y0 A2' A1' A0' m0 Y1 A2' A1' A0 m1 Y2 A2' A1 A0' m2 ... Y7 A2 A1 A0 m7

附加 控制端

集成译码器实例:74HC138

低电平 输出

S S1S 2S3 S1(S 2'S3')'

• 利用附加控制端进行扩展 例:用74HC138(3线—8线译码器) 构成 4线—16线译码器

D3=0

Z

' i

mi'

D3=1

二、二-十进制译码器 二-十进制译码器的逻辑功能是将输入的BCD代 码译成10个高、低电平输出信号。 如74HC42

Yi mi (i 0 ~ 9)

四、 用译码器设计组合逻辑电路

集成译码器实例:74HC138

附加 控制端

Yi' ( S mi )'

S 1时 Yi' mi'

低电平 输出

S 0时,输出为全1。

74HC138的功能表:

输

入

输

出

S1

S

' 2

S3'

A2

A1

A0

Y7' Y6' Y5' Y4' Y3' Y2' Y1' Y0'

0

X XXX1 1 1 1 1 1 1 1

将要实现的输出逻辑函数的最小项之和的形式两次 取反,即

Z1 ((m3 m4 m5 m6 )) (m3 m4 m5 m6 ) Z2 ((m1 m3 m7 )) (m1 m3 m7 ) Z3 ((m2 m3 m5 )) (m2 m3 m5 ) Z4 ((m0 m2 m4 m7 )) (m0 m2 m4 m7 )

译码器设计组合逻辑电路的方法步骤

译码器设计组合逻辑电路的方法步骤宝子,今天咱来唠唠用译码器设计组合逻辑电路这事儿。

译码器呢,就像是一个翻译官。

那怎么用它来设计组合逻辑电路呢?咱得先了解下要实现的逻辑功能是啥。

比如说,要实现一个判断输入信号是不是满足某个特定关系的功能。

这就好比你要知道自己要做一个啥样的小发明一样。

接着呢,要确定输入变量的个数。

这就像是你要知道自己有多少种原料可以用。

如果有3个输入变量,那就得找合适的3 - 8线译码器之类的。

然后呀,要列出逻辑函数的真值表。

这个真值表就像是一个规则手册。

把输入变量的各种可能取值,以及对应的输出结果都写清楚。

这就好比把每种原料组合能做出啥东西都写下来。

再之后呢,把逻辑函数用最小项表示出来。

这一步就像是把你的小发明的原理用一种特定的数学语言描述出来。

之后就是关键啦,要把译码器的输出和逻辑函数联系起来。

译码器的输出端那些信号就像是一个个小助手,你要根据逻辑函数的要求,把这些小助手合理地组合起来。

比如说,可能需要把某些输出端通过与门或者或门连接起来,就像把小助手们按照你的计划组队一样。

在这个过程中,可能会遇到一些小麻烦哦。

比如说,可能会发现译码器的输出和你想要的逻辑函数不太匹配。

这时候别慌,就像你做手工的时候发现材料有点不对一样,可以调整下连接方式或者再思考下逻辑关系。

最后呢,画出电路图。

这个电路图就是你的设计成果啦,就像你把自己的小发明从想法变成了实实在在的图纸一样。

宝子,用译码器设计组合逻辑电路其实也不是很难啦,只要一步一步来,就像搭积木一样,慢慢就能把它搞定啦。

而且在这个过程中,你还能发现很多逻辑的小乐趣呢。

要是遇到问题也不怕,多试几次,总能成功的哦。

译码器设计组合逻辑电路案例分析

译码器设计组合逻辑电路案例分析【信息单】一、编码器在数字系统中,把二进制码按一定的规律编排,使每组代码具有特定的含义,称为编码。

具有编码功能的逻辑电路称为编码器。

编码器是一个多输入多输出的组合逻辑电路。

按照编码方式不同,编码器可分为普通编码器和优先编码器;按照输出代码种类的不同,可分为二进制编码器和非二进制编码器。

1.普通编码器普通编码器分二进制编码器和非二进制编码器。

若输入信号的个数N 与输出变量的位数n 满足N =2n ,此电路称为二进制编码器;若输入信号的个数N 与输出变量的位数n 不满足N =2n ,此电路称为非二进制编码器。

普通编码器任何时刻只能对其中一个输入信息进行编码,即输入的N 个信号是互相排斥的。

若编码器输入为4个信号,输出为两位代码,则称为4线-2线编码器(或4/2线编码器)。

2.优先编码器优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最高的信号进行编码的编码器。

3.集成编码器10线-4线集成优先编码器常见型号为54/74147、54/74LS147,8线-3线常见型号为54/74148、54/74LS148。

4.编码器举例(1)键控8421BCD 码编码器10个按键S 0~S 9代表输入的10个十进制数0~9,输入为低电平有效,即某一按键按下,对应的输入信号为0,输出对应的8421码,输出为4位码,所以有4个输出端A 、B 、C 、D 。

真值表见表7.1,由真值表写出各输出的逻辑表达式为 9898S S S S =+=A76547654S S S S S S S S =+++=B 76327632S S S S S S S S =+++=C 9753197531S S S S S S S S S S =++++=D表7.1键控8421BCD 码编码器真值表(2)二进制编码器用n 位二进制代码对2n 个信号进行编码的电路称为二进制编码器。

3位二进制编码器有 8个输入端3个输出端,所以常称为8线—3线编码器,其功能真值表见表7.2,输入为高电平有效。

38译码器实现逻辑电路

Z 2 BC A' B 'C Z 3 A' B AB 'C Z 4 A' BC ' B 'C ' ABC

' ' ' ' ' Z1 AC ' A' BC AB 'C m(3,4,5,6) Z1 m (3,4,5,6) ( m3 m4 m5 m6 )

附加 控制端

S S3 S2 S1

低电平 输出

Yi' ( S mi )'

74HC138的功能表:

输 入

《数字电子技术基础》第五版

输

出

S1

0 X 1 1 1 1 1 1 1 1

' ' A2 A1 A0 Y ' Y ' Y ' Y ' Y ' Y ' Y ' Y ' S2 S3 7 6 5 4 3 2 1 0

1 1 1 1 1 0 1 1 1 1

1 1 1 1 0 1 1 1 1 1

1 1 1 0 1 1 1 1 1 1

1 1 0 1 1 1 1 1 1 1

《数字电子技术基础》第五版

• 利用附加控制端进行扩展 例: 用74HC138(3线—8线译码器)

4线—16线译码器

《数字电子技术基础》第五版

D3=0

1. 基本原理 3位二进制译码器给出3变量的全部最小项; 。。。 n位二进制译码器给出n变量的全部最小项; 任意函数 将n位二进制译码输出的最小项组合起来,可获 得任何形式的输入变量不大于n的组合函数

Y ∑ mi

《数字电子技术基础》第五版

2. 举例

实验-译码器

实验八译码器及其应用一、实验目的:1、掌握中规模集成译码器逻辑功能分析及测试方法;2、学会中规模集成译码器的连接使用方法;3、熟悉数码管的使用方法。

二、实验原理:1、译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有着广泛的用途,不仅适用于代码的转换,终端的数字显示,而且还适用于数据分配,存储器寻址和组合控制信号等方面。

2、译码器可分为通用译码器和显示译码器两大类。

通用译码器又分为变量译码器和代码变换译码器。

(1)、变量译码器(又称二进制译码器),用以表示输入变量的状态,如2/4线译码器、3/8线译码器和4/16线译码器。

若有n个输入变量,则有2n个不同的状态组合,就有2n 个输出端供其使用。

而每一个输出状态所代表的函数就对应一个n变量的最小项表达式。

图8-1 3-8译码器74LS138逻辑图及列脚排列以3/8线译码器74LS138为例进行分析,图8-1(a)、(b)分别为其逻辑图和引脚排列图。

A2、A1、A0为地址输入端,Y0~Y7是译码器输出端,S1、S2、S3是使能端。

表8-1为74LS138功能表,当S1=1,S2+S3=0时,器件使能端有效,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(为1)输出。

当S1=0,S2+S3=X时或S1=X,S2+S3=1时,译码器被禁止,所有输出同时为1。

二进制译码器实际上也就是负脉冲输出的脉冲分配器。

若利用使能端中的一个输入端输入数据信息,器件就成为一个数据分配器(又称多路分配器),如图8-2所示。

若在S1输入端输入数据信息,S2=S3=0,地址码所对应的输出是S1数据信息的反码;若从S2输入端输入数据信息,令S1=1,S3=0,地址码所对应的输出就是S2端数据信息的原码。

若数据信息是时钟脉冲,则数据分配器便成为时钟脉冲分配器。

根据输入地址的不同组合译出唯一的地址,故可用作地址译码器。

译码器、数据选择实现组合逻辑电路的设计(完整电子教案)

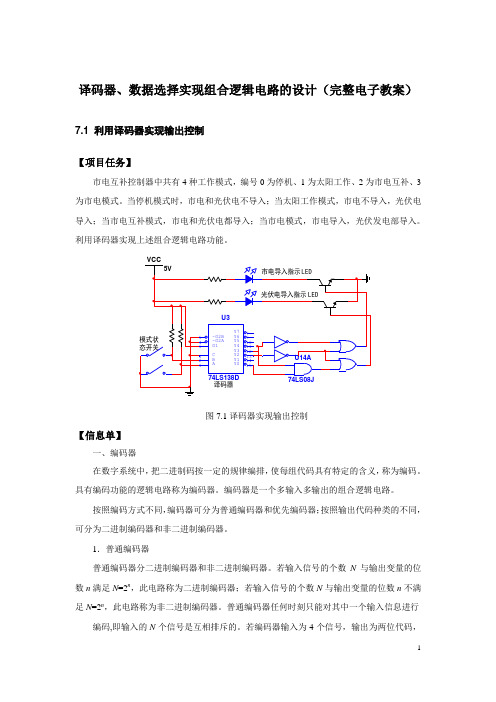

译码器、数据选择实现组合逻辑电路的设计(完整电子教案)7.1 利用译码器实现输出控制【项目任务】市电互补控制器中共有4种工作模式,编号0为停机、1为太阳工作、2为市电互补、3为市电模式。

当停机模式时,市电和光伏电不导入;当太阳工作模式,市电不导入,光伏电导入;当市电互补模式,市电和光伏电都导入;当市电模式,市电导入,光伏发电部导入。

利用译码器实现上述组合逻辑电路功能。

图7.1译码器实现输出控制【信息单】一、编码器在数字系统中,把二进制码按一定的规律编排,使每组代码具有特定的含义,称为编码。

具有编码功能的逻辑电路称为编码器。

编码器是一个多输入多输出的组合逻辑电路。

按照编码方式不同,编码器可分为普通编码器和优先编码器;按照输出代码种类的不同,可分为二进制编码器和非二进制编码器。

1.普通编码器普通编码器分二进制编码器和非二进制编码器。

若输入信号的个数N与输出变量的位数n满足N=2n,此电路称为二进制编码器;若输入信号的个数N与输出变量的位数n不满足N=2n,此电路称为非二进制编码器。

普通编码器任何时刻只能对其中一个输入信息进行编码,即输入的N个信号是互相排斥的。

若编码器输入为4个信号,输出为两位代码,则称为4线-2线编码器(或4/2线编码器)。

2.优先编码器优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最高的信号进行编码的编码器。

3.集成编码器10线-4线集成优先编码器常见型号为54/74147、54/74LS147,8线-3线常见型号为54/74148、54/74LS148。

4.编码器举例(1)键控8421BCD 码编码器10个按键S 0~S 9代表输入的10个十进制数0~9,输入为低电平有效,即某一按键按下,对应的输入信号为0,输出对应的8421码,输出为4位码,所以有4个输出端A 、B 、C 、D 。

真值表见表7.1,由真值表写出各输出的逻辑表达式为 9898S S S S =+=A76547654S S S S S S S S =+++=B 76327632S S S S S S S S =+++=C 9753197531S S S S S S S S S S =++++=D表7.1键控8421BCD 码编码器真值表(2)二进制编码器用n 位二进制代码对2n 个信号进行编码的电路称为二进制编码器。

实验4 用译码器实现组合逻辑电路

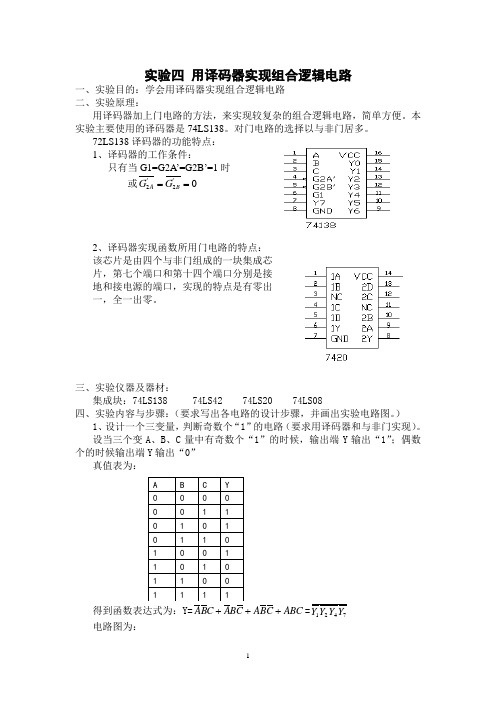

实验四 用译码器实现组合逻辑电路一、实验目的:学会用译码器实现组合逻辑电路 二、实验原理:用译码器加上门电路的方法,来实现较复杂的组合逻辑电路,简单方便。

本实验主要使用的译码器是74LS138。

对门电路的选择以与非门居多。

72LS138译码器的功能特点: 1、译码器的工作条件:只有当G1=G2A ’=G2B ’=1时或0'2'2==B A G G2、译码器实现函数所用门电路的特点:该芯片是由四个与非门组成的一块集成芯 片,第七个端口和第十四个端口分别是接 地和接电源的端口,实现的特点是有零出 一,全一出零。

三、实验仪器及器材:集成块:74LS138 74LS42 74LS20 74LS08 四、实验内容与步骤:(要求写出各电路的设计步骤,并画出实验电路图。

)1、设计一个三变量,判断奇数个“1”的电路(要求用译码器和与非门实现)。

设当三个变A 、B 、C 量中有奇数个“1”的时候,输出端Y 输出“1”;偶数个的时候输出端Y 输出“0”真值表为:得到函数表达式为:Y=ABC C B A C B A C B A +++=7421Y Y Y Y电路图为:些设备由和两台发电机供电,两台发电机的最大输出功率分别为10W 和30W ,要求设计一个逻辑电路以最节约能源的方式启、停发电机,来控制三台设备的运转、停止(要求用译码器和与非门、与门实现)。

设甲,乙分别为10W ,20W 的发电机;1为工作状态,0为不工作状态。

得到真值表为:得到函数表达式为:甲=ABC C B A C B A ++=742Y Y Y乙=ABC C AB C B A BC A C B A ++++=7631Y Y Y Y Y3、设计一个全加器(要求用译码器和与非门实现)。

Mi-1表示来自低位的进位(0表示无进位,1表示有进位);Ai 表示加数;Bi 表示被加数;Y 表示Ai+Bi 的和;N 表示向高位进位(0表示无进位,1表示有进位)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《数字电子技术基础》第五版

逻辑表达式:

用电路进行实现

《数字电子技术基础》第五版

集成译码器实例:74HC138

附加 控制端

S S3S2 S1

低电平 输出

Yi' ( S mi )'

74HC138的功能表:

《数字电子技术基础》第五版

输

入

输

出

S1

S

' 2

S

' 3

A2

A1

A0 Y7'

Y6'

Y5'

Y4'

Y3'

Y2'

Y1'

Y0'

0

X XXX1 1 1 1 1 1 1 1

X

1 XXX1 1 1 1 1 1 1 1

1

0 00011111110

1

0 00111111101

1

0 0101111101110 01111110111

1

0 10011101111

1

0 10111011111

m1 m3 m5 m7 CBA CBA CBA CBA

Z2 BC A'B'C m(1,3,7)

Z2 m(1,3,7) (m1'm3' m7' )'

Z3 A'B AB'C m(2,3,5)

Z3 m(2,3,5) (m2' m3' m5' )'

Z4 A'BC ' B'C ' ABC m(0,2,4,7) Z4 m(0,2,4,7) (m0' m2' m4' m7' )'

《数字电子技术基础》第五版 例:写出由74HC138和门电路组成的组合逻辑电路的表达式。

Y2

Y1

Y1 Y0 Y2 Y4 Y6 m0 m2 m4 m6

m0 m2 m4 m6 CBA CBA CBA CBA

《数字电子技术基础》第五版

Y2

Y1

Y2 Y1Y3 Y5 Y7 m1 m3 m5 m7

001 0000001 0

01 0000001 00

01 1 00001 000

1 000001 0000

1 01 001 00000

1 1 001 000000

1 1 1 1 0000000

真值表 Y0 A2' A1' A0' m0 Y1 A2' A1' A0 m1 Y2 A2' A1 A0' m2 ... Y7 A2 A1 A0 m7

1

0 11010111111

1

0 11101111111

《数字电子技术基础》第五版

• 利用附加控制端进行扩展 例: 用74HC138(3线—8线译码器)

4线—16线译码器

D3=0

Z

' i

mi'

《数字电子技术基础》第五版 D3=1

二、二—十进制译码器

《数字电子技术基础》第五版

• 将输入BCD码的10个代码译成10个高、低电平的输出信号 BCD码以外的伪码,输出均无低电平信号产生

• 例:74HC42

Yi' mi' (i 0 ~ 9)

《数字电子技术基础》第五版

三、用译码器设计组合逻辑电路

1. 基本原理 3位二进制译码器给出3变量的全部最小项; 。。。 n位二进制译码器给出n变量的全部最小项;

任意函数 将n位二进制译码输出的最小项组合起来,可获 得任何形式的输入变量不大于n的组合函数

Y ∑m i

《数字电子技术基础》第五版

2. 举例

例:利用74HC138设计一个多输出的组合逻辑电路,输出 逻辑函数式为:

Z1 AC ' A'BC AB'C Z2 BC A'B'C Z3 A'B AB'C Z4 A'BC ' B'C ' ABC

Z1 AC ' A'BC AB'C m(3,4,5,6) Z1 m(3,4,5,6) (m3' m4' m5' m6' )'

《数字电子技术基础》第五版

4.3.2 译码器

• 译码:将每个输入的二进制代码译成对应的输出高、低 电平信号。

• 常用的有:二进制译码器,二-十进制译码器,显示译码

器等

输入

输出

一、二进制译码器

A2 A1 A0 Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0

例:3线—8线译码器 0 0 0 0 0 0 0 0 0 0 1