第7章 定时计数器82538254

第7章 常用的可编程接口芯片8253-7.3

微机原理与接口技术 (1)方式0(计数结束中断)和方式4(软件触发选通) 软件触发计数方式 1)启动/停止:当写入计数值,就可启动计数器减1计数。 减1至0,停止计数。 2)输出: 方式0-写入CW后,OUT低,减1至0,OUT变高。 方式4-写入CW后,OUT高,减1至0,OUT输出负脉冲。 3)GATE作用:GATE=1,允许计数;GATE=0禁止计数。 4)计数过程中CR变化:按新的计数值计数。 5)重新计数:不能。

;计数器1初始化

;计数器2初始化

网络与信息工程系

微机原理与接口技术

7. 8253的工作方式

总体原则:

1)控制字CW写入计数器,所有的控制逻辑电路立即复位, 输出端进入初始状态。

2)计数初始值写入后,经过一个CLK脉冲,才由计数初值 寄存器CR送入计数执行部件CE开始计数。在输入脉冲CLK 的下降沿,计数器作减1计数。计数器的最大初始值是

硬件启动。

网络与信息工程系

微机原理与接口技术

4.外部引脚

通道的定时/计数脉 冲输入引脚 。

通道的门控信号输 入引脚,门控信号 的作用与通道的工 作方式有关。

通道的定时/计数到 信号输出引脚,输 出信号的形式由通 道工作方式确定。

网络与信息工程系

微机原理与接口技术 控制信号与执行的操作之间的对应关系

网络与信息工程系

微机原理与接口技术

网络与信息工程系

微机原理与接口技术

3. 内部结构

实现与CPU数据总线连接的8 位双向三态缓冲器。用以传 送CPU向8253的控制信息、 数据信息以及CPU从8253读 取的状态信息。 三个独立的 ,结构相同 接收CPU发来的片选信号、 的计数器/定时器通道, 地址信号和读写信号以实现 每一个通道包含一个16 片选、内部通道选择以及对 位的计数寄存器 ,用以 读/写操作进行控制。 存放计数初始值 ,和 一 个16位的减法计数器和 由CPU写入控制字,以决定 一个16位的锁存器。通道的工作方式,此寄存器 只能写入,不能读出。

定时计数器8253

古晓辉制作

2 写入计数值

示例

选择二进制时

计数值范围:0000H~FFFFH 0000H是最大值,代表65536

选择十进制(BCD码)

计数值范围:0000~9999 0000代表最大值10000

计数值写入计数器各自的I/O地址

古晓辉制作

3 读取计数值

示例

对8位数据线,读取16位计数值需分两次 计数在不断进行,应该将当前计数值先行 锁存,然后读取:

0

OUT

④ ② ① ⑥ ⑤ 计 数 设 设 计 计 值 定 定 数 数 送 计 工 结 过 入 数 作 束 程 计 初 方 数 值 式 器

古晓辉制作

古晓辉制作

方式1可重复触发的单稳方式

① ② 4 ④ ⑤ ⑥

④

⑥ ② ⑤ ① 计 ③ 数 计 设 计 设 值 硬 数 定 数 定 送 件 结 计 过 工 入 启 束 数 程 作 计 动 初 数方 值 器式

计数初值

8253内部包含3个功能完全相同的通道,每个通道内部 设有一个16位计数器,可以进行二进制或十进制(BCD码) 计数。 8253是一种减1计数器,因此在开始计数(定时)之前,一 定要根据计数(定时)的要求,先算出计数初值(定时常数), 并装入计数初值寄存器。

定时常数=要求定时的时间/时钟脉冲的周期

古晓辉制作

9.2.2 8253的工作模式

方式0——计数结束产生中断 方式1——可重复触发的单稳态触发器 方式2——分频器 方式3——方波发生器 方式4——软件触发的选通信号发生器 方式5——硬件触发的选通信号发生器

古晓辉制作

方式0 计数结束中断

① ② ④ 4 ⑤ ⑥

WR CLK GATE

方式0

4 3 2 1

(计数初值)可编程定时器计数器8253

8253-5的工作方式

②GATE=1计数进行,GATE=0计数停止,且下一个CLK计数 器重新赋初值,GATE变为高电平,计数重新开始。

29

8253-5的工作方式

③ 计数期间送入新值,本周期继续进行,下一个周期按 新值计数操作。

不用重复置数。计数器能够连续工作,输出OUT是输 入CLK的n(初值)分频。

31

8253-5的工作方式

方式3的时序波形: ① 写入CW后OUT变为高电平,输入时间常数后,下一个时 钟开始计数,计到一半时输出变为低电平,计到终值时重 新变为高电平,并开始下一次计数过程。

32

8253-5的工作方式

② 若N为偶数,高低电平持续时间相等;若为奇数,则 高电平持续时间为(N+1)/2,低电平持续时间为(N-1) /2。

35

8253-5的工作方式

①写入CW后OUT为高电平,输入时间常数后,下一个CLK 开始计数,计数器为0时,输出一个周期负脉冲,并停止 操作。

36

8253-5的工作方式

②GATE=1允许计数,GATE=0禁止计数。

37

8253-5的工作方式

③计数期间送入新的时间常数,则下一个时钟按新值重新 计数。

25

8253-5的工作方式

④计数过程中,GATE触发沿提前到来,在下一个CLK的下 降沿,计数器开始重新计数,这将使输出单稳脉冲比原 先设定的计数值加宽。

26

8253-5的工作方式

(3)方式2—速率发生器(Rate Genenator) 方式2能产生周期性的定时信号,称为速率发生器,

又称为N分频方式和周期性定时器方式。

数频率,N为计数初值。

42

8253-5的工作方式

微机接口实验8254定时计数器实验

实验七8254定时/计数器实验1 实验目的(1) 掌握8254的典型应用电路接法。

(2) 掌握8254的工作方式及应用编程。

2 实验设备PC微机一台、TD-PIT+实验系统一套、示波器。

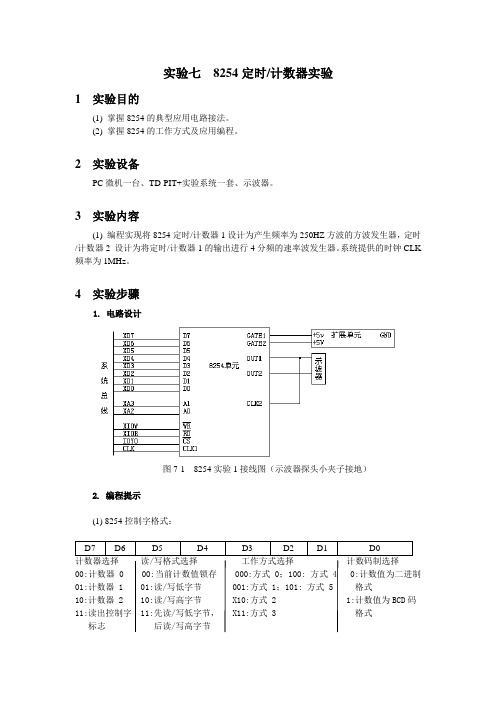

3 实验内容(1) 编程实现将8254定时/计数器1设计为产生频率为250HZ方波的方波发生器,定时/计数器2 设计为将定时/计数器1的输出进行4分频的速率波发生器。

系统提供的时钟CLK 频率为1MHz。

4 实验步骤1. 电路设计图7-1 8254实验1接线图(示波器探头小夹子接地)2. 编程提示(1) 8254控制字格式:计数器选择读/写格式选择工作方式选择计数码制选择00:计数器 0 00:当前计数值锁存 000:方式 0;100: 方式 4 0:计数值为二进制01:计数器 1 01:读/写低字节 001:方式 1;101: 方式 5 格式10:计数器 2 10:读/写高字节 X10:方式 2 1:计数值为BCD码11:读出控制字 11:先读/写低字节, X11:方式 3 格式标志后读/写高字节(2)计数初值N = f CLK/f OUT = T OUT/T CLK(3) 8254的初始化编程步骤①送控制字到控制端口;②送计数初值到计数器端口。

设置初始值时,应与控制字中的格式规定一致,当控制字中设置只读/写高字节或只读/写低字节时,初始值是1字节。

当控制字中设置先读/写低字节后读/写高字节时,初始值为2字节,分两次传送。

5 实验代码IOY0 EQU 0DC00HCOUNT0 EQU IOY0+0*4COUNT1 EQU IOY0+1*4COUNT2 EQU IOY0+2*4MODE EQU IOY0+3*4STACK1 SEGMENT STACKDW 256 DUP(?)STACK1 ENDSCODE SEGMENTASSUME CS:CODESTART:MOV DX,MODEMOV AL,01110110BOUT DX,ALMOV DX,COUNT1MOV AX,4000DOUT DX,ALMOV AL,AHOUT DX,ALMOV DX,MODEMOV AL,10010110BOUT DX,ALMOV DX,COUNT2MOV AL,3HOUT DX,ALMOV AH,4CHINT 21HCODE ENDSEND START。

第七章定时_计数器8253

4

3

2

1

3

2

1

GATE=1 4 0 3 2

本章首页

7.2 定时/计数器8253-5/8254-2(续) 定时/计数器8253-5/82544)3方式——周期性方波输出 方式——周期性方波输出 ——

与方式2一样具有自动重新装载计 自动重新装载计 数初值的功能,与方式2的区别仅 数初值 触发方式: 触发 触发方式:写入初值后,WR= 在于输出波形不同 输出波形: 输出波形:输出占空比为1:1或近似1:1的方波。初值为偶数时,前半周为高电 平,后半周为低电平;初值为奇数时,前一半加1的计数过程中为高电平 GATE作用 作用: ,停止,= ,重新开始 GATE作用:=1,允许;=0,禁止;= 计数过程中写入新初值: 计数过程中写入新初值:计数器回零,输出完整的方波后,再开始新过程

A1A0 选中通道 0 0 0 1 1 0 1 1 T0 T1 T2 T3

A0~A1:端口选择线,接收CPU的低位地址,用于8253被选中时,选择内部端口 GATE0~GATE2:T0~T2的门控信号,对计数过程进行控制,具体作用视方式而定 CLK0~CLK2:T0~T2的脉冲输入,允许计数时,8253的Ti对CLKi输入的脉冲进行减 1计数 OUT0~OUT2:T0~T2的输出信号,Ti减为0,OUTi输出有效,输出波形视方式而定

16位计数初值寄存器 装入/读出初值 LSB MSB 通道的内部结构

本章首页

7.2 定时/计数器8253-5/8254-2(续) 定时/计数器8253-5/8254读写控制逻辑: 读写控制逻辑:接收CPU的地址、读/写信号,选中一个端口并确定传送方向

2. 计数初值 操作 WR RD A1 A0 PC机 实验台 逆 减 0 1 0 0 加载T0(向T0写入初值) 40H 304H 8253/8254是逆计数器(减1 0 1 0 1 加载T1(向T1写入初值) 41H 305H 计数器),减1计数器减为0 时输出有效 0 1 1 0 加载T2(向T2写入初值) 42H 306H

微机原理实验 可编程定时器计数器82548253实验

图2 8253/8254定时器/计数器实验连线图

六、实验源程序清单

CODE SEGMENT

ASSUME CS:CODE

ORG 100H

START:MOV AL, 00010110B;控制字00-计数器0,01-低8位,011-方式3,0-二进制

OUT 03H,AL;将控制字写入控制寄存器

实验报告(45)

总分

指导教师签字:

年月日

备注:

注:1、报告内的项目或内容设置,可根据实际情况加以调整和补充。

2、教师批改学生实验报告时间应在学生提交实验报告时间后10日内。

图1可编程定时器/计数器8253/8254原理图

(2).计数器都有6种工作方式:

方式0—计数过程结束时中断;

方式1—可编程的单拍脉冲;

方式2—频率发生器;

方式3—方波发生器;

方式4—软件触发;

方式5—硬件触发。

(3)6种工作方式主要有5点不同:

一是启动计数器的触发方式和时刻不同;二是计数过程中门控信号GATE对计数操作的影响不同;三是OUT输出的波形不同;四是在计数过程中重新写入计数初值对计数过程的影响不同;五是计数过程结束,减法计数器是否恢复计数初值并自动重复计数过程的不同。

九、实验总结

硬件实验相对来说趣味性大了很多,同时也使得程序没那么复杂不过存在的问题突出表现于受到硬件实验条件的制约,硬件上的小问题就有可能导致不能出显预想的结果这也就使得在硬件连接上要很小心。

十、思考题

1.若8254模块选通线CS连到MCU主模块的地址A12,则应如何修改程序?

答:改变了存储芯片的地址范围所以将程序对应的地址范围改过即可。接A12对应地址范围是6800~6FFFH;接A14对应地址范围是3800~3FFFH。

可编程定时器/计数器i8253

③ 在计数过程中可以改变计数初值,这对正在进行的计数 过程没有影响。但当计数到1时输出变低,过一个CLK周期输 出又变高,计数器将按新的计数值计数。所以对方式2改变计 数初值时,在下一次计数有效。 (4) 方式3——方波发生器。 在方式3时,当CPU设置控制字后,输出为高电平。在写 入计数初值后就开始计数,输出保持为高。当计数到一半计数 初值时,输出变为低,直至计数到0,输出又变为高,重新开 始计数。 方式3与方式2的输出都是周期性的,它们的主要区别是: 方式3在计数过程中的输出有一半时间为高电平,另一半时间 为低电平。

00: 计数器锁存 01: 只读/写计数器低字节 10: 只读/写计数器高字节 11: 先读/写计数器低字节, 后读/写高字节

图 7- 29 8253/8254控制字的格式

SC1、SC0:计数器选择位。这两位表示这个控制字是对哪 一个计数器设置的。 00——计数器0;01——计数器1;10——计数器2;11——非法 选择。 RW1、RW0:数据读/写格式选择位。CPU在对计数器写入 初值和读取它们的当前值时,有几种不同的格式,由这两位来 决定。 00——将计数器当前值锁存于输出锁存器中,以便读出; 01——只读/写计数器的低8位,写入时高8位自动设置为0; 10— —只读/写计数器的高8位,写入时低8位自动设置为0;11——对 16位计数器进行两次读/写操作,低字节在前,高字节在后, 两次操作的地址相同。

D7 SC1

D6 SC0

D5

D4

D3 M2

D2 M1

D1 M0

D0 BCD 1: BCD码计数 0: 二进制计数 000: 方式0 001: 方式1 10: 方式2 11: 方式3 100: 方式4 101: 方式5

第7章可编程计数器8253

方式0 计数结束中断

① ② ④ 4 ⑤ ⑥

WR CLK GATE

方式0

4 3 2 1

0

OUT

④ ② ① ⑥ ⑤ 计 数 设 设 计 计 值 定 定 数 数 送 计 工 结 过 入 数 作 束 程 计 初 方 数 值 式 器

8253方式0的GATE作用时序

8253方式0 计数期间写入新的计数值的时序

8253工作方式2—比率发生器

(1) 结果特点:产生连续的负脉冲信号,负脉冲宽度等于一 个时钟周期,脉冲周期可由软件设定,脉冲周期=计数值× 时钟周期 (2)过程特点: ①控制字写入:OUT=1 ②计数值写入:OUT=1 ③启动方式:两种。一是硬件启动:GATE上调沿启动。二 是软件启动:写入计数值启动。(此时GATE=1) ④计数期间:OUT为高电平(OUT=1),但在CE由1减到 0的计数中,OUT输出一个负脉冲,宽度为一个时钟周期。 ⑤计数为0时:OUT变为高电平(OUT=1),开始下一个 周期的计数。

8253方式1—可编程单稳态输出方式

⑦GATE作用:GATE=0或=1时,不影响计数,但出

现上跳沿则重新启动计数器,按最新计数初值开始 计数,若在计数尚未结束时,就出现了上调沿,则 重新计数。因此,使输出负脉冲的宽度延长,这种 方式常用于工业控制系统中的干扰自动复位电路 ⑧计数值有效期限: 计数值多次有效,计数初值写入 CR 后,在没有新的计数值写入 CR 之前,原计数初 值在 CR 中保持不变,以后每触发一次, CR 中保存 的这个计数初值就装入CE一次。

8253工作方式4 —软件触发选通信号

⑥计数期间写入新的计数值:立即有效。写入新计 数值后,在下一个时钟周期时,新计数值被装入CE, 开始以新的计数值计数。如果写入的计数值是 2 个 字节,那么写入第一个字节时,计数不受影响,写 入第二个字节时的下个CLK时钟脉冲使CR的新值装 入CE,并以新的计数值开始重新计数。 ⑦GATE 作用: GATE=0 时,计数停止; GATE=1 时,允许计数,此时计数器从暂停的地方开始连续 计数。GATE信号不影响OUT的状态。 ⑧计数值有效期限:计数值一次有效。只有在输入 新的计数值后,才能开始。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

8253-5/8254-2是24脚双列直插式芯片,+5v电源供电。

每个芯片内部有3个独立的计数器(计数通道),每个计数器 都有自己的时钟输入CLK,计数输出OUT和控制信号GATE。 通过编程设置工作方式,计数器可作计数用,也可作定时用, 故称定时/计数器,记作T/C。其引脚分配见图7.1。

图7.6 8253的2方式时序波形

4.3方式周期性方波输出

3方式与2工作方式基本相同,也具有自动装入时间常数 的能力,不同之处在于: ①工作在3方式,OUT引脚输出的不是一个时钟周期的 负脉冲,而是占空比为1:1或近似1:1的方波;当计数初

值为偶数时,输出在前一半的计数过程中为高电平,在后一

16位计数初值寄存器 装入/读出初值 LSB MSB 图7.3 计数通道的内部结构

计数初值寄存器(16位):用于存放计数初值(定时常

数、分频系数),其长度为16位,故最大计数值为65536 (64KB)。

计数初值寄存器的初值和减1计数器的初值在初始化时 同时一起装入的,计数初值寄存器的计数初值,在计数器计 数过程中保持不变,故计数初值寄存器的作用是在自动重装 操作中为减1计数器提供计数初值,以便重复计数。

CLK N=5 WR OUT N=5 WR GATE OUT

5 5 5 5 4 3 2 1 0 4 3 2 1 0 4 3 2 1 0

GATE=1

5 5 5 4 3 2 1 0 4 3 2 1 0 5 4 3 N=5 N=4 GATE=1 WR 4 4 4 OUT 5 4 3 2 1 0 3 2 1 0 3 2 1 0 3 2

器重新装入原计数初值并重新开始计数。

③若计数器工作期间对计数器写入新的计数值后,只要 门控信号再次出现上升沿,不管原来计数是否到0,则立即 按新写入的计数值重新开始计数。

CLK WR GATE OUT WR GATE OUT WR GATE OUT

N=5

N=5

5

4

3

2

1

0

5 N=3

4 3 N=4

的关系如表7.1所示。

表7.1 8253/8254的读写操作及端口地址

其次,介绍面向I/O设备的信号线。

(6)时钟信号CLK:CLK为输入信号。三个计数器各有一 独立的时钟输入信号,分别为CLK0、CLK1、CLK2。时钟 信号的作用是在8253进行定时或计数工作时,每输入一个 时钟信号CLK,便使计数值减1。它是计量的基本时钟。

减1计数器减1至0后,可以自动把计数初值寄存器的内容

再装入减1寄存器,重新开始计数。

减1计数器(16位):用于进行减1计数操作,每来一个

时钟脉冲,它就作减1运算,直至将计数值减为零。如果要 连续进行计数,则可重装计数初值寄存器的内容到减1计数

器。

当前计数值锁存器(16位):用于锁存减1计数器的内 容,以供读出和查询。由于减1计数器的内容是随输入时钟 脉冲在不断改变的,为了读取这些不断变化的当前计数值, 只有先把它送到当前计数值锁存器,并加以锁存才能读出。 因此,若要了解计数初值,则可从计数初值寄存器直接 读出。而如果要想知道计数过程中当前计数值,则必须将当 前值锁存后,从输出锁存器读出,不能直接从减1计数器中

读出当前值。为此,在8253的命令字中,设置了锁存命令。

7.2.2 工作方式及特点

8253-5/8254-2芯片的每个计数通道都有六种工作方式 可供选用。区分这六种工作方式的主要标志有四点:一是输 出波形不同;二是启动计数器的触发方式不同;三是计数过 程中门控信号GATE对计数操作的影响不同;四是在计数过

定时电路。例如较常见的定时器件有单稳触发器和555定时

器等,利用它们和外接电阻、电容的结合,可在一定时间范 围内实现定时。利用加法或减法计数器对周期一定的时钟脉

冲计数,也是一种常见的硬件定时思路,从给计数器预置一

定的初值开始计数到计数器最高位产生进位或借位信号,其 时间间隔是一定的,而且通过改变计数器初值可使定时长短 在一定范围内改变。

2.内部逻辑结构

8253/8254内部有6个模块,其内部结构框图如图7.2所示

图7.2 8253/8254的内部结构

(1)数据总线缓冲器:它是一个三态、双向8位寄存器, 用于将8253与系统数据总线D0~D7相连。CPU通过数据总 线缓冲器向8253写入数据、命令或从数据总线缓冲器读取 数据和状态信息。

各引脚的功能定义如下;

首先,介绍面向CPU的信号线。 (1)数据总线D0~D7:它们为三态输出输入线,用于将 8253与系统数据总线相连,是8253与CPU接口数据线,供 CPU向8253进行读写数据、传送命令和状态信息。

(2)片选线CS:为输入信号,低电平有效。当CS为低电

平时CPU选中8253,可以向8253进行读写; CS为高电平

5

4

3

2

1

0

3

2

1

0

4

3

2

1

0

图7.5 8253的1方式时序波形

3. 2方式周期性负脉冲输出

2方式是一种具有自动装入时间常数(计数初值)的N分频 器。其工作特点如下:

①计数器计数期间,输出OUT为高电平,待计数值减到 1时,输出一个时钟脉冲周期的负脉冲,至计数值为0时,自 动重新装入原计数初值,输出又恢复高电平并重新作减法计 数。

这种硬件定时方案不占用CPU时间,且电路也较简单,但电

路一经连接好后,定时值就不便控制和改变。

可编程硬件定时就是在上述不可编程硬件定时的基础上 加以改进,使其定时值和定时范围可方便地由软件来确定和 改变。可编程定时电路一般都是用可编程计数器来实现,因 此它既可计数又可定时,故称之为可编程定时器/计数器电 路。 目前,各种微型计算机和微机系统中都是采用可编程定

(7)门选通信号GATE:GATE信号为输入信号。三个通

道每一个都有自己的门选通信号,分别为GATE0、GATEl、 GATE2。

GATE信号的作用是用来禁止、允许或开始计数过程的。 对8253的6种不同工作方式,GATE信号的控制作用不同(参

见后面的表7.2)。

(8)计数器输出信号OUT:OUT是8253向外输出信号。

第七章 定时/计数器8253/8254

7.1概述 7.2 可编程定时/计数器8253-5/8254-2 7.3 8253/8254的应用举例 习题 7

7.1概述

在微型计算机系统尤其是实时计算机测控系统中,经常 需要为微处理器和I/O设备提供实时时钟,以实现定时中断、

定时检测、定时扫描、定时显示等定时或延时控制,或者对

中,一律假定已经写人了控制字,通道已经进入了相应的工 作方式,波形全部从写初值至计数初值寄存器(用n值表示) 开始画起。 1.0方式低电平输出(GATE信号上升沿继续计数)

0方式有如下三个特点: ①当向计数器写完计数值时,开始计数,计数一旦开始,

输出端0UT就变成低电平,并在计数过程中一直保持低电平,

入,不能读出,其内容将在后面讨论。

(4)计数器:8253有三个独立的计数器(计数通道),每 个通道的内部结构完全相同,如图7.3所示。该图表示计数 器由16位初值寄存器、减1计数器和当前计数值锁存器组成。

MSB LSB 锁存后读出当前值 16位当前计数值锁存器 CLK GATE & 16位减1计数器 OUT 减1为0时

程中改变计数初值的处理方式不同。

工作于任何一种方式,都必须先写控制字至控制字寄存 器,以选择所需方式,同时使所有逻辑电路复位、使计数初 值寄存器内容清零、使OUT变为规定状态,再向计数初值寄 存器写入计数初值。然后才能在GATE信号的控制下,在

CLK脉冲的作用下进行计数。

下面分别介绍各种工作方式。在说明各种方式的波形图

最高频率有所差异(前者为5MHz,后者为10MHz)。另外,

还有8253(2MHz)、8254(8MHz)和8254-5(5MHz)兼容芯片。 下面以8253-5和8254-2为例进行分析。本书中,以后出现 的8253和8254均分别指8253-5和8254-2。

7.2.1 外部特性与内部逻辑结构

三个独立通道,每一个都有自己的计数器输出信号,分别为 OUT0、0UTl、OUT2。

0UT信号的作用是,计数器工作时,每来1个时钟脉冲, 计数器减1,当计数器减为0,就在输出线上输出一个OUT

信号,以指示定时或计数已到。

这个信号可作为外部定时、计数控制信号引到I/O设备用 来启动某种操作(开/关或启/停),也可作为定时、计数已到 的状态信号供CPU检测,或作为中断请求信号使用。

半的计数过程中为低电平。

②当计数初值为奇数时,在前一半加1的计数过程中, 输出为高电平,后—半减1的计数过程中为低电平。例如, 若计数初值设为5,则在前3个时钟周期中,引脚OUT输出 高电平,而在后2个时钟周期中则输出低电平。8253的2方 式和3方式都是最为常用的工作方式,工作时序如图7.7所示。

为未选中。CS由CPU输出的地址码经译码产生。

(3)读信号RD:它为输入信号,低电平有效。它由CPU发 出,用于对8253寄存器读操作。

(4)写信号WR:它为输入信号,低电平有效。它由CPU

发出,用于对8253寄存器写操作。

(5)地址线AlA0:这两根线接到系统地址总线的A1A0上。 当CS=0,8253被选中时,A1A0用于选择8253内部寄存器, 以便对它们进行读写操作。8253内部寄存器与地址线AlA0

②门控信号GATE为高电平时允许计数。若在计数期间, 门控信号变为低电平,则计数器停止计数,待GATE恢复高电 平后,计数器将按原装入的计数值重新开始计数。 ③在计数器工作期间,如果向此计数器写入新的计数值, 则计数器仍按原计数值计数,直到计数器回零之后,才按新 写入的计数值计数,其工作时序如图7.6所示。