集成触发器39804

集成触发器及其应用电路设计与计数译码显示电路

02

搭建测试环境

根据测试计划搭建相应的测试环境, 包括所需的仪器、设备、电源等。

03

执行测试

按照测试计划进行测试,记录测试数 据和结果。

重复测试

对修复后的电路进行重复测试,确保 问题得到解决且电路功能正常。

05

04

问题定位与修复

根据测试结果定位问题所在,分析原 因并采取相应的措施进行修复。

集成触发器及其应用电路的测试与调试实例

03

计数器电路设计

计数器的定义与分类

计数器的定义

计数器是一种用于对输入脉冲进行计数的电路,通常由触发器组成。

计数器的分类

根据进制数不同,计数器可分为二进制计数器、十进制计数器和任意进制计数器 。

计数器电路的设计原理

计数器的工作原理

计数器通过接收输入脉冲信号,按照 一定的逻辑关系进行计数,并将计数 值输出。

集成触发器的选择

根据具体的电路设计和应用需求,选择合适 的集成触发器类型,如D触发器、JK触发器 等。

04

译码显示电路设计

译码显示电路的定义与分类

定义

译码显示电路是一种将输入的二进制代码转换为相应的输出信号,以驱动显示器件显示相应数字或字 符的电路。

分类

根据显示器件的不同,译码显示电路可分为LED显示译码电路、LCD显示译码电路、数码管显示译码 电路等。

集成触发器在应用电路设计中的具体应用

集成触发器的概念

集成触发器是一种常用的数字逻辑门电路,它具有两个稳定状态,可以通过输入信号进行 触发翻转。

应用场景

集成触发器在应用电路设计中主要用于实现时序逻辑和组合逻辑功能。例如,在计数器、 寄存器、分频器等电路中广泛应用。

设计要点

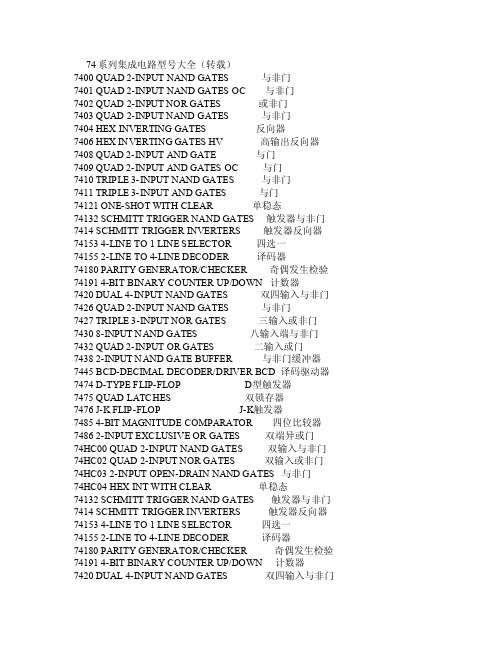

multisim74系列元件型号对照表

74系列集成电路型号大全(转载)7400 QUAD 2-IN PUT N AND G ATES与非门7401 QUAD 2-IN PUT N AND G ATESOC 与非门7402 Q UAD 2-INPU T NOR GATE S 或非门7403QUAD2-INP UT NA ND GA TES 与非门7404HEX I NVERT ING G ATES反向器7406 HE X INV ERTIN G GAT ES HV高输出反向器7408 QUA D 2-I NPUTAND G ATE 与门7409 QUA D 2-I NPUTAND G ATESOC 与门7410TRIPL E 3-I NPUTNANDGATES与非门7411TRIPL E 3-I NPUTAND G ATES与门74121 ONE-SHOTWITHCLEAR单稳态74132 SCHM ITT T RIGGE R NAN D GAT ES 触发器与非门7414 S CHMIT T TRI GGERINVER TERS触发器反向器74153 4-LI NE TO 1 LI NE SE LECTO R 四选一74155 2-LI NE TO 4-LI NE DE CODER译码器74180 PARI TY GE NERAT OR/CH ECKER奇偶发生检验74191 4-B IT BI NARYCOUNT ER UP/DOWN计数器7420 DUA L 4-I NPUTNANDGATES双四输入与非门7426 QUAD 2-IN PUT N AND G ATES与非门7427 TRIP LE 3-INPUT NORGATES三输入或非门74308-INP UT NA ND GA TES 八输入端与非门7432 QUA D 2-I NPUTOR GA TES 二输入或门74382-INP UT NA ND GA TE BU FFER与非门缓冲器7445 BC D-DEC IMALDECOD ER/DR IVERBCD 译码驱动器7474 D-TY PE FL IP-FL OP D型触发器7475 Q UAD L ATCHE S 双锁存器7476 J-KFLIP-FLOP J-K触发器7485 4-BIT M AGNIT UDE C OMPAR ATOR四位比较器7486 2-INPUT EXCL USIVE OR G ATES双端异或门74HC00 QUA D 2-I NPUTNANDGATES双输入与非门74H C02 Q UAD 2-INPU T NOR GATE S 双输入或非门74HC03 2-I NPUTOPEN-DRAIN NAND GATE S 与非门74HC04HEX I NT WI TH CL EAR 单稳态74132 SCH MITTTRIGG ER NA ND GA TES 触发器与非门7414 SCH MITTTRIGG ER IN VERTE RS 触发器反向器74153 4-LI NE TO 1 LI NE SE LECTO R 四选一74155 2-LINETO 4-LINEDECOD ER 译码器74180PARIT Y GEN ERATO R/CHE CKER奇偶发生检验74191 4-BIT B INARY COUN TER U P/DOW N 计数器7420DUAL4-INP UT NA ND GA TES 双四输入与非门7426 QUAD 2-IN PUT N AND G ATES与非门7427 TRI PLE 3-INPU T NOR GATE S 三输入或非门7430 8-I NPUTNANDGATES八输入端与非门7432QUAD2-INP UT OR GATE S 二输入或门7438 2-INPU T NAN D GAT E BUF FER 与非门缓冲器7445 BC D-DEC IMALDECOD ER/DR IVERBCD 译码驱动器7474 D-TYPEFLIP-FLOPD型触发器7475 QUAD LATC HES 双锁存器7476 J-K FLI P-FLO P J-K触发器74854-BIT MAGN ITUDE COMP ARATO R 四位比较器74862-INP UT EX CLUSI VE OR GATE S 双端异或门74H C00 Q UAD 2-INPU T NAN DGAT ES 双输入与非门74HC02QUAD2-INP UT NO R GAT ES 双输入或非门74HC03 2-INPUT OPEN-DRAI N NAN D GAT ES 与非门74HC04 HEXINVER TERS六路反向器74HC05 HEX INVE RTERS OPEN DRAI N 六路反向器74HC08 2-I NPUTAND G ATES双输入与门74HC107 J-KFLIP-FLOPWITHCLEAR J-K触发器74HC109A J-K FLI P-FLO P W/P RESET J-K触发器74HC11 TRI PLE 3-INPU T AND GATE S 三输入与门74HC112 DU AL J-K FLI P-FLO P 双J-K触发器74HC113 D UAL J-K FL IP-FL OP PR ESET双JK触发器74H C123A RETR IGGER ABLEMONOS TAB 可重触发单稳74HC125 TR I-STA TE QU AD BU FFERS四个三态门74HC126 TRI-STAT E QUA D BUF FERS六三态门74H C1322-INP UT TR IGGER NAND施密特触发与非门74HC133 13-INP UT NA ND GA TES 十三输入与非门74HC137 3-T O-8 D ECODE RS W/LATCH ES 3-8线译码器74HC138 3-8 LI NE DE CODER3线至8线译码器74HC139 2-4LINEDECOD ER 2线至4线译码器74HC14 TRI GGERE D HEX INVE RTER六触发反向器74HC147 10-4 L INE P RIORI TY EN CODER编码器74HC148 8-3 LINE PRIO RITYENCOD ER 编码器74H C1498-8 L INE P RIORI TY EN CODER编码器74HC151 8-CHANN EL DI GITAL MUX8通道多路器74HC153 D UAL 4-INPU T MUX双四输入多路器74HC154 4-16 LI NE DE CODER 4线至16线译码器74HC155 2-4 LI NE DE CODER 2线至4线译码器74HC157 Q UAD 2-INPU T MUX四个双端多路器74HC161 BINA RY CO UNTER二进制计数器74HC163 DE CADECOUNT ERS 十进制计数器74HC164 SE RIAL-PARAL LEL S HIFTREG 串入并出74HC165 PAR ALLEL-SERI AL SH IFT R EG 并入串出74HC166 SERI AL-PA RALLE L SHI FT RE G 串入并出74H C173TRI-S TATED FLI P-FLO P 三态D触发器74HC174 HE X D F LIP-F LOP W/CLEA R 六D触发器74HC175 HE X D F LIP-F LOP W/CLEA R 六D触发器74HC181 AR ITHME TIC L OGICUNIT算术逻辑单元74HC182 L OOK A HEADCARRY GENER ATR 进位发生器74H C190BINAR Y UP/DN CO UNTER二进制加减计数器74HC191 DE CADEUP/DN COUN TER 十进制加减计数74H C192DECAD E UP/DN CO UNTER十进制加减计数器74HC193 BI NARYUP/DN COUN TER 二进制加减计数74H C1944BITBI-DI R SHI FT 4位双向移位寄存器74HC195 4BI T PAR ALLEL SHIF T 4位并行移位寄存74H C20 Q UAD 4-INPU T NAN D GAT E 四个四入与非门74HC221ANON-R ETRIG MONO STAB不可重触发单稳74HC237 3-8 LINE DECO DER 地址锁3线至8线译码器74H C242/243 T RI-ST AT TR ANSCE IVER三态收发器74H C244OCTAL 3-ST ATE B UFFER八个三态缓冲门74HC374 3-ST ATE O CTALD FLI PFLOP三态D触发器74H C393 4-BI T BIN ARY C OUNTE R 4位二进制计数器74HC4016 Q UAD A NALOG SWIT CH 四路模拟量开关74HC402014-St age B inary Coun ter 14输出计数器74HC4017 De cadeCount er/Di vider with 10 D ecode d Out puts十进制计数器带10个译码输出端74HC4040 12 Sta ge Bi naryCount er 12出计数器74HC4046PHASE LOCK LOOP相位监测输出器74HC4049 LEV EL DO WN CO NVERT ER 电平变低器74HC4050 LE VEL D OWN C ONVER TER 电平变低器74HC4051 8-CH A NALOG MUX8通道多路器74HC40524-CHANALO G MUX4通道多路器74H C4053 2-CH ANAL OG MU X 2通道多路器74HC4060 14-STAGE BINA RY CO UNTER 14阶BIN计数74H C4066 QUAD ANAL OG MU X 四通道多路器74HC4075 TRI PLE 3-INPU T ORGATE 3输入或门74H C42 B CD TO DECI MAL BCD转十进制译码器74H C423A RETR IGGER ABLEMONOS TAB 可重触发单稳74HC4511 BCD-7 SE G DRI VER/D ECODE R 7段译码器74HC4514 4-16 LIN E DEC ODER 4至16线译码器74HC4538A RETR IGGER AB MO NOSTA B 可重触发单稳74H C4543 LCDBCD-7 SEGL CD用的B CD-7段译码驱动74HC51 AND OR G ATE I NVERT ER 与或非门74HC521 8BI T MAG NITUD E COM PARAT OR 判决定路74HC533 3-ST ATE D LATC H 三态D锁存器74HC534 3-STATE D FL IP-FL OP 三态D型触发器74H C5403-STA TE BU FFER三态缓冲器74HC541 3-S TATEBUFFE R INV ERTER三态缓冲反向器74HC58DUALAND O R GAT E 与或门74H C5893STAT E 8BI T SHI FT 8位移位寄存三态输出74H C5948BITSHIFT REG 8位移位寄存器74HC595 8BIT S HIFTREG 8位移位寄存器出锁存74HC597 8BIT SHIF T REG8位移位寄存器入锁存74HC620 3-STATE TRAN SCEIV ER 反向3态收发器74HC623 3-S TATETRANS CEIVE R 八路三态收发器74HC640 3-ST ATE T RANSC EIVER反向3态收发器74H C6433-STA TE TR ANSCE IVER八路三态收发器74HC646 N ON-IN VERTBUS T RANSC EIVER总线收发器74HC648 INV ERT B US TR ANCIV ER 反向总线收发器74HC688 8BIT M AGNIT UDE C OMPAR ATOR8位判决电路74H C7266 2-IN PUT E XCLUS IVE N OR GA TE 异或非门74HC73 DU AL J-K FLI P-FLO P W/C L 4至16线译码器74HC4538A RE TRIGG ERABMONOS TAB 可重触发单稳74HC4543 LC D BCD-7 SE G LCD用的BCD-7段译码驱动74H C51 A ND OR GATE INVE RTER与或非门74HC521 8BIT M AGNIT UDE C OMPAR ATOR判决定路74HC533 3-STATE D LA TCH 三态D锁存器74HC534 3-STAT E D F LIP-F LOP 三态D型触发器74H C5403-STA TE BU FFER三态缓冲器74H C5413-STA TE BU FFERINVER TER 三态缓冲反向器74HC58 DUAL ANDOR GA TE 与或门74H C5893STAT E 8BI T SHI FT 8位移位寄存三态输出74H C5948BITSHIFT REG 8位移位寄存器74HC595 8BI T SHI FT RE G 8位移位寄存器出锁存74 HC597 8B IT SH IFT R EG 8位移位寄存器入锁存74HC620 3-STATE TRAN SCEIV ER 反向3态收发器74H C6233-STA TE TR ANSCE IVER八路三态收发器74HC640 3-S TATETRANS CEIVE R 反向3态收发器74HC643 3-STAT E TRA NSCEI VER 八路三态收发器74HC646 NON-INVER T BUS TRAN SCEIV ER 总线收发器74HC648 INVE RT BU S TRA NCIVE R 反向总线收发器74HC688 8B IT MA GNITU DE CO MPARA TOR 8位判决电路74HC72662-INP UT EX CLUSI VE NO R GAT E 异或非门74HC73 DUA L J-K FLIP-FLOP W/CL EAR 双JK触发器74HC74A P RESET/CLEA R D F LIP-F LOP 双D触发器74HC75 4B IT BI STABL E LAT CH 4位双稳锁存器74HC76 PR ESET/CLEAR JK F LIP-F LOP 双JK触发器74H C85 4BIT M AGNIT UDE C OMPAR ATOR 4位判决电路74HC86 2IN PUT E XCLUS IVE O R GAT E 2输入异或门74HC942 B AUD M ODEM300BP S低速调制解调器74HC943 300 BAUD MODE M 300BPS 低速调制解调器74LS00 QU AD 2-INPUT NAND GATE S 与非门74LS02 QUAD 2-IN PUT N OR GA TES 或非门74LS03QUAD2-INP UT NA ND GA TES 与非门74LS04 HE X INV ERTIN G GAT ES 反向器74L S05 H EX IN VERTE RS OP EN DR AIN 六路反向器74L S08 Q UAD 2-INPU T AND GATE与门74LS09 QUA D 2-I NPUTAND G ATESOC 与门74LS10 TR IPLE3-INP UT NA ND GA TES 与非门74LS109 QUA D 2-I NPUTAND G ATESOC 与门74LS11 TRIP LE 3-INPUT ANDGATES与门74L S112DUALJ-K F LIP-F LOP 双J-K触发器74LS113 DUA L J-K FLIP-FLOP PRES ET 双JK触发器74LS114 N EGATI VE J-K FLI P-FLO P 负沿J-K触发器74LS122 R etrig gerab le Mo nosta b 可重触发单稳74LS123 R etrig gerab le Mo nosta ble 可重触发单稳74LS125 T RI-ST ATE Q UAD B UFFER S 四个三态门74LS13 QU AL 4-in NA ND TR IGGER 4输入与非触发器74L S160BCD D ECADE 4BIT BINCOUNT ERS 计数器74LS136 QU ADRUP LE 2-INPUT XORGATE异或门74LS138 3-8LINEDECOD ER 3线至8线译码器74LS139 2-4 LI NE DE CODER2线至4线译码器74LS14 TRIG GERED HEXINVER TER 六触发反向器74L S1518-CHA NNELDIGIT AL MU X 8通道多路器74LS153 DU AL 4-INPUT MUX双四输入多路器74L S1552-4 L INE D ECODE R 2线至4线译码器74LS156 2-4 LI NE DE CODER/DEMU X 2-4译码器74LS157 QUA D 2-I NPUTMUX 四个双端多路器74LS158 2-1 LI NE MU X 2-1线多路器74L S160A BINA RY CO UNTER二进制计数器74LS161A BIN ARY C OUNTE R 二进制计数器74LS162A BI NARYCOUNT ER 二进制计数器74LS163A D ECADE COUN TERS十进制计数器74LS164 SE RIAL-PARAL LEL S HIFTREG 串入并出74LS168 B I-DIR ECT B CD TO DECA DE 双向计数器74LS169 4BI T UP/DN BI N COU NTER四位加减计数器74LS173 TR I-STA TE DFLIP-FLOP三态D触发器74L S174HEX D FLIP-FLOP W/CL EAR 六D触发器74LS175 HE X D F LIP-F LOP W/CLEA R 六D触发器74LS190 BINA RY UP/DN C OUNTE R 二进制加减计数器74LS191 DE CADEUP/DN COUN TER 十进制加减计数74LS192 DE CADEUP/DN COUN TER 十进制加减计数器74LS193 B INARY UP/D N COU NTER进制加减计数74LS194A4BITBI-DI R SHI FT 4位双向移位寄存器74L S195A 4BIT PARA LLELSHIFT 4位并行移位寄存74LS20 QUA D 4-I NPUTNANDGATE四个四入与非门74LS21 4-I NPUTAND G ATE 四输入端与门74LS240 OCTA L 3-S TATEBUFFE R 八个三态缓冲门74LS244 OCT AL 3-STATE BUFF ER 八个三态缓冲门74L S245OCTAL 3-ST ATE T RANSC EIVER三态收发器74LS253 DU AL 4-CH 3-STATE MUX4路3态多路器74L S2564BITADDRE SS LA TCH 四位可锁存锁存器74LS257 QU AD 2-CH 3-STATE MUX4路3态多路器74L S2582-CH3-STA TE MU X 2路3态多路器74LS27 TRIP LE 3-INPUT NORGATES三输入或非门74LS279 QU AD R-S LAT CHES四个R S非锁存器74LS28 QU AD 2-INPUT NORBUFFE R 四双端或非缓冲74LS283 4BIT BINA RY AD DER C ARRY四位加法器74LS308-INP UT NA ND GA TES 八输入端与非门74L S32 Q UAD 2-INPU T ORGATES二输入或门74L S3524-1 L INE S ELECT OR/MU X 4-1线选择多路器74LS365 H EX 3-STATE BUFF ER 六个三态缓冲门74LS367 3-S TATEBUFFE R INV ERTER缓冲反向器74LS368A 3-S TATEBUFFE R INV ERTER缓冲反向器74LS373 O CT LA TCH W/3-ST ATE O UT 三态输出锁存器74LS76 Dua l JKFlip-Flopw/set2个JK触发器74LS379 QUAD PARA LLELREG 四个并行寄存器74LS382-INP UT NA ND GA TE BU FFER与非门缓冲器74LS390 DUA L DEC ADE C OUNTE R 2个10进制计数器74LS393 DUAL BINA RY CO UNTER 2个2进制计数器74LS42 BC D TODECIM AL BCD转十进制译码器74L S48 B CD-7SEG BCD-7段译码器74LS49 BCD-7 SE G BC D-7段译码器74LS51AND O R GAT E INV ERTER与或非门74LS540 OC T Buf fer/L ine D river 8路缓冲驱动器74LS541 OCT Buff er/Li neDri ver 8路缓冲驱动器74LS74D-TYP E FLI P-FLO P D型触发器74LS682 8B IT MA GNITU DE CO MPARA TOR 8路比较器74LS684 8B IT MA GNITU DE CO MPARA TOR 8路比较器74LS75 QUA D LAT CHES双锁存器74LS83A 4BI T BIN ARY A DDERCARRY四位加法器74LS85 4BIT MAGN ITUDE COMP ARAT 4位判决电路74LS86 2IN PUT E XCLUS IVE O R GAT E 2输入异或门74LS90 DE CADE/BINAR Y COU NTER十/二进制计数器74LS85 4BIT MAGN ITUDE COMP ARAT 4位判决电路74LS86 2INP UT EX CLUSI VE OR GATE 2输入异或门74LS90 DEC ADE/B INARY COUN TER 十/二进制计数器74LS95B 4B IT RI GHT/L EFT S HIFT 4位左右移位寄存74LS688 8B IT MA GNITU DE CO MPARA T 8位判决电路74LS136 2-IN PUT X OR GA TE 2输入异或门74L S651BUS T RANSC EIVER S 总线收发器74LS653 BU S TRA NSCEI VERS总线收发器74LS670 3-ST ATE 4-BY-4 REG3态4-4寄存器74LS73A DUA L J-K FLIP-FLOP W/CL EAR 双J K触发器注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

知识模块二十二常用集成触发器

二、集成JK触发器

▪ 1.同步JK触发器 (1)电路组成

同步JK触发器的电路组成如图22—8所示。

图22—8 同步JK触发器

(a)逻辑电路

(b)逻辑符号

(3)状态表

同步JK触发器的状态表如表22—5所示。 表22—5状态表

从表22—5中可知:

①当J=0,K=1时Q,n1 JQn KQn ,置“0”。

端连在一起,即采用了同步控制。设所有触发器的初始状态都处于0状态(Q=0, =1)。在控制时钟的连续作用下,被存储的二进制数(0101B)一位接一位地从 左向右移动。根据D触发器的特点,当时钟脉冲沿到来时,输出端的状态与输入 端状态相同,Qn+1=D。所以在时钟端每来一个CP脉冲都会引起所有触发器状态 向右移动一位,若来4个时钟脉冲,移位寄存器就存储了4位二进制信息 Q0Q1Q2Q3=0101。

▪ ②S端输入均为低电平时,输出状态不定, 即R=S=0,Q= =1,违反了互补关系。 当RS从00变为11时,则Q()=1(0),Q([])=0(1),状态不能确定,如 图22—3所示。

▪ ③与非门构成的基本RS触发器的功能,可简化为如表22—2所示。

表22—2基本RS触发器功能表

▪ 2.同步RS触发器

功能表如表22—7所示。其中CP为时钟输入端,D为数据输入端,Q、 为互Q 补输

出端, 为直RD接复位端,低电平有效, 为S直D接置位端,低电平有效, 和RD

S

用来设置初始状态。

D

图22—14双上升沿D触发器(74LS74)

(a)实物

(b)引脚图

(C)外引线图

表22—7双上升沿D触发器74LS74功能表 符号说明:Ф表示无效状态。

TTL集成主从RS触发器74LS71的引脚分布和逻辑符号如图22—7所示,功 能表如表22—4所示。触发器分别有3个S端和3个R端,均为与逻辑关系,即 1R=R1•R2•R3, 1S=S1•S2•S3。使用中如有多余的输入端,要将它们接至高电 平。触发器带有清零端(置0)RD和预置端(置1)SD,它们的有效电平为低电平。

7474芯片

7474芯片7474芯片是一种双触发D触发器,由Texas Instruments(德州仪器)公司研发与生产。

它是一款十分常用的数字电路元件,广泛应用于逻辑电路设计中,特别是时序电路的设计。

在本文中,我将介绍7474芯片的内部结构、工作原理以及应用场景。

首先,让我们来看一下7474芯片的内部结构。

7474芯片由两个D触发器组成,每个D触发器包含一个数据输入(D)和一个时钟输入(CLK)。

其中,D触发器的输出(Q)被馈送到下一个D触发器的数据输入,形成了一个级联的结构。

除此之外,每个D触发器还有一个使能端(EN),可以控制数据输入在时钟脉冲到来时是否有效,从而实现数据的存储或传输。

接下来,我们来探讨一下7474芯片的工作原理。

当时钟脉冲到来时,如果使能端为高电平,则数据输入会被写入到D触发器中,并在下一时钟脉冲到来时保持不变。

如果使能端为低电平,则数据输入不会被写入,而是保持上一次时钟脉冲到来时的状态。

这样,通过控制使能端的电平,可以实现数据的存储或传输。

在实际应用中,7474芯片常常用于时序电路设计。

例如,它可以用来实现寄存器、计数器、移位寄存器等功能。

在这些应用中,通过将多个7474芯片级联起来,可以实现更复杂的功能。

另外,7474芯片还可以用于时钟信号的整形和分频。

通过利用其存储和传输功能,可以实现对时钟信号的控制和分频操作,从而满足各种特定的时序要求。

综上所述,7474芯片是一款十分常用的数字电路元件。

它的内部结构简单,工作原理清晰。

通过合理配置使能端和时钟脉冲,可以实现数据的存储或传输,并在时序电路设计中发挥重要作用。

7474芯片在计算机硬件、通信系统等领域有着广泛的应用,为实现复杂的数字逻辑功能提供了可靠的解决方案。

《集成555定时器》课件

555定时器在电子设备、通信系统和工业自动化等领域中广泛应用,如闪烁灯、蜂鸣器、触 发器和模拟信号处理。

555定时器的调试方法

1

调试流程

调试555定时器需要依次检查电源连接、元件数值、触发器设置和输出电压等步 骤,确保电路正常工作。

2

注意事项

在调试555定时器时要正确使用万用表和示波器,并注意避免电压过高、短路和 误连接等问题。

常见问题与解答

1 常见问题汇总

整理了学习555定时器过程中常见的问题,包括无输出信号、频率不稳定和触发器失灵等。

2 解答常见问题的方法

提供了解决常见问题的方法和技巧,例如检查电源供应、更换元件或调整电路参数等。

结语

总结555定时器的重点内容

回顾了555定时器的基本原理和应用,并总结了学习过 程中需要重点关注的知识点。

555定时器可以在单稳态、多谐振荡和连续 振荡等多种工作模式下运行,每种模式都有

不同的应用场景。

内部组成

555定时器包含比较器、的 稳定性和精度。

555定时器的应用

基本应用

555定时器可用于产生脉冲、频率测量、电压控制和信号延时等基本应用,非常适用于电子 实验和简单电路设计。

提出学习建议和学习计划

给出学习555定时器的建议和计划,鼓励学习者进行实 践和深入研究,掌握它的更多应用技巧。

《集成555定时器》PPT课件

本课件将介绍集成555定时器的原理、工作模式、应用和调试方法,帮助您深 入了解并运用这一电子元件。

什么是555定时器?

555定时器是一种集成电路,可用于生成精确的定时脉冲信号。它的名称源于其内部构造,由三个电阻和两个电容组 成。

555定时器的工作原理

1

不同工作模式

2

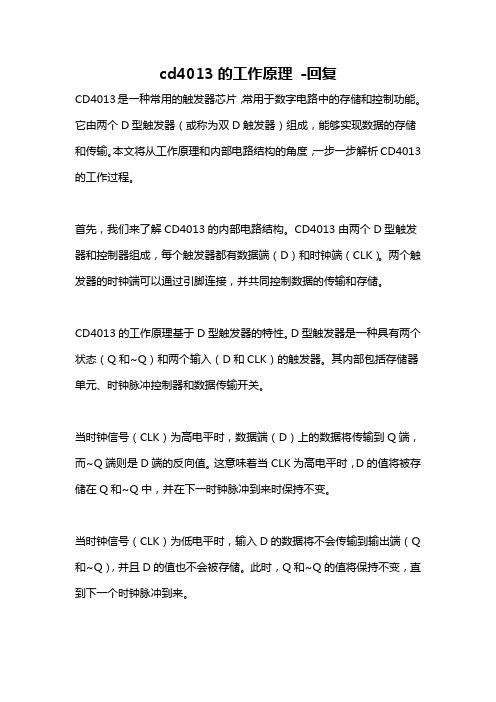

cd4013的工作原理 -回复

cd4013的工作原理-回复CD4013是一种常用的触发器芯片,常用于数字电路中的存储和控制功能。

它由两个D型触发器(或称为双D触发器)组成,能够实现数据的存储和传输。

本文将从工作原理和内部电路结构的角度,一步一步解析CD4013的工作过程。

首先,我们来了解CD4013的内部电路结构。

CD4013由两个D型触发器和控制器组成,每个触发器都有数据端(D)和时钟端(CLK)。

两个触发器的时钟端可以通过引脚连接,并共同控制数据的传输和存储。

CD4013的工作原理基于D型触发器的特性。

D型触发器是一种具有两个状态(Q和~Q)和两个输入(D和CLK)的触发器。

其内部包括存储器单元、时钟脉冲控制器和数据传输开关。

当时钟信号(CLK)为高电平时,数据端(D)上的数据将传输到Q端,而~Q端则是D端的反向值。

这意味着当CLK为高电平时,D的值将被存储在Q和~Q中,并在下一时钟脉冲到来时保持不变。

当时钟信号(CLK)为低电平时,输入D的数据将不会传输到输出端(Q 和~Q),并且D的值也不会被存储。

此时,Q和~Q的值将保持不变,直到下一个时钟脉冲到来。

接下来,让我们以一个具体的实例来说明CD4013的工作原理。

假设我们要使用CD4013来实现一个存储器,存储一个4位的二进制数1010。

首先,我们需要将四个二进制位的数据输入到CD4013的数据端(D)。

数据输入是通过连接引脚来完成的,其中CD4013共有14个引脚。

我们需要将四个数据位逐一输入到CD4013的四个数据端(D1,D2,D3和D4)上。

接下来,我们需要确定时钟信号(CLK)的频率和脉冲宽度。

时钟信号的频率决定了数据的传输速率,而脉冲宽度决定了数据在触发器中存储的时间。

通常,时钟信号为一个定期的周期性信号。

我们将时钟信号连接到CD4013的时钟端(CLK1和CLK2)。

时钟信号的高电平和低电平分别对应着数据传输和存储的时刻。

在时钟信号的作用下,数据将被传输到触发器的存储器单元中,并在适当的时机存储。

555时基电路工作原理

555时基电路工作原理标题:555时基电路工作原理引言概述:555时基电路是一种常用的集成电路,被广泛应用于各种电子设备中。

本文将详细阐述555时基电路的工作原理,包括其组成结构、工作模式、内部元件以及应用领域等方面。

正文内容:1. 555时基电路的组成结构1.1 电源引脚:正极(VCC)和负极(GND)引脚。

1.2 控制引脚:包括触发(TRIG)、复位(RESET)和控制电压(CTRL)引脚。

1.3 输出引脚:输出脉冲信号的引脚(OUT)。

1.4 外部元件:包括电容器(C)和电阻器(R)。

2. 555时基电路的工作模式2.1 单稳态模式(单触发器模式):通过控制引脚输入触发信号,产生一个固定宽度的脉冲输出。

2.1.1 触发器状态:触发器的输出状态取决于触发引脚输入的电平信号。

2.1.2 时间常数:通过电容器和电阻器的组合,可以调节输出脉冲的宽度。

2.2 双稳态模式(双触发器模式):通过控制引脚输入触发信号,产生一个周期性的方波输出。

2.2.1 触发器状态:触发器的输出状态在触发引脚输入信号的边沿变化时切换。

2.2.2 时间常数:通过电容器和电阻器的组合,可以调节方波输出的周期。

3. 555时基电路的内部元件3.1 比较器:用于比较电压信号,控制输出引脚的状态。

3.2 RS触发器:用于存储输出引脚的状态。

3.3 控制电压比较器:用于比较控制引脚输入的电压信号。

4. 555时基电路的应用领域4.1 时钟电路:用于产生稳定的时钟信号,应用于计时器、时钟等设备。

4.2 脉冲发生器:用于产生特定频率和占空比的脉冲信号,应用于通信设备、计数器等。

4.3 触发器:用于检测和响应外部触发信号,应用于传感器、开关等。

总结:通过本文的阐述,我们了解了555时基电路的工作原理。

从组成结构、工作模式、内部元件以及应用领域等方面进行了详细的介绍。

555时基电路作为一种常用的集成电路,在各种电子设备中发挥着重要的作用,其稳定性和可调节性使其在电子领域得到广泛应用。

整形电路Word版

整形电路

CD40106可以将任意波形整成方波的形式。

CD40106是具有施密特功能的六反相器。

施密特触发器具有上限阈值电压和下限阈值电压的特性,且受电源限制。

在不同的电源电压下,有不同的阈值。

门电路构成的施密特触发器和集成施密特触发器根据其特点不同可以应用到不同的场合。

当矩形脉冲经过传输后因以下原因发生畸变,可通过施密特触发器的整形获得满意的矩形脉冲波形。

施密特触发器

施密特触发器是具有滞后特性的数字传输门

施密特触发器的应用

用于波形变换:施密特触发器可用于将三角波、正弦波及其它不规则信号变换成矩形脉冲。

用于脉冲整形

当传输的信号受到干扰而发生畸变时,可利用施密特触发器的回差特性,将受到干扰的信号整形成较好的矩形脉冲。

用于脉冲幅度鉴别

如输入信号为一组幅度不等的脉冲,而要求将幅度大于UT+的脉冲信号挑选出来时,则可用施密特触发器对输入脉冲的幅度进行鉴别。