120道填空题参考答案 数字逻辑要点

数字逻辑考试题.(优选)

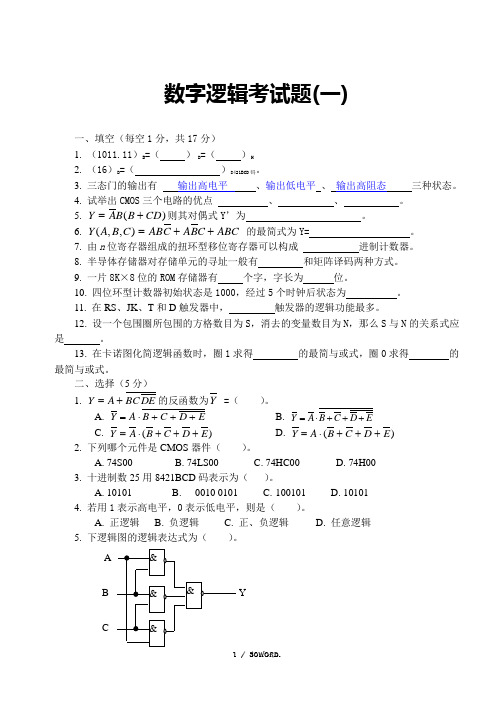

数字逻辑考试题(一)一、填空(每空1分,共17分)1. (1011.11)B =( ) D =( )H2. (16)D =( )8421BCD 码。

3. 三态门的输出有 输出高电平 、输出低电平 、 输出高阻态 三种状态。

4. 试举出CMOS 三个电路的优点 、 、 。

5. )(CD B B A Y +=则其对偶式Y ’为 。

6. ABC C B A C AB C B A Y ++=),,( 的最简式为Y= 。

7. 由n 位寄存器组成的扭环型移位寄存器可以构成 进制计数器。

8. 半导体存储器对存储单元的寻址一般有 和矩阵译码两种方式。

9. 一片8K ×8位的ROM 存储器有 个字,字长为 位。

10. 四位环型计数器初始状态是1000,经过5个时钟后状态为 。

11. 在RS 、JK 、T 和D 触发器中, 触发器的逻辑功能最多。

12. 设一个包围圈所包围的方格数目为S ,消去的变量数目为N ,那么S 与N 的关系式应是 。

13. 在卡诺图化简逻辑函数时,圈1求得 的最简与或式,圈0求得 的最简与或式。

二、选择(5分) 1. DE BC A Y +=的反函数为Y =( )。

A. E D C B A Y +++⋅= B. E D C B A Y +++⋅=C. )(E D C B A Y +++⋅=D. )(E D C B A Y +++⋅=2. 下列哪个元件是CMOS 器件( )。

A. 74S00B. 74LS00C. 74HC00D. 74H003. 十进制数25用8421BCD 码表示为( )。

A. 10101B. 0010 0101C. 100101D. 101014. 若用1表示高电平,0表示低电平,则是( )。

A. 正逻辑B. 负逻辑C. 正、负逻辑D. 任意逻辑5. 下逻辑图的逻辑表达式为( )。

A. AC BC AB Y =B. BC AC AB Y ++=C. BC AC AB Y ++=D. BC AC AB Y =6. 三态门的逻辑值正确是指它有( )。

120道填空题参考答案 数字逻辑要点

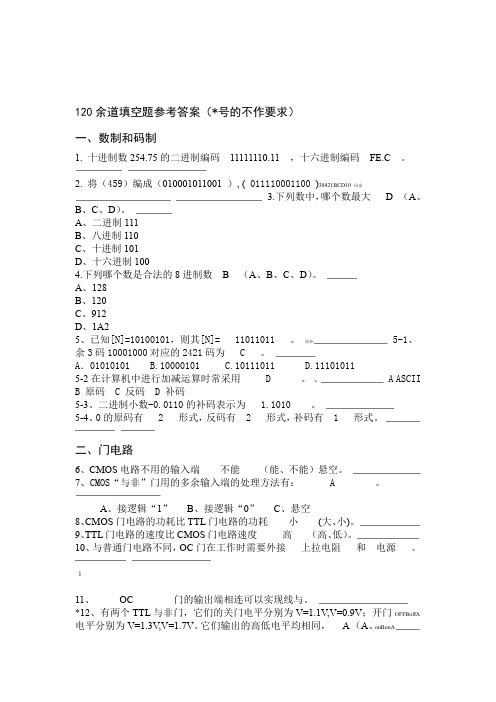

120余道填空题参考答案(*号的不作要求)一、数制和码制1.十进制数254.75的二进制编码11111110.11 ,十六进制编码FE.C 。

2. 将(459)编成(010*********), ( 011110001100 )38421BCD10 码余3.下列数中,哪个数最大 D (A、B、C、D)。

A、二进制111B、八进制110C、十进制101D、十六进制1004.下列哪个数是合法的8进制数 B (A、B、C、D)。

A、128B、120C、912D、1A25、已知[N]=10100101,则其[N]= 11011011 。

原补5-1、余3码10001000对应的2421码为 C 。

A.01010101 B.10000101 C.10111011 D.111010115-2在计算机中进行加减运算时常采用 D 。

、 A ASCII B 原码 C 反码 D 补码5-3、二进制小数-0.0110的补码表示为 1.1010 。

5-4、0的原码有 2 形式,反码有 2 形式,补码有 1 形式。

二、门电路6、CMOS电路不用的输入端不能(能、不能)悬空。

7、CMOS“与非”门用的多余输入端的处理方法有: A 。

A、接逻辑“1”B、接逻辑“0”C、悬空8、CMOS门电路的功耗比TTL门电路的功耗小(大、小)。

9、TTL门电路的速度比CMOS门电路速度高(高、低)。

10、与普通门电路不同,OC门在工作时需要外接上拉电阻和电源。

111、OC 门的输出端相连可以实现线与。

*12、有两个TTL与非门,它们的关门电平分别为V=1.1V,V=0.9V;开门OFFBoffA 电平分别为V=1.3V,V=1.7V。

它们输出的高低电平均相同, A (A、onBonAB)门的抗干扰能力强。

13、一片与非门芯片具有三个三输入端与非门,该芯片引脚数至少要14 。

(14、16、18、20)。

14、三态门除了具有高电平和低电平两种状态外,还有第三种状态叫高阻状态。

数字逻辑考题及答案

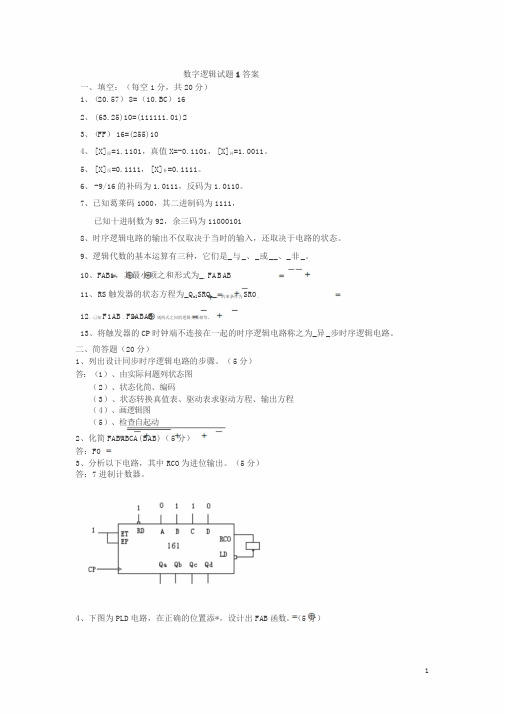

数字逻辑试题1答案一、填空:(每空1分,共20分)1、(20.57)8=(10.BC)162、(63.25)10=(111111.01)23、(FF)16=(255)104、[X]原=1.1101,真值X=-0.1101,[X]补=1.0011。

5、[X]反=0.1111,[X]补=0.1111。

6、-9/16的补码为1.0111,反码为1.0110。

7、已知葛莱码1000,其二进制码为1111,已知十进制数为92,余三码为110001018、时序逻辑电路的输出不仅取决于当时的输入,还取决于电路的状态。

9、逻辑代数的基本运算有三种,它们是_与_、_或__、_非_。

10、FAB1,其最小项之和形式为_。

FA B AB11、RS触发器的状态方程为_Q n1SRQ n_,约束条件为SR0。

12、已知F1AB、F2ABAB,则两式之间的逻辑关系相等。

13、将触发器的CP时钟端不连接在一起的时序逻辑电路称之为_异_步时序逻辑电路。

二、简答题(20分)1、列出设计同步时序逻辑电路的步骤。

(5分)答:(1)、由实际问题列状态图(2)、状态化简、编码(3)、状态转换真值表、驱动表求驱动方程、输出方程(4)、画逻辑图(5)、检查自起动2、化简FABABCA(BAB)(5分)答:F03、分析以下电路,其中RCO为进位输出。

(5分)答:7进制计数器。

4、下图为PLD电路,在正确的位置添*,设计出FAB函数。

(5分)15分注:答案之一。

三、分析题(30分)1、分析以下电路,说明电路功能。

(10分)解:XY m(3,5,6,7)m(1,2,4,7)2分ABCiXY0000000101010010111010001101101101011111该组合逻辑电路是全加器。

以上8分2、分析以下电路,其中X为控制端,说明电路功能。

(10分)解:FXA B C XABCXABCXABCXABCXABC4分FX(ABC)X(A B C ABC)4分所以:X=0完成判奇功能。

数字逻辑120道填空题参考答案

120余道填空题参考答案(*号的不作要求)一、数制和码制1.十进制数254.75的二进制编码11111110.11 ,十六进制编码FE.C 。

2. 将(459)10编成(010*********)8421BCD, ( 011110001100 )余3码3.下列数中,哪个数最大 D (A、B、C、D)。

A、二进制111B、八进制110C、十进制101D、十六进制1004.下列哪个数是合法的8进制数 B (A、B、C、D)。

A、128B、120C、912D、1A25、已知[N]补=10100101,则其[N]原= 11011011 。

5-1、余3码10001000对应的2421码为 C 。

A.01010101 B.10000101 C.10111011 D.111010115-2、在计算机中进行加减运算时常采用 D 。

A ASCIIB 原码C 反码D 补码5-3、二进制小数-0.0110的补码表示为 1.1010 。

5-4、0的原码有 2 形式,反码有 2 形式,补码有 1 形式。

二、门电路6、CMOS电路不用的输入端不能(能、不能)悬空。

7、CMOS“与非”门用的多余输入端的处理方法有: A 。

A、接逻辑“1”B、接逻辑“0”C、悬空8、CMOS门电路的功耗比TTL门电路的功耗小(大、小)。

9、TTL门电路的速度比CMOS门电路速度高(高、低)。

10、与普通门电路不同,OC门在工作时需要外接上拉电阻和电源。

11、OC 门可以实现线与输出端的相连。

*12、有两个TTL与非门,它们的关门电平分别为V offA=1.1V,V OFFB=0.9V;开门电平分别为V onA=1.3V,V onB=1.7V。

它们输出的高低电平均相同, A (A、B)门的抗干扰能力强。

13、一片与非门芯片具有三个三输入端与非门,该芯片引脚数至少要14 。

(14、16、18、20)。

14、三态门除了具有高电平和低电平两种状态外,还有第三种状态叫高阻状态。

数字逻辑考题及答案

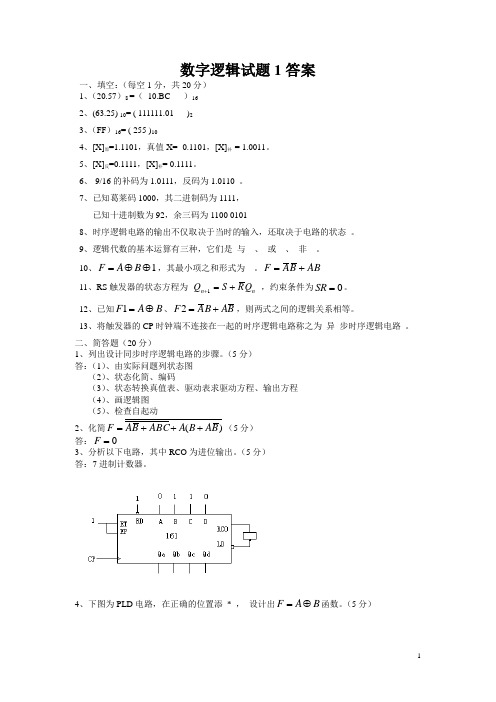

数字逻辑试题1答案一、填空:(每空1分,共20分) 1、(20.57)8 =( 10.BC )16 2、(63.25) 10= ( 111111.01 )2 3、(FF )16= ( 255 )104、[X]原=1.1101,真值X= -0.1101,[X]补 = 1.0011。

5、[X]反=0.1111,[X]补= 0.1111。

6、-9/16的补码为1.0111,反码为1.0110 。

7、已知葛莱码1000,其二进制码为1111, 已知十进制数为92,余三码为1100 01018、时序逻辑电路的输出不仅取决于当时的输入,还取决于电路的状态 。

9、逻辑代数的基本运算有三种,它们是_与_ 、_或__、_非_ 。

10、1⊕⊕=B A F ,其最小项之和形式为_ 。

AB B A F += 11、RS 触发器的状态方程为_n n Q R S Q +=+1_,约束条件为0=SR 。

12、已知B A F ⊕=1、B A B A F +=2,则两式之间的逻辑关系相等。

13、将触发器的CP 时钟端不连接在一起的时序逻辑电路称之为_异_步时序逻辑电路 。

二、简答题(20分)1、列出设计同步时序逻辑电路的步骤。

(5分) 答:(1)、由实际问题列状态图 (2)、状态化简、编码 (3)、状态转换真值表、驱动表求驱动方程、输出方程 (4)、画逻辑图 (5)、检查自起动2、化简)(B A B A ABC B A F +++=(5分) 答:0=F3、分析以下电路,其中RCO 为进位输出。

(5分) 答:7进制计数器。

4、下图为PLD 电路,在正确的位置添 * , 设计出B A F ⊕=函数。

(5分)5分 注:答案之一。

三、分析题(30分)1、分析以下电路,说明电路功能。

(10分)解: ∑∑==)7,4,2,1()7,6,5,3(m Y m X 2分A B Ci X Y 0 0 0 0 0 0110 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1该组合逻辑电路是全加器。

数字逻辑试题及答案

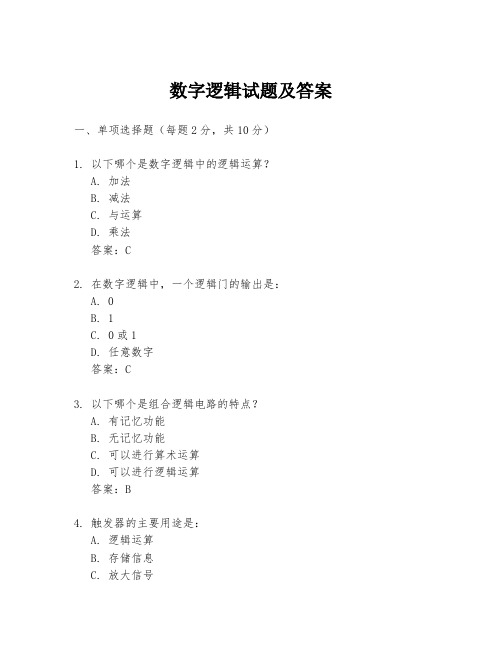

数字逻辑试题及答案一、单项选择题(每题2分,共10分)1. 以下哪个是数字逻辑中的逻辑运算?A. 加法B. 减法C. 与运算D. 乘法答案:C2. 在数字逻辑中,一个逻辑门的输出是:A. 0B. 1C. 0或1D. 任意数字答案:C3. 以下哪个是组合逻辑电路的特点?A. 有记忆功能B. 无记忆功能C. 可以进行算术运算D. 可以进行逻辑运算答案:B4. 触发器的主要用途是:A. 逻辑运算B. 存储信息C. 放大信号D. 转换信号答案:B5. 一个4位二进制计数器可以计数到:A. 8B. 16C. 32D. 64答案:B二、多项选择题(每题3分,共15分)1. 下列哪些是数字逻辑中常用的逻辑门?A. 与门B. 或门C. 非门D. 异或门E. 与非门答案:ABCDE2. 在数字逻辑中,以下哪些可以作为信号的表示?A. 电压B. 电流C. 电阻D. 电容E. 电感答案:AB3. 以下哪些是数字电路的基本组成元素?A. 逻辑门B. 电阻C. 电容D. 触发器E. 运算放大器答案:ABD4. 在数字逻辑中,以下哪些是常见的电路类型?A. 组合逻辑电路B. 时序逻辑电路C. 模拟电路D. 混合信号电路E. 微处理器答案:ABD5. 以下哪些是数字电路设计时需要考虑的因素?A. 电路的复杂性B. 电路的功耗C. 电路的可靠性D. 电路的成本E. 电路的尺寸答案:ABCDE三、填空题(每题2分,共10分)1. 在数字逻辑中,一个逻辑门的输出状态取决于其_________。

答案:输入状态2. 一个D触发器的输出在时钟信号的_________沿触发。

答案:上升沿3. 一个4位二进制计数器的计数范围是从_________到_________。

答案:0000到11114. 一个逻辑电路的输出是其输入的_________。

答案:逻辑函数5. 在数字逻辑中,使用_________可以表示一个逻辑函数的真值表。

答案:卡诺图四、简答题(每题5分,共15分)1. 描述一个典型的组合逻辑电路的工作原理。

数字逻辑训练题(一)参考答案

数字逻辑训练题参考答案一、填空题(30分,每空1分)1. 3.4 伏。

2. 算术 。

3. 奇 。

4.(a )F= 1 ;(b )F= A ;(c )F= 0 ;(d )F= A ; (e )F= B A AB + 或者:A ⊙B 或者:B A B A +;(f )F= AB 。

5.(25)10=(00100101)8421BCD ;(46+27)10= (01110011)8421BCD6. 高阻态 。

7. B A B A +, AB B A +8. 接电源9. 相邻10. 少 输入端的个数 。

11. F 1=m 0+m 3+m 5+m 7 。

12. K J Q k Q J Q n n n ++=+1二、逻辑代数公式化简函数(每小题2分,共6分)1. A+C;2. B A B A +;3. AB+C A三、组合逻辑电路的分析与设计(每题10分,共30分) 1. AB P =, AB A AP Q ==, AB B BP R ==,S=B A B A AB B AB A QR +=∙=, C=AB P =真值表如下:由真值表可知,它的逻辑功能是半加器。

2.题解:2102101m m m m m m F =++=7657652m m m m m m F =++=第三大题第1小题真值表第三大题第2小题图3.设特快、直快和普快分别为A 、B 、C ,开车信号分别为Y A 、Y B 、Y C ,车开出为“1”给开车信号为“1”。

真值表和逻辑图如下:第三大题第3小题的真值表和逻辑图四、时序逻辑电路的分析与设计(每题10分,共30分)1.解:n Q J 00= K 0=0; 01n n Q Q D ∙= nD Q R 1=分析:设触发器的初始状态为0(1)CP1的后沿到来时,触发器0状态改变为“1”态,触发器1状态不变。

(2)CP2的后沿到来时,由于触发器1的状态改变为“1”态,即0,111==n nQ Q ,而D n R Q =1,R D 是置“0”端,所以,触发器0置“0”。

理工数字逻辑道填空题参考答案

120余道填空题参考答案(*号的不作要求)一、数制和码制1.十进制数254.75的二进制编码11111110.11 ,十六进制编码FE.C 。

2. 将(459)10编成(0100 0101 1001)8421BCD, ( 011110001100 )余3码8421BCD 4位一一对应余3码就是8421+ 33.下列数中,哪个数最大 D (A、B、C、D)。

A、二进制111B、八进制110C、十进制101D、十六进制1004.下列哪个数是合法的8进制数 B (A、B、C、D)。

A、128B、120C、912D、1A25、已知[N]补=10100101,则其[N]原= 11011011 。

5-1、余3码10001000对应的2421码为 C 。

A.01010101 B.10000101 C.10111011 D.11101011前4就是2421码+3=余3 后5~9就是余3+3=24215-2、在计算机中进行加减运算时常采用 D 。

A ASCIIB 原码C 反码D 补码5-3、二进制小数-0.0110的补码表示为 1.1010 。

1代表负5-4、0的原码有 2 形式,反码有 2 形式,补码有 1 形式。

二、门电路6、CMOS电路不用的输入端不能(能、不能)悬空。

7、CMOS“与非”门用的多余输入端的处理方法有: A 。

A、接逻辑“1”B、接逻辑“0”C、悬空8、CMOS门电路的功耗比TTL门电路的功耗小(大、小)。

9、TTL门电路的速度比CMOS门电路速度高(高、低)。

10、与普通门电路不同,OC门在工作时需要外接上拉电阻和电源。

11、OC 门的输出端相连可以实现线与。

*12、有两个TTL与非门,它们的关门电平分别为V offA=1.1V,V OFFB=0.9V;开门电平分别为V onA=1.3V,V onB=1.7V。

它们输出的高低电平均相同, A (A、B)门的抗干扰能力强。

13、一片与非门芯片具有三个三输入端与非门,该芯片引脚数至少要14 。

数字逻辑试题及答案

数字逻辑试题及答案一、选择题(每题2分,共20分)1. 以下哪个是数字逻辑电路中的基本逻辑运算?A. 加法B. 减法C. 乘法D. 与运算2. 一个3输入的与门,当所有输入都为高电平时,输出为:A. 低电平B. 高电平C. 浮空D. 不确定3. 一个D触发器的Q端在时钟信号上升沿触发时,其状态变化为:A. 保持不变B. 从0变到1C. 从1变到0D. 从D输入端状态变化4. 在数字电路中,以下哪个不是布尔代数的基本定理?A. 幂等律B. 交换律C. 反演律D. 分配律5. 一个4位二进制计数器在计数到31后,下一个状态是:A. 00000B. 00001C. 11111D. 不能确定6. 以下哪个不是数字逻辑电路设计中的优化方法?A. 布尔代数简化B. 逻辑门替换C. 增加冗余D. 逻辑划分7. 一个异或门的真值表中,当输入相同,输出为:A. 0B. 1C. 无法确定D. 无输出8. 在数字电路中,同步计数器与异步计数器的主要区别在于:A. 计数范围B. 计数速度C. 电路复杂度D. 计数精度9. 以下哪个不是数字逻辑电路中的存储元件?A. 触发器B. 寄存器C. 计数器D. 逻辑门10. 一个简单的数字逻辑电路设计中,如果需要实现一个2输入的或门,至少需要几个与门?A. 1B. 2C. 3D. 4答案:1. D2. B3. D4. C5. B6. C7. A8. B9. D10. A二、填空题(每空2分,共20分)1. 数字逻辑电路中最基本的逻辑运算包括______、或运算、非运算。

2. 一个2输入的与门,当输入都为高电平时,输出为______。

3. 布尔代数的基本定理包括______、结合律、分配律等。

4. 一个D触发器的Q端在时钟信号上升沿触发时,Q端状态与______相同。

5. 4位二进制计数器的计数范围是从______到1111。

6. 数字逻辑电路设计中的优化方法包括布尔代数简化、逻辑门替换、______等。

数字逻辑总复习题答案

数字逻辑总复习题答案一、选择题1. 以下哪个选项是数字逻辑中的基本逻辑运算?A. 与运算B. 或运算C. 非运算D. 所有以上选项答案:D2. 在数字逻辑中,一个变量的真值表可以有多少行?A. 1B. 2C. 4D. 8答案:C3. 逻辑门电路中的输出状态取决于输入状态,以下哪个描述是正确的?A. 输出状态与输入状态相同B. 输出状态与输入状态相反C. 输出状态由输入状态的组合决定D. 输出状态与输入状态无关答案:C二、填空题1. 在数字逻辑中,逻辑或运算的符号通常表示为______。

答案:∨2. 一个三变量的逻辑函数,其真值表最多可以有______种不同的输出组合。

答案:83. 逻辑门电路中的与非门(NAND)可以看作是______和______的组合。

答案:与门,非门三、简答题1. 请简述数字逻辑中的布尔代数基本定理。

答案:布尔代数的基本定理包括交换律、结合律、分配律、幂等律、补余律等,这些定理是构建和简化逻辑表达式的基础。

2. 描述逻辑门电路中的异或(XOR)门的功能。

答案:异或门的输出仅在输入状态中奇数个为真时为真,其余情况下输出为假。

四、计算题1. 给定逻辑函数F(A, B, C) = Σ(0, 1, 2, 7),请写出其对应的真值表。

答案:| A | B | C | F ||||||| 0 | 0 | 0 | 0 || 0 | 0 | 1 | 1 || 0 | 1 | 0 | 1 || 0 | 1 | 1 | 0 || 1 | 0 | 0 | 1 || 1 | 0 | 1 | 0 || 1 | 1 | 0 | 0 || 1 | 1 | 1 | 1 |2. 利用卡诺图化简逻辑函数F(A, B, C, D) = Σ(0, 1, 2, 3, 8, 9,10, 11, 12, 13, 14, 15)。

答案:F(A, B, C, D) = A'C + BD请注意,以上内容仅为示例,实际的试题和答案应根据具体的课程内容和教学要求来制定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

120余道填空题参考答案(*号的不作要求)一、数制和码制1.十进制数254.75的二进制编码11111110.11 ,十六进制编码FE.C 。

2. 将(459)10编成(010*********)8421BCD, ( 011110001100 )余3码3.下列数中,哪个数最大 D (A、B、C、D)。

A、二进制111B、八进制110C、十进制101D、十六进制1004.下列哪个数是合法的8进制数 B (A、B、C、D)。

A、128B、120C、912D、1A25、已知[N]补=10100101,则其[N]原= 11011011 。

5-1、余3码10001000对应的2421码为 C 。

A.01010101 B.10000101 C.10111011 D.111010115-2、在计算机中进行加减运算时常采用 D 。

A ASCIIB 原码C 反码D 补码5-3、二进制小数-0.0110的补码表示为 1.1010 。

5-4、0的原码有 2 形式,反码有 2 形式,补码有 1 形式。

二、门电路6、CMOS电路不用的输入端不能(能、不能)悬空。

7、CMOS“与非”门用的多余输入端的处理方法有: A 。

A、接逻辑“1”B、接逻辑“0”C、悬空8、CMOS门电路的功耗比TTL门电路的功耗小(大、小)。

9、TTL门电路的速度比CMOS门电路速度高(高、低)。

10、与普通门电路不同,OC门在工作时需要外接上拉电阻和电源。

11、OC 门的输出端相连可以实现线与。

*12、有两个TTL与非门,它们的关门电平分别为V offA=1.1V,V OFFB=0.9V;开门电平分别为V onA=1.3V,V onB=1.7V。

它们输出的高低电平均相同, A (A、B)门的抗干扰能力强。

13、一片与非门芯片具有三个三输入端与非门,该芯片引脚数至少要14 。

(14、16、18、20)。

14、三态门除了具有高电平和低电平两种状态外,还有第三种状态叫高阻状态。

15、三极管作为开关器件“非门”时,不能工作在放大状态。

16、将2输入端与非门当作非门使用时,则另一输入端接 1 (0,1);将2输入端或非门当作非门使用时,则另一输入端接0 (0,1)。

17、74LS00是TTL电路(TTL电路、CMOS电路)。

74HC00是CMOS电路(TTL电路、CMOS电路)。

18、TTL门电路主要外部特性参数有标称电平、开门电平、关门电平延时、功耗、扇入系数、噪声容限等等。

*19、NMOS门电路如图19所示,输入变量为A、B,输出函数L= 。

图1920、一片芯片具有四个两输入端或非门,该芯片引脚数至少有14 (14、16、18、20)。

21、74LS00和74HC00芯片,74LS00 芯片速度更快。

图2222、上图中,Y1= L , Y2= L 。

(H=高电平、L=低电平) *23、某集成电路芯片,查手册知其最大输出低电平V OL max=0.1V ,最大输入低电平V IL max=1.5V ,最小输出高电平V OH max=4.9V ,最小输入高电平V IH max=3.5V ,则其低电平噪声容限V NL = B 。

A 2.0V B 1.4V C 1.6V D 1.2V23-1、下列真值表完成的逻辑函数为 C 。

A 、F=AB B 、F=A-BC 、F= A ⊕BD 、F=A+B23-2、X ⊕0⊕1⊕1⊕1⊕0=。

23-3、下列逻辑函数中,与A F =相等的是 B 。

)(A 11⊕=A F )(B A F =2⊙1 )(C 13⋅=A F )(D 04+=A F三、逻辑函数化简和冒险24、三变量A 、B 、C ,最小项m 0=1,m 1= 0 ,m 2= 0 。

25、x ⊕0⊕1⊕0⊕1= x 。

(X 是一位二进制数)26、由函数构成的逻辑电路 有 (有,无)险象。

27、逻辑函数F AE CDE AC =++构成的逻辑电路,(有、无) 无 逻辑冒险。

28、说法“一个没有冒险现象的逻辑表达式是最简逻辑表达式”错误。

(正确、错误)29、说法“用卡诺图简化逻辑函数时,从没有多种入圈方式的1开始画卡诺圈,这样将不会产生多余圈”正确。

(正确、错误)30、说法“卡诺圈中1的个数应该为2的整数倍,如2、4、6…个1”错误。

(正确、错误)31、逻辑函数的表达方法有表达式、电路图、真值表等。

32、竞争冒险是由于门电路延时产生的。

四、组合逻辑电路33、常用MSI组合逻辑电路有编码器、译码器、数据选择器数值比较器、全加器等。

34、说法“组合逻辑电路的输出只和即时输入有关,与过去的输入和输出无关”正确。

(正确、错误)35、与门、或门和非门是组合逻辑电路的基本单元。

36、奇偶校验器只能检测奇次(奇次、偶次)数据传输错误。

37、数据选择器的功能是 C (A、B、C、D)。

A、从两路输入信号中选一路输出。

B、把一路信号分时从几路输出。

C、从多路输入信号中选一路输出。

D、根据控制信号,决定是输出输入信号,还是输出处于高阻状态。

38、数据比较器如图所示,如果引脚234分别接“100”;9、11、14、1脚接“1001”;10、12、13、15接“1001”。

那么567脚分别输出 001 。

39、超前进位加法器与串行进位加法器相比,速度更快。

63、若要某共阴极数码管显示数字“3”,则显示代码abcdefg为。

(0000000~1111111)64、若要某共阳极数码管显示数字“3”,则显示代码abcdefg为1111001 。

(0000000~1111111)五、时序电路40、触发器是时序逻辑电路的基本单元。

41、就总体而言,主从触发器在CP的一个变化周期中,它的状态改变了 1 次,克服了空翻现象。

42、 C (A、B、C、D)克服了空翻现象。

A、基本JK触发器B、时钟JK触发器(即电平JK触发器)C、主从JK触发器D、时钟RS触发器43、与主从触发器相比,边沿触发器抗干扰性能更好。

44、触发器按结构可分为基本触发器、钟控触发器、主从触发器、边沿触发器等。

45、触发器按功能可分为RS触发器、JK 触发器、 D 触发器、T触发器等。

46、JK触发器的状态由Q n=0转换到Q n+1=1,J和K端正确而又完整的控制状态是 A (A、B、C、D)。

A、1 XB、0 XC、X 1D、X 0 (X表示1或0)47、某同步时序电路有9个状态,该电路需要 4 个触发器。

48、要设计一个14进制加法计数器,该电路至少需要 4 个触发器。

49、时序电路的逻辑功能可以用特征方程、驱动方程、状态图、状态表、时序图等方式描述。

50、请列举两种常用集成时序逻辑部件计数器、寄存器。

51、两片十进制计数器级联后,最多可构成100 进制计数器。

52、状态编码时,状态表中出现次数最多的次态应分配逻辑0 (0、1)。

53、异步时序电路中,触发器状态的变化不是(是、不是)同时发生的。

54、下面哪种说法正确 B (A、B、C)。

A、同样的输入,对于RS边沿触发器与RS主从触发器,输出状态相同。

B、同样的输入,对于RS边沿触发器与RS主从触发器,输出状态未必相同。

C、同样的输入,对于RS时钟触发器与RS主从触发器,输出状态相同。

55、图示电路是(同步时序电路,异步时序电路)异步时序电路。

56、某同步时序电路,状态转移图如图所示,其功能是具有自启动功能的模5二进制加法同步计数器。

57、某自动饮料售卖机连续投入两个一元硬币时,给出一瓶饮料,给饮料控制信号应该用时序逻辑电路(组合逻辑电路、时序逻辑电路)产生。

58、某密码箱当连续按两次“1”键,再按一次“2”键时,密码箱打开,密码箱开启控制信号应该用时序逻辑电路(组合逻辑电路、时序逻辑电路)产生。

59、某同步时序电路,状态转移图如图所示,其功能是111序列检测器。

、I IN/OUT60、时序逻辑电路设计步骤是: A (A 、B 、C 、D )。

A 、 依题意画出状态转换图,列状态表,简化状态表,状态编码,画激励和输出卡诺图,得到激励函数和输出函数表达式,依据激励函数和输出函数表达式画电路图。

B 、 依题意画出状态转换图,列状态表,状态编码,简化状态表,画激励和输出卡诺图,得到激励函数和输出函数表达式,依据激励函数和输出函数表达式画电路图。

C 、依题意画出状态转换图,进行状态编码,画电路图,得到激励函数和输出函数表达式。

D 、 依题意画出状态转换图,简化状态图,得到激励函数和输出函数表达式,进行状态编码,画电路图。

61、下列电路中,实现逻辑功能n n Q Q =+1的是 BD 。

)(A )(B)(C (D) 62、某移位寄存器的时钟脉冲频率为100KHZ ,欲将存放在该寄存器中的数左移8位,完成该操作需要 B 时间。

1C >D 1CP Q 1C > J 1 K 1 CP Q1C > N 1 CP Q0 1C > D 1CP Q QA.10μSB.80μSC.100μSD.800ms63、异步时序电路分为脉冲异步时序电路和电位异步时序电路。

六、存储器和可编程器件64、用ROM实现的逻辑函数如上图右所示,写出逻辑函数(不用简化)。

65、动态MOS存储单元(DRAM)是利用电容存储信息的,为不丢失信息,必须定期刷新,所以DRAM工作时必须辅以刷新电路。

66、根据写入的方式不同,只读存储器ROM分为MROM ,PROM ,EPROM ,E2PROM 。

67、某存储器有10条地址线和8条数据线,该储存器的容量是210字节。

68、存储器的存储矩阵由与阵列和或阵列组成。

69、可编程逻辑器件有PLA、PAL、GAL、FPGA等种类。

70、GAL与阵列可编程,或阵列固定,输出可组态。

七、其他*70、若传输门电路的个数为N、平均延迟时间为t pd,下面环形多谐振荡器的振荡周期为。

*71、555定时器可构成施密特触发器、单稳态触发器、多谐振荡器等电路。

*72、单稳态触发器的暂稳态维持时间与触发脉冲的宽度和幅度(有、无关)。

*73、施密特触发器与双稳态触发器的区别为施密特触发器是靠触发,适用于慢变化的信号,而双稳态触发器是触发,不适合于慢变的信号。

74、逻辑功能可由用户根据自己的需要来设计并通过编程实现的器件是PLD 。

(组合逻辑器件、时序逻辑器件、A/D、D/A、PLD)*75、要保证采样后的信号能反映原来的模拟信号,若A/D转换器输入模拟信号最高变化频率为1MHz,取样频率的下限是。

*76、8位ADC输入满量程为10V,当输入5V电压值,数字输出量为10000000 。

*77、A/D转换要经过采样、保持、量化、编码等步骤。

78、双踪示波器可以 C (A、B、C、D)。

A、能观测两路信号的电压,只能显示一路信号的波形。