分频器电路图

六分频加法电路的设计

六分频加法电路的设计1相关原理分析1.1计数器计数器是实现分频电路的基础,计数器包括普通计数器和约翰逊计数器两种,这两种电路均可用于分频电路中。

最普通的计数器莫过于加法(减法)计数器。

以3位二进制计数器为例,计数脉冲CP 通过计数器时,每输入一个计数脉冲,计数器的最低位(记为Q0,后面的依次记为Q1、Q2、)翻转一次,Q1、Q2、都以前一级的输出信号作为触发信号。

分析这个过程,不难得出输出波形。

图1-1 3位二进制计数器时序图由上很容易看出Q0 的频率是CP的1/2,即实现了2分频,Q1则实现了4分频,同理Q2实现了8分频。

这就是加法计数器实现分频的基本原理。

约翰逊计数器是一种移位寄存器,采用的是把输出的最高位取非,然后反馈送到最低位触发器的输入端。

约翰逊计数器在每一个时钟下只有一个输出发生变化。

同样以3为二进制为例。

假设最初值或复位状态是000,则依次是000、001、011、111、110、100、000这样循环。

由各位的输出可以看出,约翰逊计数器最起码能实现2分频。

1.2两种计数器的比较从以上分析可以看出约翰逊计数器没有充分有效地利用寄存器的所有状态,而且如果由于噪声引入一个无效状态,如010,则无法恢复到有效循环中去,需要加入错误恢复处理。

但其较之加法计数器也有它的好处。

同一时刻,加法计数器的输出可能有多位发生变化,因此当使用组合逻辑对输出进行译码时,会导致尖峰脉冲信号。

而约翰逊计数器可以避免这个问题。

1.3 计数器的选择本次训练要求设计的是加法分频电路,选择的是加法计数器。

加法计数器实现分频较之约翰逊计数器简单,编程也容易理解一些,对于初学者也较容易上手。

在前面已经讲过加法计数器实现2n的分频的方法,现在就不在赘述。

1.4 偶数分频器如前所述,分频器的基础是计数器,设计分频器的关键在于输出电平翻转的时机。

偶数分频最易于实现,要实现占空比为50%的偶数N分频,一般来说有两种方案:一是当计数器计数到N/2-1时,将输出电平进行一次翻转,同时给计数器一个复位信号,如此循环下去;二是当计数器输出为0到N/2-1时,时钟输出为0或1,计数器输出为N/2到N-1时,时钟输出为1或0,当计数器计数到N-1时,复位计数器,如此循环下去。

1.变换器

Uo T1 Uz t -Uz T2

图5 V/f转换器各点的波形

4.f/V转换器 f/V转换器能把输入频率信号转换成相应的电 压信号,使Uo随着fi的变化而变化.

电路图6:

-E +E R1 R2 +E R11 5 D1 Ui D2 3 R5 3 R6 R7 R +E C T2 R6 2 1 2 5 N1 4 D3 U1 C1 UN 2 Up 1 R10 R4 -E R3 N2 D4 4 R9 T1 C2 U2 Vz 3 R12 4 1 Uo 5 N3

由N3构成低通滤波器,输出电压平均值:

U o = TωVZ f i

图7输出各点波形

Ui 0

U1

0

Tω U2

Vz 0

UH

UL UH UP

图7输出各点波形

�

Uc t Up1 Up2 Up t Up1 Up2

Uo T1 Uz t -Uz T2

图5 V/f转换器各点的波形

显然,Ui越大,C的充电电流ic及锯齿波电压的 斜率越大.因此,每次达到负的门限电压Up2 的时间越短,输出脉冲的频率就越高. C的充电电压:

1 t U c (t ) = ∫0 U i dt RC

输出 滞后比较器

R8

单稳态电路 图6 f/V转换器电路图

放大器N1构成滞后比较器,输 入有D1,D2限幅保护.放大器 N1将输入信号转换成频率相同 的方波信号,再经微分电容C1 和二极管D3把上升窄脉冲送到 放大器N2. 放大器N2构成单稳态电路,常 态下其反相输入UN为负电位, 使放大器N2输出高电平,T1, T2导通,这时T1的输出点U2为 低电平.正脉冲触发使放大器 N2迅速翻转为低电平,T1截止, T1的输出点U2为高电平,它的 值等于稳压管稳压值Vz. 那么,UN保持高电平UH,如图7. 同时T2截止,使C通过R充电, 经过tω时间Up上升到UH以上使 N2再次翻转"复位",单稳结 束.U2输出定宽度(tω),定 幅度(Uz)的脉冲,其占空比 随着输入频率的升高而增大.

手把手教你做音箱分频器

手把手教你做音箱分频器1.电感骨架依据电感线圈的要求,选择合适的非金属骨架,如焊锡丝、密封用生料带的塑料骨架以及其它木质、胶质骨架等。

2.漆包线选用粗细合适、质量上乘的漆包线若干。

3.阻容件根据电路要求选择容量、阻值和功率合适的电容、电阻,分频电容最好选用进口或国产优质CBB电容,电阻以大功率水泥电阻为首选。

4.粘合剂此剂可选用市售“立得牢”等强粘度胶。

5.硬币、螺栓螺栓选择直径4mm左右的铜质品,其长度则根据电感骨架的高度而定。

6.敷铜板根据分频元器件的多少,选择大小合适的优质敷铜板,线路走向则根据设计要求用美工刀刻制。

7.透明胶带一盘制作1.绕电感将粘合剂瓶顶、底中间各钻一直径略大于漆包线的小孔(因液体粘稠,故不会从孔中流出),在两孔各穿一段塑料胶管之后,把漆包线从两胶管中穿过,以保漆包线通过两孔时不被刮伤,然后一人将漆包线一端拉紧,另一人就可拿漆包线的另一端在骨架上绕线,绕时双手不可接触漆包线,因漆包线在通过粘合剂时已均匀地敷上了一层粘合剂,可用手捏住骨架两端使之旋转,待电感圈数绕足之后,将多余的漆包线剪掉,固定好外引出线,待线上的粘合剂凝固以后,用透明胶带在线圈上紧绕几层。

2.元器件安装根据电感线圈及阻容件在板上的位置,用小钻在板上打好孔,在硬币中间钻一比铜螺栓直径略大的孔,将铜螺栓依次穿过硬币、线圈和电路板,然后再垫上弹簧垫片,用螺母紧固,将线圈、电容和电阻的引线刮净上锡后焊在相应的位置上,最后在板上焊接好进出线。

经过以上操作,一只质优价廉的分频器便制作完工,剩下的就是你体验成功的喜悦了。

分频器电感接线有讲究音箱分频器中电感线圈的接法对音质音色影响极大。

使用的一对倒相式音箱,电感线圈接法是外圈入里圈出音色均衡圆润。

曾使用里圈入外圈出接法,结果低音全无。

质量分频器的业余制作方法高保真的音箱多数都是由两只或两只以上的扬声器单元构成,要高质量的还原20Hz~20kHz全频段的音频信号,必须借助优质分频器的协助。

数字频率计分频电路的设计

f

=

1 (65536 ×n +

m)

× T R ×2 K

其中 : n 为溢出次数 , m 为最后一次计数值 , K CL K CL R CL K MOV C ,DOU T RLC A DJ NZ R0 ,RD - AD

RET

312 MAX7219 显示子程序 MAX7219 显示程序就是 89C51 在 CL K ( P212) ,

LOAD ( P210) 时序的配合下 , 通过 D IN ( P211) 向

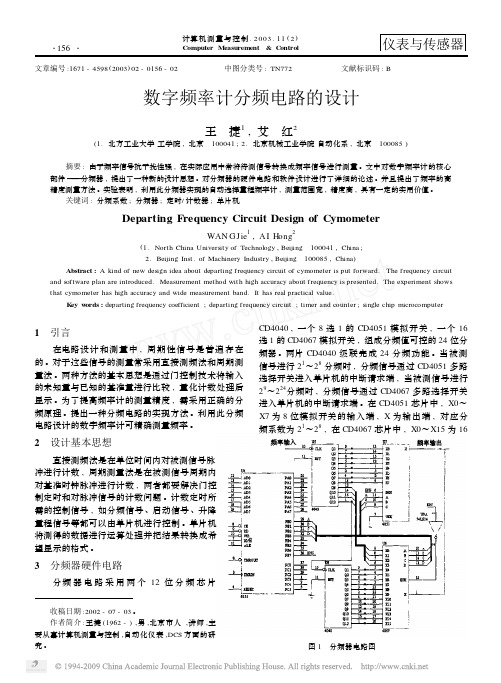

3 分频器硬件电路

分频 器 电 路 采 用 两 个 12 位 分 频 芯 片

CD4040 , 一个 8 选 1 的 CD4051 模拟开关 , 一个 16 选 1 的 CD4067 模拟开关 , 组成分频值可控的 24 位分 频器 。两片 CD4040 级联完成 24 分频功能 。当被测 信号进行 21~28 分频时 , 分频信号通过 CD4051 多路 选择开关进入单片机的中断请求端 , 当被测信号进行 29~224分频时 , 分频信号通过 CD4067 多路选择开关 进入单片机的中断请求端 。在 CD4051 芯片中 , X0~ X7 为 8 位模拟开关的输入端 , X 为输出端 , 对应分 频系数为 21~28 , 在 CD4067 芯片中 , X0~X15 为 16

4 分频原理

为了迅速确定分频系数 , 采用 16 位定时/ 计数器

进行定时计数 。方法如下 : 单片机内部定时计数器的

计数范围为 0~65535 。为保证测量精度 , 选择计数

一文看懂汽车音响分频器接线方法图解

一文看懂汽车音响分频器接线方法图解分频器原理从电路结构来看,分频器本质上是由电容器和电感线圈构成的LC 滤波网络,高音通道是高通滤波器,它只让高频信号通过而阻止低频信号;低音通道正好相反,它只让低音通过而阻止高频信号;中音通道则是一个带通滤波器,除了一低一高两个分频点之间的频率可以通过,高频成份和低频成份都将被阻止。

在实际的分频器中,有时为了平衡高、低音单元之间的灵敏度差异,还要加入衰减电阻;另外,有些分频器中还加入了由电阻、电容构成的阻抗补偿网络,其目的是使音箱的阻抗曲线心理平坦一些,以便于功放驱动。

位于功率放大器之后,设置在音箱内,通过LC滤波网络,将功率放大器输出的功率音频信号分为低音,中音和高音,分别送至各自扬声器。

连接简单,使用方便,但消耗功率,出现音频谷点,产生交叉失真,它的参数与扬声器阻抗有的直接关系,而扬声器的阻抗又是频率的函数,与标称值偏离较大,因此误差也较大,不利于调整。

将音频弱信号进行分频的设备,位于功率放大器前,分频后再用各自独立的功率放大器,把每一个音频频段信号给予放大,然后分别送到相应的扬声器单元。

因电流较小故可用较小功率的电子有源滤波器实现,调整较容易,减少功率损耗,及扬声器单元之间的干扰。

使得信号损失小,音质好。

但此方式每路要用独立的功率放大器,成本高,电路结构复杂,运用于专业扩声系统。

分频器技术参数第一个,就是分频器的分频点,这个应该不用多说。

第二个,就是所谓分频器的“路”,也就是分频器可以将输入的原始信号分成几个不同频段的信号,我们通常说的二分频、三分频,就是分频器的“路”。

第三个,就是分频器的“阶”,也称“类”。

一个无源分频器,本质上就是几个高通和低通滤波电路的复合体,而这些滤波电路的数量,就是上面所说的“路”。

但是在每一个滤波电路中,还有更精细的设计,换句话说,在每一个滤波电路中,都可以分别经过多次滤波,这个滤波的次数,就是分频器的“阶”。

课程设计—分频器的制作

电子技术课程设计报告学院:专业班级:学生姓名:学号:指导教师:完成时间:成绩:分频器的制作设计报告一. 设计要求把1000HZ的信号分成500Hz,100Hz的信号,用拨动开关控制。

发挥部分:1、200Hz信号的产生 2、倍频信号的产生。

二. 设计的作用、目的1、掌握运用中规模集成芯片设计分频器的方法。

2、掌握使用与非门、555单稳态产生倍频信号的方法。

三.设计的具体实现1、单元电路设计(或仿真)与分析1、分频信号的产生:电路图如下74ls192是同步十进制可逆计数器,具有双时钟输入,并具有异步清零等功能。

在此电路中,计数器处于加计数状态,输入脉冲1000Hz由5脚输入,用清零法组成进制可变的计数器,并通过单刀双掷开关控制。

仿真结果图如下:①当开关拨到1档时,上面频率计数器计输入信号频率为1000Hz,下面频率计数器计数频率为500Hz信号。

②当开关拨到2档时,上面频率计数器计输入信号频率为1000Hz,下面输出频率计数器显示100Hz信号。

2、200Hz信号的产生:电路图如下74ls192是同步十进制可逆计数器,具有双时钟输入,并具有异步清零等功能。

仿真结果图如下:在此电路中,计数器处于加计数状态,输入脉冲1000Hz由5脚输入,用清零法组成进制可变的计数器,2脚即输出200Hz信号。

2、倍频信号的产生:倍频信号原理图如下,输入信号由最左端输入方波(频率大于1000Hz并且峰峰值大于3v小于5v效果好)其中第一个与非门连接成非门使用,起着对输入信号倒相的作用。

这样,当有一个方波脉冲信号输入时,由C1、R1组成的微分电路将在脉冲信号的前沿产生一个正向微分脉冲信号,同时在方波下降沿处产生负向脉冲,另一路经过反相后,C2、R2微分电路产生负向脉冲(另一路产生正向脉冲同时)和负向脉冲,经过二极管滤除正向脉冲作为555单稳态的2脚触发端输入信号,而555单稳态3脚输出倍频后的方波。

仿真结果图如下:左端频率计数器显示的是输入的1000Hz的信号,右端频率计数器显示的是倍频后输出的2000Hz的信号示波器显示:号2000Hz。

分频电路

仿真波形

CLK

上பைடு நூலகம்沿Q1 上升沿Q0

下降沿Q1 下降沿Q0 Q1“相或” Q0 “相或”

举一反三

实现任意的奇数分频。归类的一般方法为:对 于实现占空比为50%的N倍奇数分频. 步骤:1. 进行上升沿触发进行模N计数,计数选 定到某一个值进行输出时钟翻转,然后经过(N1)/2再次进行翻转得到一个占空比为非50%的 奇数N分频时钟, 2.同时进行下降沿触发的模N计数,同理。 3.两个占空比非50%的N分频时钟相或运算 得到占空比为50%的奇数N分频时钟。 注意:“相或“的两端要适当选取,例如N=5时 选Q1;N=7时,选Q2;N=15时,选Q3。

分频电路部分:采用格雷码计数器,可有效的避免毛刺现象的发生。 格雷码跳变顺序:001—011—010—110—111—101 (Q2Q1Q0) 用卡诺图化简之后的逻辑表达式:Q*2=Q2Q1+Q1Q’0 Q1=Q’0Q1+Q’2Q0 Q0=Q’1Q0+Q2Q1

由于所选择的格雷码没有000状态,所以需保证起始状态不能为000, 则多了一个d高电平,用来控制起始状态。 q2的输出即是对时钟信号clk三分频之后的信号波形。

占空比为1:1的奇数分频电路的实现:

方法三:利用如下电路实现

输入时钟频率:CLK。器件:一个非与门,两个D触 发器,分别为D1(输入), Q1(输出)和D2,Q2 注意:开始要复位触发器。 D0=Q0*=A’ AND B’

D1=Q1*=A Clk3*=(CLK+B’)AND(A+clk3)

错位相或法

以3分频为例: 首先设计模三的计数器,其真值表如下:

2.5分频电路的设计

数电第二次大作业--2.5分频电路的设计班级:001111姓名:江新远 00111116时间:2013年6月16日一、设计要求利用所学数字电路知识设计2.5分频电路。

二、设计思路本次数电实验共采用两种设计方案,各方案具体实现思想如下:方案一:首先进行模3的计数,在计数到2时,将输出时钟赋为'1',而当回到计数0时,又赋为0,这样,当计数值为2时,输出时钟才为1,因此,只要保持计数值2为半个输入时钟周期,即可实现2.5分频时钟。

因此,保持2为半个时钟周期即是该设计的关键。

从中可以发现,因为计数器是通过时钟上升沿计数,故可在计数为2时对计数触发时钟进行翻转,那么,时钟的下降沿就变成了上升沿。

即在计数值为2期间的时钟下降沿变成了上升沿,也就是说,计数值2只保持了半个时钟周期。

由于时钟翻转下降沿变成上升沿,因此,计数值变为0。

所以,每产生一个2.5分频时钟的周期,触发时钟都要翻转一次。

方案二:将2.5分频电路分解为两个五分频电路,其中一个为上升沿触发,另外一个为下降沿触发,两个电路之间存在2.5个时钟脉冲的间隔,将这两个5分频电路的输出用或门进行或运算,即可得出所需2.5分频电路。

三、电路设计过程方案一:1. 实验原理图如下。

电路是一个分频系数为2.5的分频器电路,该电路是用VHDL 来设计半整数分频器的。

它由模3计数器、异或门和D 触发器组成。

2. 其中模3计数器部分可以用74LS161实现,也可以用VHDL 直接编写,本次设计采用VHDL 语言编写模3计数器。

下面是模3计数器的VHDL 源代码library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity dec is port( fin:in std_logic; fout:buffer std_logic); end dec;architecture fpq of dec is signal clk,div2:std_logic;signal count:std_logic_vector(3 downto 0);signal preset:std_logic_vector(3 downto 0):="0011"; begin clk<=fin xor div2; p1:process(clk) begin if clk'event and clk='1'then if(count="0000")then count<=preset-1; fout<='1';异或门带预置数功能的模N 减法计数器2分频计数器elsecount<=count-1;fout<='0';end if;end if;end process p1;p2:process(fout)beginif(fout'event and fout='1')thendiv2<=not div2;end if;end process p2;end fpq;生产元件符号:3. 电路设计图如下4. 仿真结果:方案二:1. 计数器使用74LS161设计实现,采用Oc 置数法(使用后5个状态)来实现计数器,即计到15(1111)状态时产生进位信号,利用进位信号使计数器返回初态11(1011)。