PLL格式_频率合成实验

DDS激励PLL方式的频率合成器设计

科技与创新┃Science and Technology & Innovation·120·文章编号:2095-6835(2016)11-0120-02DDS 激励PLL 方式的频率合成器设计武志敏(河北诺亚人力资源开发有限公司,河北 石家庄 050081)摘 要:DDS+PLL 是目前频率合成技术的常用组合方式之一。

首先就DDS+PLL 的几种常用合成方式的特点进行了简单介绍,然后重点利用DDS 激励PLL 的方式,实现了一种低杂散低相噪的频率合成器的设计。

在自己的工作中证明了该方案的可实现性。

关键词:DDS ;PLL ;低杂散;低相位噪声;频率合成器中图分类号:TN97 文献标识码:A DOI :10.15913/ki.kjycx.2016.11.120现代通信技术的发展迅猛,使得电子对抗领域对频率源的准确度、换频时间以及杂散相位噪声等技术指标的要求越来越高。

一般我们经常使用DDS+PLL 的方法来实现高频率、小步进、低相噪的频率合成器设计。

以下是对DDS+PLL 的常见组合方式作一简介。

1 DDS+PLL 的频率合成方式 1.1 DDS 内插于PLL这种方式是把DDS 看作分频器插入PLL 。

正是因为DDS 的频率的分辨率是非常高的,因而可以实现宽频带、小步进频率的合成。

但是因为DDS 还可实现小数分频,所以会有部分频段出现杂散现象。

1.2 DDS 倍频于PLL此种方式是将DDS 作为PLL 倍频的参考信号,PLL 就成了N 倍频环。

此方式的优点是:电路设计简单,可以得到较高的频率输出。

因而适合应用在相对杂散、指标要求不是很高的分机以及系统中。

缺点是:因为PLL 用于直接倍频,所以在环路噪声带宽内的输出信号,相位噪声以及杂散指标,都将恶化20 dB 。

1.3 DDS 和PLL 直接混频此方式是将PLL 信号作为本振信号,将DDS 信号做上变频、混频后,再通过一级带通滤波器将信号输出。

模拟锁相环实验报告

模拟锁相环实验报告锁相环(PLL)是一种常见的控制系统,它可以将输入信号的频率和相位与参考信号匹配,从而实现精确的信号同步和频率锁定。

本次实验旨在通过模拟锁相环的实验,了解PLL的基本原理和实现方式,并探究其在频率合成和时钟恢复等应用中的优势和局限性。

一、实验原理1.1 PLL的基本原理PLL由相频比较器、环形控制器、振荡器和分频器等组成。

其基本原理如下:(1)将参考信号和输出信号输入相频比较器,得到误差信号;(2)将误差信号输入环形控制器,控制其输出的控制电压;(3)将控制电压输入振荡器,控制其输出的频率和相位;(4)将振荡器的输出信号通过分频器分频后反馈给相频比较器,形成闭环控制。

通过不断比较和修正,PLL可以使输出信号的频率和相位与参考信号匹配,从而实现锁定。

1.2 实验器材本次实验采用的器材如下:信号发生器、示波器、多路开关、振荡器、计数器等。

1.3 实验步骤(1)将信号发生器产生的正弦波信号作为参考信号,通过示波器观测其频率和相位;(2)将信号发生器产生的方波信号作为输入信号,通过多路开关控制输入信号的频率和幅值;(3)将输入信号和参考信号输入相频比较器,得到误差信号;(4)将误差信号输入环形控制器,控制其输出的控制电压;(5)将控制电压输入振荡器,控制其输出的频率和相位;(6)将振荡器的输出信号通过分频器分频后反馈给相频比较器,形成闭环控制;(7)通过计数器观测输出信号的频率和相位,调整环形控制器的参数,使输出信号与参考信号匹配。

二、实验结果在实验过程中,我们先设置参考信号的频率为1KHz,通过示波器观测其频率和相位,然后将信号发生器产生的方波信号作为输入信号,进行频率和幅值的调节,使其与参考信号匹配。

在调节的过程中,我们观测到输出信号的频率和相位逐渐趋近于参考信号的频率和相位,最终实现了同步锁定。

然后,我们进一步测试了PLL在频率合成和时钟恢复等应用中的性能。

我们将输入信号的频率和幅值进行变化,观测输出信号的变化情况。

仿真实验-频率合成仿真实验报告

频率合成实验(虚拟实验)姓名:郑仕力学号:04209722(一)锁相环频率合成器f1= fr/M = 3Mhz/3 = 1MHz; f2 = 2MHz; f4 = fo =10MHz; f5 = 1MHz; f6 = fr = 3MHz 各理论值与实验值相等(2)示波器3中的VCO的控制电压的变化曲线,其从开始阶跃到固定值间经历的时间为1.4×10﹣4 s,即为环路的锁定时间。

稳定值为1.75V。

分析:(将synSen的初始值为3e6与5e6分别与初始情况作比较)(1)改变synSen的初始值,无论是增大还是减小,除示波器3外,其余示波器波形的周期幅度均没有变化,说明改变压控振荡器的压控灵敏度不会改变输出信号的频率。

(2)synSen的初始值为3e6,即相对4e6减小,示波器3中的电压最大值增大,稳定值也增大,环路锁定时间增大。

synSen的初始值为5e6,即相对4e6增大,示波器3中的电压最大值减小,稳定值也减小,环路锁定时间1.2×10﹣4 s,减小。

(3)对于基本单环频率合成器,捕获时间tp=4/ζwn=8Nτ1/τ2K0K d,压控灵敏度K0增大,捕获时间减小。

(二)小数频率合成器分析:(1)reference信号的频率为10MHz,divided synthesized信号的频率为10MHz,但相位延迟π/2,phase difference信号频率为20MHz。

(2)因为synM=0.3,synN=10,所以一个循环周期内的分频次数为P=10,一个循环周期内删除脉冲的个数为Q=3,10次分频中,必须进行7次10分频,3次11分频,则一个循环周期内总的平均分频比为10.3。

(3)合成信号的频率大于100MHZ,因为fout=fref*10.3。

基于DDS和PLL的频率合成器的研制

(a)span=250KHz fb)span=10KHz

图4.14一波段70.955MHz频谱

Fi94.14the spectrum at70.955MHz in the fast band

(b)胛”2lO舭

(a)spa^:250KHz

图4.15一波段72.055Wlz频谱

Fi94.15the spectrum at72.055MI-tz in the first band

首先分析直接数字频率合成器(DDS)的基本结构、工作原理、杂散来源、输出频谱特性。然后介绍了锁相环(PLL)的基本结构、相位模型、频率响应、噪声及杂散性能。接着对DDS+PLL频率合成器常用组合方案进行了介绍,并对DDS+PLL系统的相位噪声、杂散、频率转换速度进行了分析。

DDS+PLL频率合成方法有很多优点。它可以将DDS的超高频率分辨率、高频率精确度、容易实现程控等优点与锁相环良好的窄带跟踪滤波特性相结合。利用这一理论并结合系统要求的技术指标,选用了性能优良的DDS和PLL芯片,最终实现方案采用了DDS+PLL+混频+倍频等综合频率合成技术,有效的减小了环路N值,实现了宽带低相位噪声高分辨率频率合成器。分析了电路的主要组成单元,对重要的技术和电路单元作了详细说明,最后对电路进行了测试。

pll频率合成技术简介

第 5 次

平均值

瞬时相位误差会产生大量的小数杂散,并出现在偏移中心频率 Nfractional x PDF 之处

Page 24

小数分频杂散抑制方法1——增加▽∑级数

• 1阶调制器 • N 计数器交替采用 900 与 901 这两个数值 • 2阶调制器 • N 计数器交替采用 898、899、900 及 901 这 4 个数值 • 3阶调制器 • N 计数器交替采用 896、895、898、899、900、901、902 及 904 这几个数值 • 理论上,3阶 delta sigma 锁相环的杂散应少于2阶 delta sigma 锁 相环

Page 23

小数分频

• 1阶delta sigma 锁相环 • • • 没有补偿的传统式小数锁相环 N 计数器交替采用 2 个数值 例如,N 计数器交替采用 900 及 901 这两个数值,最后得出 900.2 的数值

900

900 900 900

第 1 次

第 2 次 第 3 次 第 4 次

901

Page 19

系统关键性能——相位余量和环路带宽

• 环路带宽定义: 环路带宽越大→锁定时间越短→带外杂散抑制小

环路带宽一般选在:PLL噪声=VCO噪声(理想状态)

• 相位余量定义: 相位余量越大→锁定时间越长 相位余量越大→系统越稳定 平衡锁定时间和稳定性,相位余量一般选在48°

Page 20

小数分频

Page 21

小数分频

fo fr R N

fo =N f PDF

• 整数分频锁相环:

fvco = (N)PDF, (N+1)PDF, (N+2)PDF, …..

步进取决于鉴相频率

基于锁相环(PLL)L波段的频率合成技术

t

b● an.O1d - Z● n n

a a O n

d H .1 U Te

. J C

U h

a n

n

O l

Abstract:Frequency synthesizer iS the core component Oo f the electronic equipment,the performance of the

g

performance of the overall performance of the electryo nic equipment.In thiS paper,a phase locked loop

VA

frequency technique based on phase locked loop (PLL) L Z U b and is studied.Its design scheme uses MC145152 to P

中 能 够有效地 减少对 同步噪声的影 响 从 而使 电视同步 的性能 展 晨 从黑白电视水平同步电路中开始的 庙于其可以降低噪声

显著提升。锁相环路的低噪声跟踪功能 ,已经得到人们的重视 越 对同步的影响 使得电视图像的同步性能得到很大的提高。因此

来越快地发展 届 前已经广泛应用于各个领域。

频率源 通过 分频 倍 频和混频 以获 得更多的频 率。

获得 了广 泛的应 用。由于锁相 技术 广泛使 用在 电子技 术各个 领

频率合成技术与其他科学技术是一样的 砉陧 从实际需要中

20l6.01

域 这 已经成为 常用的 电子 器件的一个 基本组成部 分。锁 相环是 2.1 锁相 环在频率合成 电路 中的应用

PLL频率合成器的杂散性能分析

器,以提高其反向隔离度;③使用一个对应工作频

段的定向耦合器,但需要占用一定的PCB板空间。

112110

在离PLL芯片稍远一点的地方,这样在小电容和大

电容之间的走线将增加线上的电感,这种做法有助

于抑制高频噪声。同时在电源线上增加一个小电阻

有助于抑制低频噪声,这个电阻上的压降一般保持

器设计的首选。

PLL频率合成器的关键指标主要有

相位噪声、杂散抑制和换频时间等。由于换频时间

不具有普遍性

,仅在频率捷变系统中有严格的要求

,

另外关于相位噪声性能分析的资料较多

,因此本文

仅对频谱杂散进行详细分析。

1 杂散性能分析

111 杂散概念

杂散是指和输出信号没有谐波关系的一些无用

在载波频率的两端。工程上的解决方法主要是对参

考信号进行适当的滤波处理,以及保持一个合理的

输入电平。

11216 双PLL相互串扰引入的杂散

该类杂散通常出现在2个PLL电路靠的比较近

且同时工作的场合。某些情况下,这类杂散将会比

较大。其原因在于不合理的电源设计以及PCB布

局设计。2个PLL的充电泵同时工作时,它们将在

有

:必须保证

PLL芯片的输入信号电平在芯片标识

特性的范围以内

,同时尽可能在工作频率上实现阻

抗匹配

,并且使

VCO的谐波抑制小于

-20 dBc ,甚至

更低

,以减少前置分频器的计数错误。

11219 前置分频器输出引入的杂散

该类杂散通常离载波频率比较远

,偏移值为

:①在反馈路径上放一个有

《基于FPGA的PLL+DDS的频率合成器》范文

《基于FPGA的PLL+DDS的频率合成器》篇一一、引言随着电子技术的发展,频率合成器作为现代通信、雷达、电子对抗等系统中的核心部件,其性能和稳定性要求越来越高。

FPGA(现场可编程门阵列)技术以其灵活、高速、低功耗等优势,在频率合成器的设计中得到了广泛应用。

本文将详细介绍基于FPGA的PLL(锁相环)+DDS(直接数字频率合成器)的频率合成器设计。

二、PLL+DDS原理概述PLL是一种能够跟踪输入信号频率并产生精确输出信号的电路。

DDS则是一种基于数字算法生成任意频率、相位和幅度的信号的技术。

将PLL和DDS相结合,可以实现高精度、高稳定性的频率合成。

在基于FPGA的PLL+DDS的频率合成器中,PLL用于提供稳定的参考频率,而DDS则用于生成所需的各种频率信号。

通过FPGA对PLL和DDS的控制,可以实现频率的快速切换和调整,满足不同应用场景的需求。

三、FPGA在频率合成器中的应用FPGA在频率合成器中的应用主要体现在以下几个方面:1. 控制逻辑设计:FPGA可以实现对PLL和DDS的控制逻辑设计,包括信号的输入、输出、频率切换等操作。

2. 高速数据处理:FPGA具有高速数据处理能力,可以实现对DDS生成的高速率数字信号的处理和传输。

3. 灵活性高:FPGA的现场可编程特性使得频率合成器的设计具有很高的灵活性,可以根据不同需求进行定制化设计。

四、基于FPGA的PLL+DDS的频率合成器设计基于FPGA的PLL+DDS的频率合成器设计主要包括以下几个部分:1. 参考频率源设计:采用高稳定度的晶体振荡器作为参考频率源,为PLL提供稳定的参考信号。

2. PLL模块设计:利用FPGA实现PLL模块的设计,通过调整环路参数实现精确的频率跟踪和相位锁定。

3. DDS模块设计:采用FPGA实现DDS模块的设计,生成所需的各种频率信号。

4. 信号处理与输出:通过FPGA对DDS生成的数字信号进行高速处理和传输,并输出到相应的设备或系统。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

频率合成实验(虚拟实验)

(一)锁相环频率合成器

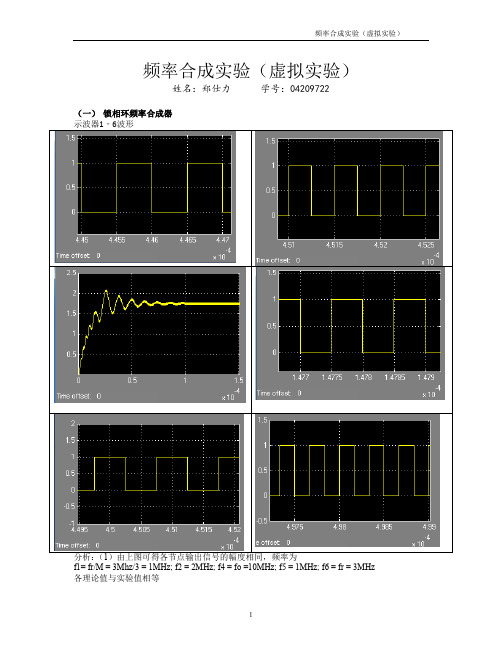

示波器1‐6波形

由示波器1的波形可以看出前置分频器输出频率为1Mhz,通过计算输出方波波形的频率,可得出fout=fr*synN/SynM的关系。

通过示波器3的波形可看出,低通滤波器滤除了鉴相器输出的无用的高频成分和其它干扰分量。

通过环路的调节,输入参考信号和下分频器的输出信号之间相位差达到最小。

当环路趋近于锁定,滤波器输出稳定的控制电压用这个电压去控制VCO,最终使其输出频率稳定不再变化,此时输入参考时钟信号和下分频模块的输出信号之间频率相等,相位差不随时间变化,达到锁定状态。

由上图可得各节点输出信号的幅度相同,频率为f1=fr/M=3Mhz/3=1MHz;f2=2MHz;f4=fo=10MHz;f5=1MHz;f6=fr=3MHz。

各理论值与实验值相等.

示波器 3中的 VCO的控制电压的变化曲线,其从开始阶跃到固定值间经历的时间为1.4×

10^(-4) s,即为环路的锁定时间。

稳定值为1.75V。

分析:(将synSen的初始值为3e6与5e6与初始情况作比较)

(1)改变synSen的初始值,无论是增大还是减小,除示波器3外,其余示波器波形的周期幅度均没有变化,说明改变压控振荡器的压控灵敏度不会改变输出信号的频率。

(2)synSen的初始值为3e6,即相对4e6减小,示波器3中的电压最大值增大,稳定值也增大,环路锁定时间增大。

synSen的初始值为5e6,即相对4e6增大,示波器3中的电压最大值减小,稳定值也减小,环路锁定时间1.2×10﹣4 s,减小。

(3)对于基本单环频率合成器,捕获时间tp=4/ζwn=8Nτ1/τ2K0K d,压控灵敏度K0增大,捕获时间减小。

(二)小数频率合成器

分析:

reference信号的频率为10MHz,divided synthesized信号的频率为10MHz,但相位延迟π/2,phase difference信号频率为20MHz。

小数分频既是双模分频,十分之七个循环周期的时间,进行3分频,其余时间进行4分频,导致3.3倍分频。

因为synM=0.3,synN=10,所以一个循环周期内的分频次数为P=10,一个循环周期内删除脉冲的个数为Q=3,10次分频中,必须进行7次10分频,3次11分频,则一个循环周期内总的平均分频比为10.3。