LATCHUP测试分析

ESD与latchup测试介绍

1、ESD模型分类 2、HBM和MM测试方法标准 3、 CDM模型和测试方法标准 4、拴锁测试 5、 I-V测试 6、标准介绍

1、ESD模型分类

因ESD产生的原因及其对集成电路放电的方式不同, 经过统计,ESD放电模型分下列四类:

(1) 人体放电模式 (Human-Body Model, HBM) (2) 机器放电模式 (Machine Model, MM) (3) 组件充电模式 (Charged-Device Model, CDM) (4) 电场感应模式 (Field-Induced Model, FIM) 另外还有两个测试模型: (5)对于系统级产品测试的IEC电子枪空气放电模式 (6)对于研究设计用的TLP模型

人体放电模式 (Human-Body Model, HBM)

人体放电模式(HBM)的ESD是指因人体在地上走动磨擦或其它因素在人体上 已累积了静电,当此人去碰触到IC时,人体上的静电便会经由IC的脚(pin)而 进入IC内,再经由IC放电到地去,如图2.1-1(a)所示。此放电的过程会在短 到几百毫微秒(ns)的时 间内产生数安培的瞬间放电电流,此电流会把IC内的 组件 给烧毁。 不同HBM静电电压相对产生的瞬间放电电流与时间的关系 显 示于图2.1-1(b)。对一般商用IC的2-KV ESD放电电压而言,其瞬间放电电流 的尖峰值大约是1.33 安培。

有关FIM的放电模式早在双载子(bipolar)晶体管时代 就已被发现,现今已有工业测试标准。

国际电子工业标准(EIA/JEDEC STANDARD) 中亦 有此电场感应模式订定测试规范 (JESD22-C101) 。

HBM, MM与CDM模型参数比较

2KV HBM, 200V MM, 与1KV CDM的放电电流比较,其中1KV CDM的放电电流 在不到1ns的时间内,便已冲到约15安培的尖峰值,但其放电的总时段约在10ns的 时间内便结束。此种放电现象更易造成集成电路的损伤。

闩锁效应latch up

闩锁效应(latch up)闩锁效应(latch up)是CMOS必须注意的现象,latch我认为解释为回路更合适,大家以后看到latch up就联想到在NMOS与PMOS里面的回路,其实你就懂了一半了.为什么它这么重要?因为它会导致整个芯片的失效,所以latch up是QUAL测试的一种,并且与ESD(静电防护)紧密相关。

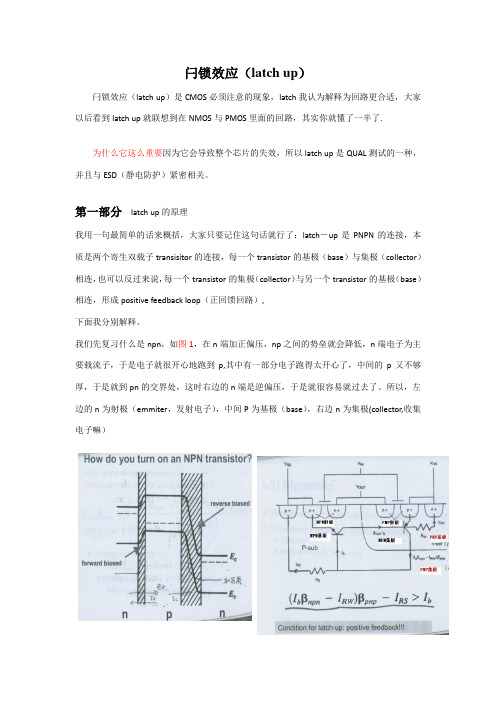

第一部分 latch up的原理我用一句最简单的话来概括,大家只要记住这句话就行了:latch-up是PNPN的连接,本质是两个寄生双载子transisitor的连接,每一个transistor的基极(base)与集极(collector)相连,也可以反过来说,每一个transistor的集极(collector)与另一个transistor的基极(base)相连,形成positive feedback loop(正回馈回路),下面我分别解释。

我们先复习什么是npn,如图1,在n端加正偏压,np之间的势垒就会降低,n端电子为主要载流子,于是电子就很开心地跑到p,其中有一部分电子跑得太开心了,中间的p又不够厚,于是就到pn的交界处,这时右边的n端是逆偏压,于是就很容易就过去了。

所以,左边的n为射极(emmiter,发射电子),中间P为基极(base),右边n为集极(collector,收集电子嘛)理解了npn,那么pnp就好办,如图2。

图2清楚的表示了latch up的回路。

左边是npn,右边是pnp,图3是电路示意图。

大家可以看出,P-sub既是npn的基极,又是pnp的集极;n-well既是既是pnp的基极,又是npn的集极,所以说,每一个transistor的集极(collector)与另一个transistor的基极(base)相连。

那么电流怎么走呢?比如在P+加5V-->电洞被从P+推到N well-->越过n well再到p sub-->这个时候,大家注意,电洞有两条路可走,一是跑到NMOS的N+,二是跑到旁边的Nwell,nwell比n+深,当然更好去,所以电洞又回去了。

ESD,Latch-up测试 介绍

ESD Design Window

Pin Combination in HBM/MM ESD Testing

10

0

0 -10

50

100

-20

-30

MM

150

•The CDM discharge is 100x faster than HBM or MM •The peak current can be 40x that of an HBM pulse

200

ns

ESD/Latch-Up

但测试过程中出现异常,虽经由操作人员做重置(Re-set)或重开机 也不能回复功能, 这种情况大概产品已损伤严重, 仅符合D级判定 结果.(这属不合格)。

依IEC 61000-4-2法规建议,产品采购验证必须符合A级或B级的 判定才能接受, C级和D级判定是不合格的.

ESD/Latch-Up

4.抗栓鎖(Latch-Up)測試主要國際規範:

*JEDEC EIA/JESD78A 電子工業協會 *AEC-Q100-004-REV-C 汽車電子協會

ESD/Latch-Up

Special

IEC 61000-4-2 放 电 示 意 图

IEC 61000-4-2 放 电 Waveform

IEC 61000-4-2 测试结果评估判定

ESD测试结果评估须按被测试产品功能受影响的程度做判定, 依法规系将受影响的程度分为四级,说明如下:

Level 1 2 3 4

latch up测试标准

latch up测试标准Latch up是指集成电路中的一种失效现象,当一个晶体管或器件被误用时,或由于外界干扰等原因导致,会出现电流过大的现象,从而导致电路失效或损坏。

Latch up测试是为了验证电路的稳定性和可靠性,以确保电路能够正常工作并长期稳定运行。

Latch up是一种瞬态故障,通常发生在集成电路中存在PNPN结构的电路,例如CMOS电路或双极性晶体管。

这种结构使得电路在特定条件下会形成一个自反馈回路,导致电流大幅度增加,进而导致电路失效。

Latch up测试通常包括以下步骤:1.设计电路:首先,在设计电路时需要充分考虑到避免触发Latch up现象的条件。

例如,采用合适的工艺参数和结构设计,选择适当的尺寸和电流容限,并避免形成PNPN结构的电路。

2.模拟仿真:使用电路仿真软件进行模拟分析,验证设计电路的稳定性和可靠性。

通过模拟仿真,可以观察电路在边界条件下是否可能出现Latch up现象。

3.制造过程控制:在芯片制造过程中,需要严格控制工艺参数和制造流程,以确保电路的稳定性。

例如,控制晶体管制造的掺杂浓度、尺寸和位置,避免PNPN结构的形成。

4.电流注入测试:进行电流注入测试是验证电路是否存在Latchup现象的重要步骤。

通常,将高电压施加到电路的输入、输出端口,然后测量电路中的电流变化。

如果电流显著增加,就说明电路存在Latch up现象。

5.温度测试:温度是影响电路稳定性的重要因素,因此进行温度测试可以验证电路在不同温度条件下的工作情况。

在温度测试中,可以观察电路在不同温度下的电流变化和稳定性。

6.电压应力测试:电压应力测试是在电路上施加不同的电压,并监测电流的变化。

通过电压应力测试,可以验证电路在不同电压条件下的稳定性和可靠性。

7.压耐测试:压耐测试是对电路进行高电压的耐受能力测试。

在压耐测试中,会施加高于设计电压的电压,并观察电路的稳定性和可靠性。

如果电路能够正常工作且没有失效,说明电路具有良好的压耐性能。

ESD与latchup测试介绍解读

HBM测试方法及标准 1.ANSI-STM5.1-2001 JESD22-A114D -2005 AEC-Q100-002D -2003 2.该标准用于明确HBM模式下的ESD电压敏感度的 测试、评价以及分级过程 3.整个测试过程繁琐,尤其对仪器及脉冲波形的校 验工作,但非常必要 4. ESD测试中,器件不在工作状态

FIM模式的静电放电发生是因电场感应而起的。当 IC因输送带或其它因素而经过一电场时,其相对 极性的电荷可能会自一些IC脚而排放掉,等IC通 过电场之后,IC本身便累积了静电荷,此静电荷 会以类似CDM的模式放电出来。

有关FIM的放电模式早在双载子(bipolar)晶体管时代 就已被发现,现今已有工业测试标准。 国际电子工业标准(EIA/JEDEC STANDARD) 中亦 有此电场感应模式订定测试规范 (JESD22-C101) 。

ESD模型及有关测试

1、ESD模型分类 2、HBM和MM测试方法标准 3、 CDM模型和测试方法标准 4、拴锁测试 5、 I-V测试 6、标准介绍

1、ESD模型分类

因ESD产生的原因及其对集成电路放电的方式不同, 经过统计,ESD放电模型分下列四类: (1) 人体放电模式 (Human-Body Model, HBM) (2) 机器放电模式 (Machine Model, MM) (3) 组件充电模式 (Charged-Device Model, CDM) (4) 电场感应模式 (Field-Induced Model, FIM) 另外还有两个测试模型: (5)对于系统级产品测试的IEC电子枪空气放电模式 (6)对于研究设计用的TLP模型

HBM/MM测量方法

如果每次调升的ESD测试电压调幅太小,则测试到IC脚损坏要 经过多次的ESD放电,增长测试时间; 若每次调升的ESD测试电 压太大,则难以较精确测出该IC脚的ESD耐压能力。 规定: 正负极性均要测试 从低压测到高压,起始电压为70%的平均ESD failure threshold (VESD) 步进当小于1000V时步进50V(100V),大于1000V时步进 100V(250V, 500V) 可以是一个管脚步进测量或者所有管脚扫描测量

latch-up版图

latch-up原理分析

I n Out N+ P+ P+ Q1 Q2 N+ N+ P+

R w ell N w ell P- e p i

R su b P+s u b

华侨大学厦门专用集成电路系统重点实验室

Copyright by Huang Weiwei

latch-up原理分析

I n Out N+ P+ P+ Q1 Q1 Q2 OUT R su b P+s u b R su b Q2 OUT N+ N+ P+ R w ell

R su b

Q2

华侨大学厦门专用集成电路系统重点实验室

Copyright by Huang Weiwei

latch-up原理分析

I n Out N+ P+ P+ Q1 Q2 N+ N+ P+ R w ell N w ell P- e p i R su b P+s u b

Latch up的具体原因5 5 产生Latch up

OUT Q1

R w ell

R su b

Q2

华侨大学厦门专用集成电路系统重点实验室

Copyright by Huang Weiwei

latch-up原理分析

I n Out N+ P+ P+ Q1 Q2 N+ N+ P+ R w ell N w ell P- e p i R su b P+ s u b

华侨大学厦门专用集成电路系统重点实验室

Copyright by Huang Weiwei

latch-up保护方法

latch up考核标准

latchup考核标准一、考核目的LATCHUP考核旨在评估员工在工作中对LatchUp知识的掌握程度和应用能力,以确保员工能够胜任相关岗位的工作,提高工作效率和质量。

二、考核范围tchUp基础知识:包括LatchUp定义、基本原理、特点等。

tchUp应用技能:包括LatchUp在电路设计、调试、测试等方面的应用技能。

3.实际案例分析:根据实际工作场景,对LatchUp应用案例进行分析和解决。

三、考核标准1.知识掌握程度:a.正确回答LatchUp基础知识试题的比例;b.能够运用LatchUp基础知识进行电路设计,说明其原理和应用;c.能够运用LatchUp基础知识解决实际工作中的问题,提供合理有效的解决方案。

2.技能应用能力:a.完成LatchUp电路调试的时间和成功率;b.能够在团队中有效协作,与其他成员共同完成LatchUp电路的设计和调试;c.能够根据实际需求,选择合适的LatchUp技术进行电路设计。

3.案例分析能力:a.对实际工作场景中的LatchUp应用案例分析的准确性和全面性;b.能够提出有效的解决方案,并得到实际验证;c.能够总结经验教训,为今后的工作提供参考。

四、考核方式1.笔试:通过试卷形式,测试员工对LatchUp基础知识和技能的掌握程度。

2.实践操作:员工在实际工作中应用LatchUp技术进行电路设计、调试和测试,展示技能应用能力。

3.案例分析:员工对实际工作场景中的LatchUp应用案例进行分析和解决,展示案例分析能力。

五、考核周期和评分标准1.考核周期:每季度进行一次LATCHUP考核,以确保员工能够及时了解自己的不足之处并加以改进。

2.评分标准:根据考核结果,员工将获得相应的分数和评级。

分数越高,评级越高,说明员工在LATCHUP方面的表现越好。

具体的评分标准如下:a.优秀(90分以上):表现出色,能够熟练运用LatchUp技术进行电路设计、调试和测试,同时具备较强的案例分析能力;b.良好(80-89分):表现良好,具备一定的LatchUp技能应用能力和案例分析能力,但仍需继续提高;c.一般(70-79分):需要加强学习,具备一定的LatchUp基础知识,能够完成基本的电路设计和调试任务;d.待提高(70分以下):需要加强学习和实践,尽快掌握LatchUp技术。

latch_up分析

闩锁效应(latch up)闩锁效应(latch up)是CMOS必须注意的现象,latch我认为解释为回路更合适,大家以后看到latch up就联想到在NMOS与PMOS里面的回路,其实你就懂了一半了.为什么它这么重要因为它会导致整个芯片的失效,所以latch up是QUAL测试的一种,并且与ESD(静电防护)紧密相关。

第一部分latch up的原理我用一句最简单的话来概括,大家只要记住这句话就行了:latch-up是PNPN的连接,本质是两个寄生双载子transisitor的连接,每一个transistor的基极(base)与集极(collector)相连,也可以反过来说,每一个transistor的集极(collector)与另一个transistor的基极(base)相连,形成positive feedback loop(正回馈回路),下面我分别解释。

我们先复习什么是npn,如图1,在n端加正偏压,np之间的势垒就会降低,n端电子为主要载流子,于是电子就很开心地跑到p,其中有一部分电子跑得太开心了,中间的p又不够厚,于是就到pn的交界处,这时右边的n端是逆偏压,于是就很容易就过去了。

所以,左边的n为射极(emmiter,发射电子),中间P为基极(base),右边n为集极(collector,收集电子嘛)理解了npn,那么pnp就好办,如图2。

图2清楚的表示了latch up的回路。

左边是npn,右边是pnp图3是电路示意图。

大家可以看出,P-sub既是npn的基极,又是pnp的集极;n-well既是既是pnp的基极,又是npn的集极,所以说,每一个transistor的集极(collector)与另一个transistor的基极(base)相连。

那么电流怎么走呢比如在P+加5V-->电洞被从P+推到N well-->越过n well再到p sub-->这个时候,大家注意,电洞有两条路可走,一是跑到NMOS的N+,二是跑到旁边的Nwell,nwell比n+深,当然更好去,所以电洞又回去了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LATCH UP 测试

LATCH UP 测试。

但是,以前我没做过类似的工作,因为以前的公司的芯片LATCH UP测试都是找宜硕这样的公司进行测试。

LATCH UP测试主要分为VSUPPLY OVER VOLTAGE TEST ,I TEST。

I test又分为PIT(POSITIVE I TEST)和NIT(NEGATIVE I TEST)。

不过我们公司还增加了PVT(positive voltage test)和NVT(negative voltage test)。

在JESD78D 规范(这个可以从JEDEC 网站上下到)上提到latch up 的测试流程。

首先待测试的IC 需要经过ATE测试,保证功能是正常的。

然后首先进行I-TEST,如果I-TEST FAIL,那这颗芯片就没PASS,如果通过了I-TEST,然后再进行OVER VOLTAGE TEST; 如果此时IC FAIL,那么这颗芯片就没有通过LATCH UP TEST, 这些通过I-TEST 和OVER VOLTAGE TEST的芯片还要再进行ATE测试来确认芯片的功能是否正常。

但是好多公司最后的ATE测试都省了。

VSUPPLY OVER VOLTAGE TEST,主要是对芯片的电源引脚进行过压测试,如果芯片有多个电源引脚,每个电源引脚都要进行测试。

测试条件:一般是对电压引脚进行一个 1.5X MAX VSUPPLY的TRIGGER 测试,1)其他引脚接LOGIC HIGH, 2)其他引脚接LOGIC LOW。

这两种情况都要进行测试。

PIT 测试是对除电源和地外的其他I/O引脚进行测试。

电源接VCC,1)所有引脚接LOGIC HIGH, 然后给待测试引脚来一个POSITIVE TRIGGER CURRENT PULSE。

2)所有引脚接LOGIC LOW,然后给待测试引脚来一个POSITIVE TRIGGER CURRENT PULSE。

NIT 测试是对除电源和地外的其他I/O引脚进行测试。

电源接VCC,1)所有引脚接LOGIC HIGH, 然后给待测试引脚来一个Negative TRIGGER CURRENT PULSE。

2)所有引脚接LOGIC LOW,然后给待测试引脚来一个Negative TRIGGER CURRENT PULSE。

LATCH UP 失效判定标准:

如果INOM<=25mA, 经过LATCH UP 测试之后,发现电流>INOM+10,则该芯片没有PASS LATCH

UP 测试。

如果INOM>25mA, 经过LATCH UP 测试之后,发现电流>1.4X INOM,则该芯片没有PASS LATCH UP 测试。

LATCH UP 测试前后的电流对比差异,看有没有发生拴锁?

通常芯片经过LATCH UP 测试前后的电流变化很小。