基于FPGA视频图像采集及显示系统的设计与实现

基于FPGA的MIPI CSI-2图像采集系统设计

基于FPGA的MIPI CSI-2图像采集系统设计赵清壮【摘要】This paper elaborates a design of MIPI CSI-2 high-definition camera interface image acquisition system based on FPGA. Now, MIPI high-definition CCD is used widely, this design uses FPGA to achieve MIPI high-definition CCD collect and provides two outputs of LCD screen and USB, the data transmission is stable and reliable, it make MIPI interface camera applied widely by the other circuit systems, accelerates system development and saves cost.%阐述一种基于FPGA的MIPI CSI-2接口高清摄像头图像采集系统设计,该设计用FPGA实现当前应用广泛的MIPI高清CCD采集,并提供LCD屏、USB两路输出,数据传输稳定可靠,把MIPI接口摄像头应用到更广泛的其他电路系统中,加快系统开发,节省成本。

【期刊名称】《价值工程》【年(卷),期】2015(000)029【总页数】2页(P84-85)【关键词】MIPI;CSI-2;图像采集;FPGA【作者】赵清壮【作者单位】广州飒特红外特股份有限公司,广州510000【正文语种】中文【中图分类】TP302.10 引言CSI(Camera Serial Interface)是由MIPI(Mobile Industry Processor Interface)联盟下Camera工作组制定的接口标准,是MIPI联盟发起的为移动应用处理器制定的开放标准,MIPI联盟由ARM、诺基亚、意法半导体和德州仪器发起成立,作为移动行业领导者的合作组织,MIPI联盟旨在确定并推动移动应用处理器接口的开放性标准。

基于FPGA的多路图像采集系统的软件设计

ue o r AA7 1 H vd od c d r n woF GA oahe e tea q iio ssfu S 1 3 ie e o esa d t P t c iv h c ust n,soa e n ipa ft h n e ma e i trg ,a d dsly o woc a n li g ,

fl sre .I fr e e l e h ac d o f u ain o wo F GA,a d te F mnb s c n g rt n, te I U6 6 ul cen t ut rrai s te c sa e c n g rt ft P — h z i o n h C o iu o f u ai i o h T 5

( 安 工 业 大 学 计 算机 科 学 与 工程 学 院 , 西 西 安 7 0 3 ) 西 陕 10 2

摘 要 :分 析 了 现 有 的 视 频 采 集 方 案 的 研 究现 状 。 对如 何 采 用 C D 摄 像 头采 集 多通 道 、 C 高分 辨 率 、 高质 量 的 图像 以及

基 于 F G 的 嵌 入 式 图 像 采 集 系统 的 实 现 方 法做 了研 究 。 与传 统 图像 采 集 系统 相 比 . 系统 主要 利 用 四 片视 频 解码 PA 该

关键 词 : A 7 l H;F G I U 6 ;图像 采 集 S A l3 P A; T 5 5

,

文 章 编 号 :17 — 2 6 2 1 )3 14 0 6 4 6 3 (0 号 :I 99 , 1 ’ P

文献标识码 : A

The s fwa e de i n o u t- ha ne m a e a q sto s s e b s d o FPGA o t r sg fm lic n li g c uiii n y t m a e n

基于ZYNQ FPGA实现图像采集存储显示

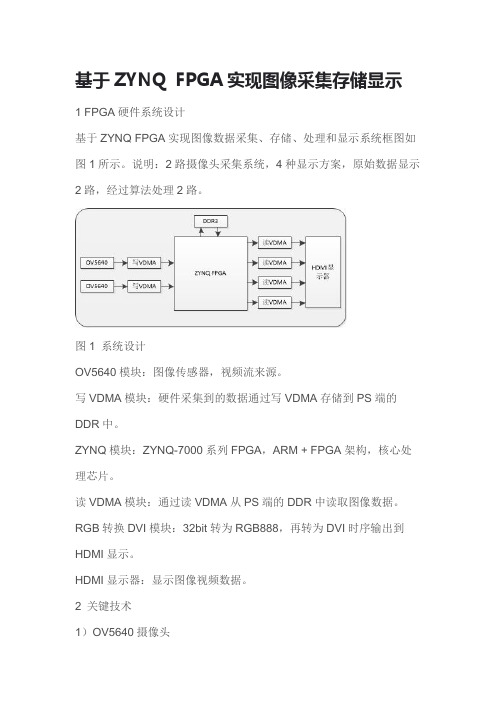

基于ZYNQ FPGA实现图像采集存储显示1 FPGA硬件系统设计基于ZYNQ FPGA实现图像数据采集、存储、处理和显示系统框图如图1所示。

说明:2路摄像头采集系统,4种显示方案,原始数据显示2路,经过算法处理2路。

图1 系统设计OV5640模块:图像传感器,视频流来源。

写VDMA模块:硬件采集到的数据通过写VDMA存储到PS端的DDR中。

ZYNQ模块:ZYNQ-7000系列FPGA,ARM + FPGA架构,核心处理芯片。

读VDMA模块:通过读VDMA从PS端的DDR中读取图像数据。

RGB转换DVI模块:32bit转为RGB888,再转为DVI时序输出到HDMI显示。

HDMI显示器:显示图像视频数据。

2 关键技术1)OV5640摄像头设计中采用两片美国OmniVision公司的CMOS图像传感器OV5640,OV5640芯片支持DVP和MIPI接口。

为保证OV5640正常工作,需要依次实现以下时序要求。

a、ResetB拉低、PWND拉高;b、DOVDD和AVDD同时上电;c、电源稳定5ms后,拉低PWND,再过1ms,拉高ResetB;d、20ms后初始化OV5640DESCCB寄存器。

e、通过IIC接口配置,配置目标为RGB565、30FPS、720输出格式;f、FPGA接收来自OV5640的视频流数据输入,需要对摄像头完成相应的时序操作。

每次传输8bit,16bit为一个像素点,所以要进行数据转换8bit-16bit-32bit;2)图像处理算法边缘检测算法要求首先找到图片中物体的边缘,由于边缘处颜色变化一般比较明显,在工程上一般借助卷积滤波器实现,卷积滤波器相当于求导的离散版本。

针对图像进行边缘检测,有多种不同的滤波器算子,我们采用的Sobel滤波器算子图1,分别针对图像水平方向的边缘以及竖直方向的边缘,求和得出图像的边缘。

图1 滤波器算子3)ZYNQ FPGAZYNQ 7000系列基于Xilinx 全可编程的扩展处理平台结构,芯片内部集成ARM 公司双核Cortex-A9处理器的处理系统(PS端)和基于Xilinx逻辑资源的可编程逻辑系统(PL端)。

一种基于FPGA的高速图像采集及显示电路设计

1 9

一

种基于 F G P A的高速图像采集及显示电路设计

De i f Hi —s e d Vi o Ac ust n An Dip a r utBa e o P sgn o gh— p e de q iio d i s ly Ci i c s d n F GA

选 用 的 接 收 芯 片是 DS 0 R 8 , 最 高 数 据 传输 速 率 可 以达 到 9 C 2 6其

该 F G 进 行 配 置和 验 证 , 试 表 明该 设 计 不仅 实现 了 图像 高 速 采 集和 显 示 , 使 图像 清 晰 、 PA 测 且 系统 稳 定 可 靠 。

关 键 词 :P F GA, Cl CP 总线 , 图像 采 集

Ab ta t s rc

Th si u e Ca Ln nera e nd e de gn s d m ik it f c a DVI o r al e i -s ed i a qust d t e i hgh pe vdeo c iion an diply.hi z i s a T s pap itodu es er nr c t e y tm of i a quiion nd h s se vdeo c st a diply a d i s a b se on PGA,h ws o F s o h w t s m pl m o e he a e dul ba ed s on Cam Lnk n e ce i it da an DVI s a o e d diply m dul wor d. d de An ba ed n s o CP bu ,i Cl shgh- ee i a da a ex h ge et e c sp d m ge t c an b we n ompu e an i tr d mag e ci ui wa r aied. EP 30 7 4 FP r t c s el z 2S F6 21 GA o t m p y i u e t n i d ery h de i . e es manfses h fAl Co an s s d o co fg an v i te er f sgnTh t t i t te e de i n tonl eaied i sgn o y r l z hgh—s ee vdeo a p d i cqust a d iion n diply, talo m a de ea ,y tm r i l i s a bu s de vi o cl rs se el e ab Ke wo d : P y r s F GA. Cl s, de a quiion CP bu vi o c st i

基于FPGA的视频采集显示系统

随着 高 品质 实 时 视 频 显示 技 术 低 , 民用 领域 如 天 气预报 、 资源探测 、 机器 人 视觉 以及 各 种医学 图像 的实 时分 析 ; 军 用 领域 如 导 弹精 确 制 导 、 战场 动 态分 析 等 , 均需要 高 质量实 时视 频显 示 系统 的支 持 。近年 来低 成 本的 F P G A( F i l e d P r o g r a m ma b l e G a t e A r r a y ) 不 断 推 陈 出新 , 利用 E D A工具对 F P G A芯 片 进 行 多 样 性 设 计 , 已经 成为 电子设 计 的通 用 平 台 , 并逐 步 向支 持 系统 级 设计 的方 向发 展 。 与专 用 集 成 电 路 相 比 , F P G A芯 片 具有 快速 的定 制 性 和 高灵 活 性 , 扩 展 性 强 的特 点 。作

3 叶技 2 0 1 3 年 第 2 6 卷 第2 期

E l e c t r o n i c S c i . &T e c h . / F e b . 1 5. 2 0 1 3

基于 F P G A 的视 频 采 集 显 示 系统

李 国兴 ,杨

摘 要

芳

7 2 3 0 0 0 )

( 陕西理工学院 物理 与电信工程学 院 ,陕西 汉 中

显 示 。 整 个 系统 获得 了较 好 图像 采 集 、 显 示 效果 。 关键词 F P G A;视 频 处理 ;T F T L C D;N i o s I I

中图分类号

T N 7 9 ;T P 2 7 4 . 2

文献标识码

A

文章编号

1 0 0 7— 7 8 2 0 ( 2 0 1 3 ) 0 2— 0 2 2— 0 4

基于FPGA的图像采集模块设计

口可兼 容 +5V, 常 工 作 时 功 耗 为 0 4 W , 闲 时 功 耗 为 正 . 空 o 0 。 钟 丢失 、 源 电 压 降 低 都 会 引起 芯 片 的 自动 复 . 7W 时 电 位, 因此 要 保 证 供 电系 统 的 稳 定 可靠 性 。

足 够 的 IE以及 RAM 单 元 , 在 其 内 部 实 现 像 预 处 理 为

行 同步信号 , 只有 在行 场 同步 信号 同时有效 时 , 且 才是 有

且 用 DS P的 IC总 线 来 配 置 其 内部 的 各 个 寄存 器 。这 里 把 S AA7 1 H 相 应 的 信 号 R 1 RTS 13 TS 、 0分 别 配 置 成 场 、

* 基 金 项 目: 东省 自然 科 学 基 金 ( o 62 69 。 广 N . 0 9 6 )

提 供 了保 障 , 且 具 有 足 够 的 I( 引 脚 使 其 方 便 与 其 他 设 并 /)

备 相 接 。本 文 将 详 细 描 述 F GA如 何 对 S P AA7 1 H 解 码 13 后 的 图 像 数 据 信 号 及 一 些 控 制 信 号 进 行 采 集 , 得 到 一 幅 并 完 整 的 图像 供后 续 系 统 进 行 处 理 。也 就 是 说 , 何 编 写 出 如 F GA程 序 来 控 制 各 个 信 号 , 而 采 集 图 像 。 最 后 , P 从 在 Qu ru IMo eSm 等 软 件 上 验 证 了 系 统 中一 些 重 要 的 at sI、 d l i 信 号 , 到 了较 为满 意 的效 果 。 达

出 8位 “ ’ VP 总线 , 标 准 的 I 为 TU6 6 YUV 5、 4:2: 2格 式 。 S AA7 1 H 的模 拟 与 数 字 部 分 均采 用 +3 3V, 字 Io接 13 . 数 /

基于FPGA的LVDS视频图像采集与预处理系统的设计实现

基于FPGA的LVDS视频图像采集与预处理系统的设计实现作者:黄国鹏刘卫东乔明胜陈兴锋来源:《现代显示》2009年第02期文章编号:1006-6268(2009)02-0032-04摘要:以LED背光源液晶电视为应用背景,在FPGA硬件平台上实现了LVDS视频图像采集和直方图预处理系统的设计。

关键词:现可编程门阵列;低压差分信号;直方图;约束中图分类号:TN911.73文献标识码:ADesign and Implement of FPGA-based LVDS Video Acquisition and Preprocessing SystemHUANG Guo-peng1,LIU Wei-dong1,2,QIAO Ming-sheng2,CHEN Xing-feng1(1.Dept. of Electrical Engineering ,Ocean University of China,Qingdao 266100;2. Hisense Electric Co.,Ltd, Qingdao 266071)Abstract:This paper ,taking LED backlight for LCD TV as application background, has researched to achieve LVDS video acquisition and preprocessing system based on FPGA .Keywords: FPGA;LVDS;histogram;constraints引言FPGA在信号实时处理领域得到越来越广泛的应用。

相比ASIC和DSP,FPGA有更高的吞吐量、位级的可编程能力、开发周期短和风险大大降低等优点。

随着65nm甚至45nm工艺技术的面世,FPGA在逻辑门集成数量和工作的频率上取得了很大的提高。

在大数量数据处理领域,其并行处理数据的优势可以得到充分体现,特别是在在图像帧速率和分辨率要求比较高的场合使用高速大容量FPGA可以得到令人满意的结果。

基于FPGA的实时视频图像采集与显示系统的设计与实现

基于FPGA的实时视频图像采集与显示系统的设计与实现作者:贡镇来源:《现代电子技术》2013年第13期摘要:主要针对目前视频图像处理发展的现状,结合FPGA技术,设计了一个基于FPGA的实时视频图像采集与显示系统。

系统采用FPGA作为主控芯片,搭载专用的编码解码芯片进行图像的采集与显示,主要包括解码芯片的初始化、编码芯片的初始化、FPGA图像采集、PLL设置等几个功能模块。

采用FPGA的标准设计流程及一些常用技巧来对整个系统进行编程。

重点在于利用FPFA开发平台对普通相机输出的图像进行采集与显示,最终能在连接的RCA端口显示屏显示。

关键词: FPGA;视频图像采集;编码芯片;解码芯片中图分类号: TN911⁃34 文献标识码: A 文章编号: 1004⁃373X(2013)13⁃0046⁃03Design and Implementation of real⁃time video image captureand display system based on FPGAGONG Zhen(Anhui University of Science and Technology, Huainan 232000, China)Abstract: Based on the current development status of the video image processing and FPGA technology, a FPGA⁃based real⁃time video image capture and display system is designed in this paper. Equipped with dedicated coding and decoding ship for image capture and display, the system adopts FPGA as the main control chip, which are composed of decoding chip initialization module, the encoding chip initialization module, FPGA image acquisition module and PLL setting module. FPGA⁃standard design flow and some commonly used techniques are taken to program the entire system. The focus is to realize the ordinary camera output image acquisition and display via the FPFA development platform, and ultimately connect the RCA port display screen.Keywords: FPGA; video image capture; coding chip; decoding chip0 引言随着时代的发展,人们在图像处理领域取得了相当多的成果,研究出了很多算法,例如中值滤波、高通滤波等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

OPEN ACCESS

19

SDRAM 2x64MB FLASH 1x8MB

CMOS图像 传感器

RS232 串口

基于 FPGA 视频图像采集及显示系统的设计与实现

E2PROM FPGA配置器件

SDRAM 控制器 FLASH 控制器

图像采 集及数 据压缩

模块

RS485 控制器 UART 控制器

Avalon交 换总线

摘 要:针对图像处理实时性要求高的领域,利用最新的可编程片上系统技术,设计并实现了基于可编程逻辑 器件 FPGA 的视频图像采集及显示系统。系统以 NIOS II 软核为主控制器,将图像采集、图像处理及存储、图像显 示等功能集成在单片可编程逻辑器件 FPGA 上,实现了实时视频图像的采集、处理及显示。实验结果表明,系统 有着易于移植、便于针对特定应用定制、成本大幅降低等优势,具有较高的工程应用与参考价值。

根据图 4 所示时序编写 VGA 显示控制程序,产 生 VGA 相关同步信号,同时送出 25 MHz 给 AD7123, 将 RGB 视频数据输出到 VGA 设备上。

本系统中的显示模块可以根据前端图像采集模 块的输出自动通过 NIOS II 配置输出其他常用格式的

视频,比如 SVGA(60 Hz)、XGA(60 Hz)等。

[3] 刘松, 付扬, 郭培源 (2010) 基于 FPGA 的数字视频监控系统 设计. 电视技术, 3, 92.

[4] 徐遵磊, 贾建援, 张大兴 (2008) 基于 FPGA 的视频信息采集 系统设计. 微计算机信息, 14, 76.

Figure 5. Video capture and display result 图 5. 采集及显示效果图

Design and Implementation of a Video Image Capture and Display System Based on FPGA

Hui Peng

Department of Information Technology and Management, Zhejiang Police Academy, Hangzhou Email: penghui@, 47437998@

CMOS 数字图像传感器,CMOS 图像传感器输出的数 字图像信号,由 FPGA 采集及数据转换模块将其转化 为 30 位的 RGB 信号,并存储到外部 SDRAM 图像缓 存器,经过图像处理模块的预处理后再通过 VGA 显 示模块直接输出到显示终端上,另外也可以通过千兆 以太网通信通道将图像信息传输到后台计算机后处 理。

3. 视频数据采集及存储

本系统采用 CMOS 数字图像传感器 D5M,最大 输出图像像素为 2592 × 1944,图像颜色格式为 Bayer 格式,图像输出格式可以通过 I2C 总线进行配置,支 持多种常用的格式比如 VGA、SVGA、XGA 等,另外 增益、暴光时间等参数也可以动态调整。CMOS 图像 传感器将接收的光信号转换成电信号,并通过片内 12

本系统的总体框架如图 1 所示,采用 Altera 的 Cyclone IV EP4CE115F29 器件作为核心控制器,基于 SOPC 技术将主要功能模块集成在同一个可编程逻辑 器件上,同时将一个 NIOS II 软核处理器嵌入到里面, 负责对整个系统的管理和配置,另外内部各模块通过 Avalon 总线互连和通讯[3]。系统前端图像采集器采用

像素时钟

帧有效 行有效

图像数据

P0

P1

P2

P3

P4

P5

Pn

垂直消隐

水平消隐

有效图像数据

Figure 2. CMOS image sensor data output timing 图 2. CMOS 图像传感器数据输出时序

水平消隐

垂直消隐

Figure 3. Functional parts connection relationship diagram in display module 图 3. 显示模块各功能部件连接关系图

OPEN ACCESS

21

视频数据 水平同步

基于 FPGA 视频图像采集及显示系统的设计与实现

1.9us

行消隐后肩

25.4us

有效视频数据

0.6us

行消隐前肩

RGB

3.8us

同步脉冲宽度

视频数据 场同步

33行

场消隐后肩

480行

有效视频数据

10行

场消隐前肩

RGB

2行

同步脉冲宽度

Figure 4. VGA standard timing 图 4. VGA 标准时序图

22

OPEN ACCESS

关键词:可编程片上系统;图像采集;VGA;FPGA;实时

1. 引言

2. 视频图像采集及显示系统总体框架

随着可编程逻辑器件的发展,使得它在图像尤其 是视频图像领域的应用趋于广泛,并已经成为对图像 处理实时性要求高的领域如动态目标跟踪、生物特征 识别、车辆车牌识别等中重要的研究对象[1,2]。因此,本 文将深入研究基于 FPGA 视频图像采集及显示系统, 对于开发实时高速图像处理系统有着重要的参考意义。

位 A/D 转换器将模拟信号转换成 12 位的数字信号, 图像数据输出时序如图 2 所示 。

由于视频数据量较大,实时性要求较高,所以本 系 统 的图 像存 储 部分 由两 片 数据 位宽 为 16 位的 SDRAM 芯片构成,通过 ALTERA 专用 AVALON 总 线连接到 NIOS II 软核。本系统中 CMOS 图像传感器 输出的 Bayer 图像数据转换成 30 位 RGB 数据后,为 了提高存储器带宽利用率,将 R[9:0]和 G[9:5]存入到 第一片 SDRAM 中,将 G[4:0]和 B[9:0]存入到第二片 SDRAM 中,并且采用乒乓缓存思想,将 SDRAM 划 分成两块独立存储块,当其中一片存储块用于采集后 图像数据写入时,另一片存储块用于显示图像数据的 读出,具体实现过程为系统初始化后,将两帧图像数 据分别存入两块存储块,后续当偶数帧的帧同步信号 下降沿时触发控制器去读前一个奇数帧所在存储块,

Keywords: System-On-Programmable-Chip; Image Acquisition; VGA; FPGA; Real Time

基于 FPGA 视频图像采集及显示系统的设计与实现

彭辉

浙江警官职业学院信息技术与管理系,杭州 Email: penghui@, 47437998@ 收稿日期:2013 年 11 月 29 日;修回日期:2013 年 12 月 22 日;录用日期:2014 年 1 月 5 日

NIOS II CPU

FPGA 图像处理

模块

MAC控 制器 MDIO

控制器

VGA控 制器

IIC控制 器

千兆以太网收 发器

1000BASET/TX

1000BASE-X

VGA解码器

VGA显示终 端

Figure 1. Video capture and display system block diagram 图 1. 视频图像采集及显示系统总体框架图

参考文献 (References)

[1] 雷元武, 窦勇, 郭松 (2012) 基于 FPGA 的高精度科学计算加 速器研究. 计算机学报, 1, 112-122.

[2] 石美红, 房超, 张卫军, 仇涵 (2009) 基于 FPGA 的线阵 CCD 图像采集控制的实现微计算机信息. 微计算机信息, 5-2, 177-178.

Computer Science and Application 计算机科学与应用, 2014, 4, 19-22 /10.12677/csa.2014.41004 Published Online January 2014 (/journal/csa.html)

Received: Nov. 29th, 2013; revised: Dec. 22nd, 2013; accepted: Jan. 5th, 2014 Copyright © 2014 Hui Peng. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited. In accordance of the Creative Commons Attribution License all Copyrights © 2014 are reserved for Hans and the owner of the intellectual property Hui Peng. All Copyright © 2014 are guarded by law and by Hans as a guardian.