基于fpga的图像采集系统

基于FPGA的MIPI CSI-2图像采集系统设计

基于FPGA的MIPI CSI-2图像采集系统设计赵清壮【摘要】This paper elaborates a design of MIPI CSI-2 high-definition camera interface image acquisition system based on FPGA. Now, MIPI high-definition CCD is used widely, this design uses FPGA to achieve MIPI high-definition CCD collect and provides two outputs of LCD screen and USB, the data transmission is stable and reliable, it make MIPI interface camera applied widely by the other circuit systems, accelerates system development and saves cost.%阐述一种基于FPGA的MIPI CSI-2接口高清摄像头图像采集系统设计,该设计用FPGA实现当前应用广泛的MIPI高清CCD采集,并提供LCD屏、USB两路输出,数据传输稳定可靠,把MIPI接口摄像头应用到更广泛的其他电路系统中,加快系统开发,节省成本。

【期刊名称】《价值工程》【年(卷),期】2015(000)029【总页数】2页(P84-85)【关键词】MIPI;CSI-2;图像采集;FPGA【作者】赵清壮【作者单位】广州飒特红外特股份有限公司,广州510000【正文语种】中文【中图分类】TP302.10 引言CSI(Camera Serial Interface)是由MIPI(Mobile Industry Processor Interface)联盟下Camera工作组制定的接口标准,是MIPI联盟发起的为移动应用处理器制定的开放标准,MIPI联盟由ARM、诺基亚、意法半导体和德州仪器发起成立,作为移动行业领导者的合作组织,MIPI联盟旨在确定并推动移动应用处理器接口的开放性标准。

基于FPGA和USB3.0的高速视频图像采集处理系统设计

摘要随着机器视觉的广泛应用,以及工业4.0和“中国制造2025”的提出,在数字图像的采集、传输、处理等领域也提出了越来越高的要求。

传统的基于ISA接口、PCI接口、串行和并行等接口的图像采集卡已经不能满足人们对于高分辨率、实时性的图像采集的需求了。

一种基于FPGA和USB3.0高速接口,进行实时高速图像采集传输的研究越来越成为国内外在高速图像采集研究领域的一个新的热点。

针对高速传输和实时传输这两点要求,通过采用FPGA作为核心控制芯片与USB3.0高速接口协调工作的架构,实现高帧率、高分辨率、实时性的高速图像的采集和传输,并由上位机进行可视化操作和数据的保存。

整体系统采用先硬件后软件的设计方式进行设计,并对系统各模块进行了测试和仿真验证。

通过在FPGA 内部实现滤波和边缘检测等图像预处理操作,验证了FPGA独特的并行数据处理方式在信号及图像处理方面的巨大优势。

在系统硬件设计部分,采用OV5640传感器作为采集前端,选用Altera的Cyclone IV E系列FPGA作为系统控制芯片,由DDR2存储芯片进行数据缓存,采用Cypress公司的USB3.0集成型USB3.0芯片作为数据高速接口,完成了各模块的电路设计和采集卡PCB实物制作。

系统软件设计,主要分为FPGA逻辑程序部分、USB3.0固件程序部分和上位机应用软件部分。

通过在FPGA上搭建“软核”的方式,由Qsys系统完成OV5640的配置和初始化工作。

由GPIF II接口完成FPGA和FX3之间的数据通路。

通过编写状态机完成Slave FIFO的时序控制,在Eclipse中完成USB3.0固件程序的设计和开发。

上位机采用VS2013软件通过MFC方式设计,从而完成整体图像采集数据通路,并在上位机中显示和保存。

整体设计实现预期要求,各模块功能正常,USB3.0传输速度稳定在320MB/s,通过上位机保存至PC机硬盘的图像分辨率大小为1920*1080,与传感器寄存器设置一致,采集卡图像采集帧率为30fps,滤波及边缘检测预处理符合要求,采集系统具有实际应用价值和研究意义。

基于FPGA的图像处理算法实现及其优化

基于FPGA的图像处理算法实现及其优化随着科技的不断发展,计算机图像处理技术在各个领域中的应用越来越广泛,而基于FPGA的图像处理算法实现及其优化成为了最受关注的热点问题之一。

FPGA是现代数字电路设计中使用最广泛的可编程逻辑器件之一,可以用于快速实现各种数字信号处理算法。

基于FPGA的图像处理算法实现具有硬件加速的优势,能够实现高效的并行计算以及低延迟的图像处理效果。

基于FPGA的图像处理算法实现的流程一般包括:图像采集、处理算法设计、硬件系统实现以及性能分析等步骤。

图像采集是基于FPGA图像处理的第一步,它的主要目的是将需要进行处理的图像数据读入FPGA中。

在图像采集的过程中,需要设计合适的硬件电路和软件程序对图像进行处理,以满足不同应用场景的需求。

常见的图像采集设备包括CCD/CMOS等数字相机、遥感卫星传感器、X光/磁共振成像等医学成像设备等。

处理算法设计是基于FPGA图像处理的核心步骤,它的主要目的是设计有效的图像处理算法以满足不同应用场景的需求。

基于FPGA的图像处理算法主要包括:滤波、分割、去噪、增强、特征提取等内容。

其中,滤波算法可以用于去除图像中的噪声与杂质;分割算法可以将图像中不同区域进行分离;去噪算法可以用于降低图像采集过程中的噪声;增强算法可以增强图像中的亮度、对比度等特征;特征提取算法可以用于从图像中提取出特定的目标区域。

硬件系统实现是基于FPGA图像处理的第三步,它的主要目的是将处理算法转换为硬件电路并在FPGA上实现。

硬件系统实现需要考虑硬件资源占用、时钟频率、功耗等多重因素,以实现高效的图像处理性能和优化的花费效益比。

性能分析是基于FPGA图像处理的最后一步,它的主要目的是评估算法的执行效率和处理质量。

常用的性能分析指标包括:处理时间、处理吞吐率、图像质量等。

在实现基于FPGA的图像处理算法时,需要从多个方面进行优化,以提高算法的处理效率和性能。

具体的优化方法包括:优化算法设计、优化硬件电路、改善时钟频率、减少功耗、优化存储器结构等。

基于FPGA的新型高速CCD图像数据采集系统

作 为 图 像 数 据 的 控 制 和 处 理 核 心 , 过 采 用 高速 A/ 异 步 FF U R 以 及 电 平 转 换 、 大 滤 波 、 通 D、 IO、 A T 放 二 值 化 电 路 和 光 学 系 统 实 现 对 图 像 数 据 的 信 号 处 理 , 运 用 V s a Su i + 和 Mirsf 公 司 的 基 本 类 并 i l tdo C + u coot 库 MF 实现 对 采 集 数 据 的 显 示 、 图 、 输 控 制 等 。 利 用 搭 建 的 系统 平 台 实 现 对 物 体 尺 寸 的 测 量 , C 绘 传 通

Ue s Vi a t d o s l ui u S C + + a d n Mir s f Co a y F u d t n l s MF t a he e h d s ly coot mp n o n a i C a s o C o c i v t e ip a .ma p n a d r n miso o t l p ig n t s s in c n r a o

W EI Ch n W e ,YUAN Zo g ag i n He g,ZHANG W e Ta n n o,W ANG i e ,XI Pe P i NG Da Ya n

( e a m n o lc o i E gneig u i U i r t o Eet ncT c nlg,G in 5 10 ,C ia D p r e t fEet nc nier ,G in nv sy f lc o i eh o y ul 4 0 4 hn ) t r n l e i r o i

基于FPGA的网络图像采集处理系统设计

基于FPGA的网络图像采集处理系统设计作者:王永欣, 佟立飞,唐艺灵来源:《现代电子技术》2011年第20期摘要:介绍一种基于FPGA的网络图像采集处理系统设计,该系统采用单片FPGA,实现了图像的采集、压缩和网络传输功能,具有体积小,集成度高,算法升级灵活方便的特点。

详述了模块的图像采集逻辑、RAM控制逻辑、压缩算法逻辑和网络传输功能的实现方法。

测试结果表明,系统运行稳定,性能满足要求。

关键词:FPGA;图像压缩;网络传输; JPEG中图分类号:TN919-34 文献标识码:A文章编号:1004-373X(2011)20-0029-04Design of Network Image Acquisition and Processing System Based on FPGAWANG Yong---(1.Department of Automatic Test and Control, Harbin Institute of Technology, Harbin 150001, China; 2. Unit 92941 of PLA, Huludao 458000, China)Abstract: A design of network image acquisition and processing system based on FPGA is introduced. The system uses a single FPGA to complete the functions of image acquisition,even has a small size. The details the logics of image acquisition module, RAM control module and compression algorithm, furthermore the implementation method of network transmission. The results show that the system is stable and meets the requirements.Keywords: FPGA; image compression; transmission by network; JPEG0 引言随着网络技术的发展,网络化仪器以结构简单,机动灵活,吞吐率高和成本低等优点而越来越受到重视[1],并在军用自动测试装备中得到广泛的应用。

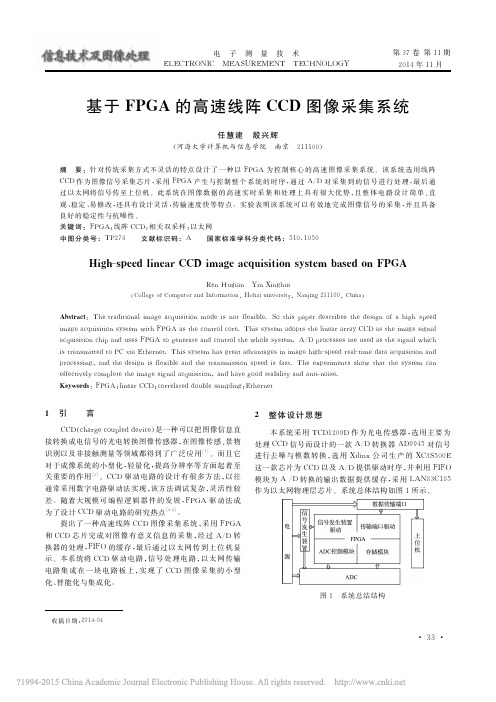

基于FPGA的高速线阵CCD图像采集系统_任慧建

3.1 TCD1209D 采样模块设计 TCD1209D 的驱动时序如图2所示,由图 知,完成芯片

的驱动需要5路驱动脉冲,分别为:移位脉冲 φ1 和 φ2,转移 脉冲 SH,复位脉冲 RS,钳位脉冲 CP[5],各路脉冲必须严格 满 足 时 序 要 求 。 每 帧 输 出 信 号 首 先 是 32 个 哑 元 像 素 信 号 ,

1 引 言

CCD(charge coupled device)是 一 种 可 以 把 图 像 信 息 直 接 转 换 成 电 信 号 的 光 电 转 换 图 像 传 感 器 ,在 图 像 传 感 、景 物 识别以及非接触测量等领域都得到了 广 泛 应 用 。 [1] 而 且 它 对 于 成 像 系 统 的 小 型 化 ,轻 量 化 ,提 高 分 辨 率 等 方 面 起 着 至 关重要的作用[2]。CCD 驱 动 电 路 的 设 计 有 很 多 方 法,以 往 通 常 采 用 数 字 电 路 驱 动 法 实 现 ,该 方 法 调 试 复 杂 ,灵 活 性 较 差。随着大规模可 编 程 逻 辑 器 件 的 发 展,FPGA 驱 动 法 成 为了设计 CCD 驱动电路的研究热点 。 [3-4]

图 1 系 统 总 结 结 构

收 稿 日 期 :2014-04

· 33 ·

第 37 卷

电 子 测 量 技 术

首先通过 代 码控 制 FPGA 输出 与 CCD 芯片 时序要 求 相对应 的 驱 动 信 号 对 CCD 进 行 驱 动,CCD 输 出 信 号 经 过 电容滤波后送入 AD9945进行相关 双 采样 与 A/D 转换,之 后将获得的数字信 号 放 入 FPGA 的 FIFO 数 据 缓 存 器,再 经过以太网传至上位机。

基于FPGA和USB2.0的线阵X射线图像采集系统设计

廖朝 阳 武 和 雷 项 安

( 1南 昌 大 学 电 气 与 自动 化 系 ,南 昌 3 3 0 0 3 1 ; 2 同济 大 学 电气 工 程 系 ,上 海 2 0 1 8 0 4 )

摘 要 :基于 F P G A和 U S B 2 . 0传 输技术 构 建 了一 套 线阵 x 射线 图像 采集 系 统 。系统 以 F P G A芯 片 为控 制核 心 , 在F P G A芯 片上 实现 了对探 测 器 的控 制 、 A / D采样 时 序 控 制 、 图 像数 据 预 处理 、 U S B数 据 传 输控 制等 功能 。U S B 2 . 0微控 芯片 作 为传输 接 口 , 充分 发 挥 了 U S B 2 . 0支持 热拔 插 、 高速 可靠 、 扩 展性 强的特 点 。该 图像

0 引 言

阵列 ( f i e l d p r o g r a m ma b l e g a t a a r r a y ,F P G A) 为核 心 控

随着人 们对 公共 安 全的 重 视 , X射线 安 全 检 查 系 制 器 , C y p r e s s 公 司的 E Z - U S B F X 2系 列 C Y 7 C 6 8 0 1 3 A 统 已经成 为机 场 、 海关 、 铁 路 以 及 公路 等 交 通 出入 口 芯 片 构建 U S B 2 . 0协 议传 输接 口集 成 了高速 图 像数据 的安检 必 备设 备 。完 整 的 x射 线 安 检 系 统包 含 x射 采 集 、 图像 预 处 理 、 高 速 图 像 传 输 等 多 种 功 能 。 系 统 可满 足工 业 级 高速 图像 采 集 任 务 线源 、 探测器 、 图像 采 集 、 工控机 、 光 电传 感 器 以 及 必 具 有 高速和 可靠 性 ,

基于FPGA的多通道高速CMOS图像采集系统

DOI 1. 7 /i n10 — 3 1 0 8 1 1 文章编 号:0 2 83 (0 8 2 — 0 6 0 文献标识码 : 中图分类号: P 7 :03 8 .s. 2 8 3 . 0 . . 2 7 js 0 2 20 10 — 3 1 2 0 )1 0 4 — 3 A T24

1 引言

t m s s t e mo u e t cu e e i n L e u e h d l sr t r d sg , VDS n i g p n tr e h o o is a d e s r s t e r a — i e fr n e o aa a — u a d p n — a g so e t c n l ge , n n u e h e l t me p r ma c f d t c o q ii o a d r n mi s n I n r d c s h o e ai g r cp e a d r a iain u st n n t s s i . i t u e t e p r t p i i ls n e l t meh d o ma e c u st n, a a r n i o s — i a o t o n n z o t o s f i g a q ii o d t t s in, e i a t q e t l c n r l n d t d s raii g u n i o t a d aa e e ilz mo u e . h e p r n e i c t s h s se r aie ma e c u st n, a s s in n a o n d ls e x ei T me t c r f a e t e y tm e l s i g a q ii o t n miso a d ti z i r

基于FPGA的实时视频图像采集与显示系统的设计与实现

基于FPGA的实时视频图像采集与显示系统的设计与实现作者:贡镇来源:《现代电子技术》2013年第13期摘要:主要针对目前视频图像处理发展的现状,结合FPGA技术,设计了一个基于FPGA的实时视频图像采集与显示系统。

系统采用FPGA作为主控芯片,搭载专用的编码解码芯片进行图像的采集与显示,主要包括解码芯片的初始化、编码芯片的初始化、FPGA图像采集、PLL设置等几个功能模块。

采用FPGA的标准设计流程及一些常用技巧来对整个系统进行编程。

重点在于利用FPFA开发平台对普通相机输出的图像进行采集与显示,最终能在连接的RCA端口显示屏显示。

关键词: FPGA;视频图像采集;编码芯片;解码芯片中图分类号: TN911⁃34 文献标识码: A 文章编号: 1004⁃373X(2013)13⁃0046⁃03Design and Implementation of real⁃time video image captureand display system based on FPGAGONG Zhen(Anhui University of Science and Technology, Huainan 232000, China)Abstract: Based on the current development status of the video image processing and FPGA technology, a FPGA⁃based real⁃time video image capture and display system is designed in this paper. Equipped with dedicated coding and decoding ship for image capture and display, the system adopts FPGA as the main control chip, which are composed of decoding chip initialization module, the encoding chip initialization module, FPGA image acquisition module and PLL setting module. FPGA⁃standard design flow and some commonly used techniques are taken to program the entire system. The focus is to realize the ordinary camera output image acquisition and display via the FPFA development platform, and ultimately connect the RCA port display screen.Keywords: FPGA; video image capture; coding chip; decoding chip0 引言随着时代的发展,人们在图像处理领域取得了相当多的成果,研究出了很多算法,例如中值滤波、高通滤波等。

基于FPGA和ISA总线的图像数据采集系统

控 制 信 号 如 时 钟 信 号 MCL 单 帧模 式 下 的 帧触 发 K、 信 号 S NC、 位 信 号 I T 等 等 。 其 中 MCL 由 Y 复 NI K OS C分 频 得 到 , Y S NC通 过 I 地址 0 0 写 操 作 来 O 3A 产生 , 位信 号 可 由 F G 或 外 接 开关 产 生 。 复 P A

控 制 其 它 子 模 块 , 接 受 其 它 子 模 块 送 来 的 数 据 和 并 状 态 信 号 ,送 到 I A 总 线 :IC TRL 模 块 与 S IC

S M2 0 4的 IC总 线 接 口 , I L T 模 块 的 控 C 01 I 在 OS C 制 信 号 下 , 格 按 照 IC标 准 , 成 对 S M2 0 4的 严 I 完 C 01 初 始 化 , 将 寄 存 器 数 据 和 出 错 信 号 通 过 I L T 并 OS C 模 块 送 到 微 机 ;S AM C RL 模 块 与 S A R T R M 和 S M2 0 4接 口 , 成 数 据 缓 存 功 能 , 先 将 图 像 数 C 01 完 首 据转 移 到 S AM 中 缓 存 , 将 图 像 数 据 从 S R 再 RAM 中转 移 到 计 算 机 中 ; DMA —S模 块 实 现 DMA 方 式 , 当D MA—S收 到 I L T 模 块 发 出 的 DMA 允 许 信 OS C 号 , 发 送 DMA 请 求 , 待 计 算 机 发 DMA 应 答 信 就 等 号后 , 传 输 开始 信 号 , 发 S M —C RL模 块 将 发 触 RA T 数据 从 S M 中 转 移 到 微 机 中 ; MP E NT 模 块 RA C L TI

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

四川师范大学成都学院EDA实训报告书 1 基于FPGA的图像采集系统设计

前言 随着科技社会的发展,图像采集系统在日常生活、工业生产、国家安全等众多领域得到广泛的应用,具有广阔的应用前景和研究价值。采用FPGA进行设计的图像采集系统有良好的扩展性能和相对稳定的硬件结构。主要工作如下: 1)分析图像采集和图像处理的原理和特点,设计硬件电路的原理图,完成系统PCB板图的设计。 2)针对FPGA进行内部功能模块的划分,使用Verilog HDL硬件描述语言进行设计。 3)利用SOPC Builder完成NIOS处理器软核及其外设的创建和配置。 4)根据FPGA内部硬件电路的特点,选择适合FPGA的算法,并对算法进行优化。 5)在NIOS II IDE环境下用Verilog HDL语言编写图像传感器控制、图像采集、SRAM读写控制、图像显示等程序,实现完整的图像采集系统功能。

1课题分析 1.1 选题背景(含国内外相关研究综述及评价)与意义 EDA技术的发展和应用普及性越来越高,已经涉及到现代电子产品设计的各个系统、各个领域中。之所以有这样的广泛应用,主要得益于可编程逻辑器件的长足发展和日益成熟,可编程逻辑器件(Programmable Logic Device, PLD)是一种半定制集成电路,在其内部集成了大量的门和触发器等基本逻辑单元电路,通过用户编程来改变PLD内部电路的逻辑关系或连线,从而得到所需要的电路设计功能。这种新型逻辑器件,不仅速度快、集成度高,能够完成用户定义的逻辑功能,还可以加密和重新定义编程,其允许编程次数可以达到上万次。可编程逻辑器件的出现,大大改变了传统数字系统设计方法,简化了硬件系统、降低成本、提高系统的可靠性、灵活性。因此,自20世纪70年代问世以后,PLD受到广大工程师的青睐,被广泛应用于工业控制、通信设备、仪器仪表和医疗电子仪器等众多领域,为EDA技术开创了广阔的发展空间。 VGA作为一种标准的显示接口,在视频和计算机领域得到了广泛的应用。VGA图像信号发生器是电视台、电视机生产企业、电视维修人员常用的仪器,其主要功能就是产生标准的图像测试信号。对VGA而言,其主要应用在工业控制领域,通过VGA接口实现将信息、图像、文字等内容显示各种VGA显示器上,为客户提供一种完美的显示界面,也是目前重要的显示终端。本次实验设计主要是基于FPGA芯片为处理器,利用硬件描述语言完成VGA的时序控制,并利用相应的实验平台,进行设计验证,基本实现了VGA的彩条信号和图像显示效果,达到了整个设计目标和要求。 四川师范大学成都学院EDA实训报告书 2 1.2 选题研究的方法与主要内容

1.2.1研究方法 通过查阅资料,学习VGA工作原理和控制方法,掌握EDA技术应用基本技巧,运用FPGA为设计实现的处理器,完成VHDL对各个模块的功能描述,在实验平台上完成整个系统设计实现。

1.2.2主要内容 根据设计任务,制定实现方案 应用VHDL完成对系统中各个功能模块的描述 完成顶层设计文件,并调试仿真系统 下载程序代码到FPGA,在实验平台上验证VGA是否正常显示 撰写设计报告书

1.3 研究条件和可能存在的问题 1.3.1研究条件 会使用EDA开发工具软件Quartus II ,能熟练使用VHDL语言编写时序电路,需要有相应的实验开发平台。 1.3.2可能存在的问题: VGA时序控制不正确,无法正常显示相应的图形 VGA硬件接口电路PCB设计不能实现其功能 FPGA内部ROM存储空间太小,不能存储大容量的图片数据

1.4 拟解决的主要问题和预期的结果 1.4.1拟解决的主要问题 VGA时序控制问题 PROTEL绘制VGA电阻分压网络电路设计问题 调试VHDL程序代码常见错误

1.4.2预期的结果 通过完成整个系统的电路设计,实现各个功能模块和顶层设计电路,能在显示器上

正确看到横竖彩条、棋盘格图形和图片显示等效果。

2 图像采集系统介绍 2.1 图像采集系统功能分析 这部分阐述了图像采集系统的各种动作功能和控制要求,给出了完整的图像采集系统操作规程,并介绍了图像采集运行系统中所包括的人工操作步骤。 2.1.1 图像采集系统的基本功能 在进行上、下位机程序编写之前,首先要做的工作是确定图像采集系统本身所具四川师范大学成都学院EDA实训报告书 3 备的功能及在进行某种操作后所具有的状态。

在实际生活中,我们见到的图像采集系统可以采集一些简单的图像,如书本、人物和植物等。图像采例集系统的基本功能就是对图像进行采集,并进行简单的处理。举一个简单的例子来说明: 采集一本书的图像,系统会根据书的颜色大小自动调整,使采集的图像清晰,尽量减小失真。当图像达到最佳状态时,系统等待外部命令,如继续采集,则同上,如果此时不再采集而按下退出按钮,系统则要进行退出操作,并提示你是否保存所采集的图像,完成此次操作。由此看来,系统一次采集要涉及摄像头、VGA以及FPGA等,这是它的内部功能。基于FPGA实现的图像采集系统的整体结构框图如图1.1.1-1所示: 系统主要分为:图像采集模块、PLL锁相环时钟管理模块、I2C总线模块、FIFO图像数据处理模块、Nios II 显示控制模块。系统中PLL负责为Nios II嵌入式内核、外部SDRAM和OV7670摄像头提供时钟,系统通电后,FPGA首先从EPCS中读取配置数据,完成自身程序加载,随后对系统时钟分频为摄像头提供系统时钟,然后通过I2C总线完成对OV7670摄像头的配置。 配置完成后,OV7670将采集到的图像数据输出格式转换为标准的图像数据及图像时钟送入FPGA进行处理,并将处理后的图像数据通过FIFO模块暂时存储在SDRAM中进行缓冲,同时Nios II模块读取存放在SDRAM中的图像数据,按照TFT液晶显示的时序、数据要求将图像数据送到TFT彩色液晶显示屏上显示。

图1.1.1-1 图像采集系统结构 3 系统硬件设计

3.1 FPGA选型

FPGA是该系统的核心,由于系统目前只是完成简单的图像处理,故FPGA选用Altera

公司的低成本FPGA Cyclone II系列器件简介如表所示。

OV7670摄像头 I2C模块 视频采集模块 EPCS16配置芯片 PLL FIFO数据缓存模块

彩色LCD

显示

液晶显示控制模块

SDRAM控制模块 SDRAM 四川师范大学成都学院EDA实训报告书

4 Cyclone II器件采用90nm工艺制造,它延续Cyclone的低成本定位,在逻辑容量、

PLL、乘法器和I/O数量上都比Cyclone有了较大提高,应用Cyclone II进行图像处理开发有如下优点:(1)低成本高性能,适应图像处理要求较高的需要。(2)丰富的内嵌存储器资源,适应大量图像数据存取的需要。(3)丰富的硬件乘法器,适应图像处理算法的需要。系统的FPGA选用开发板自带的EP2CS5Q208C8芯片。

Cyclone II系列FPGA参数对比 器件 EP2C5 EP2C8 EP2C15 EP2C20 EP2C35 EP2C50 EP2C70 逻辑单元 4608 8256 14448 18752 33216 50528 68416 M4K RAM块 26 36 52 52 105 129 250 总比特数 119808 165888 239616 239616 483840 594432 1152000 嵌入式乘法器 13 18 26 26 35 86 150 PLL个数 2 2 4 4 4 4 4 最多用户I/O管脚 158 182 315 315 475 450 622

3.2 图像采集模块选择

图像采集采用OV7670图像传感器,OV7670图像传感器体积小、工作电压低。OV7670

摄影头的VGA图像最高达到30帧/秒。通过SCCB总线控制内部寄存器,可以是OV7670输出整帧、子采样、取窗口等方式的各种分辨率的图像数据。用户还可以完全控制图像质量、数据格式和传输方式。OV7670与FPGA硬件连接如图所示。

3.3 图像显示模块

图像显示通过在FPGA中构建的Nios II嵌入式内核实现,Nios II系统可以在设计

阶段根据实际的需求来增减外设的数量和种类。可以使用Altera提供的开发工具SOPC Builder,在FPGA器件上创建软硬件开发的基础平台,即用SOPC Builder创建嵌入式四川师范大学成都学院EDA实训报告书 5 内核CPU和参数化的接口总线Avalon。在此基础上,可以快速地将硬件系统与常规软件

集成在单一可编程芯片中。而且SOPC Builder还提供标准的接口方式,以便用户将外围电路做成Nios II嵌入式内核可以添加的外设模块。这种设计方式,方便了各类系统的调试。 3.4 PLC的选型与工作原理 当某一个控制任务决定由PLC来完成后,选择PLC就成为最重要的事情。一方面要选择多大容量的PLC ,另一方面是选择什么公司的PLC及外设。 对第一个问题,首先要对控制任务进行详细的分析,把所有的I/O点找出来,包括开关量I/O和模拟量I/O以及输出是用继电器还是晶体管或是可控硅型。

3.4.1 PLC的硬件结构图:

图2.4.1-1 PLC硬件结构图 3.4.2 PLC各部分的作用与工作原理 3.4.2.1 中央处理器 CPU是由控制器和运算器组成的。运算器也称为算术逻辑单元,它的功能就是进行算术运算和逻辑运算。控制器的作用是控制整个计算机的各个部件有条不紊地工作,其基本功能是从内存中取指令和执行指令。他的重要功能如下:

★ 诊断PLC电源、内部电路的工作状态及编制程序中的语法错误。 ★ 采集由现场输入装置送来的状态或数据,并送入PLC的寄存器中。 ★ 按用户程序存储器中存放的先后顺序逐条读取指令,进行编译解释后,按