基于FPGA的图像采集系统设计与实现

基于FPGA控制的图像采集和存储系统

储 系 统 结 构 。 计 了在 图 像 采 集 和存 储 系 统 中 的 F GA 控 制 模 块 , US 设 P 用 B通 讯 模 块 实 现 了 采 集 存 储 系统 和计 算 机 之 问 的 数

据 传输 , 足 了系 统 对 回放 的存 储 图像 不 丢 帧 的 要求 。经 实 际 检 验 , 好 地 满 足 了实 验要 求 。 满 较 关 键 词 :P A, F G 图像 采 集 和 存储 , B通讯 模 块 US

FP GA o t o s d sg e n t e s s e o ma e a q i i o n t r g . e mo u e o B r a ie h c n r l e i n d i h y t m fI g c u s t n a d s o a e Th d l fUS e l s t e i i z d t o mu a a i n b t e h ma e a q iiin a d s o a e s s e a d t e c mp t r a d t i c e a ac m n c t e we n t e I g c u st n t r g y t m n h o u e , n h s s h me o o me t h n e t a y t m ’S t r g i g s o o t P a t a p l a i n s o h s s h me s e s t e e d h t s se s o a e ma e i n t l s . r c i l a p i to h ws t i c e i c c ra o a l. e s n b e

的实 时采集 , 储并 回放存 储 图像 的 系统 。 存

l 系统结 构 与组 成

基于FPGA的一体化实时图像采集系统设计

快 速采 样 、存 储及 图像 数据 处 理 就 显 得 尤 为必 要。 传统 的使 用单 片机作 为控 制器 对数 据进 行 间

B a s e d o n C MO S i m a g e s e n s o r ,o n e F i e l d P r o g r a m ma b l e G a t e A r r a y ( F P G A )i s c h o s e n a s t h e

7 2 6 0 0 0 )

Ab s t r a c t : I n o r d e r t o o b t a i n r e a l - t i me a n d p r e c i s i o n i ma g e f r o m CMOS i ma g e s e n s o r ,a n i mp r o v e d r e a l - t i me d a t a a c q u i s i t i o n s y s t e m i s d e s i g n e d b a s e d o n t h e c o mb i n a t i 刘 萌

( 商洛学 院 物理与电子信息工程系, 陕西商洛 7 2 6 0 0 0 )

摘 要: 为 了通过 C MO S图像探测器实时准确 的获取 图像 。 设计 了一套基 于 F P G A结合 S D R A M

的 实时图像 采 集 系统。根据 C MO S图像探 测 器输 出图像 格式 的特 点 ,选 用 了一 片 X i l i n x公 司

Ke y wor ds : CMOS i ma g e s e n s o r ;F PGA;p i n g — po ng o p e r a t i o n;SDRAM

基于FPGA的多路图像采集系统的软件设计

ue o r AA7 1 H vd od c d r n woF GA oahe e tea q iio ssfu S 1 3 ie e o esa d t P t c iv h c ust n,soa e n ipa ft h n e ma e i trg ,a d dsly o woc a n li g ,

fl sre .I fr e e l e h ac d o f u ain o wo F GA,a d te F mnb s c n g rt n, te I U6 6 ul cen t ut rrai s te c sa e c n g rt ft P — h z i o n h C o iu o f u ai i o h T 5

( 安 工 业 大 学 计 算机 科 学 与 工程 学 院 , 西 西 安 7 0 3 ) 西 陕 10 2

摘 要 :分 析 了 现 有 的 视 频 采 集 方 案 的 研 究现 状 。 对如 何 采 用 C D 摄 像 头采 集 多通 道 、 C 高分 辨 率 、 高质 量 的 图像 以及

基 于 F G 的 嵌 入 式 图 像 采 集 系统 的 实 现 方 法做 了研 究 。 与传 统 图像 采 集 系统 相 比 . 系统 主要 利 用 四 片视 频 解码 PA 该

关键 词 : A 7 l H;F G I U 6 ;图像 采 集 S A l3 P A; T 5 5

,

文 章 编 号 :17 — 2 6 2 1 )3 14 0 6 4 6 3 (0 号 :I 99 , 1 ’ P

文献标识码 : A

The s fwa e de i n o u t- ha ne m a e a q sto s s e b s d o FPGA o t r sg fm lic n li g c uiii n y t m a e n

基于ZYNQ FPGA实现图像采集存储显示

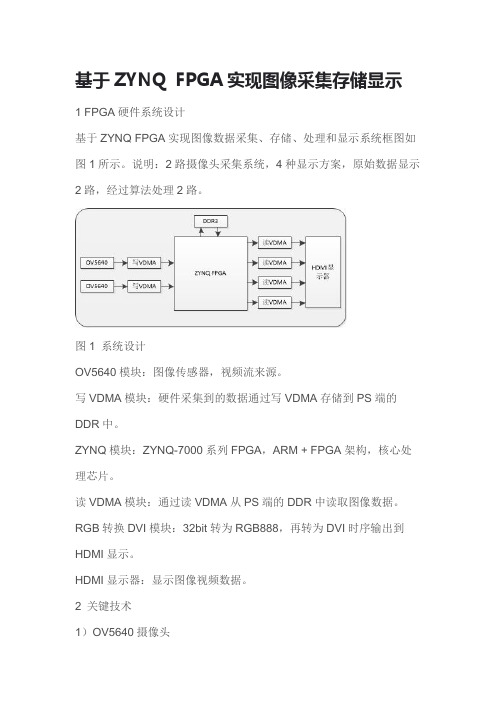

基于ZYNQ FPGA实现图像采集存储显示1 FPGA硬件系统设计基于ZYNQ FPGA实现图像数据采集、存储、处理和显示系统框图如图1所示。

说明:2路摄像头采集系统,4种显示方案,原始数据显示2路,经过算法处理2路。

图1 系统设计OV5640模块:图像传感器,视频流来源。

写VDMA模块:硬件采集到的数据通过写VDMA存储到PS端的DDR中。

ZYNQ模块:ZYNQ-7000系列FPGA,ARM + FPGA架构,核心处理芯片。

读VDMA模块:通过读VDMA从PS端的DDR中读取图像数据。

RGB转换DVI模块:32bit转为RGB888,再转为DVI时序输出到HDMI显示。

HDMI显示器:显示图像视频数据。

2 关键技术1)OV5640摄像头设计中采用两片美国OmniVision公司的CMOS图像传感器OV5640,OV5640芯片支持DVP和MIPI接口。

为保证OV5640正常工作,需要依次实现以下时序要求。

a、ResetB拉低、PWND拉高;b、DOVDD和AVDD同时上电;c、电源稳定5ms后,拉低PWND,再过1ms,拉高ResetB;d、20ms后初始化OV5640DESCCB寄存器。

e、通过IIC接口配置,配置目标为RGB565、30FPS、720输出格式;f、FPGA接收来自OV5640的视频流数据输入,需要对摄像头完成相应的时序操作。

每次传输8bit,16bit为一个像素点,所以要进行数据转换8bit-16bit-32bit;2)图像处理算法边缘检测算法要求首先找到图片中物体的边缘,由于边缘处颜色变化一般比较明显,在工程上一般借助卷积滤波器实现,卷积滤波器相当于求导的离散版本。

针对图像进行边缘检测,有多种不同的滤波器算子,我们采用的Sobel滤波器算子图1,分别针对图像水平方向的边缘以及竖直方向的边缘,求和得出图像的边缘。

图1 滤波器算子3)ZYNQ FPGAZYNQ 7000系列基于Xilinx 全可编程的扩展处理平台结构,芯片内部集成ARM 公司双核Cortex-A9处理器的处理系统(PS端)和基于Xilinx逻辑资源的可编程逻辑系统(PL端)。

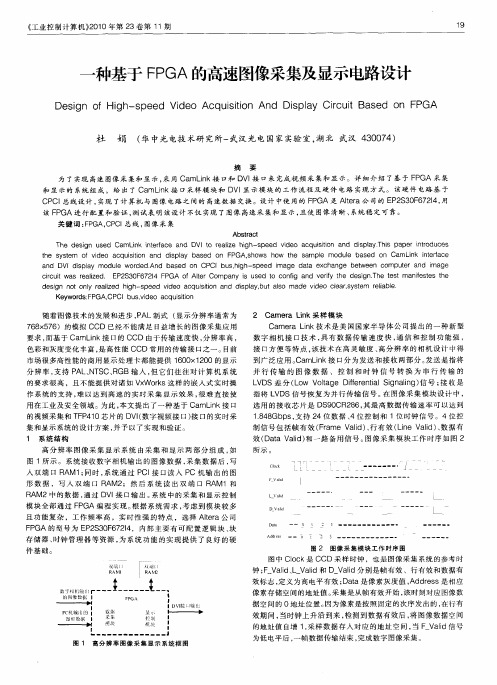

一种基于FPGA的高速图像采集及显示电路设计

1 9

一

种基于 F G P A的高速图像采集及显示电路设计

De i f Hi —s e d Vi o Ac ust n An Dip a r utBa e o P sgn o gh— p e de q iio d i s ly Ci i c s d n F GA

选 用 的 接 收 芯 片是 DS 0 R 8 , 最 高 数 据 传输 速 率 可 以达 到 9 C 2 6其

该 F G 进 行 配 置和 验 证 , 试 表 明该 设 计 不仅 实现 了 图像 高 速 采 集和 显 示 , 使 图像 清 晰 、 PA 测 且 系统 稳 定 可 靠 。

关 键 词 :P F GA, Cl CP 总线 , 图像 采 集

Ab ta t s rc

Th si u e Ca Ln nera e nd e de gn s d m ik it f c a DVI o r al e i -s ed i a qust d t e i hgh pe vdeo c iion an diply.hi z i s a T s pap itodu es er nr c t e y tm of i a quiion nd h s se vdeo c st a diply a d i s a b se on PGA,h ws o F s o h w t s m pl m o e he a e dul ba ed s on Cam Lnk n e ce i it da an DVI s a o e d diply m dul wor d. d de An ba ed n s o CP bu ,i Cl shgh- ee i a da a ex h ge et e c sp d m ge t c an b we n ompu e an i tr d mag e ci ui wa r aied. EP 30 7 4 FP r t c s el z 2S F6 21 GA o t m p y i u e t n i d ery h de i . e es manfses h fAl Co an s s d o co fg an v i te er f sgnTh t t i t te e de i n tonl eaied i sgn o y r l z hgh—s ee vdeo a p d i cqust a d iion n diply, talo m a de ea ,y tm r i l i s a bu s de vi o cl rs se el e ab Ke wo d : P y r s F GA. Cl s, de a quiion CP bu vi o c st i

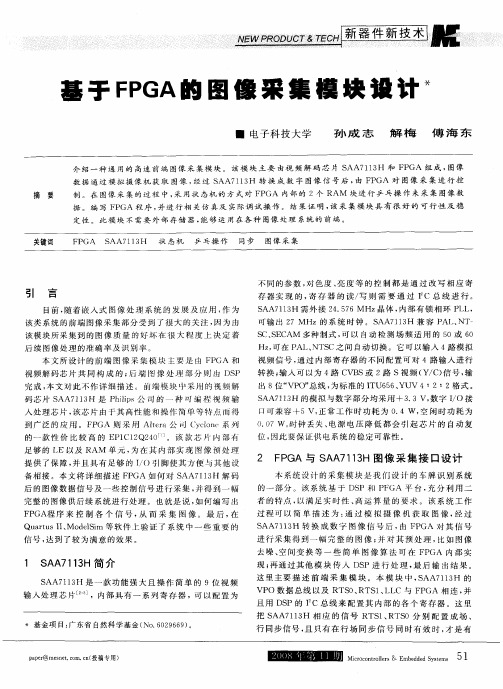

基于FPGA的图像采集模块设计

口可兼 容 +5V, 常 工 作 时 功 耗 为 0 4 W , 闲 时 功 耗 为 正 . 空 o 0 。 钟 丢失 、 源 电 压 降 低 都 会 引起 芯 片 的 自动 复 . 7W 时 电 位, 因此 要 保 证 供 电系 统 的 稳 定 可靠 性 。

足 够 的 IE以及 RAM 单 元 , 在 其 内 部 实 现 像 预 处 理 为

行 同步信号 , 只有 在行 场 同步 信号 同时有效 时 , 且 才是 有

且 用 DS P的 IC总 线 来 配 置 其 内部 的 各 个 寄存 器 。这 里 把 S AA7 1 H 相 应 的 信 号 R 1 RTS 13 TS 、 0分 别 配 置 成 场 、

* 基 金 项 目: 东省 自然 科 学 基 金 ( o 62 69 。 广 N . 0 9 6 )

提 供 了保 障 , 且 具 有 足 够 的 I( 引 脚 使 其 方 便 与 其 他 设 并 /)

备 相 接 。本 文 将 详 细 描 述 F GA如 何 对 S P AA7 1 H 解 码 13 后 的 图 像 数 据 信 号 及 一 些 控 制 信 号 进 行 采 集 , 得 到 一 幅 并 完 整 的 图像 供后 续 系 统 进 行 处 理 。也 就 是 说 , 何 编 写 出 如 F GA程 序 来 控 制 各 个 信 号 , 而 采 集 图 像 。 最 后 , P 从 在 Qu ru IMo eSm 等 软 件 上 验 证 了 系 统 中一 些 重 要 的 at sI、 d l i 信 号 , 到 了较 为满 意 的效 果 。 达

出 8位 “ ’ VP 总线 , 标 准 的 I 为 TU6 6 YUV 5、 4:2: 2格 式 。 S AA7 1 H 的模 拟 与 数 字 部 分 均采 用 +3 3V, 字 Io接 13 . 数 /

基于FPGA的CMOS图像采集系统设计

DP S 模块等整个系统 的胶合作用 , 是整个系统中 开发难度最大的部分。系统 的框图如图 1 所示。

AS P 模块采用选用 C O M S图像 传感 器芯片 0 74。S M芯片选用 IS 公司静态随机存储 V 69 R A SI

C O 工艺静态随机存储器。 MS 整个 系统的主控芯 片采用 XLN 的 F G ,P A有着丰富的逻辑 II X P A FG 门和 I O引脚 ,P A作为采样控制芯片, FG 其主要 作用是产生 S C C B总线来配置内部寄存器 , 控制 0 74 输出的视频数据在 S M 中的存储 , V 69 A R 这

维普资讯

第 3期

20 0 7年 9月

电

光

系 统

No 3 . Au .2 0 g 07

E e t n c a d E e to o t a y tms l cr i n l cr - p i lS s o c e

基于 F G P A的 C S图像采集 系统设计 MO

CO M S图像传感器是 近年发展较快 的新 型 图像传感器 , 当前 图像传 感器市场 , M S 在 C O 传 感器以其低廉的价格得到越来越多消费者的青 睐。由于采用 了相同的 C O 技术 , M S 因此可以将 像素阵列与外围支持 电路集成在 同一块芯片上。 CO M S图像传感器将整个 图像 系统 集成在一块 芯片上 , 具有以下优点 : 体积小 、 重量轻、 功耗低、 编程方便 、 易于控制、 平均成本低。 在 目 的应用中, 前 多数采用软件进行数据的

样就可以让 D P集中于图像的处理工作. S 概括地 讲, 它主要包括如下几个逻辑控制功能:

基于FPGA的双通道CMOS图像采集系统设计

0 引 言

整 个 系 统 的 可 靠 性 。 同 时 , 用 2片 大 容 量 的 S R M 以 采 D A

目前 , 越来越多 的图像采集 系统采用 C S图像传 感 MO

器 …作为图像采 集器件 。随着 集成 电路设 计技 术 的不断 提高 , MO C S图像传 感器 的采集速 度不 断增大 。在 实际 应用 中, 传统 的单通道 数据传输 方式和单 片机实现 的图像 处理系统 已经远远无法满 足设计要 求 , 须采用新 的数据 必 传输方式和设计方法来实现图像采集 、 传输和存储功能。

本 文 设 计 了一 种 以 F G 芯 片 为 核 心 处 理 器 的 双 通 道 PA

乒乓操作 的方式进行 数据存储 , 保证 能够实时地接 收图像

传感器产生的图像数据 。 经综合 分 析 和考 虑,P A采 用 A e FG hr a的 C c n yl e o E 2 3 F8 C 视频采集芯片用 飞利 浦的 S A 132块 型 P C 5 4 4 8, A 71 , 号为 K S 42的 S R M 和 F G 463 D A P A构成 图像 帧存储 与传输

Ab ta t Re lt r c s ig o g s u u l o t — e k i mb d e ma e p o e sn y tm. a i g sr c : a — me p o e sn fi e i s al a b t e n c n e e d d i g rc s i g s s i ma y l e T kn

teavnaeo aae poes g af l por al gt ar ( P A)b sdC S i g cu io h da t fprll rcsi , e rga g l n id mm b a r y F G e e a ae MO mae aq it n si ss m ids nd T em d l s ut eds n fs i fsotFF yt ei e . h o u rc r ei ,rtni t u( IO)adpn—ags r cn l e r ue e s g et u g i r n igpn o t h o g s e sd tee o i a

基于FPGA的图像处理与识别系统设计

基于FPGA的图像处理与识别系统设计摘要:本文章主要介绍了基于FPGA的图像处理与识别系统的设计。

首先,简要介绍了FPGA技术的基本原理和优势。

接着,分析了图像处理与识别系统的关键问题和需求。

然后,详细描述了基于FPGA的图像处理与识别系统的设计步骤和流程。

最后,给出了实验结果和性能评估。

通过本文的阐述,读者可以了解基于FPGA的图像处理与识别系统的设计思路和方法,并且可以应用于实际应用中。

关键词:FPGA,图像处理,识别系统,设计。

1. 引言随着计算机视觉技术的飞速发展,图像处理与识别技术在各个领域得到广泛应用。

基于FPGA的图像处理与识别系统具有并行性能强、低功耗、高速处理等优势,成为研究和应用的热点之一。

本文旨在通过设计一个基于FPGA的图像处理与识别系统,探索FPGA技术在该领域的应用。

2. FPGA技术概述FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它由大量的逻辑门和可编程的互连电路组成。

与传统的ASIC(Application-Specific Integrated Circuit)相比,FPGA具有灵活性和可重新配置性的特点,可以极大地加快设计周期并降低成本。

3. 图像处理与识别系统的关键问题和需求图像处理与识别系统的关键问题主要包括图像采集、特征提取、分类判断等。

针对不同领域和应用,系统的需求也有所不同,例如实时性要求、算法复杂度、性能稳定性等。

4. 基于FPGA的图像处理与识别系统设计步骤4.1 图像采集与预处理图像采集是构建图像处理与识别系统的基础,可以通过CCD或CMOS等传感器进行图像采集。

在FPGA中,采用外部模块与FPGA进行通信,将图像数据传输到FPGA 芯片中,并进行预处理。

4.2 特征提取与处理特征提取是图像处理与识别系统的核心任务。

在FPGA 中,可以通过利用FPGA的并行计算能力加速特征提取算法。

例如,采用卷积神经网络(CNN)对图像进行卷积运算,提取图像的特征。

基于FPGA的图像处理系统设计与实现

基于FPGA的图像处理系统设计与实现图像处理是计算机视觉领域中的重要技术之一,可以对图像进行增强、滤波、分割、识别等操作,广泛应用于医学图像处理、工业检测、安防监控等领域。

而FPGA(Field Programmable Gate Array)可编程门阵列,则是一种自由可编程的数字电路,具有并行处理能力和灵活性。

本文将介绍基于FPGA的图像处理系统的设计与实现。

一、系统设计流程1. 系统需求分析:首先需要明确图像处理系统的具体需求,例如实时性、处理的图像类型、处理的算法等。

根据需求,选择合适的FPGA芯片和外设。

2. 图像采集与预处理:使用图像传感器或摄像头采集图像数据,然后对图像进行预处理,如去噪、增强、颜色空间转换等,从而提高后续处理的准确性和效果。

3. 图像处理算法设计与优化:根据具体的图像处理需求,选择适合的图像处理算法,并对算法进行优化,以提高处理速度和效率。

常用的图像处理算法包括滤波、边缘检测、图像分割等。

4. FPGA硬件设计:基于选定的FPGA芯片,设计硬件电路,包括图像存储、图像处理模块、通信接口等。

通过使用硬件描述语言(如Verilog、VHDL)进行功能模块设计,并进行仿真和验证。

5. 系统集成与编程:将设计好的硬件电路与软件进行集成,包括FPGA程序编写、软件驱动开发、系统调试等。

确保系统的稳定运行和功能实现。

6. 系统测试与优化:对整个系统进行完整的测试和验证,包括功能性测试、性能测试、稳定性测试等。

根据测试结果,对系统进行优化,提高系统的性能和可靠性。

二、关键技术及挑战1. FPGA芯片选择:不同的FPGA芯片具有不同的资源和性能特点,需要根据系统需求选择合适的芯片。

一方面需要考虑芯片的处理能力和资源利用率,以满足图像处理算法的实时性和效果。

另一方面,还需要考虑芯片的功耗和成本,以便在实际应用中具有可行性。

2. 图像处理算法优化:在FPGA上实现图像处理算法需要考虑到算法的计算复杂度和存储开销。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的图像采集系统设计与实现

摘要:图像采集是数字化图像处理的第一步,开发图像采集平台是视觉系统开发的基础。

本课题提出了基于FPGA的图像采集系统整体实现方案。

采用Verilog HDL语言编写程序,并用Modelsim等软件进行联合仿真,然后下载到DE2开发板实现图像采集功能。

关键词:FPGA 图像采集DE2开发板Verilog HDL Modelsim

图像采集是视频信号处理系统的前端部分,正在向高速、高分辨率、高集成化、高可靠性方向发展。

图像采集处理器件主要有专用集成芯片、数字信号处理器和现场可编程门阵列以及相关电路组成。

近年来,微电子技术和超大规模的集成电路制造技术的发展,特别FPGA 的发展,为提高图像采集处理系统各种性能提供了新的思路和方法。

1 系统硬件结构设计

本系统采用的是DE2开发平台,系统主芯片采用Altera公司的Cyclone II系列FPGA(EP2C35F672C6),该芯片具有33 216个LE,105个M4K RAM块,472 kb的内部RAM容量,35个内嵌乘法器单元,4个模拟锁相环等,广泛应用于汽车电子、消费电子、音/视频处理、通信以及测试测量等终端产品市场。

系统设计还包含有:D5M视频采集板,8MB SDRAM、视频D/A、VGA接口等,硬件结构如图1所示。

1.1 图像传感器

本系统所采用的TDRB_D5M摄像头套件,使用的是CMOS图像传感器。

集成500万像素摄像头,通过对其内部寄存器的设置,来配置摄像头的图像采集和工作模式。

1.2 视频缓存器设计

DE2平台采用的是型号为IS42S16400的SDRAM,IS42S16400是ISSI公司推出的一种单片存储容量高达64 Mb(即8 MB)的16位字宽高速SDRAM芯片。

1.3 视频D/A电路

DE2平台的Video DAC选用了Analog Device公司的ADV7123。

从图像缓存器中提取的数据转换为视频信号,通过VGA输出显示。

ADV7123是三路高速、10位输入的视频D/A转换器,具有240MHz 的最大采样速度,与多种高精度的显示系统兼容,包括RS-343A和RS-170,可以广泛应用于如HDTV、数字视频系统、高分辨率的彩色图片图像处理、视频信号再现等,因此,能够满足我们多方面应用需求。

2 FPGA内部模块设计

在确定DE2平台的硬件需求部分后,需要在FPGA中设计相应的功能模块,才能使系统正常的工作。

这些功能模块有:图像采集模块、图像格式转换模块、图像缓存模块和图像显示模块。

2.1 像采集模块

系统硬件使用的是D5M摄像头套件,该套件采用的是500万像素CMOS数字图像传感器,可以使用I/C总线配置其相应的寄存器来设置工作模式和采集数据的大小。

图像采集模块可以分为:图像数据捕获模块和COMS传感器配置模块。

2.2 图像格式转换模块

本系统采用的CMOS传感器采集到的数据是Bayer颜色模式,使用数据缓存加流水线的处理方式,将由上一级抓取到行数据实时转换成RGB数据,其中R、G、B各占12位,在输入SDRAM缓存中时,多口SDRAM控制模块只取用R、G、B的高10位来存储,所以RGB最终是30位的数据。

2.3 图像缓存模块

预处理的图像需要放在存储器中,对于大部分的FPGA来说器件内部都含有4 k的内存,而本系统采集的图像容量为1.1 MB左右,还要考虑今后对动态图像处理功能的扩展,所以本设计选用了DE2外扩存储容量为8 M的SDRAM。

2.4 VGA显示模块

要把存储器里的图像在VGA接口显示器中显示,扫描时序是需要我们构造的。

不同的显示模式和刷新频率下,具体同步信号前、后、

同步信号、有效像素数是不同的,要根据像素时钟频率来设置。

本系统从缓存中读出的图像大小为640×480,59.94 Hz(60 Hz)。

3 系统仿真和结果分析

我们采用SignalTap II嵌入逻辑分析仪和ModelSim进行联合测试与仿真。

仿真结果完全符合系统的实时要求。

在Quartus II下在完成了整个系统工程的调试和验证后,通过Compilation仿真的Compilation Report可以看出系统的资源消耗,整个硬件系统消耗的逻辑资源为5%,实验表明,还有大量资源可以应用于其他模块。

本系统实现了实时图像采集,为之后的实时图像预处理和分析做准备。

这些信息可以用于图像分析、目标识别以及图像滤波等领域。

利用本课题所采用的开发环境可以进一步开发出更复杂的图像算法和创建更复杂的系统功能,使整个视频图像处理系统达到全面集成化,最终达到资源的充分利用。

参考文献

[1]张志刚.FPGA与SOPC设计教程DE2实践[M].西安:西安电子科技大学出版社,2007.

[2]李贵华,夏磊,韦先霜,等.基于SOPC的VGA显示技术的研究[J].计算机与数字工程,2007(2):138-139.

[3]胡瑶荣.基于FPGA的实时视频采集系统[J].电视技

术,2005(2):81-83.

[4]胡晓飞,殳国华,张士文.基于视频处理芯片和CPLD的实时图像采集系统[J].电子技术,2002(10):28-30.。