漏极开路od门中上拉电阻的取值范围的计算

上拉电阻的计算

上拉电阻的计算(2009-05-24 11:51:13)转载标签:杂谈(一)上拉电阻:1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC门电路必须加上拉电阻,才能使用。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

(二)上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理(三)对上拉电阻和下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素:1.驱动能力与功耗的平衡。

以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计是应注意两者之间的均衡。

2.下级电路的驱动需求。

同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

3.高低电平的设定。

不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。

以上拉电阻为例,当输出低电平时,开关管导通,上拉电阻和开关管导通电阻分压值应确保在零电平门槛之下。

4.频率特性。

以上拉电阻为例,上拉电阻和开关管漏源级之间的电容和下级电路之间的输入电容会形成RC延迟,电阻越大,延迟越大。

集电极开路 漏极开路 推挽 上拉电阻

集电极开路(OC)输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路;左边的三极管为反相之用,使输入为“0”时,输出也为“0”。

对于图 1,当左端的输入为“0”时,前面的三极管截止,所以5v电源通过1k电阻加到右边的三极管上,右边的三极管导通;当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止。

我们将图1简化成图2的样子,很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。

而当开关断开时,则输出端悬空了,即高阻态。

这时电平状态未知,如果后面一个电阻负载到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。

图3中那个1k的电阻即是上拉电阻。

如果开关闭合,则有电流从1k电阻及开关上流过,但由于开关闭合时电阻为0(方便我们的讨论,实际情况中开关电阻不为0,另外对于三极管还存在饱和压降),所以在开关上的电压为0,即输出电平为0。

如果开关断开,则由于开关电阻为无穷大(同上,不考虑实际中的漏电流),所以流过的电流为0,因此在1k 电阻上的压降也为0,所以输出端的电压就是5v了,这样就能输出高电平了。

但是这个输出的内阻是比较大的——即1k,如果接一个电阻为r的负载,通过分压计算,就可以算得最后的输出电压为5*r/(r+1000)伏,所以,如果要达到一定的电压的话,r就不能太小。

如果r 真的太小,而导致输出电压不够的话,那我们只有通过减小那个1k的上拉电阻来增加驱动能力。

但是,上拉电阻又不能取得太小,因为当开关闭合时,将产生电流,由于开关能流过的电流是有限的,因此限制了上拉电阻的取值。

另外还需要考虑到,当输出低电平时,负载可能还会给提供一部分电流从开关流过,因此要综合这些电流考虑来选择合适的上拉电阻。

如果我们将一个读数据用的输入端接在输出端,这样就是一个IO口了,51的IO口就是这样的结构,其中P0口内部不带上拉,而其它三个口带内部上拉。

当我们要使用输入功能时,只要将输出口设置为1即可,这样就相当于那个开关断开,而对于P0口来说,就是高阻态了。

上拉电阻详解

上拉电阻详解上拉电阻:1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC门电路必须加上拉电阻,才能使用。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理对上拉电阻和下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素:1.驱动能力与功耗的平衡。

以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计是应注意两者之间的均衡。

2.下级电路的驱动需求。

同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

3.高低电平的设定。

不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。

以上拉电阻为例,当输出低电平时,开关管导通,上拉电阻和开关管导通电阻分压值应确保在零电平门槛之下。

4.频率特性。

以上拉电阻为例,上拉电阻和开关管漏源级之间的电容和下级电路之间的输入电容会形成RC延迟,电阻越大,延迟越大。

上拉电阻的设定应考虑电路在这方面的需求。

下拉电阻的设定的原则和上拉电阻是一样的。

求职笔试基本考题—模电数电

求职笔试的基本考题—模电数电1,TTL电平:输出高电平>2.4V,输出低电平<0.4V。

在室温下,一般输出高电平是3.5V,输出低电平是0.2V。

最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。

2,CMOS电平:1逻辑电平电压接近于电源电压,0逻辑电平接近于0V。

而且具有很宽的噪声容限。

3,电平转换电路:因为TTL和COMS的高低电平的值不一样(ttl 5v<==>cmos 3.3v),所以互相连接时需要电平的转换:就是用两个电阻对电平分压,没有什么高深的东西。

哈哈4,OC门,即集电极开路门电路,OD门,即漏极开路门电路,必须外界上拉电阻和电源才能将开关电平作为高低电平用。

否则它一般只作为开关大电压和大电流负载,所以又叫做驱动门电路。

5,TTL和COMS电路比较:1)TTL电路是电流控制器件,而coms电路是电压控制器件。

2)TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。

COMS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。

COMS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常现象。

3)COMS电路的锁定效应:COMS电路由于输入太大的电流,内部的电流急剧增大,除非切断电源,电流一直在增大。

这种效应就是锁定效应。

当产生锁定效应时,COMS的内部电流能达到40mA以上,很容易烧毁芯片。

防御措施:1)在输入端和输出端加钳位电路,使输入和输出不超过不超过规定电压。

2)芯片的电源输入端加去耦电路,防止VDD端出现瞬间的高压。

3)在VDD和外电源之间加线流电阻,即使有大的电流也不让它进去。

4)当系统由几个电源分别供电时,开关要按下列顺序:开启时,先开启COMS电路得电源,再开启输入信号和负载的电源;关闭时,先关闭输入信号和负载的电源,再关闭COMS电路的电源。

6,COMS电路的使用注意事项1)COMS电路时电压控制器件,它的输入总抗很大,对干扰信号的捕捉能力很强。

上拉电阻和下拉电阻的选型和计算

上拉电阻和下拉电阻的选型和计算常见各类技术资料上,有些技术规范写道“无用的管脚不允许悬空状态,必须接上拉或下拉电阻以提供确定的工作状态”。

这个提法基本是对的,但也不全对。

下面详细加以说明。

管脚上拉下拉电阻设计出发点有两个:一个是在正常工作或单一故障状态下,管脚均不应出现不定状态,如接头脱落后导致的管脚悬空;二是从功耗的角度考虑,就是在长时间的管脚等待状态下,管脚端口的电阻上不应消耗太多电流,尤其是对电池供电设备。

从抗扰的角度,信号端口优选上拉电阻。

上拉电阻时,在待机状态下,源端输入常为高阻态,如果没有上拉电阻或下拉电阻,输入导线呈现天线效应,一旦管脚受到辐射干扰,管脚输入状态极容易被感应发生变化。

所以,这个电阻是肯定要加的。

下一个问题就是加上拉还是下拉。

如果加了下拉,在平常状态下,输入表现为低电平,但辐射干扰进来后,会通过下拉电阻泻放到地,就会发生从Low—High的一个跳变,产生误触发。

相当于一个乞丐,你给了他10万元,他的生活方式就会从穷人到富人发生一个改变。

但如果加了上拉电阻,在平常状态下,输入表现为高电平,辐射干扰进来后,如果低也没关系,上拉电阻会将输入端钳位在高电平,如果辐射干扰强,超过了Vcc的电平,导线上的高电平干扰会通过上拉电阻泻放到Vcc上去,无论怎样干扰,都只会发生High—Higher的变化,不会产生误触发。

相当于人家本来是一个富豪,你给了他10万元,他的生活方式不会发生任何的改变。

图1和图2是干扰状态下的电平示意图。

图2中的低电平由VL变为VL+ΔV时,产生了从低电平到高电平的跳变,有可能使后级电路误动作的风险。

下一个问题就是,确定了用上拉电阻后,是不是上拉电阻就可以随便选了呢?答案当然是“no”。

上拉电阻计算

上拉电阻的计算(一)上拉电阻:1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC门电路必须加上拉电阻,才能使用。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

(二)上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理(三)对上拉电阻和下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素:1.驱动能力与功耗的平衡。

以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计是应注意两者之间的均衡。

2.下级电路的驱动需求。

同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

3.高低电平的设定。

不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。

以上拉电阻为例,当输出低电平时,开关管导通,上拉电阻和开关管导通电阻分压值应确保在零电平门槛之下。

4.频率特性。

以上拉电阻为例,上拉电阻和开关管漏源级之间的电容和下级电路之间的输入电容会形成RC延迟,电阻越大,延迟越大。

上拉电阻的设定应考虑电路在这方面的需求。

上拉法测阻值原理

上拉法测阻值原理说起上拉法测阻值的原理,我有一些心得想分享。

你看啊,在我们的生活中,就像我们想知道一个不知道容量的水桶还能装多少水。

我们先把水桶装满水,然后看倒了多少水进去才能装满,这就有点类似于上拉法测阻值的思路,但不完全一样,只是个生活中的简单类比,方便理解。

在电路里,上拉法测阻值呢,简单来说,就是利用了欧姆定律这个理论依据。

欧姆定律就像一个准则,告诉我们电压、电流和电阻之间的稳定关系,也就是I = U / R(这里I是电流,U是电压,R是电阻)。

打个比方吧,电阻就像一个小怪兽,想要知道这个小怪兽有多厉害(阻值是多少),我们可以给它一个已知力量的挑战。

在上拉法里,我们给这个未知电阻串接上一个已知的电阻,然后再加上一个已知的电压。

这就像组队去挑战小怪兽一样,已知电阻就是我们的一个队友。

有意思的是,加上电压后就会有电流产生。

通过测量整个串联电路的电流大小,我们再根据欧姆定律,就可以大致算出这个未知电阻的阻值啦。

就好像我们知道了组队挑战小怪兽一共使出的力气,也知道队友的实力,就能推断出小怪兽的实力了。

实际应用案例很多,比如说在一些简单的电路板检测中。

要是某个小电阻坏了,我们不知道它正常阻值是多少,就可以用这个方法来测量。

不过说到这里,你可能会问:那上拉电阻的大小有限制吗?老实说,我一开始也不明白。

后来我发现它是有限制的,如果这个上拉电阻太大或者太小都会对测量结果有影响。

太大的话电流很小,测量精度就会下降很多;太小了又可能会对其他电路部分造成干扰。

在学习这个原理的时候,我还遇见过好多疑惑呢。

这就是我对上拉法测阻值原理的理解和分享啦。

那大家在自己生活中有没有遇到类似这种通过已知量去求未知量的事呢?欢迎一起讨论呀。

希望我的分享能让大家对这个原理有个初步的认识。

GPIO的问题介绍

今天一上午测试了下nandflash的各个管脚发现wp引脚无法拉高,一直处于写保护状态,导致NANDFLASH id无法读取,直接将wp通过上拉电阻拉高不行将控制WP的io隔断分别上拉和下拉电阻才搞定,具体原因不明,接下来再分析吧!nandflash id读取正确了但是驱动外部flash发现R/B引脚一直为高电平(由于NANDFLASH的r/b引脚为OD输出所以已经外接上拉电阻4.7k上拉)但是发现R/B引脚在操作的时候一直为高电平我不停的读nandflash ID发现R/B仍然是保持高电平按时序应该有低电平出现啊不知道什么原因?这个检测R/B电平的IO口也是OD门不知道是否这里有影响。

明天重新换下LPC2478的io口线试试看,因为这两个口线都是与2478的两OD 引脚连接了很是郁闷。

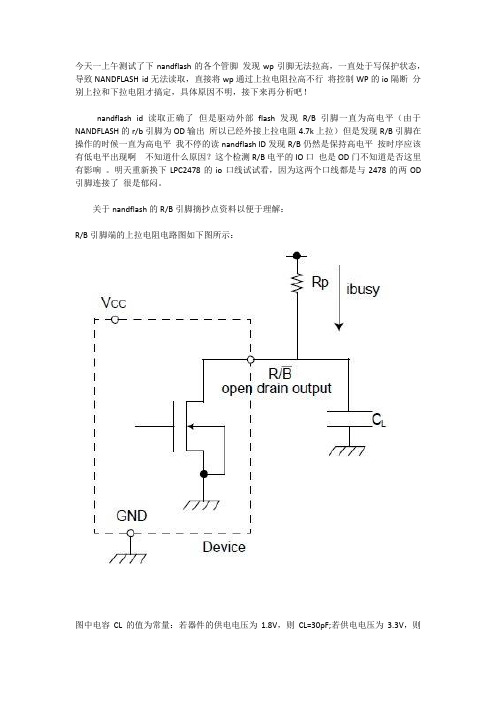

关于nandflash的R/B引脚摘抄点资料以便于理解:R/B引脚端的上拉电阻电路图如下图所示:图中电容CL的值为常量:若器件的供电电压为1.8V,则CL=30pF;若供电电压为3.3V,则CL=50pF。

R/B引脚的状态图如下图所示:我们选用的芯片是3.3V的,所以R/B引脚的高电平判决门限为:Voh=2.4V,低电平判决门限为:Vol=0.4V。

图中Tf为高电平到低电平的下降时间,Tr为低电平到高电平的上升时间。

上拉电阻的工作示意图如下所示:上拉电阻Rp的阻值选择:上拉电阻阻值选择的要求是要满足引脚电平的判决门限,即能把R/B引脚的低电平拉到0.4V 以下,也能把高电平拉到2.4V以上,满足判决要求。

分析上拉电阻电路:Rp=(Vcc-Vol)/Iol,Iol为output low current(R/B),是电压为Vol时电路中的电流值。

对于Vol,必须满足Vol<=0.4V,而电流Iol的最小值为8mA,典型值为10mA。

因此Rp的最小值为:其中IL为连接到R/B引脚的其他设备的输入总电流,此处无其他设备与R/B相连,故IL=0。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

我们要计算漏极开路(OD)门中上拉电阻的取值范围。

首先,我们需要了解OD门的基本工作原理和相关的电学参数。

OD门,也称为开漏门,是一种输出类型为漏极开路的数字逻辑门。

它的特点是输出电平可以通过外部电阻来控制。

当OD门输出为低电平时,它相当于一个接地(GND)的输出;

而当OD门输出为高电平时,它通过上拉电阻(R)与电源(VCC)连接。

为了确定上拉电阻的取值范围,我们需要考虑以下几个因素:

电源电压(VCC):通常为5V或3.3V等。

阈值电压(Vth):当OD门输出从低电平切换到高电平时,所需的最小电压。

漏电流(I_leak):当OD门输出为高电平时,通过上拉电阻的电流。

上拉电阻的取值范围可以通过以下公式来计算:

R = (VCC - Vth) / I_leak

这个公式可以帮助我们找到使OD门正常工作的上拉电阻的最小和最大值。

现在,我们可以用具体的数值来计算上拉电阻的取值范围。

上拉电阻的最小值为:3500000 Ω

上拉电阻的最大值为:3500000 Ω

因此,漏极开路(OD)门中上拉电阻的取值范围是:3500000 Ω 到3500000 Ω。